# DALLA

# DS129x **Fliminator**

#### **FEATURES**

- Replaces 8 or 16 hard-to-get-at manual switches

- Options printed circuit board via software

- Modular expansion by cascading packages

- · Set or interrogate with only three signals

- Requires no pull-up resistors

- Links to system bus with the DS1206 Phantom Serial Interface Chip

- Low-power CMOS

- Switch setting changes occur simultaneously

- DS1290 and DS1292 maintain settings in the absence of power; DS1291 and DS1293 are volatile

- Over 10 years of data retention for DS1290 and DS1292

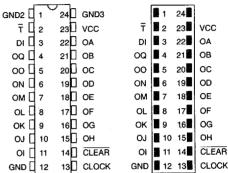

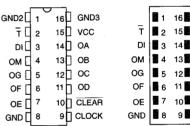

### PIN ASSIGNMENT

DS1293 24-Pin DIP (300 Mil) See Mech. Drawings Section

DS1292 24-Pin Encapsulated Package (450 Mil) See Mech. **Drawings Section**

15 VCC

14 OA

10

9

ОВ

OC

OD

CLEAR

CLOCK

DS1291 16-Pin DIP (300 Mil) See Mech. Drawings Section

DS1290 16-Pin Encapsulated Package (450 Mil) See Mech. Drawings Section

## DESCRIPTION

The DS129x Eliminator replaces manual switches used to option printed circuit boards. Up to sixteen output pins can be set to a logic level or interrogated by three signals: clock, data and transfer. The Eliminator can be controlled with software using the DS1206 Phantom Interface to synthesize the clock, data and transfer signals from a system bus. Multiple packages can be strung together for modular expansion. Once programmed, the DS1290 and DS1292 will maintain high or low level outputs, duplicating the effects of a mechanical switch and pull-up resistor. The technical support needed to configure a system is minimized with the Eliminator, Phantom Interface and menu-driven software.

### PIN DESCRIPTION

CLEAR

Ŧ Transfer DI Data Input OA-OO Switch Outputs CLOCK Clock Input

+5 Volts  $V_{CC}$ GND Ground

GND2 Missing on DS1292. Must be grounded on DS1293.

All Outputs Set Low

GND3 Missing on DS1292. Must be grounded on DS1293.

#### **OPERATION**

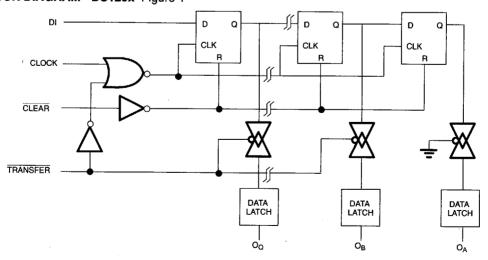

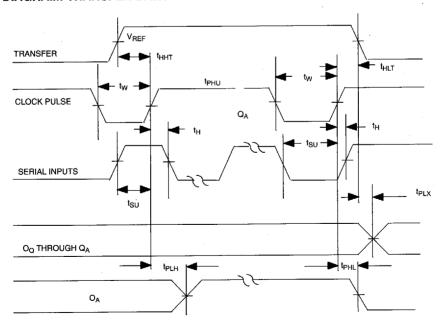

The DS1292/DS1293 Eliminator is a 16-bit shift register that has a clocked serial input, an asynchronous clear, and an output transfer control (see "Block Diagram" in Figure 1). The DS1290/DS1291 Eliminator is an 8-bit shift register that has a clocked serial input, an asynchronous clear, and an output transfer control. Data can be entered into the registers only when the transfer input (T) is at a high level. While at a high level, the transfer function allows serial entry of data via the data input pin (DI). The outputs 00 through 08 remain in the state that was set prior to  $\overline{T}$  being driven to a high level. Output  $0_A$ will change state as new data is entered. This output provides a method of feeding back actual output settings prior to setting the Tinput low (Figure 2). When the  $\overline{\mathsf{T}}$  input is driven low, new data that has been input into the 16-bit shift register is now locked at outputs 00 through  $0_A$ . When the  $\overline{T}$  input is low, all clock and data inputs are ignored. Valid data is clocked into the eliminator while T is high on the low-to-high transition of the CLOCK input. Data can be changed while the CLOCK input is high or low, but only data meeting the setup requirements will enter the shift register. The CLEAR input will always set all outputs to low level regardless of the level of the CLOCK or T input.

#### **DATA RETENTION MODE**

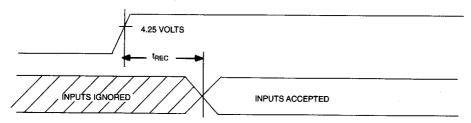

The DS129x Eliminator provides full functional capability when  $V_{CC}$  is greater than 4.5 volts and will ignore all inputs when  $V_{CC}$  reaches 4.25 volts typical. In this manner, the settings of each register remain intact during

power transients. As  $V_{CC}$  falls below approximately 3 volts, an internal power switching circuit connects a lithium energy source to the shift register to maintain data. During power-up when  $V_{CC}$  rises above approximately 3 volts, the power switching circuit connects external  $V_{CC}$  to the shift register and disconnects the lithium energy source. Normal operation can resume after  $V_{CC}$  exceeds 4.5 volts for 10 ms minimum. During power transients the 16 outputs will track the level of  $V_{CC}$  if set to logic 1 and will remain at ground level if set to Logic 0.

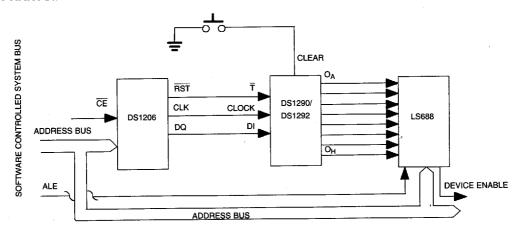

## **TYPICAL APPLICATION - ELIMINATOR**

The DS129x and DS1206 combine to make a programmable nonvolatile DIP switch that can be transparently set in systems without disturbing other operations. Because the switches are nonvolatile, they need only be set once; they will remain in the programmed state indefinitely. The block diagram of Figure 2 shows the Eliminator implemented with the DS1206 Phantom Serial Interface Chip. The DS1206 samples four address lines and the chip enable signal looking for a special pattern for 24 consecutive cycles (see the DS1206 data sheet). When a proper match is found, the address lines and one data line become control and data signals that are used to program and verify the settings of the DS129x. All of the signaling sent to the DS1206 and subsequently to the DS1292 is generated by software-controlled read cycles that have no effect on the rest of system operation. The clear signal can be used to restore a system back to an unconfigured state.

## BLOCK DIAGRAM - DS129x Figure 1

# PHANTOM INTERFACE AND ELIMINATOR TYPICAL APPLICATION Figure 2

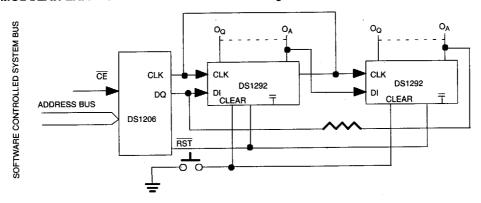

# MODULAR EXPANSION OF THE ELIMINATOR Figure 3

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage on any Pin Relative to Ground Operating Temperature Storage Temperature Soldering Temperature

-0.3V to +7.0V 0°C to 70°C -40°C to +70°C 260°C for 10 seconds

## RECOMMENDED DC OPERATING CONDITIONS

(0°C to 70°C)

| PARAMETER      | SYMBOL          | MIN  | TYP | MAX                  | UNITS | NOTES |

|----------------|-----------------|------|-----|----------------------|-------|-------|

| Supply Voltage | V <sub>CC</sub> | 4.5  | 5.0 | 5.5                  | ٧     | 1     |

| Logic 1        | V <sub>IH</sub> | 2.2  |     | V <sub>CC</sub> +0.3 | >     | 1     |

| Logic 0        | V <sub>IL</sub> | -0.3 |     | +0.8                 | ٧     | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to } 70^{\circ}\text{C}; V_{\text{CC}} = 4.5\text{V to } 5.5\text{V})$

| PARAMETER             | SYMBOL          | MIN  | TYP | MAX  | UNITS | NOTES |

|-----------------------|-----------------|------|-----|------|-------|-------|

| Supply Current        | Icc             |      | 3   | 5    | mA    |       |

| Input Leakage         | I <sub>IL</sub> | -1.0 |     | +1.0 | μА    | 4     |

| Output Leakage        | l <sub>LO</sub> | -1.0 |     | +1.0 | μА    |       |

| Logic 1 Output @ 2.4V | Іон             | -1.0 |     |      | mA    | 2     |

| Logic 0 Output @ 0.4V | l <sub>OL</sub> |      |     | 4.0  | mA    | 2     |

**CAPACITANCE**

$(t_A = 25^{\circ}C)$

| PARAMETER          | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance  | C <sub>IN</sub>  |     |     | 5   | pF    |       |

| Output Capacitance | C <sub>OUT</sub> |     |     | 7   | pF    |       |

#### **AC ELECTRICAL CHARACTERISTICS**

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{CC} = 5\text{V} \pm 10\%)$

| PARAMETER                                                   | SYMBOL              | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------------------------------|---------------------|-----|-----|-----|-------|-------|

| Clock Frequency                                             | fcLock              |     |     | 10  | MHz   |       |

| Width of Clock Pulse                                        | tw <sub>CLOCK</sub> | 50  |     |     | ns    | 3     |

| Width of Clear Pulse                                        | tw <sub>CLEAR</sub> | 50  |     |     | ns    | 3     |

| Data Setup Time                                             | t <sub>SU</sub>     | 30  |     |     | ns    | 3     |

| Data Hold Time                                              | t <sub>H</sub>      | 10  |     |     | ns    | 3     |

| Propagation Delay Time High to Low Level Clear to Output    | t <sub>PHLC</sub>   |     |     | 70  | ns    | 3     |

| Propagation Delay Time Low to<br>High Level Clock to Output | t <sub>PLH</sub>    |     |     | 50  | ns    | 3     |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# AC ELECTRICAL CHARACTERISTICS (cont'd)

| PARAMETER                                                  | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------------------------------------|------------------|-----|-----|-----|-------|-------|

| Propagation Delay Time High to Low Level Clock to Output   | t <sub>PHL</sub> |     |     | 50  | ns    | 3     |

| Recovering on Power-Up                                     | t <sub>REC</sub> | 10  |     |     | ms    |       |

| Propagation Delay Time High to Low Level Transfer to O Out | t <sub>PLX</sub> |     |     | 50  | ns    | 3     |

| Transfer High to Clock Input High                          | t <sub>HHT</sub> | 50  |     |     | ns    | 3     |

| Transfer Low from Clock Input High                         | thlt             | 50  |     |     | ns    | 3     |

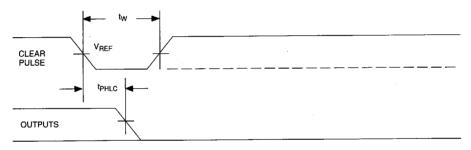

# TIMING DIAGRAM: CLEAR CONTROL (3)

# TIMING DIAGRAM: TRANSFER DATA (3)

# TIMING DIAGRAM: POWER-UP (3)

#### **NOTES:**

- 1. All voltages are referenced to ground.

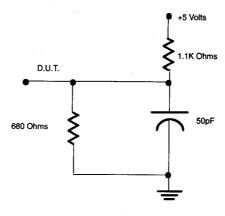

- 2. Measured with a load as shown in Figure 4.

- 3.  $V_{REF} = 1.5 \text{ volts.}$

- 4. Clock and transfer inputs have internal pull-down resistors of 20K ohms typical. Clear has an internal pull-up resistor of 20K ohms typical.

## **OUTPUT LOAD** Figure 4