## XBERT Device Bit Error Rate Generator Receiver TXC-06125

## **DATA SHEET**

## FEATURES

- Bit-serial, nibble-parallel, and byte-parallel interface capability, selectable via control bits

- Transmit and receive clock rate: 100 Hz to 78 MHz for serial, nibble, byte I/O (all telecom rates up to OC-12/STM-4)

- Test patterns at up to 622 Mbit/s using byteparallel interface and some external circuitry

- 2<sup>15</sup> 1, 2<sup>20</sup> 1, 2<sup>20</sup> 1 QRSS and 2<sup>23</sup> 1 pseudo-random generators and detectors

- · Fixed word test generator and detector

- All ones

- All zeros

- Alternate 1/0 pattern

- Alternate 11/00 pattern

- Microprocessor-programmable test word generator and detector (1 to 4 bytes)

- Error generators (single, or 10<sup>-3</sup> and 10<sup>-6</sup> BER)

- Bit error counter and clock counter (24 bits each)

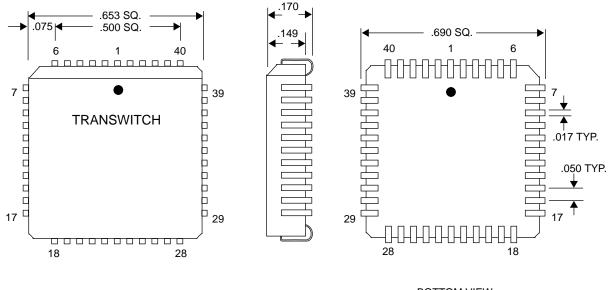

- 44-pin plastic leaded chip carrier

#### **DESCRIPTION ≡**

The Bit Error Rate Generator/Receiver (XBERT) VLSI device is a microprocessor-programmable multi-rate test pattern generator and receiver on a single chip. It is used for testing the performance of digital communication circuits and communication links. It provides a bitserial, nibble-parallel or byte-parallel interface, and is capable of operating in a burst data mode by using external signals to enable/disable the transmit and receive clocks. The XBERT generates and analyzes pseudo-random patterns, fixed words, or programmable words. Four pseudo-random test patterns are provided:  $2^{15}$  - 1,  $2^{20}$  - 1,  $2^{20}$  - 1 with zero suppression (Quasi-Random Signal Source, not available in byte-parallel mode), and  $2^{23}$  - 1. The fixed word mode generates and analyzes all zeros, all ones, alternate one/zero pattern or a double alternate one/zero (1100) pattern. The programmable mode allows a choice of one to four bytes written by the microprocessor.

## APPLICATIONS ≡

- Transmission and switching systems

- Data communications

- Test equipment

- Remote testing and fault isolation

- · Embedded test for proprietary framing algorithms

- Embedded test for secure lines

TranSwitch Corporation • 8 Progress Drive • Shelton, CT 06484 • USA • Tel: 203-929-8810 • Fax: 203-926-9453

## TABLE OF CONTENTS

| SECTION                                                              | PAGE  |

|----------------------------------------------------------------------|-------|

| Block Diagram                                                        | 3     |

| Block Diagram Description                                            | 3     |

| Pin Diagram                                                          | 5     |

| Pin Descriptions                                                     | 5     |

| Absolute Maximum Ratings                                             | 9     |

| Thermal Characteristics                                              | 9     |

| Power Requirements                                                   | 9     |

| Input, Output and I/O Parameters                                     | 11    |

| Timing Characteristics                                               |       |

| Operation                                                            | 20-21 |

| Decoupling of Power Supply Pins                                      | 20    |

| External Circuit for Proper Updating of Bit Error and Clock Counters | 20    |

| Memory Map                                                           | 22    |

| Memory Map Descriptions                                              | 23    |

| Package Information                                                  |       |

| Ordering Information                                                 | 27    |

| Related Products                                                     | 27    |

| Standards Documentation Sources                                      |       |

| List of Data Sheet Changes                                           | 29    |

| Documentation Update Registration Form                               | 33    |

|                                                                      |       |

## LIST OF FIGURES

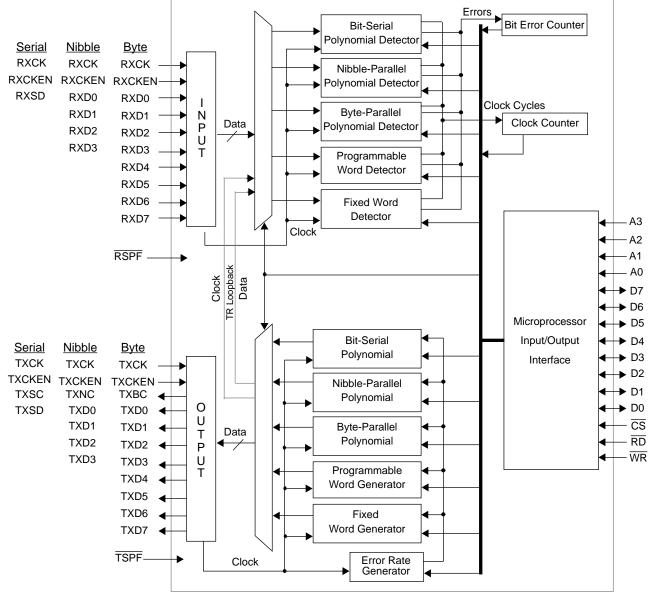

| Figure 1.  | XBERT TXC-06125 Block Diagram                      | 3  |

|------------|----------------------------------------------------|----|

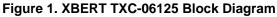

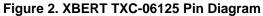

| Figure 2.  | XBERT TXC-06125 Pin Diagram                        | 5  |

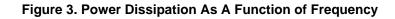

| Figure 3.  | Power Dissipation as a Function of Frequency       | 10 |

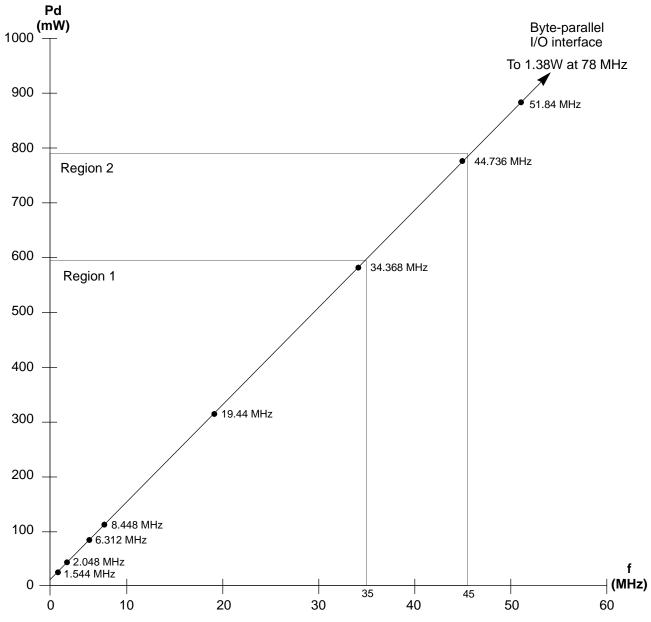

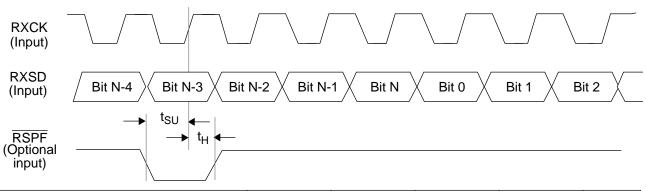

| Figure 4.  | Receive Serial Interface Timing                    | 12 |

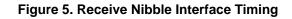

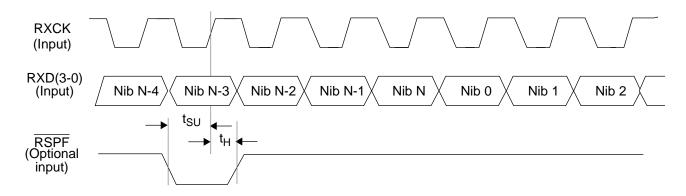

| Figure 5.  | Receive Nibble Interface Timing                    | 13 |

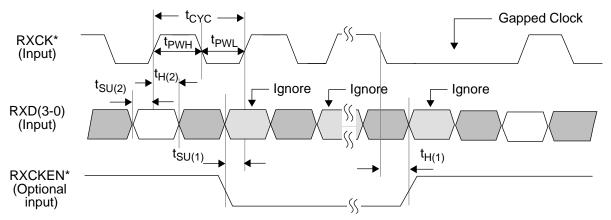

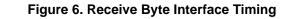

| Figure 6.  | Receive Byte Interface Timing                      | 14 |

| Figure 7.  | Transmit Serial Interface Timing                   | 15 |

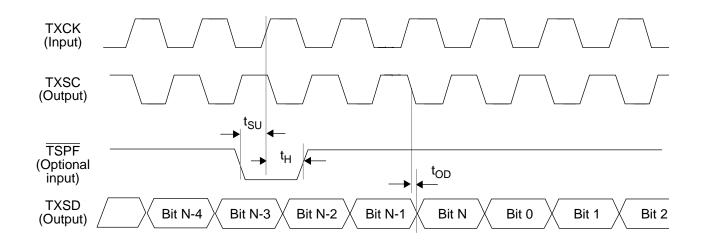

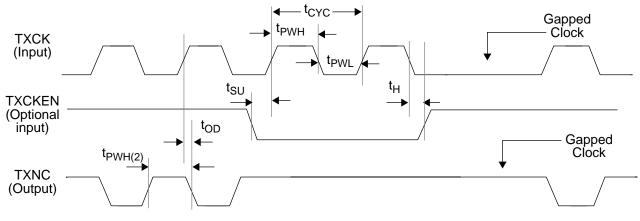

| Figure 8.  | Transmit Nibble Interface Timing                   | 16 |

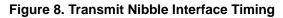

| Figure 9.  | Transmit Byte Interface Timing                     | 17 |

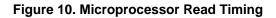

| Figure 10. | Microprocessor Read Timing                         | 18 |

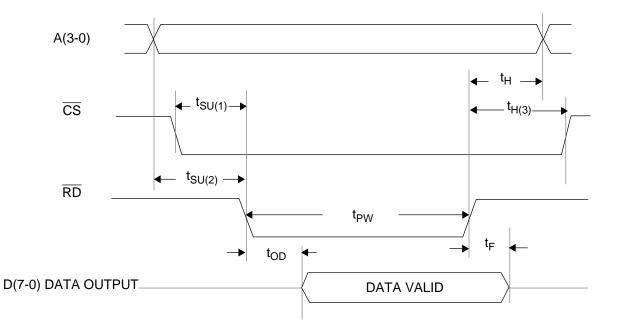

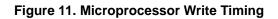

| Figure 11. | Microprocessor Write Timing                        | 19 |

| Figure 12. | Recommended Decoupling of Power Supply Pins        | 20 |

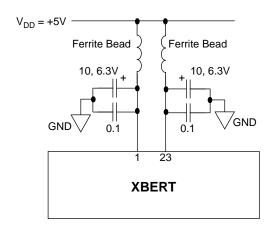

| Figure 13. | Protection of XBERT from Read/Write Signals        |    |

|            | Intended for other Devices                         | 21 |

| Figure 14. | XBERT TXC-06125 44-Pin Plastic Leaded Chip Carrier | 26 |

## **BLOCK DIAGRAM**

## **BLOCK DIAGRAM DESCRIPTION**

Figure 1 is a simplified block diagram of the XBERT. The Input Block accepts bit-serial (RXSD), nibble-parallel (RXD3-RXD0) or byte-parallel (RXD7-RXD0) data, one of which is selected by writing control bits in the memory map. Incoming data is clocked into the XBERT on positive transitions of the clock signal (RXCK). An input for a receive enable signal (RXCKEN) is provided. A low on this signal lead disables the input clock from clock-ing in data and permits operation in burst mode.

The test pattern, which is common to both the receiver and transmitter, is selected by writing control bits in the memory map. Each of the test pattern detectors is equipped with a pattern generator and comparator. The comparison between the incoming data and the pattern generator is enabled after frame alignment takes place, or when the receive start of the pseudo-random feature (RSPF) is used.

For a 1100 test pattern, a simplified view of the frame alignment (after two consecutive pattern matches), error detection, and loss of frame alignment (after three consecutive pattern match failures) is shown below:

|                         | "in frame"<br>start detected | LOF<br>detected       |

|-------------------------|------------------------------|-----------------------|

| Count good/bad patterns | 1 2                          | 1   2   3             |

| Received signal         | 1100110011001100             | .11001000111011011100 |

| Local generated signal  | 1100110011001100             | 1100110011001100      |

| Detected errors         | 000000000000000              | . 000010000100001     |

Running counts of the numbers of bit errors and clock cycles are maintained in two 24-bit counters. Bit error rate performance is determined by having the microprocessor read the counters on a scheduled basis and compute the ratio as an error rate, making due allowance for bit/clock ratios of 4 in nibble-parallel operation and 8 in byte-parallel operation. The clock counter operates regardless of frame alignment status. Both counters should be read together, and at intervals of less than the roll-over interval of the clock counter (about 16 million clock cycles). When XBERT is "in frame", errors are detected one event later. No bit errors are detected after a loss of frame condition occurs.

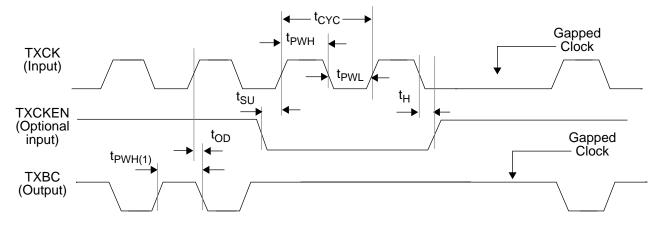

The transmit clock signal (TXCK) provides the time base for transmitter operation. An input transmit enable signal (TXCKEN) is provided. A low disables the input clock (TXCK) from clocking out data and permits operation in burst mode. This feature is provided for applications where a gapped clock signal is required to prevent the transmitter from clocking out test pattern data.

The interface selection is common to both the receiver and transmitter. The transmit clock signal (TXCK) is used to derive the TXSC, TXNC and the TXBC clock signals. Bit-serial, nibble-parallel and byte-parallel data are clocked out of the XBERT on the falling edges of TXSC, TXNC and TXBC respectively.

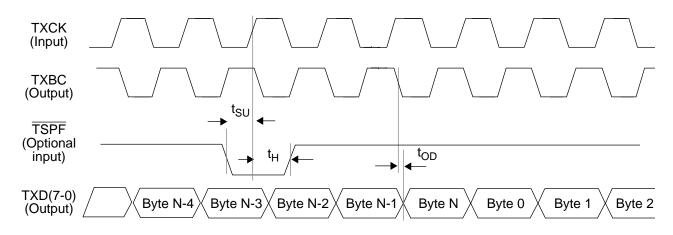

For framer applications, a transmit start of pseudo-random pattern framing pulse ( $\overline{\text{TSPF}}$ ) is used to preset the transmit pseudo-random generators' shift registers to ones. This feature permits the XBERT to start the pseudo-random pattern immediately with a fixed relationship to the start of a frame.

For framer applications, a receive start of pseudo-random pattern framing pulse ( $\overline{RSPF}$ ) disables the frame alignment circuits in the pseudo-random pattern detectors and presets the pseudo-random generators' shift registers to ones, which will result in an immediate "in frame" condition. Used in conjunction with the transmit start of pseudo-random pattern pulse, this feature permits the XBERT to start a search immediately for bit errors in the receive data. A software reset is required to enable the frame alignment circuitry in the pseudo-random detectors for normal operation.

The microprocessor interface consists of four address bits (A3-A0), eight bidirectional data bus bits (D7-D0), chip select ( $\overline{CS}$ ), and the read ( $\overline{RD}$ ) and write ( $\overline{WR}$ ) signal inputs. A Transmit-to-Receive (TR) loopback feature is provided for self-testing the XBERT device.

## **PIN DIAGRAM**

## **PIN DESCRIPTIONS**

#### POWER SUPPLY AND GROUND

| Symbol | Pin No.          | I/O/P* | Туре                                  | Name/Function |  |  |

|--------|------------------|--------|---------------------------------------|---------------|--|--|

| VDD    | 1, 23            | Р      | V <sub>DD</sub> : +5 volt supply, ±5% |               |  |  |

| GND    | 12, 22<br>29, 34 | Р      | Ground: Zero volt reference level.    |               |  |  |

\*Note: I = Input; O = Output; P = Power

## **RECEIVE INTERFACE**

| Symbol    | Pin No. | I/O/P | Type* | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----------|---------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RXCK      | 2       | Ι     | TTLp  | <b>Receive Clock:</b> Bit-serial, nibble-parallel, and byte-parallel receive data is clocked into the XBERT on the rising edge of this clock. This clock is used as the time base for all receive functions. It may be gapped to accommodate overhead bit times. Loss of this clock causes the XBERT receiver to become inoperative. See Note 1.                                                                                                                                                                                              |  |  |

| RXCKEN    | 3       | I     | TTLp  | <b>Receive Clock Enable:</b> A high enables the receive clock for clocking data into the XBERT. A low disables the clock from clocking in receive bit-serial, nibble-parallel, or byte-parallel data. See Note 1.                                                                                                                                                                                                                                                                                                                             |  |  |

| RXSD/RXD0 | 4       | I     | TTLp  | Receive Bit-Serial Data/Receive Nibble- or Byte-<br>Parallel Data, Bit 0: This is the input pin for receive bit-<br>serial data. It is also used as the least significant bit (bit<br>0) input pin for receive nibble- or byte-parallel data.                                                                                                                                                                                                                                                                                                 |  |  |

| RXD1      | 5       | I     | TTLp  | Receive Nibble- or Byte-Parallel Data, Bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RXD2      | 6       | I     | TTLp  | Receive Nibble- or Byte-Parallel Data, Bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RXD3      | 7       | I     | TTLp  | <b>Receive Nibble- or Byte-Parallel Data, Bit 3:</b> This is the input pin for the most significant bit (bit 3) for the receive nibble-parallel interface.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| RXD4      | 8       | I     | TTLp  | Receive Byte-Parallel Data, Bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RXD5      | 9       | I     | TTLp  | Receive Byte-Parallel Data, Bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RXD6      | 10      | I     | TTLp  | Receive Byte-Parallel Data, Bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RXD7      | 11      | Ι     | TTLp  | <b>Receive Byte-Parallel Data, Bit 7:</b> This is the input pin for the most significant bit (bit 7) for the receive byte-parallel interface.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RSPF      | 20      | Ι     | ΤΤLp  | <b>Receive Start of Pseudo-random Pattern Framing:</b><br>An active low enables the PRBS detector to search for<br>an all ones pattern, defining the start of PRBS pattern<br>detection. The first receive pulse sequence (all ones)<br>disables the loss of frame alignment circuit and enables<br>the bit error counter and clock cycle counter. RXCKEN<br>must be enabled before RSPF is clocked in. Once<br>enabled, this feature can only be disabled by a reset.<br>This pin is inoperative for fixed or programmable word<br>patterns. |  |  |

\* See Input, Output and I/O Parameters section for Type definitions.

Note 1: Use of a gapped Receive Clock input (RXCK) or the Receive Clock Enable (RXCKEN) input to disable clocking in of Receive Data for defined time intervals is subject to restrictions. Please contact TranSwitch Applications Engineering for additional technical information relevant to applications employing these capabilities.

### TRANSMIT INTERFACE

| Symbol                 | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------------------|---------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ТХСК                   | 24      | I     | TTLp   | <b>Transmit Clock:</b> An input clock used as the time base<br>for generating the test patterns and for sourcing bit-<br>serial, nibble-parallel, and byte-parallel transmit data ou<br>of the XBERT. This clock may be gapped to accommo-<br>date overhead bit times, as required. Loss of this clock<br>causes the XBERT transmitter to become inoperative.                                                                                                                                                                                                                                                       |  |  |

| TXCKEN                 | 25      | I     | TTLp   | <b>Transmit Clock Enable:</b> A high enables the transmit clock (TXCK) for clocking data out of the XBERT. A low disables the clock from clocking out transmit bit-serial, nibble-parallel, or byte-parallel data.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| TXSC/<br>TXNC/<br>TXBC | 26      | 0     | TTL8mA | Transmit Serial/Nibble/Byte Clock: This clock is<br>derived from the transmit clock signal (TXCK), and is<br>used for clocking out data from the XBERT. Data is<br>clocked out of the XBERT on the falling edge of this<br>clock. This clock will have gapped periods correspond-<br>ing to the times when the transmit enable signal<br>(TXCKEN) is low.                                                                                                                                                                                                                                                           |  |  |

| TXSD/TXD0              | 27      | 0     | TTL8mA | Transmit Bit-Serial Data/Transmit Nibble- or Byte-<br>Parallel Data, Bit 0: This is the output pin for transmit<br>bit-serial data. It is also used as the least significant bit<br>(bit 0) output pin for transmit nibble- or byte-parallel data.<br>This bit is the least significant bit and the last bit clocked<br>out for transmit nibble- or byte-parallel data.                                                                                                                                                                                                                                             |  |  |

| TXD1                   | 28      | 0     | TTL8mA | Transmit Nibble- or Byte-Parallel Data, Bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TXD2                   | 30      | 0     | TTL8mA | Transmit Nibble- or Byte-Parallel Data, Bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TXD3                   | 31      | 0     | TTL8mA | <b>Transmit Nibble- or Byte-Parallel Data, Bit 3:</b> This is the output pin for the most significant bit (bit 3) for the transmit nibble-parallel interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| TXD4                   | 32      | 0     | TTL8mA | Transmit Byte-Parallel Data, Bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TXD5                   | 33      | 0     | TTL8mA | Transmit Byte-Parallel Data, Bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TXD6                   | 35      | 0     | TTL8mA | Transmit Byte-Parallel Data, Bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TXD7                   | 36      | 0     | TTL8mA | <b>Transmit Byte-Parallel Data, Bit 7.</b> This is the output pin for the most significant bit (bit 7) for the transmit byte-parallel interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| TSPF                   | 21      | Ι     | TTLp   | Transmit Start of Pseudo-random Pattern Framing:<br>An active low pulse causes the XBERT to reset to the<br>beginning of the PRBS pattern. The starting pulse<br>sequence is an all ones pattern, which defines the start<br>of the transmitted PRBS test pattern. If the transmit clock<br>enable signal (TXCKEN) is high when TSPF is clocked<br>in on the positive edge of the clock, the generator trans-<br>mits the start of the pseudo-random test pattern one and<br>one half clock cycles later (on a negative clock transi-<br>tion). This pin is inoperative for fixed or programmable<br>word patterns. |  |  |

## MICROPROCESSOR INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                          |  |  |

|--------|---------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D(7-0) | 44-37   | I/O   | TTL8mA | <b>Data Bus:</b> Used for programming and reading the registers which reside in the XBERT. The most significant bit is D7. High is logic 1.                                                                            |  |  |

| CS     | 17      | I     | TTLp   | Chip Select: A low enables data transfers between the microprocessor and the XBERT memory map during a read/write bus cycle.                                                                                           |  |  |

| RD     | 18      | Ι     | TTLp   | <b>Read Data:</b> An active low signal generated by the micro-<br>processor for reading the registers which reside in the<br>memory map. The XBERT memory I/O is selected by<br>placing a low on the chip select lead. |  |  |

| WR     | 19      | Ι     | TTLp   | Write Data: An active low signal generated by the micro-<br>processor for writing to the registers which reside in the<br>memory map. The XBERT memory I/O is selected by<br>placing a low on the chip select lead.    |  |  |

| A(3-0) | 16-13   | I     | TTLp   | Address Lines: The four address lines are used to select an XBERT register location. A7 is the most significant bit. High is logic 1.                                                                                  |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol          | Min* | Max*                  | Unit |

|--------------------------------|-----------------|------|-----------------------|------|

| Supply voltage                 | V <sub>DD</sub> | -0.3 | 7.0                   | V    |

| DC input voltage               | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Continuous power dissipation   | P <sub>C</sub>  |      | **                    | mW   |

| Ambient operating temperature  | T <sub>A</sub>  | **   | **                    | °C   |

| Operating junction temperature | TJ              |      | 125                   | °C   |

| Storage temperature range      | Τ <sub>S</sub>  | -55  | 125                   | °C   |

\*Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

\*\*The minimum and maximum allowable ambient operating temperatures, and the maximum power dissipation, will be dependent on the total thermal analysis.

## THERMAL CHARACTERISTICS

| Parameter                                   | Min | Тур | Max  | Unit | Test Conditions         |

|---------------------------------------------|-----|-----|------|------|-------------------------|

| Thermal resistance -<br>junction to ambient |     |     | 68   | °C/W | 0 ft/min linear airflow |

| Thermal resistance -<br>junction to case    |     |     | 13.4 | °C/W | 0 ft/min linear airflow |

## POWER REQUIREMENTS

| Parameter       | Min  | Тур | Мах  | Unit | Test Conditions  |

|-----------------|------|-----|------|------|------------------|

| V <sub>DD</sub> | 4.75 | 5.0 | 5.25 | V    |                  |

| I <sub>DD</sub> |      |     | *    | mA   |                  |

| P <sub>DD</sub> |      |     | *    | mW   | Inputs switching |

\*Power dissipation is application specific and depends on the operating frequency, as shown in Figure 3.

For operation of the XBERT device in still air without a heat sink, the safe operating regions are defined by the equation:  $T_{JMAX} = T_A + [(68^{\circ}C/W) \times (Pd)] = 125^{\circ}C$

**Region 1 =** XBERT may be used in a maximum ambient temperature of  $T_A = 85^{\circ}C$  for TXCK and RXCK clock frequencies  $\leq 35$  MHz. This yields a maximum bit rate of 8 x 35 = 280 Mbit/sec.

**Region 2 =** XBERT may be used in a maximum ambient temperature of  $T_A = 70^{\circ}C$  for TXCK and RXCK clock frequencies 35 MHz  $\leq$  f  $\leq$  45 MHz. This yields a maximum bit rate of 8 x 45 = 360 Mbit/sec.

**Note:** Combinations of frequency and ambient temperature beyond the safe operating regions require additional heat dissipation methods (the maximum power is 1.38 watts at 622/8 = 78 MHz). A TranSwitch Application Note entitled "Designing with TranSwitch XBERT Devices for Byte Interface at the OC-12 Rate", document number TXC-06125-AN1, provides guidance on circuit and heat sink requirements for operation of XBERT at 622 Mbit/s.

## INPUT, OUTPUT AND I/O PARAMETERS

#### INPUT PARAMETERS FOR TTLp

| Parameter             | Min | Тур   | Max | Unit | Test Conditions              |

|-----------------------|-----|-------|-----|------|------------------------------|

| V <sub>IH</sub>       | 2.0 |       |     | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |     |       | 0.8 | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |     | -70.0 |     | μA   | V <sub>DD</sub> = 5.25       |

| Input capacitance     |     | 3.8   |     | pF   |                              |

Note: Input has a 72k (nominal) internal pullup resistor.

#### **OUTPUT PARAMETERS FOR TTL8mA**

| Parameter         | Min | Тур | Max  | Unit | Test Conditions                                |

|-------------------|-----|-----|------|------|------------------------------------------------|

| V <sub>OH</sub>   | 3.7 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -8.0 |

| V <sub>OL</sub>   |     |     | 0.5  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0  |

| I <sub>OL</sub>   |     |     | 8.0  | mA   |                                                |

| I <sub>OH</sub>   |     |     | -8.0 | mA   |                                                |

| t <sub>RISE</sub> | 1.0 | 2.7 | 5.7  | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub> | 2.7 | 6.1 | 11.7 | ns   | C <sub>LOAD</sub> = 15 pF                      |

#### **INPUT/OUTPUT PARAMETERS FOR TTL8mA**

| Parameter             | Min | Тур   | Max  | Unit | Test Conditions                                |

|-----------------------|-----|-------|------|------|------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |       |      | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                   |

| V <sub>IL</sub>       |     |       | 0.8  | V    | $4.75 \le V_{DD} \le 5.25$                     |

| Input leakage current |     | -70.0 |      | μΑ   | V <sub>DD</sub> = 5.25                         |

| Input capacitance     |     | 7.1   |      | pF   |                                                |

| V <sub>OH</sub>       | 3.7 |       |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -8.0 |

| V <sub>OL</sub>       |     |       | 0.5  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0  |

| I <sub>OL</sub>       |     |       | 8.0  | mA   |                                                |

| I <sub>OH</sub>       |     |       | -8.0 | mA   |                                                |

| t <sub>RISE</sub>     | 1.1 | 3.3   | 7.3  | ns   | C <sub>LOAD</sub> = 15 pF                      |

| t <sub>FALL</sub>     | 3.1 | 8.0   | 16.0 | ns   | C <sub>LOAD</sub> = 15 pF                      |

## TIMING CHARACTERISTICS

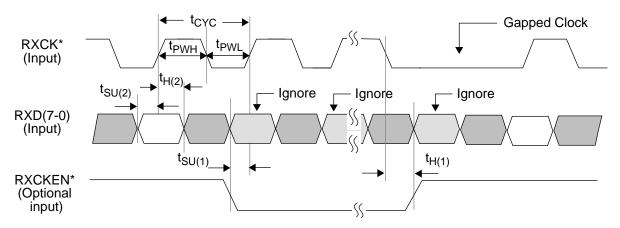

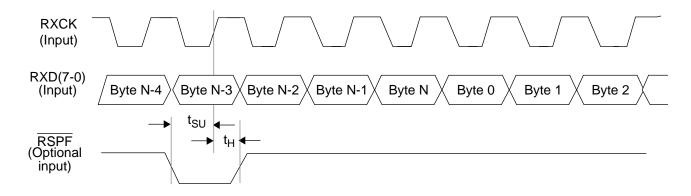

Detailed timing diagrams for the XBERT are illustrated in Figures 4 through 11, with values of the timing intervals tabulated below each diagram. All output times are measured with a maximum 75 pF load capacitance. Timing parameters are measured at voltage levels of  $(V_{IH} + V_{IL})/2$  for input signals or  $(V_{OH} + V_{OL})/2$  for output signals.

\* See Note in Pin Descriptions section.

| Parameter                                | Symbol             | Min  | Тур                  | Max | Unit |

|------------------------------------------|--------------------|------|----------------------|-----|------|

| RXCK clock period                        | t <sub>CYC</sub>   | 12.8 |                      |     | ns   |

| RXCK high time                           | t <sub>PWH</sub>   | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| RXCK low time                            | t <sub>PWL</sub>   | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| RXCKEN set-up time before RXCK1          | t <sub>SU(1)</sub> | 2.5  |                      |     | ns   |

| RXCKEN hold time after RXCK $\downarrow$ | t <sub>H(1)</sub>  | 2.5  |                      |     | ns   |

| RXSD set-up time before RXCK1            | t <sub>SU(2)</sub> | 3.0  |                      |     | ns   |

| RXSD hold time after RXCK <sup>↑</sup>   | t <sub>H(2)</sub>  | 3.0  |                      |     | ns   |

Note: RXCK may be gapped or stretched without the use of the RXCKEN input to accommodate overhead bit times. The set-up and hold times specified for RXCKEN must be met to ensure correct operation.

| Parameter                                 | Symbol          | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------|-----|-----|-----|------|

| RSPF set-up time before RXCK <sup>↑</sup> | t <sub>SU</sub> | 2.5 |     |     | ns   |

| RSPF hold time after RXCK↑                | t <sub>H</sub>  | 2.5 |     |     | ns   |

\* See Note in Pin Descriptions section.

| Parameter                                     | Symbol             | Min  | Тур                  | Max | Unit |

|-----------------------------------------------|--------------------|------|----------------------|-----|------|

| RXCK clock period                             | t <sub>CYC</sub>   | 12.8 |                      |     | ns   |

| RXCK high time                                | t <sub>PWH</sub>   | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| RXCK low time                                 | t <sub>PWL</sub>   | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| RXCKEN set-up time before RXCK1               | t <sub>SU(1)</sub> | 2.5  |                      |     | ns   |

| RXCKEN hold time after RXCK $\downarrow$      | t <sub>H(1)</sub>  | 2.5  |                      |     | ns   |

| RXD(3-0) set-up time before RXCK <sup>↑</sup> | t <sub>SU(2)</sub> | 3.0  |                      |     | ns   |

| RXD(3-0) hold time after RXCK <sup>↑</sup>    | t <sub>H(2)</sub>  | 3.0  |                      |     | ns   |

Note: RXCK may be gapped or stretched without the use of the RXCKEN input to accommodate overhead bit times. The set-up and hold times specified for RXCKEN must be met to ensure correct operation.

| Parameter                                 | Symbol          | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------|-----|-----|-----|------|

| RSPF set-up time before RXCK <sup>↑</sup> | t <sub>SU</sub> | 2.5 |     |     | ns   |

| RSPF hold time after RXCK↑                | t <sub>H</sub>  | 2.5 |     |     | ns   |

\* See Note in Pin Descriptions section.

| Parameter                                   | Symbol             | Min  | Тур                  | Max | Unit |

|---------------------------------------------|--------------------|------|----------------------|-----|------|

| RXCK clock period                           | t <sub>CYC</sub>   | 12.8 |                      |     | ns   |

| RXCK high time                              | t <sub>PWH</sub>   | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| RXCK low time                               | t <sub>PWL</sub>   | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| RXCKEN set-up time before RXCK <sup>↑</sup> | t <sub>SU(1)</sub> | 2.5  |                      |     | ns   |

| RXCKEN hold time after RXCK $\downarrow$    | t <sub>H(1)</sub>  | 2.5  |                      |     | ns   |

| RXD(7-0) set-up time before RXCK↑           | t <sub>SU(2)</sub> | 3.0  |                      |     | ns   |

| RXD(7-0) hold time after RXCK <sup>↑</sup>  | t <sub>H(2)</sub>  | 3.0  |                      |     | ns   |

Note: RXCK may be gapped or stretched without the use of the RXCKEN input to accommodate overhead bit times. The set-up and hold times specified for RXCKEN must be met to ensure correct operation.

| Parameter                                 | Symbol          | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------|-----|-----|-----|------|

| RSPF set-up time before RXCK <sup>↑</sup> | t <sub>SU</sub> | 2.5 |     |     | ns   |

| RSPF hold time after RXCK↑                | t <sub>H</sub>  | 2.5 |     |     | ns   |

#### Figure 7. Transmit Serial Interface Timing

| Parameter                                   | Symbol              | Min  | Тур                  | Max | Unit |

|---------------------------------------------|---------------------|------|----------------------|-----|------|

| TXCK clock period                           | t <sub>CYC</sub>    | 12.8 |                      |     | ns   |

| TXCK high time                              | t <sub>PWH</sub>    | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| TXCK low time                               | t <sub>PWL</sub>    | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| TXCKEN set-up time before TXCK <sup>↑</sup> | t <sub>SU</sub>     | 2.5  |                      |     | ns   |

| TXCKEN hold time after TXCK $\downarrow$    | t <sub>H</sub>      | 2.5  |                      |     | ns   |

| TXSC output delay after TXCK↑               | t <sub>OD</sub>     |      |                      | 5.0 | ns   |

| TXSC high time                              | t <sub>PWH(1)</sub> | 5.4  |                      |     | ns   |

Note: The clock (TXCK) may be gapped or stretched without the use of TXCKEN to accommodate overhead bit times. The set-up and hold times specified for TXCKEN must be met to ensure correct operation.

| Parameter                                 | Symbol          | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------|-----|-----|-----|------|

| TXSD output delay after TXSC $\downarrow$ | t <sub>OD</sub> |     |     | 5.0 | ns   |

| TSPF set-up time before TXCK1             | t <sub>SU</sub> | 2.5 |     |     | ns   |

| TSPF hold time after TXCK1                | t <sub>H</sub>  | 2.5 |     |     | ns   |

| Parameter                                | Symbol              | Min  | Тур                  | Max | Unit |

|------------------------------------------|---------------------|------|----------------------|-----|------|

| TXCK clock period                        | t <sub>CYC</sub>    | 12.8 |                      |     | ns   |

| TXCK high time                           | t <sub>PWH</sub>    | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| TXCK low time                            | t <sub>PWL</sub>    | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| TXCKEN set-up time before TXCK↑          | t <sub>SU</sub>     | 2.5  |                      |     | ns   |

| TXCKEN hold time after TXCK $\downarrow$ | t <sub>H</sub>      | 2.5  |                      |     | ns   |

| TXNC output delay after TXCK1            | t <sub>OD</sub>     |      |                      | 5.0 | ns   |

| TXNC high time                           | t <sub>PWH(1)</sub> | 5.4  |                      |     | ns   |

Note: The clock (TXCK) may be gapped or stretched without the use of TXCKEN to accommodate overhead bit times. The set-up and hold times specified for TXCKEN must be met to ensure correct operation.

| Parameter                                | Symbol          | Min | Тур | Max | Unit |

|------------------------------------------|-----------------|-----|-----|-----|------|

| TXD output delay after TXNC $\downarrow$ | t <sub>OD</sub> |     |     | 5.0 | ns   |

| TSPF set-up time before TXCK↑            | t <sub>SU</sub> | 2.5 |     |     | ns   |

| TSPF hold time after TXCK1               | t <sub>H</sub>  | 2.5 |     |     | ns   |

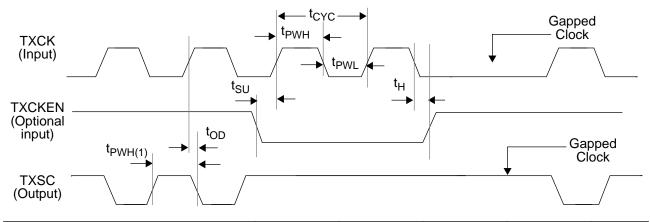

#### Figure 9. Transmit Byte Interface Timing

| Parameter                                | Symbol              | Min  | Тур                  | Max | Unit |

|------------------------------------------|---------------------|------|----------------------|-----|------|

| TXCK clock period                        | t <sub>CYC</sub>    | 12.8 |                      |     | ns   |

| TXCK high time                           | t <sub>PWH</sub>    | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| TXCK low time                            | t <sub>PWL</sub>    | 5.4  | 1/2 t <sub>CYC</sub> |     | ns   |

| TXCKEN set-up time before TXCK↑          | t <sub>SU</sub>     | 2.5  |                      |     | ns   |

| TXCKEN hold time after TXCK $\downarrow$ | t <sub>H</sub>      | 2.5  |                      |     | ns   |

| TXBC output delay after TXCK↑            | t <sub>OD</sub>     |      |                      | 5.0 | ns   |

| TXBC high time                           | t <sub>PWH(1)</sub> | 5.4  |                      |     | ns   |

Note: The clock (TXCK) may be gapped or stretched without the use of TXCKEN to accommodate overhead bit times. The set-up and hold times specified for TXCKEN must be met to ensure correct operation.

| Parameter                                | Symbol          | Min | Тур | Max | Unit |

|------------------------------------------|-----------------|-----|-----|-----|------|

| TXD output delay after TXBC $\downarrow$ | t <sub>OD</sub> |     |     | 5.0 | ns   |

| TSPF set-up time before TXCK↑            | t <sub>SU</sub> | 2.5 |     |     | ns   |

| TSPF hold time after TXCK1               | t <sub>H</sub>  | 2.5 |     |     | ns   |

| Parameter                                                                  | Symbol             | Min  | Тур | Мах | Unit |

|----------------------------------------------------------------------------|--------------------|------|-----|-----|------|

| A(3-0) set-up time before $\overline{RD}\downarrow$                        | t <sub>SU(2)</sub> | 10.0 |     |     | ns   |

| $\overline{\text{CS}}$ set-up time before $\overline{\text{RD}}\downarrow$ | t <sub>SU(1)</sub> | 5.0  |     |     | ns   |

| A(3-0) hold time after $\overline{RD}^{\uparrow}$                          | t <sub>H</sub>     | 10.0 |     |     | ns   |

| RD pulse width                                                             | t <sub>PW</sub>    | 38   |     |     | ns   |

| DATA output delay after $\overline{RD}\downarrow$                          | t <sub>OD</sub>    |      |     | 8.0 | ns   |

| DATA float time after $\overline{RD}$                                      | t <sub>F</sub>     |      |     | 2.0 | ns   |

| $\overline{\text{CS}}$ hold time after $\overline{\text{RD}}$              | t <sub>H(3)</sub>  | 5.0  |     |     | ns   |

Note: A minimum of 10 TXCK clock cycles must occur after power-up, before the read cycles will operate correctly.

| Parameter                                                                  | Symbol             | Min  | Тур | Мах | Unit |

|----------------------------------------------------------------------------|--------------------|------|-----|-----|------|

| A(3-0) set-up time before $\overline{WR}\downarrow$                        | t <sub>SU(2)</sub> | 10.0 |     |     | ns   |

| $\overline{\text{CS}}$ set-up time before $\overline{\text{WR}}\downarrow$ | t <sub>SU(1)</sub> | 5.0  |     |     | ns   |

| A(3-0) hold time after $\overline{WR}$                                     | t <sub>H(1)</sub>  | 10.0 |     |     | ns   |

| WR pulse width                                                             | t <sub>PW</sub>    | 38   |     |     | ns   |

| DATA set-up time before $\overline{WR}^\uparrow$                           | t <sub>SU(3)</sub> | 10.0 |     |     | ns   |

| DATA hold time after $\overline{WR}$ $\uparrow$                            | t <sub>H(2)</sub>  | 5.0  |     |     | ns   |

| $\overline{\text{CS}}$ hold time after $\overline{\text{WR}}$              | t <sub>H(3)</sub>  | 5.0  |     |     | ns   |

Note: A minimum of 10 TXCK clock cycles must occur after power-up, before the write cycles will operate correctly.

## OPERATION

#### DECOUPLING OF POWER SUPPLY PINS

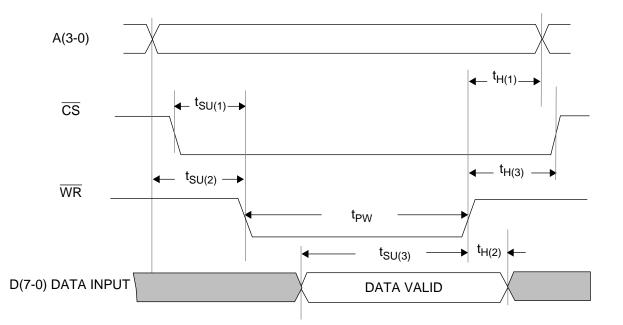

Each of the two +5 volt power supply pins of the XBERT device, pins 1 and 23, should be decoupled using a series inductor (ferrite bead) and capacitors that are effective at both low and high frequencies, as shown in Figure 12. These external components should be placed close to the pin, especially the lower-valued RF capacitor.

Notes:

1. Fair-Rite Products Part No. 2743002111, or equivalent, should be used for each ferrite bead (Walkill, NY, 914-895-2055).

2. All capacitor values are shown in microfarads.

#### Figure 12. Recommended Decoupling of Power Supply Pins

#### EXTERNAL CIRCUIT FOR PROPER UPDATING OF BIT ERROR AND CLOCK COUNTERS

Under certain combinations of microprocessor access and telecommunications usage, the Bit Error Counter (at memory map addresses 06H, 07H and 08H) and the Clock Counter (at memory map addresses 09H, 0AH and 0BH) may not be updated correctly by the XBERT device. Since it is not possible to specify all the combinations of conditions under which this incorrect operation can occur, it is recommended that users of the XBERT device should either contact the Applications Engineering Department at TranSwitch for advice on the susceptibility of their particular applications, or avoid any potential problems in their designs by employing the external circuit and special software precautions described below.

The two 24-bit counters are specially designed to record their event counts accurately even when the counters are being read by the microprocessor. The counters latch during a microprocessor read operation, and both counters must be read together by six read cycles performed on addresses 09H (first), 0AH, 0BH, 06H, 07H and 08H (last). The final reading of address 08H starts a state machine that transfers the counts synchronously with the receive clock. This transfer occurs upon the third ungapped receive clock after the rising edge of the RD input signal applied during the address 08H read access. However, the state machine is cleared from its update sequence upon the next microprocessor initiation of active RD or WR input signals, so correct update operation requires that one of these does not occur before the update has been processed, i.e., before three clock periods have elapsed. Incorrect operation will result in a failure to update the counters, which will appear to be stuck.

This problem may avoided by employing an external circuit and special software to ensure that the XBERT does not experience an active RD or WR input during the critical period of three clock cycles. The circuit shown in Figure 13 gates the read and write lines with the XBERT's chip select input to ensure that the XBERT does not see any read or write signals intended for other devices, which may occur during the critical period (the gate in the chip select line is intended only to equalize the gate delays on all three input pins so that the microprocessor read/write cycle timing diagrams of this Data Sheet are applicable without special adjustment for differences in the relative timing between RD or WR and CS). Read or write signals which are intended for the XBERT (i.e., those which are active when CS is low) must be programmed not to occur during the critical period. The hold-off time from reading address 08H to the next read or write of the group starting with address 09H must be arranged to be a minimum of:

[3 + (maximum number of successive read clock gaps)] x 1/(receive clock frequency)

For example, a T1 application requires the following hold-off time from accessing address 08H to accessing address 09H:

$[3 + (1 \text{ overhead bit time})] \times 1/1.544 \text{MHz} = 4 \times 0.666 = 2.664 \text{ microseconds (rounded up to 2.7)}.$

Figure 13. Protection of XBERT from Read/Write Signals Intended for other Devices

## **MEMORY MAP**

The XBERT memory map consists of register bit positions and counters, which may be accessed by a microprocessor for read and (except for counters) write cycles. The unused bit position at bit 3 of register 01H is a "don't care" bit, but it is recommended that it should be set to 0.

| Address<br>(Hex) | Mode* | Bit7                        | Bit6                            | Bit5 | Bit4        | Bit3         | Bit2  | Bit1  | Bit0  |

|------------------|-------|-----------------------------|---------------------------------|------|-------------|--------------|-------|-------|-------|

| 00               | R/W   | POLY                        | PROG                            | SEL1 | SEL0        | RESET        | INVTD | MODE1 | MODE0 |

| 01               | R/W   | ERR1                        | ERR0                            | SSE  | RESETC      | Unused       | TRLBK | TEST  | LOF   |

| 02               | R/W   |                             |                                 | F    | Programmabl | e Word, Byte | e 4   |       |       |

| 03               | R/W   |                             |                                 | F    | Programmabl | e Word, Byte | e 3   |       |       |

| 04               | R/W   |                             |                                 | F    | Programmabl | e Word, Byte | e 2   |       |       |

| 05               | R/W   |                             |                                 | F    | Programmabl | e Word, Byte | e 1   |       |       |

| 06               | R     |                             | Bit Error Counter (MS Byte)     |      |             |              |       |       |       |

| 07               | R     |                             | Bit Error Counter (Middle Byte) |      |             |              |       |       |       |

| 08               | R     |                             | Bit Error Counter (LS Byte)     |      |             |              |       |       |       |

| 09               | R     | Clock Counter (MS Byte)     |                                 |      |             |              |       |       |       |

| 0A               | R     | Clock Counter (Middle Byte) |                                 |      |             |              |       |       |       |

| 0B               | R     | Clock Counter (LS Byte)     |                                 |      |             |              |       |       |       |

\*Read/write (R/W); Read only (R).

# MEMORY MAP DESCRIPTIONS

| Address* | Bit              | Symbol                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     | Descri                                   | ption                                            |                                                                                                                 |  |

|----------|------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| 00       | 7<br>6<br>5<br>4 | POLY<br>PROG<br>SEL1<br>SEL0 | <b>Test Pattern Generator and Detector:</b> Bits 7 through 4 are used to select a test pattern according to the truth table shown below. The $2^{20}$ - 1 pseudo-random test pattern designator ZS stands for zero suppression. The $2^{20}$ - 1 with zero suppression is also defined as a QRSS signal. This test pattern is not supported in the byte mode. The test pattern is common for both generation and detection (including programmable words). For "in frame" and Loss Of Frame conditions please refer to the LOF bit description for Address 01H, bit 0. |                                                     |                                          |                                                  |                                                                                                                 |  |

|          |                  |                              | Polynomial<br>(POLY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Program<br>(PROG)                                   | Select 1<br>(SEL1)                       | Select 0<br>(SEL0)                               | Test<br>Pattern                                                                                                 |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 0                                        | 0                                                | 000000000                                                                                                       |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 0                                        | 1                                                | 111111111                                                                                                       |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 1                                        | 0                                                | 1010101010                                                                                                      |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 1                                        | 1                                                | 1100110011                                                                                                      |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                   | 0                                        | 0                                                | Byte 1 only                                                                                                     |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                   | 0                                        | 1                                                | Bytes 1 & 2                                                                                                     |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                   | 1                                        | 0                                                | Bytes 1,2 &3                                                                                                    |  |

|          |                  |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                   | 1                                        | 1                                                | Bytes 1, 2, 3 & 4                                                                                               |  |

|          |                  |                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 0                                        | 0                                                | 2 <sup>15</sup> - 1                                                                                             |  |

|          |                  |                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 0                                        | 1                                                | 2 <sup>20</sup> - 1(ZS)                                                                                         |  |

|          |                  |                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 1                                        | 0                                                | 2 <sup>20</sup> - 1                                                                                             |  |

|          |                  |                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                   | 1                                        | 1                                                | 2 <sup>23</sup> - 1                                                                                             |  |

|          | 3                | RESET                        | tion. This must the internal cou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | be followed to<br>nters, generato<br>to counters in | by writing a<br>ators, and d<br>the memo | zero into this<br>letectors, as<br>ry map. All R | written to this bit posi-<br>location. Reset clears<br>well as the control bits<br>X/W memory map bit<br>reset. |  |

|          | 2                | INVTD                        | <ul> <li>inverted for transmission. The data is inverted for the bit-serial, nibble-parallel, and byte-parallel interfaces.</li> <li><b>XBERT Interface Selection:</b> The XBERT transmit and receive interface is</li> </ul>                                                                                                                                                                                                                                                                                                                                          |                                                     |                                          |                                                  |                                                                                                                 |  |

|          | 1<br>0           | MODE1<br>MODE0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                                          |                                                  |                                                                                                                 |  |

|          |                  |                              | M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ODE1 M                                              | IODE0                                    | Interface S                                      | Selected                                                                                                        |  |

|          |                  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                   | 0                                        | Bit-se                                           | erial                                                                                                           |  |

|          |                  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                   | 1                                        | Nibble-p                                         |                                                                                                                 |  |

|          |                  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                   | 1                                        | Byte-pa                                          | arallel                                                                                                         |  |

\* Note: All addresses are shown in hexadecimal form.

| Address | Bit    | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |                                   |                                                                                                                          |          |