**Vishay Siliconix**

## Latchable Single 8-Ch/Differential 4-Ch Analog Multiplexers

#### DESCRIPTION

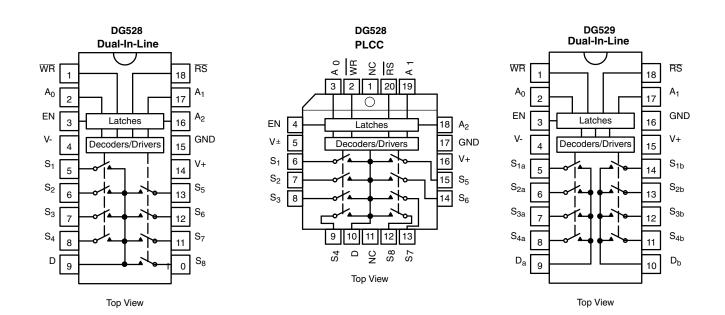

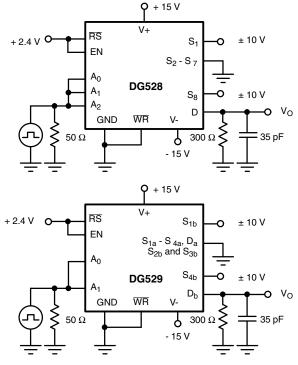

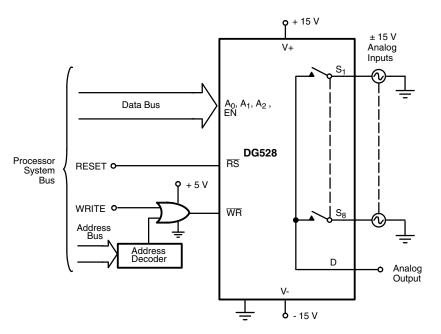

The DG528 is an 8-channel single-ended analog multiplexer designed to connect one of eight inputs to a common output as determined by a 3-bit binary address ( $A_0$ ,  $A_1$ ,  $A_2$ ). DG529, a 4-channel dual analog multiplexer, is designed to connect one of four differential inputs to a common differential output as determined by its 2-bit binary address ( $A_0$ ,  $A_1$ ) logic.

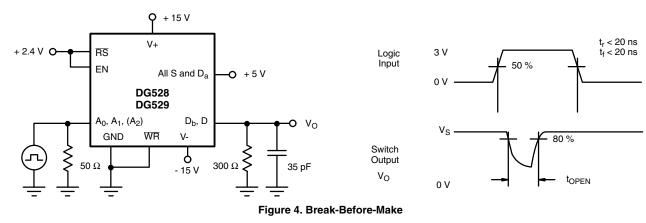

These analog multiplexers have on-chip address and control latches to simplify design in microprocessor based applications. Break-before-make switching action protects against momentary shorting of the input signals. The DG528/529 are built on the improved PLUS-40 CMOS process. A buried layer prevents latchup.

The on chip TTL-compatible address latches simplify digital interface design and reduce board space in data acquisition systems, process controls, avionics, and ATE.

#### **FEATURES**

- Low R<sub>DS(on)</sub>: 270 Ω

- 44 V Power Supply Rating

- On-Board Address Latches

- Break-Before-Make

- Low Leakage I<sub>D(on)</sub>: 30 pA

#### **BENEFITS**

- Improved System Accuracy

- Microporcessor Bus Compatible

- Easily Interfaced

- Reduced Crosstalk

#### **APPLICATIONS**

- Data Acquisition Systems

- Automatic Test Equipment

- · Avionics and Military Systems

- Medical Instrumentation

#### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

Document Number: 70068 S11-1029–Rev. D, 23-May-11 www.vishay.com

1

Vishay Siliconix

### TRUTH TABLES AND ORDERING INFORMATION

| TRUTH TABLE - DG528                |                       |                       |      |    |    |                                        |  |  |  |  |

|------------------------------------|-----------------------|-----------------------|------|----|----|----------------------------------------|--|--|--|--|

| 8-Channel Single-Ended Multiplexer |                       |                       |      |    |    |                                        |  |  |  |  |

| A <sub>2</sub>                     | <b>A</b> <sub>1</sub> | <b>A</b> <sub>0</sub> | EN   | WR | RS | On Switch                              |  |  |  |  |

| Latch                              | Latching              |                       |      |    |    |                                        |  |  |  |  |

| х                                  | х                     | х                     | х    |    | 1  | Maintains previous<br>switch condition |  |  |  |  |

| Reset                              | Reset                 |                       |      |    |    |                                        |  |  |  |  |

| Х                                  | Х                     | Х                     | Х    | Х  | 0  | None (latches cleared)                 |  |  |  |  |

| Trans                              | parent                | Opera                 | tion |    |    |                                        |  |  |  |  |

| Х                                  | Х                     | Х                     | 0    | 0  | 1  | None                                   |  |  |  |  |

| 0                                  | 0                     | 0                     | 1    | 0  | 1  | 1                                      |  |  |  |  |

| 0                                  | 0                     | 1                     | 1    | 0  | 1  | 2                                      |  |  |  |  |

| 0                                  | 1                     | 0                     | 1    | 0  | 1  | 3                                      |  |  |  |  |

| 0                                  | 1                     | 1                     | 1    | 0  | 1  | 4                                      |  |  |  |  |

| 1                                  | 0                     | 0                     | 1    | 0  | 1  | 5                                      |  |  |  |  |

| 1                                  | 0                     | 1                     | 1    | 0  | 1  | 6                                      |  |  |  |  |

| 1                                  | 1                     | 0                     | 1    | 0  | 1  | 7                                      |  |  |  |  |

| 1                                  | 1                     | 1                     | 1    | 0  | 1  | 8                                      |  |  |  |  |

| <b>ORDERING INFORMATION - DG528</b> |                    |                |  |  |  |  |  |

|-------------------------------------|--------------------|----------------|--|--|--|--|--|

| Temp Range                          | Package            | Part Number    |  |  |  |  |  |

| 0 °C to 70 °C                       | 18-pin Plastic DIP | DG528CJ        |  |  |  |  |  |

| 0 0 10 70 0                         | 20-pin PLCC        | DG528DN        |  |  |  |  |  |

| - 25 °C to 85 °C                    |                    | DG528BK        |  |  |  |  |  |

|                                     | 18-pin Cer DIP     | DG528AK        |  |  |  |  |  |

| - 55 °C to 125 °C                   | ro-pin Ger DIP     | DG528AK/883    |  |  |  |  |  |

|                                     |                    | 5962-8768901VA |  |  |  |  |  |

| TRUTH TABLE - DG529                       |                    |        |   |                        |  |  |  |  |  |

|-------------------------------------------|--------------------|--------|---|------------------------|--|--|--|--|--|

| Differential 4-Channel Multiplexer        |                    |        |   |                        |  |  |  |  |  |

| A <sub>0</sub>                            | EN WR RS On Switch |        |   |                        |  |  |  |  |  |

| Latching                                  |                    |        |   |                        |  |  |  |  |  |

| X X 1 Maintains previous switch condition |                    |        |   |                        |  |  |  |  |  |

| Reset                                     | Reset              |        |   |                        |  |  |  |  |  |

| Х                                         | Х                  | Х      | 0 | None (latches cleared) |  |  |  |  |  |

| Transpa                                   | rent Ope           | ration | • |                        |  |  |  |  |  |

| Х                                         | 0                  | 0      | 1 | None                   |  |  |  |  |  |

| 0                                         | 1                  | 0      | 1 | 1                      |  |  |  |  |  |

| 1                                         | 1                  | 0      | 1 | 2                      |  |  |  |  |  |

| 0                                         | 1                  | 0      | 1 | 3                      |  |  |  |  |  |

| 1                                         | 1                  | 0      | 1 | 4                      |  |  |  |  |  |

| _ogic "0" = $V_{AL} \le 0.8 \text{ V}$    |                    |        |   |                        |  |  |  |  |  |

Logic "1" =  $V_{AL} \ge 0.6$  V Logic "1" =  $V_{AH} \ge 2.4$  V

X = Don't Care

ORDERING INFORMATION - DG529

Temp Range

Package

Part Number

0 °C to 70 °C

18-pin Plastic DIP

DG529CJ

- 25 °C to 85 °C

18-pin Cer DIP

DG529BK

- 55 °C to 125 °C

18-pin Cer DIP

DG529AK/883

| ABSOLUTE MAXIMUM RATINGS                                      |                                 |        |                                                          |      |  |  |

|---------------------------------------------------------------|---------------------------------|--------|----------------------------------------------------------|------|--|--|

| Parameter                                                     |                                 | Symbol | Limit                                                    | Unit |  |  |

| Valtages Deferenced to V                                      | V+                              |        | 44                                                       |      |  |  |

| Voltages Referenced to V-                                     | GND                             |        | 25                                                       |      |  |  |

| Digital Inputs <sup>a</sup> , V <sub>S</sub> , V <sub>D</sub> |                                 |        | (V-) - 2 to (V+) + 2<br>or 30 mA, whichever occurs first |      |  |  |

| Current (Any Terminal Except S                                | S or D)                         |        | 30                                                       |      |  |  |

| Continuous Current, S or D                                    |                                 |        | 20                                                       | mA   |  |  |

| Peak Current, S or D (Pulsed at 1 ms, 10 % duty cycle max)    |                                 |        | 40                                                       |      |  |  |

| Storogo Tomporaturo                                           | (AK, BK Suffix)                 |        | - 65 to 150                                              | ℃    |  |  |

| Storage Temperature                                           | (CJ, DN Suffix)                 |        | - 65 to 125                                              | U    |  |  |

|                                                               | 18-pin Plastic DIP <sup>c</sup> |        | 470                                                      |      |  |  |

| Power Dissipation (Package) <sup>b</sup>                      | 18-pin CerDIP <sup>d</sup>      |        | 900                                                      | mW   |  |  |

|                                                               | 20-pin PLCC <sup>e</sup>        |        | 800                                                      |      |  |  |

Notes:

a. Signals on S<sub>X</sub>, D<sub>X</sub> or IN<sub>X</sub> exceeding V+ or V- will be clamped by internal diodes. Limit forward diode current to maximum current ratings.

b. All leads soldered or welded to PC board.

c. Derate 6.3 mW/°C above 75 °C.

d. Derate 12 mW/°C above 75 °C.

e. Derate 10 mW/°C above 75 °C.

www.vishay.com 2 Document Number: 70068 S11-1029–Rev. D, 23-May-11

# DG528, DG529

**Vishay Siliconix**

| SPECIFICATIONS <sup>a</sup>                                             |                         |                                                                                  |               |                    |                   |                   |                    |                           |                             |      |

|-------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------|---------------|--------------------|-------------------|-------------------|--------------------|---------------------------|-----------------------------|------|

|                                                                         |                         | Test Conditions<br>Unless Otherwise Specified<br>V+ = 15 V, V- = - 15 V, WR = 0, |               |                    |                   |                   | uffix<br>to 125 °C | <b>B, C, I</b><br>- 40 °C | <b>) Suffix</b><br>to 85 °C |      |

| Parameter                                                               | Symbol                  | $\overline{RS} = 2.4 \text{ V}, \text{ V}_{IN} = 2.4 \text{ V}, 0$               |               | Temp. <sup>b</sup> | Typ. <sup>c</sup> | Min. <sup>d</sup> | Max. <sup>d</sup>  | Min. <sup>d</sup>         | Max. <sup>d</sup>           | Unit |

| Analog Switch                                                           |                         |                                                                                  |               |                    |                   |                   |                    |                           |                             |      |

| Analog Signal Range <sup>e</sup>                                        | V <sub>ANALOG</sub>     |                                                                                  |               | Full               |                   | - 15              | 15                 | - 15                      | 15                          | V    |

| Drain-Source<br>On-Resistance                                           | R <sub>DS(on)</sub>     | $V_{D} = \pm 10 \text{ V}, \text{ I}_{S} = -200$                                 | μA            | Room<br>Full       | 270               |                   | 400<br>500         |                           | 450<br>550                  | Ω    |

| Greatest Change in R <sub>DS(on)</sub><br>Between Channels <sup>f</sup> | $\Delta R_{DS(on)}$     | - 10 V < V <sub>S</sub> < 10 V                                                   |               | Room               | 6                 |                   |                    |                           |                             | %    |

| Source Off Leakage Current                                              | I <sub>S(off)</sub>     | $V_{EN} = 0 V, V_{D} = \pm 10$<br>$V_{S} = \pm 10 V$                             | V             | Room<br>Full       | ± 005             | - 1<br>- 50       | 1<br>50            | - 5<br>- 50               | 5<br>50                     |      |

| Drain Off Leakage Current                                               | I <sub>D(off)</sub>     | $V_{EN} = 0 V, V_{D} = \pm 10 V$                                                 | DG528         | Room<br>Full       | ± 0.015           | - 10<br>- 200     | 10<br>200          | - 20<br>- 200             | 20<br>200                   |      |

|                                                                         | D(011)                  | $V_{S} = \pm 10 V$                                                               | DG529         | Room<br>Full       | ± 0.008           | - 10<br>- 100     | 10<br>100          | - 20<br>- 100             | 20<br>100                   | nA   |

| Drain On Leakage Current                                                |                         | $V_{\rm S} = V_{\rm D} = \pm 10$ V                                               | DG528         | Room<br>Full       | ± 0.03            | - 10<br>- 200     | 10<br>200          | - 20<br>- 200             | 20<br>200                   |      |

| Dialition Leakage outletic                                              | I <sub>D(on)</sub>      | $V_{EN} = 2.4 V$                                                                 | DG529         | Room<br>Full       | ± 0.015           | - 10<br>- 100     | 10<br>100          | - 20<br>- 100             | 20<br>100                   |      |

| Digital Control                                                         |                         |                                                                                  |               |                    |                   |                   |                    |                           |                             |      |

| Logic Input Current                                                     | – I <sub>AH</sub> –     | V <sub>A</sub> = 2.4 V<br>V <sub>A</sub> = 15 V                                  |               | Room<br>Hot        | - 0.002           | - 10<br>- 30      |                    | - 10<br>- 30              |                             | μΑ   |

| Input Voltage High                                                      | 'AH                     |                                                                                  |               | Room<br>Hot        | 0.006             |                   | 10<br>30           |                           | 10<br>30                    |      |

| Logic Input Current<br>Input Voltage Low                                | I <sub>AL</sub>         | V <sub>EN</sub> = 0 V, 2.4 V, V <sub>A</sub> = 0 V<br>RS = 0 V, WR = 0 V         |               | Room<br>Hot        | - 0.002           | - 10<br>- 30      |                    | - 10<br>- 30              |                             |      |

| Dynamic Characteristics                                                 | -1 - L                  |                                                                                  |               |                    |                   | •                 |                    | •                         | <u></u>                     |      |

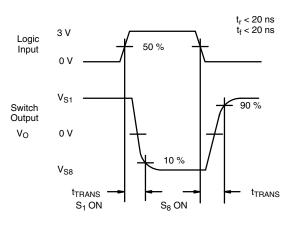

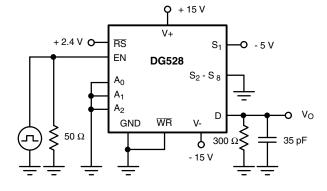

| Transition Time                                                         | t <sub>TRANS</sub>      | See Figure 5                                                                     |               | Room               | 0.6               |                   | 1                  |                           |                             |      |

| Break-Before-Make Interval                                              | t <sub>OPEN</sub>       | See Figure 4                                                                     |               | Room               | 0.2               |                   |                    |                           |                             |      |

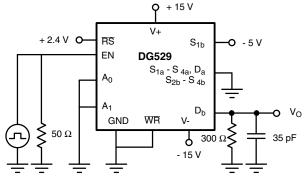

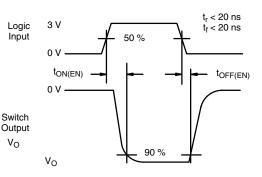

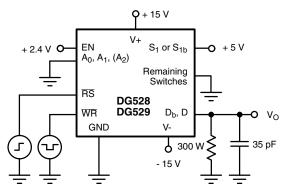

| EN and WR Turn-On Time                                                  | t <sub>ON(EN,WR)</sub>  | See Figure 6 and 7                                                               |               | Room               | 1                 |                   | 1.5                |                           |                             | μs   |

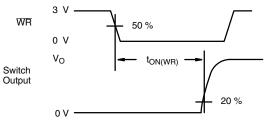

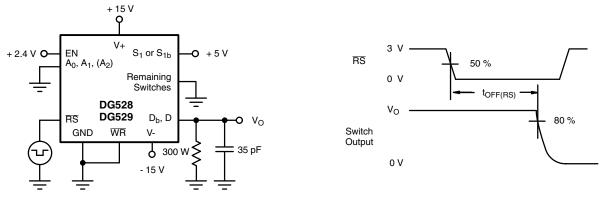

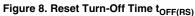

| EN and WR Turn-Off Time                                                 | t <sub>OFF(EN,RS)</sub> | See Figure 6 and 8                                                               |               | Room               | 0.4               |                   | 1                  |                           |                             |      |

| Charge Injection                                                        | Q                       | $V_{S} = 0 V, R_{V} = 0 \Omega, C_{L} = 100$                                     | 10 μF         | Room               | 4                 |                   |                    |                           |                             | рС   |

| Off Isolation                                                           | OIRR                    | $V_{EN} = 0 V, R_L = 1 k\Omega, C_L = V_S = 7 V_{RMS}, f = 500 k$                | ⊧ 15 pF<br>Hz | Room               | 68                |                   |                    |                           |                             | dB   |

| Logic Imput Capacitance                                                 | C <sub>in</sub>         | f = 1 MHz                                                                        |               | Room               | 2.5               |                   |                    |                           |                             |      |

| Source Off Capacitance                                                  | C <sub>S(off)</sub>     | $V_{EN} = 0 V, V_{D} = 0 V, f = 14$                                              | l0 kHz        | Room               | 5                 |                   |                    |                           |                             | _    |

|                                                                         |                         | V <sub>EN</sub> = 0 V, V <sub>D</sub> = 0 V                                      | DG528         | Room               | 25                |                   |                    |                           |                             | pF   |

| Drain Off Capacitance                                                   | C <sub>D(off)</sub>     | f = 140 kHz                                                                      | DG529         | Room               | 12                |                   |                    |                           |                             |      |

| Minimum Input Timing Requ                                               | uirements               |                                                                                  |               |                    |                   |                   | 1                  |                           | I                           | 1    |

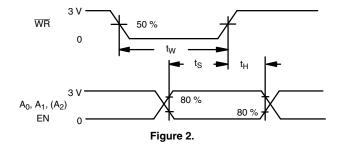

| Write Pulse Width                                                       | t <sub>W</sub>          |                                                                                  |               | Full               |                   | 300               |                    | 300                       |                             |      |

| A <sub>X</sub> , EN Data Set Up time                                    | t <sub>S</sub>          |                                                                                  |               | Full               |                   | 180               |                    | 180                       |                             | ns   |

| A <sub>X</sub> , EN Data Hold Time                                      | t <sub>H</sub>          |                                                                                  |               | Full               |                   | 30                |                    | 30                        |                             |      |

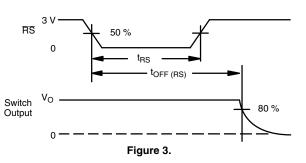

| Reset Pulse Width                                                       | t <sub>RS</sub>         | V <sub>S</sub> = 5 V, See Figure 3                                               |               | Full               |                   | 500               |                    | 500                       |                             |      |

| Power Supplies                                                          |                         |                                                                                  |               |                    |                   |                   |                    |                           |                             |      |

| Positive Supply Current                                                 |                         |                                                                                  | Room          |                    |                   | 2.5               |                    | 2.5                       | mA                          |      |

| Negative Supply Current                                                 | I-                      |                                                                                  |               | Room               |                   | - 1.5             |                    | - 1.5                     |                             |      |

Notes:

a. Refer to PROCESS OPTION FLOWCHART.

b. Room = 25  $^{\circ}$ C, Full = as determined by the operating temperature suffix.

c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

d. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

e. Guaranteed by design, not subject to production test.

f.  $V_{IN}$  = input voltage to perform proper function.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Vishay Siliconix

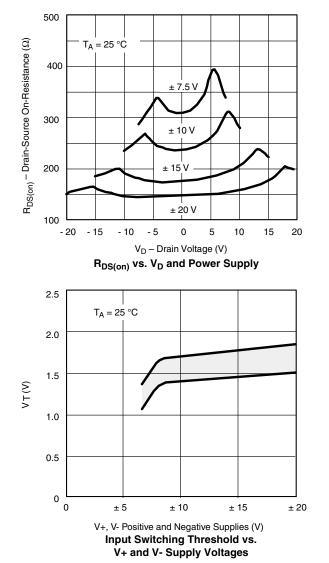

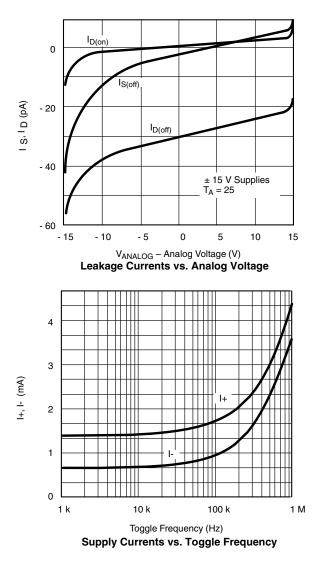

## **TYPICAL CHARACTERISTICS** (T<sub>A</sub> = 25 °C, unless noted)

www.vishay.com

4

Document Number: 70068 S11-1029–Rev. D, 23-May-11

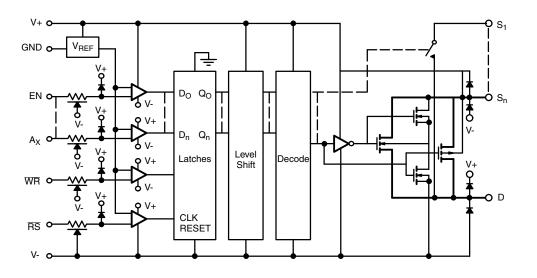

#### SCHEMATIC DIAGRAM (TYPICAL CHANNEL)

#### Figure 1.

#### **DETAILED DESCRIPTION**

The internal structure of the DG528/DG529 includes a 5-V logic interface with input protection circuitry followed by a latch, level shifter, decoder and finally the switch constructed with parallel n- and p-channel MOSFETs (see Figure 1).

The logic interface circuit compares the TTL input signal against a TTL threshold reference voltage. The output of the comparator feeds the data input of a D type latch. The level sensitive D latch continuously places the D<sub>X</sub> input signal on the Q<sub>X</sub> output when the WR input is low, resulting in transparent latch operation. As soon as WR returns high, the latches hold the data last present on the D<sub>X</sub> input, subject to the minimum input timing requirements.

Following the latches the  $Q_X$  signals are level shifted and decoded to provide proper drive levels for the CMOS switches. This level shifting insures full on/off switch operation for any analog signal present between the V+ and V- supply rails.

The EN pin is used to enable the address latches during the  $\overline{\text{WR}}$  pulse. It can be hard-wired to the logic supply or to V+ if one of the channels will always be used (except during a reset) or it can be tied to address decoding circuitry for memory mapped operation. The  $\overline{\text{RS}}$  pin is used as a master reset. All latches are cleared regardless of the state of any other latch or control line. The  $\overline{\text{WR}}$  pin is used to transfer the state of the address control lines to their latches, except during a reset or when EN is low (see Truth Tables).

Document Number: 70068 S11-1029–Rev. D, 23-May-11

# DG528, DG529

Vishay Siliconix

### **TEST CIRCUITS**

Figure 5. Transition Time

Document Number: 70068 S11-1029–Rev. D, 23-May-11

#### **TEST CIRCUITS**

Figure 6. Enable t<sub>ON/tOFF</sub> Time

Figure 7. Write Turn-On Time t<sub>ON(WR)</sub>

Document Number: 70068 S11-1029–Rev. D, 23-May-11

www.vishay.com 7

# DG528, DG529

Vishay Siliconix

### **TEST CIRCUITS**

Figure 9. Bus Interface

www.vishay.com 8 **VISHAY**

| APPLICATION HINTS <sup>a</sup>       |                                      |                                                                                            |                                                                 |  |  |  |  |

|--------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| V+<br>Positive Supply Voltage<br>(V) | V-<br>Negative Supply Voltage<br>(V) | V <sub>IN</sub><br>Logic Input Voltage V <sub>INH(min)</sub> /V <sub>INL(max)</sub><br>(V) | V <sub>S</sub> or V <sub>D</sub><br>Analog Voltage Range<br>(V) |  |  |  |  |

| 20                                   | - 20                                 | 2.4/0.8                                                                                    | ± 20                                                            |  |  |  |  |

| 15 <sup>b</sup>                      | - 15                                 | 2.4/0.8                                                                                    | ± 15                                                            |  |  |  |  |

| 8 <sup>c</sup>                       | - 8 (min)                            | 2.4/0.8                                                                                    | ± 8                                                             |  |  |  |  |

| Notes:                               |                                      |                                                                                            |                                                                 |  |  |  |  |

a. Application Hints are for DESIGN AID ONLY, not guaranteed and not subject to production testing. b. Electrical Parameter Chart based on V+ = 15 V, V- = - 15 V, V<sub>R</sub> = GND. c. Operation below  $\pm$  8 V is not recommended.

The DG528/DG529 minimize the amount of interface hardware between a microprocessor system bus and the analog system being controlled or measured. The internal TTL compatible latches give these multiplexers write-only memory, that is, they can be programmed to stay in a particular switch state (e.g., switch 1 on) until the microprocessor determines it is necessary to turn different switches on or turn all switches off (see Figure 9).

The input latches become transparent when  $\overline{WR}$  is held low; therefore, these multiplexers operate by direct command of the coded switch state on  $A_2$ ,  $A_1$ ,  $A_0$ . In this mode the DG528 is identical to the popular DG508A. The same is true of the DG529 versus the popular DG509A.

During system power-up, RS would be low, maintaining all eight switches in the off state. After RS returned high the DG528 maintains all switches in the off state. When the system program performs a write operation to the address assigned to the DG528, the address decoder provides a  $\overline{CS}$ active low signal which is gated with the WRITE (WR) control signal. At this time the data on the DATA BUS (that will determine which switch to close) is stabilizing. When the  $\overline{WR}$  signal returns to the high state, (positive edge) the input latches of the DG528 save the data from the DATA BUS. The coded information in the A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub> and EN latches is decoded and the appropriate switch is turned on.

The EN latch allows all switches to be turned off under program control. This becomes useful when two or more DG528s are cascaded to build 16-line and larger multiplexers.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?70068.

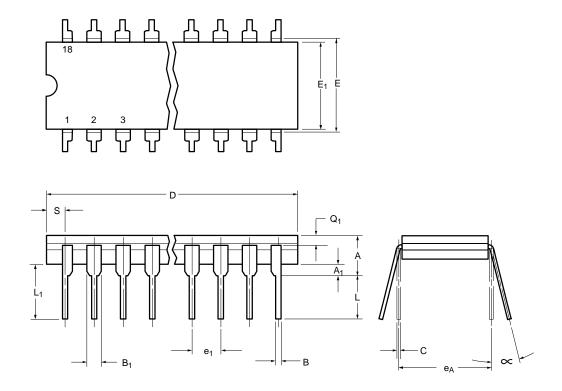

### CERDIP: 18-LEAD

|                                             | MILLIM | ETERS | INC       | HES   |  |  |  |

|---------------------------------------------|--------|-------|-----------|-------|--|--|--|

| Dim                                         | Min    | Max   | Min       | Max   |  |  |  |

| Α                                           | 4.06   | 5.08  | 0.160     | 0.200 |  |  |  |

| A <sub>1</sub>                              | 0.51   | 1.14  | 0.020     | 0.045 |  |  |  |

| В                                           | 0.38   | 0.51  | 0.015     | 0.020 |  |  |  |

| B <sub>1</sub>                              | 1.14   | 1.65  | 0.045     | 0.065 |  |  |  |

| С                                           | 0.20   | 0.30  | 0.008     | 0.012 |  |  |  |

| D                                           | 22.35  | 22.86 | 0.880     | 0.900 |  |  |  |

| E                                           | 7.62   | 8.26  | 0.300     | 0.325 |  |  |  |

| E <sub>1</sub>                              | 6.60   | 7.62  | 0.260     | 0.300 |  |  |  |

| e <sub>1</sub>                              | 2.54   | BSC   | 0.100 BSC |       |  |  |  |

| e <sub>A</sub>                              | 7.62   | BSC   | 0.300     | BSC   |  |  |  |

| L                                           | 3.18   | 3.81  | 0.125     | 0.150 |  |  |  |

| L <sub>1</sub>                              | 3.81   | 5.08  | 0.150     | 0.200 |  |  |  |

| Q <sub>1</sub>                              | 1.27   | 2.16  | 0.050     | 0.085 |  |  |  |

| S                                           | 0.76   | 1.52  | 0.030     | 0.060 |  |  |  |

| ~                                           | 0°     | 15°   | 0°        | 15°   |  |  |  |

| ECN: S-03946—Rev. D, 09-Jul-01<br>DWG: 5313 |        |       |           |       |  |  |  |

## Package Information Vishay Siliconix

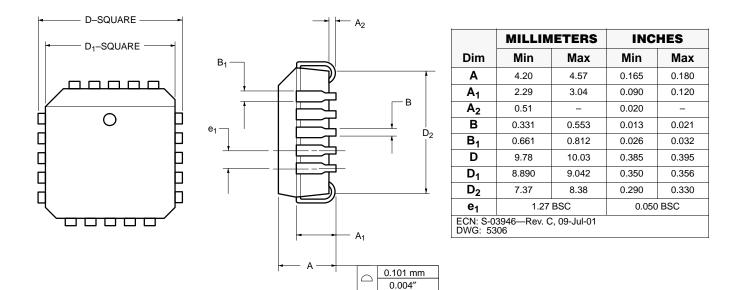

### PLCC: 20-LEAD

Vishay

## Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.