# UDN-6540B 8-CHANNEL DMOS HIGH-VOLTAGE DRIVER

#### **FEATURES**

- 200 V Outputs

- CMOS, PMOS Compatible

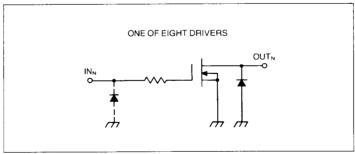

- Internal Gate Limiting Resistors

- Diode Clamped Inputs and Outputs

- Improved Output SOA

The UDN-6540B is an eight-channel high-voltage DMOS driver capable of sinking 200 mA and maintaining an output OFF voltage of 200 V. This device has many possible applications such as driving piezoelectric elements, gas-discharge or electroluminescent displays, and other high-voltage power loads. This device is input compatible with 7-20 V logic such as PMOS, CMOS, and high-voltage open collector TTL.

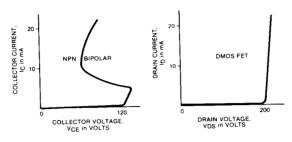

Because DMOS outputs have output SOA superior to that of conventional bipolar technologies, the UDN-6540B is ideal for inductive load applications. Unlike NPN transistors, DMOS devices can operate safely to their breakdown voltage limit without risk of secondary breakdown (latch-back) or sacrifice of reliability.

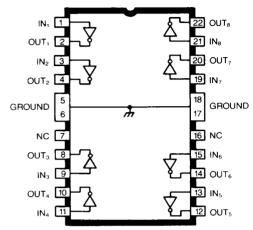

Dwg. No. W-103

The UDN-6540B is furnished in a 22-pin dual inline package with 0.400" row centers and sink contact tabs. A copper-alloy lead frame provides maximum power dissipation using standard cooling methods. This lead configuration facilitates attachment of external heat-sinks for increased power dissipation with standard IC sockets and printed wiring boards.

Dwg. No. W-104

### **ABSOLUTE MAXIMUM RATINGS** at +25°C Free-Air Temperature

| Output Voltage, V <sub>DS</sub>   | 200 V             |

|-----------------------------------|-------------------|

| Input Voltage, V <sub>IN</sub>    | 20V               |

| Output Current, IouT              | 250 mA            |

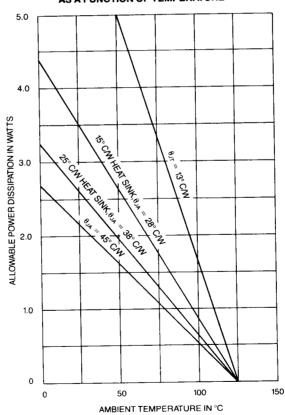

| Power Dissipation, P <sub>D</sub> | See Graph         |

| Storage Temperature Range         | ~ 55°C to + 150°C |

| Operating Temperature Range Ta    | - 20°C to + 85°C  |

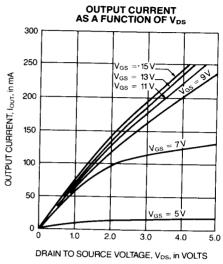

Dwg. No. W-169

## ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$

|                                         | Symbol              | Test Conditions                                                     |          | Limits |       |  |

|-----------------------------------------|---------------------|---------------------------------------------------------------------|----------|--------|-------|--|

| Characteristics                         |                     |                                                                     |          | Max.   | Units |  |

| Output Leakage Current                  | Ipss                | V <sub>DS</sub> = 200 V, Gate Shorted to Source                     |          | 10     | μA    |  |

| Drain to Source<br>ON Voltage           | V <sub>DS(ON)</sub> | $V_{GS} = 10 V$ , $I_{OUT} = 100 \text{ mA}$                        | <u> </u> | 2.5    | V     |  |

|                                         |                     | $V_{GS} = 10 V$ , $I_{OUT} = 200 \text{ mA}$                        |          | 5.0    | ٧     |  |

|                                         |                     | $V_{GS} = 15V$ , $I_{OUT} = 200 \text{ mA}$                         | _        | 4.0    | V     |  |

| Input Threshold Voitage V <sub>TH</sub> | V <sub>TH</sub>     | $I_{OUT} = 10 \text{ mA}, V_{DS} = 0.5 \text{ V}$                   |          | 7.0    | V     |  |

|                                         |                     | $I_{OUT} = 50 \text{ mA}, V_{DS} = 1.0 \text{ V}$                   | _        | 8.5    | V     |  |

| Turn-On Delay                           | ton                 | $0.5E_{IN}$ to $0.5E_{OUT}$ , $R_L = 1 k\Omega$ , $V_{OUT} = 200 V$ | _        | 0.5    | μS    |  |

| Turn-Off Delay                          | toff                | $0.5E_{IN}$ to $0.5E_{OUT}$ , $R_L=1$ k $\Omega$ , $V_{OUT}=200$ V  | _        | 0.5    | μS    |  |

# **BREAKDOWN CHARACTERISTICS**

Dwg. No. SD-113

# ALLOWABLE AVERAGE PACKAGE POWER DISSIPATION AS A FUNCTION OF TEMPERATURE

Dwg. No. W-105