### INTEGRATED CIRCUITS

# DATA SHEET

# SAA5360; SAA5361 Multi page intelligent teletext decoder

Product specification Supersedes data of 2005 Jan 25 2005 Mar 09

# Multi page intelligent teletext decoder

**SAA5360; SAA5361**

| CONTENT                                  | rs                                                                                                   | 13           | PACKAGE OUTLINE                                                                |

|------------------------------------------|------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------|

| 1                                        | FEATURES                                                                                             | 14           | SOLDERING                                                                      |

| 2                                        | GENERAL DESCRIPTION                                                                                  | 14.1         | Introduction to soldering surface mount packages                               |

| 3                                        | QUICK REFERENCE DATA                                                                                 | 14.2         | Reflow soldering                                                               |

| 4                                        | ORDERING INFORMATION                                                                                 | 14.3         | Wave soldering                                                                 |

| 5                                        | BLOCK DIAGRAM                                                                                        | 14.4<br>14.5 | Manual soldering                                                               |

| 6                                        | PINNING                                                                                              | 14.5         | Suitability of surface mount IC packages for wave and reflow soldering methods |

| 6.1                                      | Type SAA5360                                                                                         | 15           | DATA SHEET STATUS                                                              |

| 6.2                                      | Type SAA5361                                                                                         | 16           | DEFINITIONS                                                                    |

| 7                                        | COMMANDS AND CHARACTER SETS                                                                          | 17           | DISCLAIMERS                                                                    |

| 7.1<br>7.2                               | High-level command interface<br>Character sets                                                       | 18           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                |

| 8                                        | LIMITING VALUES                                                                                      |              |                                                                                |

| 9                                        | THERMAL CHARACTERISTICS                                                                              |              |                                                                                |

| 10                                       | QUALITY AND RELIABILITY                                                                              |              |                                                                                |

| 11                                       | CHARACTERISTICS                                                                                      |              |                                                                                |

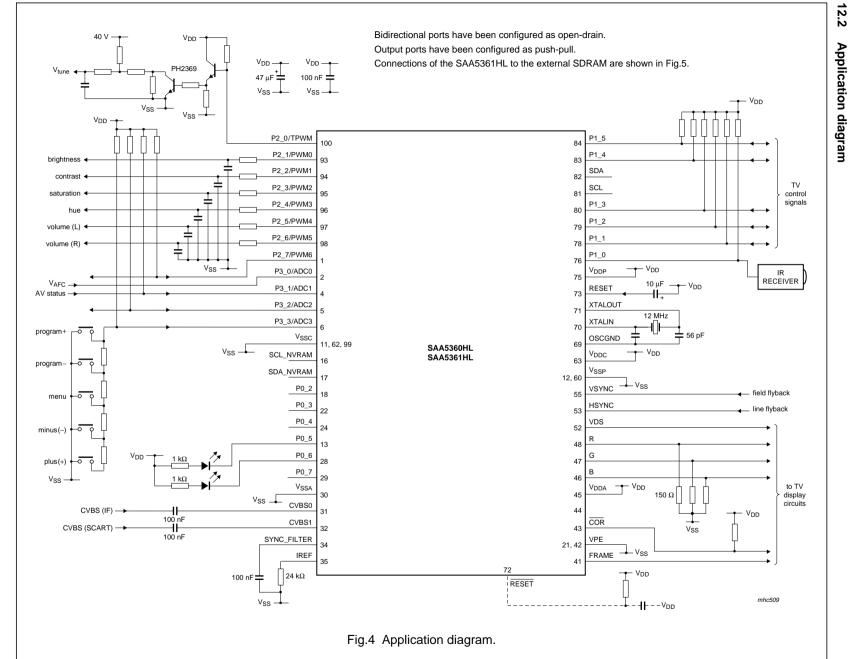

| 12                                       | APPLICATION INFORMATION                                                                              |              |                                                                                |

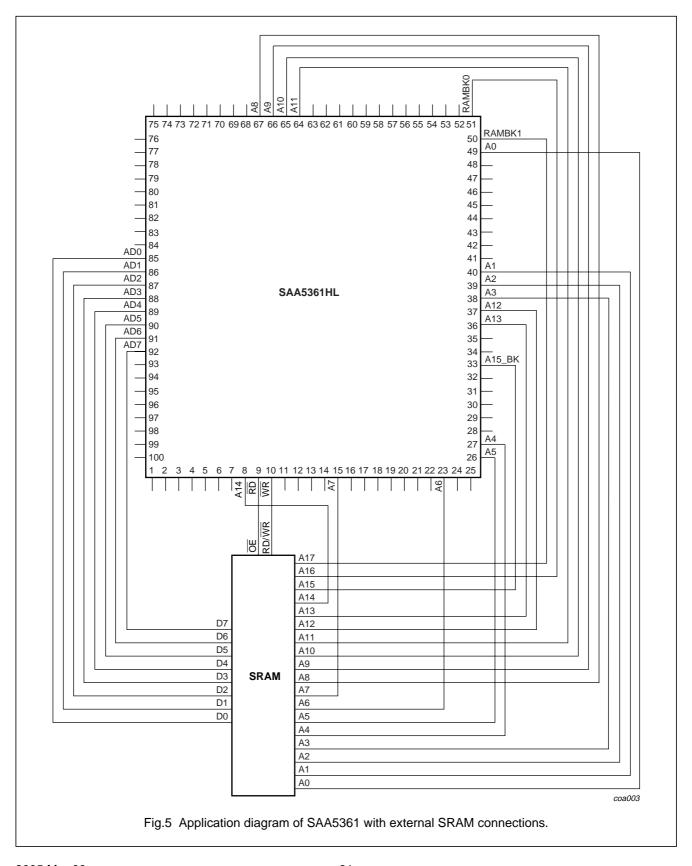

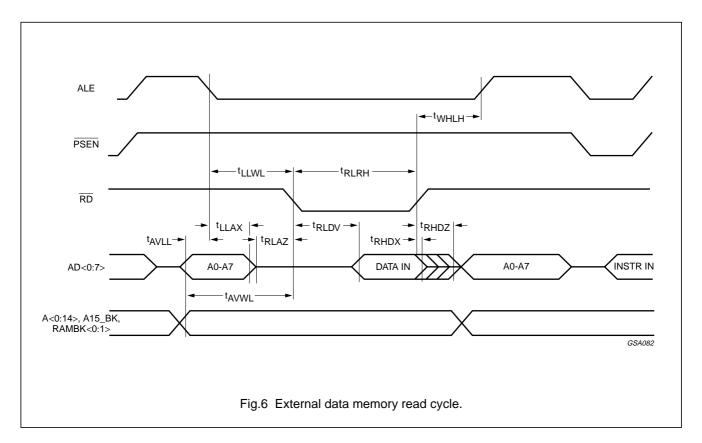

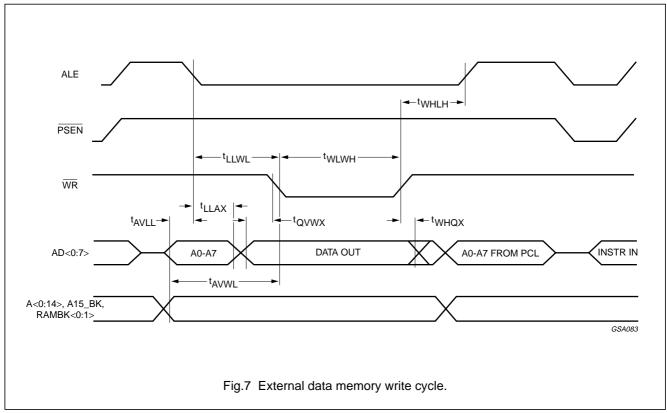

| 12.1<br>12.2<br>12.3<br>12.3.1<br>12.3.2 | EMC guidelines Application diagram Application notes External data memory access Symbol explanations |              |                                                                                |

### Multi page intelligent teletext decoder

SAA5360; SAA5361

#### 1 FEATURES

- Support for 50 or 60 and 100 or 120 Hz and progressive scan display modes

- Complete 625 line teletext decoder in one chip reduces printed-circuit board area and cost

- Automatic detection of transmitted fastext links or service information (packet 8/30)

- On-Screen Display (OSD) for user interface menus using teletext and dedicated menu icons

- · Video Programming System (VPS) decoding

- Wide Screen Signalling (WSS) decoding

- SAA5360 supports Pan-European, Arabic and Iranian character sets

- SAA5361 supports Pan-European, Cyrillic, Greek and Arabic character sets

- High-level command interface via I<sup>2</sup>C-bus gives easy control with a low software overhead

- High-level command interface is backward compatible to Stand-Alone Fastext And Remote Interface (SAFARI)

- 625 and 525 line display

- RGB interface to standard colour decoder ICs; current source

- Versatile 8-bit open-drain Input/Output (I/O) expander;

5 V tolerant

- Single 12 MHz crystal oscillator

- Single power supply: from 3.0 V to 3.6 V

- Operating temperature: –20 to +70 °C

- Automatic detection of transmitted pages to be selected by page up and page down

- 8 page fastext decoder

- Table Of Pages (TOP) decoder with Basic Top Table (BTT) and Additional Information Tables (AITs)

- · 4 page user-defined list mode.

### 2 GENERAL DESCRIPTION

The SAA5360; SAA5361 is a single-chip multi page 625 line world system teletext decoder with a high-level command interface, and is SAFARI compatible.

The device is designed to minimize the overall system cost, due to the high-level command interface offering the benefit of a low software overhead in the TV microcontroller.

The SAA5360 incorporates the following functions:

- 10 page teletext decoder with OSD, fastext, TOP, default and list acquisition modes

- · Automatic channel installation support.

The functionality of the SAA5361 is similar to the SAA5360, but offers the capability to store up to 250 additional pages of teletext in an external SRAM.

#### 3 QUICK REFERENCE DATA

| SYMBOL                 | PARAMETER                 | CONDITIONS                    | MIN. | TYP. | MAX. | UNIT |

|------------------------|---------------------------|-------------------------------|------|------|------|------|

| $V_{DD}$               | all supply voltages       | referenced to V <sub>SS</sub> | 3.0  | 3.3  | 3.6  | ٧    |

| I <sub>DDP</sub>       | periphery supply current  | note 1                        | 1    | _    | _    | mA   |

| I <sub>DDC</sub>       | core supply current       | normal mode                   | _    | 15   | 18   | mA   |

|                        |                           | idle mode                     | _    | 4.6  | 6    | mA   |

| I <sub>DDA</sub>       | analog supply current     | normal mode                   | _    | 45   | 48   | mA   |

|                        |                           | idle mode                     | _    | 0.87 | 1    | mA   |

| f <sub>xtal(nom)</sub> | nominal crystal frequency | fundamental mode              | _    | 12   | _    | MHz  |

| T <sub>amb</sub>       | ambient temperature       |                               | -20  | _    | +70  | °C   |

| T <sub>stg</sub>       | storage temperature       |                               | -55  | _    | +125 | °C   |

#### Note

1. Periphery supply current is dependent on external components and I/O voltage levels.

### Multi page intelligent teletext decoder

SAA5360; SAA5361

### 4 ORDERING INFORMATION

| TYPE NUMBER  |         | PACKAGE                                                                             |          |  |  |  |  |

|--------------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|--|

| I TPE NOWBER | NAME    | DESCRIPTION                                                                         | VERSION  |  |  |  |  |

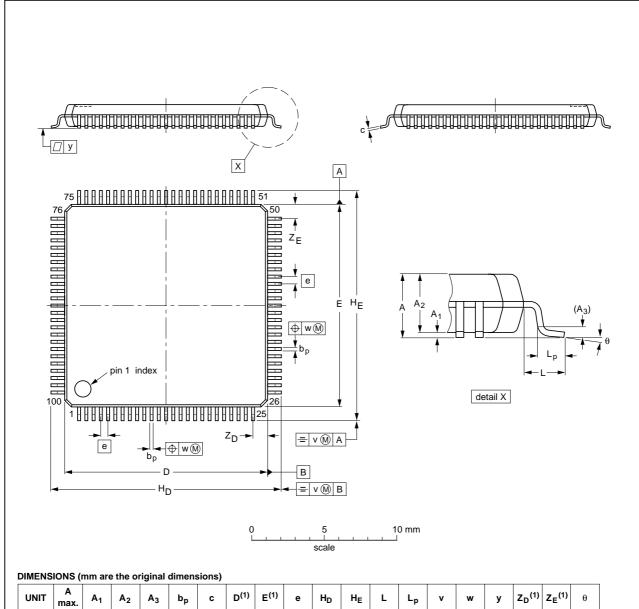

| SAA5360HL    | LQFP100 | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm | SOT407-1 |  |  |  |  |

| SAA5361HL    | LQFP100 | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm | SOT407-1 |  |  |  |  |

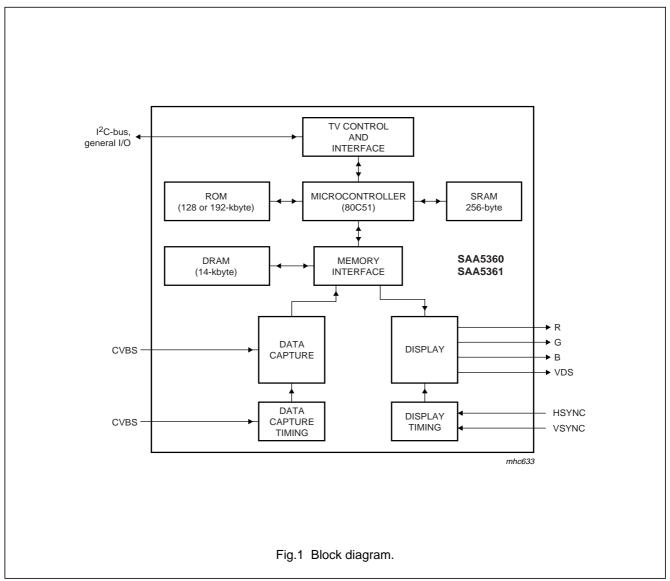

### 5 BLOCK DIAGRAM

# Multi page intelligent teletext decoder

SAA5360; SAA5361

### 6 PINNING

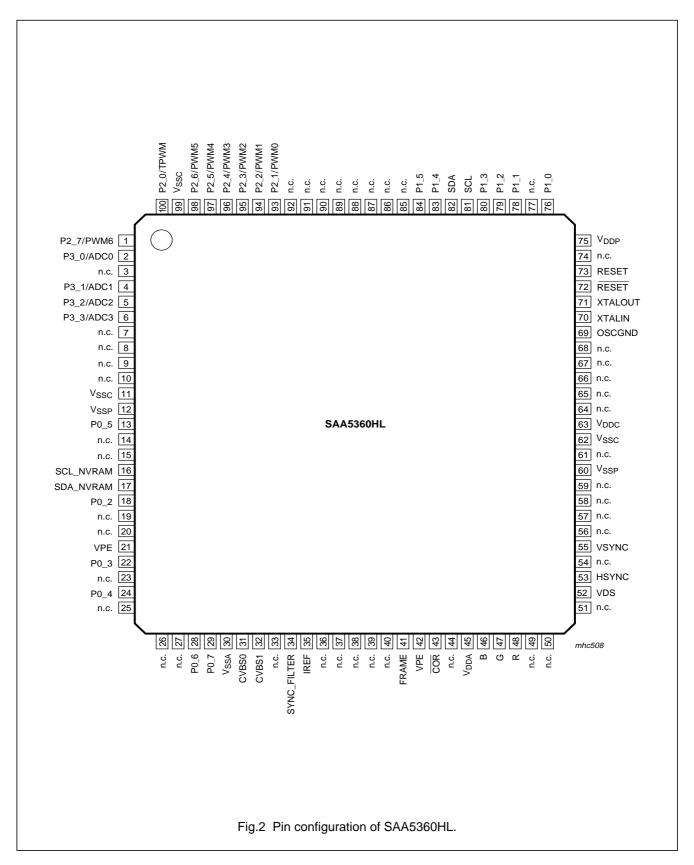

### 6.1 Type SAA5360

| SYMBOL           | PIN | TYPE | DESCRIPTION                                                                                                                   |

|------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------|

| P2_7/PWM6        | 1   | I/O  | programmable bidirectional port 2: bit 7 or output bit 6 of the 7-bit PWM                                                     |

| P3_0/ADC0        | 2   | I/O  | programmable bidirectional port 3: bit 0 or input 0 for the software ADC facility                                             |

| n.c.             | 3   | _    | not connected                                                                                                                 |

| P3_1/ADC1        | 4   | I/O  | programmable bidirectional port 3: bit 1 or input 1 for the software ADC facility                                             |

| P3_2/ADC2        | 5   | I/O  | programmable bidirectional port 3: bit 2 or input 2 for the software ADC facility                                             |

| P3_3/ADC3        | 6   | I/O  | programmable bidirectional port 3: bit 3 or input 3 for the software ADC facility                                             |

| n.c.             | 7   | _    | not connected                                                                                                                 |

| n.c.             | 8   | _    | not connected                                                                                                                 |

| n.c.             | 9   | _    | not connected                                                                                                                 |

| n.c.             | 10  | _    | not connected                                                                                                                 |

| V <sub>SSC</sub> | 11  | _    | core ground                                                                                                                   |

| V <sub>SSP</sub> | 12  | _    | periphery ground                                                                                                              |

| P0_5             | 13  | I/O  | 8 mA current sinking output for direct drive of LED                                                                           |

| n.c.             | 14  | _    | not connected                                                                                                                 |

| n.c.             | 15  | _    | not connected                                                                                                                 |

| SCL_NVRAM        | 16  | I    | I <sup>2</sup> C-bus serial clock input to non-volatile RAM                                                                   |

| SDA_NVRAM        | 17  | I/O  | I <sup>2</sup> C-bus serial data input and output of non-volatile RAM                                                         |

| P0_2             | 18  | I/O  | programmable bidirectional port 0: bit 2                                                                                      |

| n.c.             | 19  | _    | not connected                                                                                                                 |

| n.c.             | 20  | _    | not connected                                                                                                                 |

| VPE              | 21  | ı    | OTP programming voltage input; connect to ground                                                                              |

| P0_3             | 22  | I/O  | programmable bidirectional port 0: bit 3                                                                                      |

| n.c.             | 23  | _    | not connected                                                                                                                 |

| P0_4             | 24  | I/O  | programmable bidirectional port 0: bit 4                                                                                      |

| n.c.             | 25  | _    | not connected                                                                                                                 |

| n.c.             | 26  | _    | not connected                                                                                                                 |

| n.c.             | 27  | _    | not connected                                                                                                                 |

| P0_6             | 28  | I/O  | 8 mA current sinking output for direct drive of LED                                                                           |

| P0_7             | 29  | I/O  | programmable bidirectional port 0: bit 7                                                                                      |

| V <sub>SSA</sub> | 30  | _    | analog ground                                                                                                                 |

| CVBS0            | 31  | I    | composite video input 0 selectable via SFR; a positive-going 1 V (p-p) input is required and connected via a 100 nF capacitor |

| CVBS1            | 32  | I    | composite video input 1 selectable via SFR; a positive-going 1 V (p-p) input is required and connected via a 100 nF capacitor |

| n.c.             | 33  | _    | not connected                                                                                                                 |

| SYNC_FILTER      | 34  | I/O  | CVBS sync filter input; this pin should be connected to V <sub>SSA</sub> via a 100 nF capacitor                               |

| IREF             | 35  | I    | reference current input for analog circuits and connected to $V_{\text{SSA}}$ via a 24 $k\Omega$ resistor                     |

# Multi page intelligent teletext decoder

SAA5360; SAA5361

| SYMBOL           | PIN | TYPE | DESCRIPTION                                                                                                                                              |

|------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| n.c.             | 36  | _    | not connected                                                                                                                                            |

| n.c.             | 37  | _    | not connected                                                                                                                                            |

| n.c.             | 38  | _    | not connected                                                                                                                                            |

| n.c.             | 39  | _    | not connected                                                                                                                                            |

| n.c.             | 40  | _    | not connected                                                                                                                                            |

| FRAME            | 41  | 0    | de-interlace output synchronized with the VSYNC pulse to produce a non-interlaced display by adjustment of the vertical deflection circuits              |

| VPE              | 42  | I    | OTP programming voltage input; connect to ground                                                                                                         |

| COR              | 43  | 0    | output which allows selective contrast reduction of the TV picture to enhance a mixed mode display; open-drain; active LOW                               |

| n.c.             | 44  | _    | not connected                                                                                                                                            |

| $V_{DDA}$        | 45  | _    | 3.3 V analog supply voltage                                                                                                                              |

| В                | 46  | 0    | pixel rate output of the blue colour information                                                                                                         |

| G                | 47  | 0    | pixel rate output of the green colour information                                                                                                        |

| R                | 48  | 0    | pixel rate output of the red colour information                                                                                                          |

| n.c.             | 49  | _    | not connected                                                                                                                                            |

| n.c.             | 50  | _    | not connected                                                                                                                                            |

| n.c.             | 51  | _    | not connected                                                                                                                                            |

| VDS              | 52  | 0    | video or data switch push-pull output for dot rate fast blanking                                                                                         |

| HSYNC            | 53  | I    | Schmitt-triggered input for a TTL-level version of the horizontal sync pulse; the polarity of this pulse is programmable by register bit TXT1.H POLARITY |

| n.c.             | 54  | _    | not connected                                                                                                                                            |

| VSYNC            | 55  | I    | Schmitt-triggered input for a TTL-level version of the vertical sync pulse; the polarity of this pulse is programmable by register bit TXT1.V POLARITY   |

| n.c.             | 56  | _    | not connected                                                                                                                                            |

| n.c.             | 57  | _    | not connected                                                                                                                                            |

| n.c.             | 58  | _    | not connected                                                                                                                                            |

| n.c.             | 59  | _    | not connected                                                                                                                                            |

| V <sub>SSP</sub> | 60  | _    | periphery ground                                                                                                                                         |

| n.c.             | 61  | _    | not connected                                                                                                                                            |

| V <sub>SSC</sub> | 62  | _    | core ground                                                                                                                                              |

| $V_{DDC}$        | 63  | _    | 3.3 V core supply voltage                                                                                                                                |

| n.c.             | 64  | _    | not connected                                                                                                                                            |

| n.c.             | 65  | _    | not connected                                                                                                                                            |

| n.c.             | 66  | _    | not connected                                                                                                                                            |

| n.c.             | 67  | _    | not connected                                                                                                                                            |

| n.c.             | 68  | _    | not connected                                                                                                                                            |

| OSCGND           | 69  | _    | crystal oscillator ground                                                                                                                                |

| XTALIN           | 70  | I    | 12 MHz crystal oscillator input                                                                                                                          |

| XTALOUT          | 71  | 0    | 12 MHz crystal oscillator output                                                                                                                         |

| RESET            | 72  | I    | reset input; if LOW for at least 24 crystal oscillator periods while the oscillator is running, the device is reset; internal pull-up                    |

# Multi page intelligent teletext decoder

SAA5360; SAA5361

| SYMBOL           | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                    |

|------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET            | 73  | I    | reset input; if HIGH for at least 24 crystal oscillator periods while the oscillator is running, the device is reset; this pin should be connected to V <sub>DDC</sub> via a capacitor if an active HIGH reset is required; internal pull-down |

| n.c.             | 74  | _    | not connected                                                                                                                                                                                                                                  |

| $V_{DDP}$        | 75  | _    | 3.3 V periphery supply voltage                                                                                                                                                                                                                 |

| P1_0             | 76  | I/O  | programmable bidirectional port 1: bit 0                                                                                                                                                                                                       |

| n.c.             | 77  | _    | not connected                                                                                                                                                                                                                                  |

| P1_1             | 78  | I/O  | programmable bidirectional port 1: bit 1                                                                                                                                                                                                       |

| P1_2             | 79  | I/O  | programmable bidirectional port 1: bit 2                                                                                                                                                                                                       |

| P1_3             | 80  | I/O  | programmable bidirectional port 1: bit 3                                                                                                                                                                                                       |

| SCL              | 81  | I    | I <sup>2</sup> C-bus serial clock input from application                                                                                                                                                                                       |

| SDA              | 82  | I/O  | I <sup>2</sup> C-bus serial data input from or output to application                                                                                                                                                                           |

| P1_4             | 83  | I/O  | programmable bidirectional port 1: bit 4                                                                                                                                                                                                       |

| P1_5             | 84  | I/O  | programmable bidirectional port 1: bit 5                                                                                                                                                                                                       |

| n.c.             | 85  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 86  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 87  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 88  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 89  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 90  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 91  | _    | not connected                                                                                                                                                                                                                                  |

| n.c.             | 92  | _    | not connected                                                                                                                                                                                                                                  |

| P2_1/PWM0        | 93  | I/O  | programmable bidirectional port 2: bit 1 or output bit 0 of the 7-bit PWM                                                                                                                                                                      |

| P2_2/PWM1        | 94  | I/O  | programmable bidirectional port 2: bit 2 or output bit 1 of the 7-bit PWM                                                                                                                                                                      |

| P2_3/PWM2        | 95  | I/O  | programmable bidirectional port 2: bit 3 or output bit 2 of the 7-bit PWM                                                                                                                                                                      |

| P2_4/PWM3        | 96  | I/O  | programmable bidirectional port 2: bit 4 or output bit 3 of the 7-bit PWM                                                                                                                                                                      |

| P2_5/PWM4        | 97  | I/O  | programmable bidirectional port 2: bit 5 or output bit 4 of the 7-bit PWM                                                                                                                                                                      |

| P2_6/PWM5        | 98  | I/O  | programmable bidirectional port 2: bit 6 or output bit 5 of the 7-bit PWM                                                                                                                                                                      |

| V <sub>SSC</sub> | 99  | _    | core ground                                                                                                                                                                                                                                    |

| P2_0/TPWM        | 100 | I/O  | programmable bidirectional port 2: bit 0 or output for 14-bit high precision PWM                                                                                                                                                               |

### Multi page intelligent teletext decoder

SAA5360; SAA5361

# Multi page intelligent teletext decoder

SAA5360; SAA5361

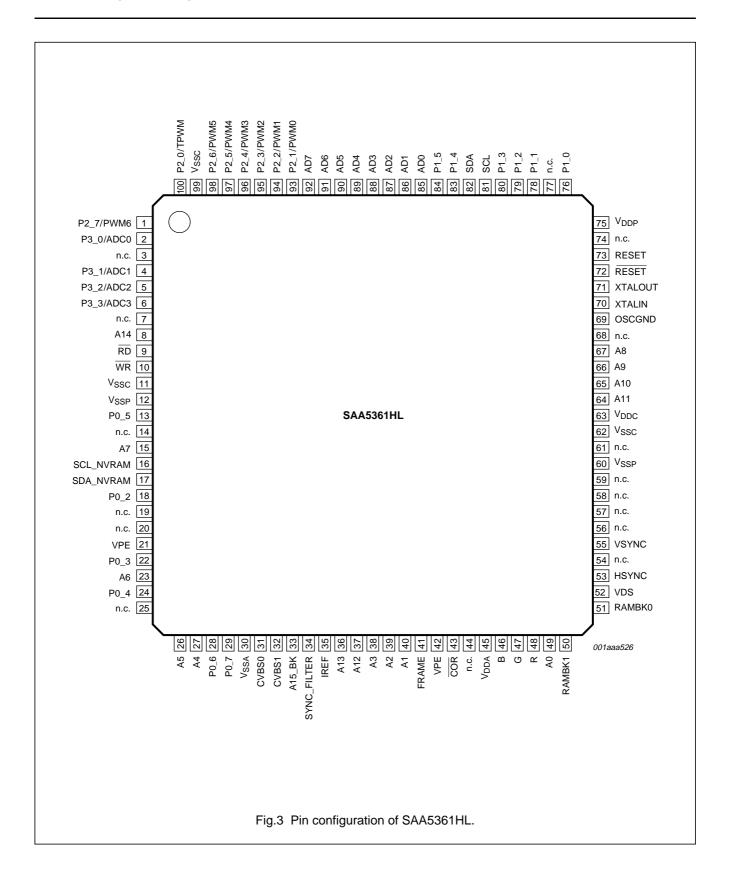

### 6.2 Type SAA5361

| SYMBOL           | PIN | TYPE | DESCRIPTION                                                                                                                   |

|------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------|

| P2_7/PWM6        | 1   | I/O  | programmable bidirectional port 2: bit 7 or output bit 6 of the 6-bit PWM                                                     |

| P3_0/ADC0        | 2   | I/O  | programmable bidirectional port 3 with alternative functions: bit 0 or input 0 for the software ADC facility                  |

| n.c.             | 3   | 0    | not connected                                                                                                                 |

| P3_1/ADC1        | 4   | I/O  | programmable bidirectional port 3 with alternative functions: bit 1 or input 1 for the software ADC facility                  |

| P3_2/ADC2        | 5   | I/O  | programmable bidirectional port 3 with alternative functions: bit 2 or input 2 for the software ADC facility                  |

| P3_3/ADC3        | 6   | I/O  | programmable bidirectional port 3 with alternative functions: bit 3 or input 3 for the software ADC facility                  |

| n.c.             | 7   | 0    | not connected                                                                                                                 |

| A14              | 8   | 0    | address line 14                                                                                                               |

| RD               | 9   | 0    | read control output to external data memory; active LOW                                                                       |

| WR               | 10  | 0    | write control output to external data memory; active LOW                                                                      |

| V <sub>SSC</sub> | 11  | -    | core ground                                                                                                                   |

| V <sub>SSP</sub> | 12  | -    | periphery ground                                                                                                              |

| P0_5             | 13  | I/O  | 8 mA current sinking output for direct drive of LED                                                                           |

| n.c.             | 14  | I    | not connected                                                                                                                 |

| A7               | 15  | 0    | address line 7                                                                                                                |

| SCL_NVRAM        | 16  | I    | I <sup>2</sup> C-bus serial clock input to non-volatile RAM                                                                   |

| SDA_NVRAM        | 17  | I/O  | I <sup>2</sup> C-bus serial data input and output of non-volatile RAM                                                         |

| P0_2             | 18  | I/O  | programmable bidirectional port 0 with alternative functions: bit 2 input and output for general use                          |

| n.c.             | 19  | 0    | not connected                                                                                                                 |

| n.c.             | 20  | 0    | not connected                                                                                                                 |

| VPE              | 21  | I    | OTP programming voltage input; connect to ground                                                                              |

| P0_3             | 22  | I/O  | programmable bidirectional port 0 with alternative functions: bit 3 input and output for general use                          |

| A6               | 23  | 0    | address line 6                                                                                                                |

| P0_4             | 24  | I/O  | programmable bidirectional port 0 with alternative functions: bit 4 input and output for general use                          |

| n.c.             | 25  | I/O  | not connected                                                                                                                 |

| A5               | 26  | 0    | address line 5                                                                                                                |

| A4               | 27  | 0    | address line 4                                                                                                                |

| P0_6             | 28  | I/O  | 8 mA current sinking output for direct drive of LED                                                                           |

| P0_7             | 29  | I/O  | programmable bidirectional port 0 with alternative functions: bit 7 input and output for general use                          |

| V <sub>SSA</sub> | 30  | -    | analog ground                                                                                                                 |

| CVBS0            | 31  | I    | composite video input 0 selectable via SFR; a positive-going 1 V (p-p) input is required and connected via a 100 nF capacitor |

| CVBS1            | 32  | I    | composite video input 1 selectable via SFR; a positive-going 1 V (p-p) input is required and connected via a 100 nF capacitor |

# Multi page intelligent teletext decoder

SAA5360; SAA5361

| SYMBOL           | PIN | TYPE | DESCRIPTION                                                                                                                                              |

|------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A15_BK           | 33  | 0    | address line 15                                                                                                                                          |

| SYNC_FILTER      | 34  | I/O  | CVBS sync filter input; this pin should be connected to V <sub>SSA</sub> via a 100 nF capacitor                                                          |

| IREF             | 35  | I    | reference current input for analog circuits and connected to $V_{\text{SSA}}$ via a 24 $k\Omega$ resistor                                                |

| A13              | 36  | 0    | address line 13                                                                                                                                          |

| A12              | 37  | 0    | address line 12                                                                                                                                          |

| A3               | 38  | 0    | address line 3                                                                                                                                           |

| A2               | 39  | 0    | address line 2                                                                                                                                           |

| A1               | 40  | 0    | address line 1                                                                                                                                           |

| FRAME            | 41  | 0    | de-interlace output synchronized with the VSYNC pulse to produce a non-interlaced display by adjustment of the vertical deflection circuits              |

| VPE              | 42  | I    | OTP programming voltage input; connect to ground                                                                                                         |

| COR              | 43  | 0    | output which allows selective contrast reduction of the TV picture to enhance a mixed mode display; open-drain; active LOW                               |

| n.c.             | 44  | I/O  | not connected                                                                                                                                            |

| $V_{DDA}$        | 45  | -    | 3.3 V analog supply voltage                                                                                                                              |

| В                | 46  | 0    | pixel rate output of the blue colour information                                                                                                         |

| G                | 47  | 0    | pixel rate output of the green colour information                                                                                                        |

| R                | 48  | 0    | pixel rate output of the red colour information                                                                                                          |

| A0               | 49  | 0    | address line 0                                                                                                                                           |

| RAMBK1           | 50  | 0    | RAMBK SFR selection bits input 1 for external program SRAM data storage                                                                                  |

| RAMBK0           | 51  | 0    | RAMBK SFR selection bits input 0 for external program SRAM data storage                                                                                  |

| VDS              | 52  | 0    | video or data switch push-pull output for dot rate fast blanking                                                                                         |

| HSYNC            | 53  | I    | Schmitt-triggered input for a TTL-level version of the horizontal sync pulse; the polarity of this pulse is programmable by register bit TXT1.H POLARITY |

| n.c.             | 54  | I/O  | not connected                                                                                                                                            |

| VSYNC            | 55  | I    | Schmitt-triggered input for a TTL-level version of the vertical sync pulse; the polarity of this pulse is programmable by register bit TXT1.V POLARITY   |

| n.c.             | 56  | 0    | not connected                                                                                                                                            |

| n.c.             | 57  | 0    | not connected                                                                                                                                            |

| n.c.             | 58  | 0    | not connected                                                                                                                                            |

| n.c.             | 59  | I/O  | not connected                                                                                                                                            |

| V <sub>SSP</sub> | 60  | -    | periphery ground                                                                                                                                         |

| n.c.             | 61  | I    | not connected (internal pull-up)                                                                                                                         |

| V <sub>SSC</sub> | 62  | -    | core ground                                                                                                                                              |

| $V_{DDC}$        | 63  | -    | 3.3 V core supply voltage                                                                                                                                |

| A11              | 64  | 0    | address line 11                                                                                                                                          |

| A10              | 65  | 0    | address line 10                                                                                                                                          |

| A9               | 66  | 0    | address line 9                                                                                                                                           |

| A8               | 67  | 0    | address line 8                                                                                                                                           |

| n.c.             | 68  | 0    | not connected                                                                                                                                            |

| OSCGND           | 69  | -    | crystal oscillator ground                                                                                                                                |

# Multi page intelligent teletext decoder

SAA5360; SAA5361

| SYMBOL           | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                    |

|------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTALIN           | 70  | I    | 12 MHz crystal oscillator input                                                                                                                                                                                                                |

| XTALOUT          | 71  | 0    | 12 MHz crystal oscillator output                                                                                                                                                                                                               |

| RESET            | 72  | I    | reset input; if LOW for at least 24 crystal oscillator periods while the oscillator is running, the device is reset; internal pull-up                                                                                                          |

| RESET            | 73  | I    | reset input; if HIGH for at least 24 crystal oscillator periods while the oscillator is running, the device is reset; this pin should be connected to V <sub>DDC</sub> via a capacitor if an active HIGH reset is required; internal pull-down |

| n.c.             | 74  | 0    | not connected                                                                                                                                                                                                                                  |

| $V_{DDP}$        | 75  | -    | 3.3 V periphery supply voltage                                                                                                                                                                                                                 |

| P1_0             | 76  | Ю    | programmable bidirectional port 1 with alternative functions: bit 0 input and output for general use                                                                                                                                           |

| n.c.             | 77  | 0    | not connected                                                                                                                                                                                                                                  |

| P1_1             | 78  | I/O  | programmable bidirectional port 1 with alternative functions: bit 1 input and output for general use                                                                                                                                           |

| P1_2             | 79  | I/O  | programmable bidirectional port 1 with alternative functions: bit 2 input and output for general use                                                                                                                                           |

| P1_3             | 80  | I/O  | programmable bidirectional port 1 with alternative functions: bit 3 input and output for general use                                                                                                                                           |

| SCL              | 81  | ı    | I <sup>2</sup> C-bus serial clock input from application                                                                                                                                                                                       |

| SDA              | 82  | I/O  | I <sup>2</sup> C-bus serial data input from or output to application                                                                                                                                                                           |

| P1_4             | 83  | I/O  | programmable bidirectional port 1 with alternative functions: bit 4 input and output for general use                                                                                                                                           |

| P1_5             | 84  | I/O  | programmable bidirectional port 1 with alternative functions: bit 5 input and output for general use                                                                                                                                           |

| AD0              | 85  | I/O  | address line 0 with multiplexed data line 0                                                                                                                                                                                                    |

| AD1              | 86  | I/O  | address line 1 with multiplexed data line 1                                                                                                                                                                                                    |

| AD2              | 87  | I/O  | address line 2 with multiplexed data line 2                                                                                                                                                                                                    |

| AD3              | 88  | I/O  | address line 3 with multiplexed data line 3                                                                                                                                                                                                    |

| AD4              | 89  | I/O  | address line 4 with multiplexed data line 4                                                                                                                                                                                                    |

| AD5              | 90  | I/O  | address line 5 with multiplexed data line 5                                                                                                                                                                                                    |

| AD6              | 91  | I/O  | address line 6 with multiplexed data line 6                                                                                                                                                                                                    |

| AD7              | 92  | I/O  | address line 7 with multiplexed data line 7                                                                                                                                                                                                    |

| P2_1/PWM0        | 93  | I/O  | programmable bidirectional port 2: bit 1 or output bit 0 of the 6-bit PWM                                                                                                                                                                      |

| P2_2/PWM1        | 94  | I/O  | programmable bidirectional port 2: bit 2 or output bit 1 of the 6-bit PWM                                                                                                                                                                      |

| P2_3/PWM2        | 95  | I/O  | programmable bidirectional port 2: bit 3 or output bit 2 of the 6-bit PWM                                                                                                                                                                      |

| P2_4/PWM3        | 96  | I/O  | programmable bidirectional port 2: bit 4 or output bit 3 of the 6-bit PWM                                                                                                                                                                      |

| P2_5/PWM4        | 97  | I/O  | programmable bidirectional port 2: bit 5 or output bit 4 of the 6-bit PWM                                                                                                                                                                      |

| P2_6/PWM5        | 98  | I/O  | programmable bidirectional port 2: bit 6 or output bit 5 of the 6-bit PWM                                                                                                                                                                      |

| V <sub>SSC</sub> | 99  | -    | core ground                                                                                                                                                                                                                                    |

| P2_0/TPWM        | 100 | I/O  | programmable bidirectional port 2: bit 0 or output for 14-bit high precision PWM                                                                                                                                                               |

### Multi page intelligent teletext decoder

SAA5360; SAA5361

### Multi page intelligent teletext decoder

SAA5360; SAA5361

#### 7 COMMANDS AND CHARACTER SETS

### 7.1 High-level command interface

The I<sup>2</sup>C-bus interface is used to pass control commands and data between the SAA5360; SAA5361 and the television microcontroller. The interface uses high-level commands, which are backwards compatible with the SAFARI.

The I<sup>2</sup>C-bus transmission formats are given in Tables 1 to 3.

### Table 1 User command

| USER COMMAND |                              |       |     |         |     |      |  |  |  |

|--------------|------------------------------|-------|-----|---------|-----|------|--|--|--|

| START        | I <sup>2</sup> C-bus address | write | ACK | command | ACK | STOP |  |  |  |

### Table 2 System command

| SYSTEM COMMAND |                              |       |     |         |     |           |     |      |  |

|----------------|------------------------------|-------|-----|---------|-----|-----------|-----|------|--|

| START          | I <sup>2</sup> C-bus address | write | ACK | command | ACK | parameter | ACK | STOP |  |

#### Table 3 User read

|       | USER READ                    |      |     |      |     |      |  |  |  |  |

|-------|------------------------------|------|-----|------|-----|------|--|--|--|--|

| START | I <sup>2</sup> C-bus address | read | ACK | data | ACK | STOP |  |  |  |  |

### 7.2 Character sets

The SAA5360HL/M1/0004 contains the character set for Pan-Euro, Arabic and Iranian and has slave address 58H.

The SAA5361HL/M1/1651 contains the character set for Pan-Euro, Cyrillic, Greek and Arabic and has slave address 60H.

### Multi page intelligent teletext decoder

SAA5360; SAA5361

### **8 LIMITING VALUES**

In accordance with Absolute Maximum Rating System (IEC 60134).

| SYMBOL             | PARAMETER                        | CONDITIONS                                   | MIN. | MAX.                  | UNIT |

|--------------------|----------------------------------|----------------------------------------------|------|-----------------------|------|

| $V_{DD}$           | all supply voltages              |                                              | -0.5 | +4.0                  | V    |

| V <sub>I</sub>     | input voltage (any input)        | V <sub>DD</sub> < 3.6 V; note 1              | -0.5 | V <sub>DD</sub> + 0.5 | V    |

|                    |                                  | V <sub>DD</sub> ≥ 3.6 V; note 1              | -0.5 | 4.1                   | V    |

| Vo                 | output voltage (any output)      | note 1                                       | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Io                 | output current (each output)     |                                              | _    | 10                    | mA   |

| I <sub>IO(d)</sub> | diode DC input or output current |                                              | _    | 20                    | mA   |

| T <sub>amb</sub>   | ambient temperature              |                                              | -20  | +70                   | °C   |

| T <sub>j</sub>     | junction temperature             |                                              | -20  | +125                  | °C   |

| T <sub>stg</sub>   | storage temperature              |                                              | -55  | +125                  | °C   |

| V <sub>esd</sub>   | electrostatic discharge voltage  | Human body model;<br>C = 100 pF; R = 1.5 kΩ  | _    | 2000                  | V    |

|                    |                                  | Machine model;<br>C = 200 pF; R = 0 $\Omega$ | _    | 200                   | V    |

| I <sub>lu</sub>    | latch-up current                 | $1.5 \times V_{DD}$                          | _    | 100                   | mA   |

### Note

### 9 THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 52    | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 8     | K/W  |

### 10 QUALITY AND RELIABILITY

In accordance with "General Quality Specification for Integrated circuits SNW-FQ-611".

<sup>1.</sup> This maximum value refers to 5 V tolerant I/Os and may be 6 V maximum but only when  $V_{\text{DD}}$  is present.

# Multi page intelligent teletext decoder

SAA5360; SAA5361

### 11 CHARACTERISTICS

$V_{DD}$  = 3.3 V  $\pm$  10 %;  $V_{SS}$  = 0 V;  $T_{amb}$  = –20 °C to +70 °C; unless otherwise specified.

| SYMBOL            | PARAMETER                                   | CONDITIONS                                                  | MIN.  | TYP.  | MAX.  | UNIT |

|-------------------|---------------------------------------------|-------------------------------------------------------------|-------|-------|-------|------|

| Supplies          |                                             |                                                             |       |       | 1     | !    |

| V <sub>DD</sub>   | any supply voltage                          | referenced to V <sub>SS</sub>                               | 3.0   | 3.3   | 3.6   | V    |

| I <sub>DDP</sub>  | periphery supply current                    | note 1                                                      | 1     | _     | _     | mA   |

| I <sub>DDC</sub>  | core supply current                         | operating mode                                              | _     | 15    | 18    | mA   |

|                   |                                             | idle mode                                                   | _     | 4.6   | 6     | mA   |

|                   |                                             | power-down mode                                             | _     | 0.76  | 1     | mA   |

| I <sub>DDA</sub>  | analog supply current                       | operating mode                                              | _     | 45    | 48    | mA   |

|                   |                                             | idle mode                                                   | _     | 0.87  | 1     | mA   |

|                   |                                             | power-down mode                                             | _     | 0.45  | 0.7   | mA   |

| Digital inp       | outs                                        |                                                             |       |       |       |      |

| PIN RESE          | Г                                           |                                                             |       |       |       |      |

| V <sub>IL</sub>   | LOW-level input voltage                     |                                                             | _     | _     | 1.00  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage                    |                                                             | 1.85  | _     | 5.5   | V    |

| V <sub>hys</sub>  | hysteresis voltage of Schmitt-trigger input |                                                             | 0.44  | _     | 0.58  | V    |

| ILI               | input leakage current                       | $V_I = 0$                                                   | _     | _     | 0.17  | μΑ   |

| R <sub>pd</sub>   | equivalent pull-down resistance             | $V_I = V_{DD}$                                              | 55.73 | 70.71 | 92.45 | kΩ   |

| PIN RESE          | Ī                                           |                                                             | '     | '     | _     | '    |

| V <sub>IL</sub>   | LOW-level input voltage                     |                                                             | _     | _     | 0.98  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage                    |                                                             | 1.73  | _     | 5.5   | V    |

| V <sub>hys</sub>  | hysteresis voltage of Schmitt-trigger input |                                                             | 0.41  | _     | 0.5   | V    |

| ILI               | input leakage current                       | $V_I = V_{DD}$                                              | _     | _     | 0.00  | μΑ   |

| R <sub>pu</sub>   | equivalent pull-up resistance               | V <sub>I</sub> = 0                                          | 46.07 | 55.94 | 70.01 | kΩ   |

| PINS HSYN         | NC AND VSYNC                                |                                                             |       |       |       |      |

| V <sub>IL</sub>   | LOW-level input voltage                     |                                                             | _     | _     | 0.96  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage                    |                                                             | 1.80  | _     | 5.5   | V    |

| V <sub>hys</sub>  | hysteresis of Schmitt-trigger input         |                                                             | 0.40  | _     | 0.56  | V    |

| ILI               | input leakage current                       | $V_I = 0$ to $V_{DD}$                                       | _     | _     | 0.00  | μΑ   |

| Digital out       | puts                                        |                                                             |       | '     | •     |      |

| PINS FRAN         | ME AND VDS                                  |                                                             |       |       |       |      |

| V <sub>OL</sub>   | LOW-level output voltage                    | I <sub>OL</sub> = 3 mA                                      | _     | _     | 0.13  | V    |

| V <sub>OH</sub>   | HIGH-level output voltage                   | I <sub>OH</sub> = 3 mA                                      | 2.84  | _     | _     | V    |

| t <sub>o(r)</sub> | output rise time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF | 7.50  | 8.85  | 10.90 | ns   |

| t <sub>o(f)</sub> | output fall time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF | 6.70  | 7.97  | 10.00 | ns   |

# Multi page intelligent teletext decoder

SAA5360; SAA5361

| SYMBOL            | PARAMETER                                   | CONDITIONS                                                             | MIN.    | TYP.     | MAX.  | UNIT |

|-------------------|---------------------------------------------|------------------------------------------------------------------------|---------|----------|-------|------|

| PIN COR (         | OPEN-DRAIN)                                 |                                                                        |         |          | 1     |      |

| V <sub>OL</sub>   | LOW-level output voltage                    | I <sub>OL</sub> = 3 mA                                                 | _       | _        | 0.14  | V    |

| V <sub>OH</sub>   | HIGH-level pull-up output voltage           | $I_{OL} = -3 \text{ mA}$ ; push-pull                                   | 2.84    | _        | _     | V    |

| ILI               | input leakage current                       | $V_I = 0$ to $V_{DD}$                                                  | _       | _        | 0.12  | μΑ   |

| t <sub>o(r)</sub> | output rise time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF            | 7.20    | 8.64     | 11.10 | ns   |

| t <sub>o(f)</sub> | output fall time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF            | 4.90    | 7.34     | 9.40  | ns   |

| Digital inp       | out/outputs                                 |                                                                        | •       |          |       |      |

| PINS SCL_         | NVRAM, SDA_NVRAM, P0_4 TO P0_7, P1          | _0, P1_1, P2_1 to P2_7                                                 | AND P3_ | 0 то Р3_ | _4    |      |

| V <sub>IL</sub>   | LOW-level input voltage                     |                                                                        | _       | _        | 0.98  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage                    |                                                                        | 1.78    | _        | 5.50  | V    |

| V <sub>hys</sub>  | hysteresis of Schmitt-trigger input         |                                                                        | 0.41    | _        | 0.55  | V    |

| ILI               | input leakage current                       | $V_I = 0$ to $V_{DD}$                                                  | _       | _        | 0.01  | μΑ   |

| V <sub>OL</sub>   | LOW-level output voltage                    | I <sub>OL</sub> = 4 mA                                                 | _       | _        | 0.18  | V    |

| V <sub>OH</sub>   | HIGH-level output voltage                   | $I_{OH} = -4 \text{ mA}$ ; push-pull                                   | 2.81    | _        | _     | V    |

| t <sub>o(r)</sub> | output rise time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF; push-pull | 6.50    | 8.47     | 10.70 | ns   |

| t <sub>o(f)</sub> | output fall time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF            | 5.70    | 7.56     | 10.00 | ns   |

| PINS P1_2         | , P1_3 AND P2_0                             | - '                                                                    |         | 1        |       |      |

| V <sub>IL</sub>   | LOW-level input voltage                     |                                                                        | _       | _        | 0.99  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage                    |                                                                        | 1.80    | _        | 5.50  | V    |

| V <sub>hys</sub>  | hysteresis voltage of Schmitt-trigger input |                                                                        | 0.42    | _        | 0.56  | V    |

|                   | input leakage current                       | $V_I = 0$ to $V_{DD}$                                                  | _       | _        | 0.02  | μΑ   |

| V <sub>OL</sub>   | LOW-level output voltage                    | I <sub>OL</sub> = 4 mA                                                 | _       | _        | 0.17  | V    |

| V <sub>OH</sub>   | HIGH-level output voltage                   | $I_{OH} = -4 \text{ mA}$ ; push-pull                                   | 2.81    | _        | _     | V    |

| t <sub>o(r)</sub> | output rise time                            | 10 % to 90 % of $V_{DD}$ ;<br>$C_L = 70 \text{ pF}$ ; push-pull        | 7.00    | 8.47     | 10.50 | ns   |

| t <sub>o(f)</sub> | output fall time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF            | 5.40    | 7.36     | 9.30  | ns   |

| PINS P0_5         | AND P0_6                                    |                                                                        | · ·     |          |       |      |

| V <sub>IL</sub>   | LOW-level input voltage                     |                                                                        | _       | _        | 0.98  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage                    |                                                                        | 1.82    | _        | 5.50  | V    |

| I <sub>LI</sub>   | input leakage current                       | $V_I = 0$ to $V_{DD}$                                                  | _       | _        | 0.11  | μΑ   |

| V <sub>hys</sub>  | hysteresis voltage of Schmitt-trigger input |                                                                        | 0.42    | _        | 0.58  | V    |

| V <sub>OL</sub>   | LOW-level output voltage                    | I <sub>OL</sub> = 8 mA                                                 | -       | _        | 0.20  | V    |

| V <sub>OH</sub>   | HIGH-level output voltage                   | $I_{OH} = -8 \text{ mA}$ ; push-pull                                   | 2.76    | _        | _     | V    |

| t <sub>o(r)</sub> | output rise time                            | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF; push-pull | 7.40    | 8.22     | 8.80  | ns   |

# Multi page intelligent teletext decoder

SAA5360; SAA5361

| SYMBOL                 | PARAMETER                                                               | CONDITIONS                                                                                | MIN.  | TYP.  | MAX.                   | UNIT |

|------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|------------------------|------|

| t <sub>o(f)</sub>      | output fall time                                                        | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF                               | 4.20  | 4.57  | 5.20                   | ns   |

| PINS P1_4              | AND P1_5 (OPEN DRAIN)                                                   |                                                                                           |       |       |                        |      |

| V <sub>IL</sub>        | LOW-level input voltage                                                 |                                                                                           | -     | _     | 1.08                   | V    |

| V <sub>IH</sub>        | HIGH-level input voltage                                                |                                                                                           | 1.99  | _     | 5.50                   | V    |

| V <sub>hys</sub>       | hysteresis voltage of Schmitt-trigger input                             |                                                                                           | 0.49  | _     | 0.60                   | V    |

| I <sub>LI</sub>        | input leakage current                                                   | $V_I = 0$ to $V_{DD}$                                                                     | _     | _     | 0.13                   | μΑ   |

| V <sub>OL</sub>        | LOW-level output voltage                                                | I <sub>OL</sub> = 8 mA                                                                    | _     | _     | 0.35                   | V    |

| $t_{o(f)}$             | output fall time                                                        | 10 % to 90 % of V <sub>DD</sub> ;<br>C <sub>L</sub> = 70 pF                               | 69.70 | 83.67 | 103.30                 | ns   |

| t <sub>o(f)(I2C)</sub> | output fall time in relation to the I <sup>2</sup> C-bus specifications | $V_0 = 3 \text{ V to } 1.5 \text{ V at}$<br>$I_{OL} = 3 \text{ mA}; C_L = 400 \text{ nF}$ | _     | 57.80 | _                      | ns   |

| Analog in              | puts                                                                    |                                                                                           |       | '     | _                      | •    |

| PINS CVBS              | 60 AND CVBS1                                                            |                                                                                           |       |       |                        |      |

| V <sub>sync</sub>      | sync voltage amplitude                                                  |                                                                                           | 0.1   | 0.3   | 0.6                    | V    |

| $V_{v(p-p)}$           | video input voltage amplitude<br>(peak-to-peak value)                   |                                                                                           | 0.7   | 1.0   | 1.4                    | V    |

| Z <sub>source</sub>    | source impedance                                                        |                                                                                           | 0     | _     | 250                    | Ω    |

| V <sub>IH</sub>        | HIGH-level input voltage                                                |                                                                                           | 3.0   | _     | V <sub>DDA</sub> + 0.3 | V    |

| Ci                     | input capacitance                                                       |                                                                                           | _     | _     | 10                     | pF   |

| PIN IREF               |                                                                         |                                                                                           |       |       |                        |      |

| R <sub>gnd</sub>       | resistance to ground                                                    | resistor tolerance 2 %                                                                    | _     | 24    | _                      | kΩ   |

| Pins ADC               | ) TO ADC3                                                               |                                                                                           | •     |       | •                      |      |

| V <sub>IH</sub>        | HIGH-level input voltage                                                | range = V <sub>DDP</sub> - V <sub>TN</sub> ;<br>note 2                                    | _     | _     | $V_{DDA}$              | V    |

| C <sub>i</sub>         | input capacitance                                                       |                                                                                           | _     | _     | 10                     | pF   |

| Analog ou              | itputs                                                                  |                                                                                           | '     | '     |                        | •    |

| PINS R, G              | AND B                                                                   |                                                                                           |       |       |                        |      |

| I <sub>o(b)</sub>      | output current (black level)                                            | V <sub>DDA</sub> = 3.3 V                                                                  | -10   | _     | +10                    | μΑ   |

| I <sub>o(max)</sub>    | output current (maximum Intensity)                                      | V <sub>DDA</sub> = 3.3 V; intensity<br>level code = 31 decimal                            | 6.0   | 6.67  | 7.3                    | mA   |

| I <sub>o(70)</sub>     | output current (70 % of full intensity)                                 | V <sub>DDA</sub> = 3.3 V; intensity<br>level code = 0 decimal                             | 4.2   | 4.7   | 5.1                    | mA   |

| R <sub>L</sub>         | load resistor                                                           | referenced to V <sub>SSA;</sub> resistor tolerance 5 %                                    | _     | 150   | _                      | Ω    |

| C <sub>L</sub>         | load capacitance                                                        |                                                                                           | _     | _     | 15                     | pF   |

| t <sub>o(r)</sub>      | output rise time                                                        | 10 % to 90 % full intensity                                                               | _     | 16.1  | _                      | ns   |

| t <sub>o(f)</sub>      | output fall time                                                        | 90 % to 10 % full intensity                                                               | _     | 14.5  | -                      | ns   |