# CMOS CacheRAM™ 32K x 9-BIT (288K-BIT) BURST COUNTER & SELF-TIMED WRITE

IDT71589SA

#### **FEATURES:**

- · High density 32K x 9 architecture

- · Internal write registers (address, data, and control)

- · Self-timed write cycle

- · Internal burst read and write address counter

- · Clock to data times: 19, 24, and 34ns

- Chip select for depth expansion

- Complies with all timing and signals of 80486 processors up to 40MHz

- · I/O pins directly TTL-compatible

- Packaged in plastic 300 mil 32-pin SOJ

- BiCMOS version available for 50MHz and 67MHz systems (IDT71B589)

- SIMM module versions also available from IDT in 128KB (IDT7MP6085 and IDT7MP6086) and 256KB (IDT7MP6087) densities, plus parity

#### DESCRIPTION:

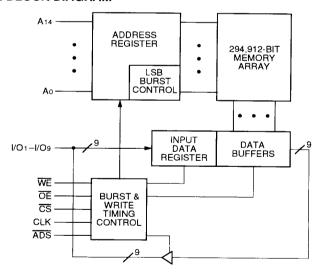

The IDT71589 is a very high-speed 32K x 9-bit static RAM with full on-chip hardware support of the 80486 CPU interface. This part is designed to facilitate the implementation of the highest-performance secondary caches for the 486 architecture while using low-speed cache-tag RAMs and PALs and consuming the minimum possible board space.

The IDT71589 CacheRAM contains a full set of write data and address registers. Internal logic allows the processor to generate a self-timed write based upon a decision which can be left until the extreme end of the write cycle.

An internal burst address counter accepts the first cycle address from the processor, then cycles through the adjacent four locations using the 486's burst refill sequence on appropriate rising edges of the system clock.

Fabricated using IDT's CMOS high-performance sub-micron technology, this device operates at a very low power consumption and offers a maximum clock to data access time as fast as 19ns.

The IDT71589SA CacheRAMs are packaged in a 32-pin small-outline J-bend (SOJ) package, which allows for a 128KB (plus parity) secondary cache to be built in approximately 1.20 square inches.

# **FUNCTIONAL BLOCK DIAGRAM**

2947 drw 01

The IDT logo is a registered trademark and CacheRAM is a trademark of Integrated Device Technology, Inc. Intel and i486 are trademarks of Intel Corp.

COMMERCIAL TEMPERATURE RANGE

SEPTEMBER 1992

©1992 Integrated Device Technology, Inc

10.4-/

DSC-1043/1

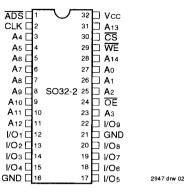

### PIN CONFIGURATION

#### SOJ TOP VIEW

## **PIN NAMES**

| A0-A14    | Address Inputs           |

|-----------|--------------------------|

| I/O1-I/O9 | Data Input/Output        |

| CS        | Chip Select/Count Enable |

| WE        | Write Enable             |

| ŌĒ        | Output Enable            |

| ADS       | Address Status           |

| CLK       | System Clock             |

| GND       | Ground                   |

| Vcc       | Power                    |

2947 tbl 01

2947 tbl 02

# **SPEED SELECTION**

| 80486 Speed | Suggested IDT71589             |

|-------------|--------------------------------|

| 25MHz       | IDT71589SA35                   |

| 33MHz       | IDT71589SA25                   |

| 40MHz       | IDT71589SA20                   |

| 50MHz       | IDT71B589S14 <sup>(1, 2)</sup> |

| 50MHz       | IDT71B589S12 <sup>(1, 2)</sup> |

| 67MHz       | IDT71B589S10 <sup>(1, 3)</sup> |

#### NOTES:

- Separate data sheet available for BiCMOS version.

- 2. Either part may be used, depending on system loads.

- 3. Intended for the P5 or future faster versions of the 80486.

# COUNT SEQUENCE(1) (Ao. A1 ONLY)

|       | ·  |    |    |

|-------|----|----|----|

| Start | +1 | +2 | +3 |

| 0     | 1  | 2  | 3  |

| 1     | 0  | 3  | 2  |

| 2     | 3  | 0  | 1  |

| 3     | 2  | 1  | 0  |

#### NOTE:

2947 tbl 03

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                               | Value        | Unit |

|--------|--------------------------------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | ٧    |

| TA     | Operating Temperature                | -0 to +70    | °C   |

| TBIAS  | Temperature Under Bias               | -65 to +135  | °С   |

| Тѕтс   | Storage Temperature                  | -65 to +150  | °C   |

| Рт     | Power Dissipation                    | 1.5          | W    |

| lout   | DC Output Current                    | 50           | mA   |

#### NOTE:

2947 tbl 04

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Ambient Temperature | GND | Vcc       |

|------------|---------------------|-----|-----------|

| Commercial | 0°C to +70°C        | ٥V  | 5.0V ± 5% |

2947 tbl 05

# RECOMMENDED DC OPERATING CONDITIONS

| Symbol | Parameter         | Min.               | Тур. | Max. | Unit |  |

|--------|-------------------|--------------------|------|------|------|--|

| Vcc    | Supply Voltage    | 4.75               | 5.0  | 5.25 | ٧    |  |

| GND    | Supply Voltage    | 0                  | 0    | 0.0  | ٧    |  |

| V≀H    | Input High Votage | 2.2                | _    | 6.0  | ٧    |  |

| VIL    | Input Low Voltage | 0.5 <sup>(1)</sup> | _    | 0.8  | ٧    |  |

NOTE:

2947 tbl 06

1. VIL (min.) = −1.5V for pulse width of less than 10ns, once per cycle.

10.4-2

2

The counter wraps around to its starting value and repeats the same sequence after the last count.

# DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE ( $Vcc=5.0V\pm5\%$ )

| Symbol | Parameter                      | Parameter Test Condition               |     | Max. | Unit |

|--------|--------------------------------|----------------------------------------|-----|------|------|

| lu     | Input Leakage Current          | Vcc = 5.25V, Vin = 0V to Vcc           |     | 10   | μА   |

| luo    | Output Leakage Current         | CS = VIH, VOUT = 0V to VCC, VCC = Max. | -   | 10   | μА   |

| Vol    | Output Low Voltage (I/O1-I/O9) | IoL = 8mA, Vcc = Min.                  |     | 0.4  | ٧    |

| Vон    | Output High Voltage            | Iон = −4mA, Vcc = Min.                 | 2.4 | —    | ٧    |

2947 tbl 07

2947 thi 08

# DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(1)</sup> (Vcc = 5.0V ± 5%, VLc = 0.2V, VHc = Vcc - 0.2V)

|        |                                   |                                                                | 71589SA20 <sup>(3)</sup> 71589SA25 71589SA3 |      | 71589SA20 <sup>(3)</sup> 71589SA25 |      | SA35   |      |      |

|--------|-----------------------------------|----------------------------------------------------------------|---------------------------------------------|------|------------------------------------|------|--------|------|------|

| Symbol | Parameter                         | Test Condition                                                 | Com'l.                                      | Mil. | Com'l.                             | Mil. | Com'l. | Mil. | Unit |

| Icc1   | Operating Power<br>Supply Current | CS = ViL, Outputs Open<br>Vcc = Max., f = 0 <sup>(2)</sup>     | 130                                         | _    | 130                                | _    | 130    | _    | mA   |

| ICC2   | Dynamic Operating<br>Current      | CS = Vil., Outputs Open<br>Vcc = Max., f = fMax <sup>(2)</sup> | 240                                         | _    | 220                                | _    | 200    | 1    | mA   |

#### NOTES:

- 1. All values are maximum guaranteed values.

- 2. At f = fMax, address inputs are cycling at the maximum frequency of read cycles of 1/tnc. f = 0 means no input lines are changing.

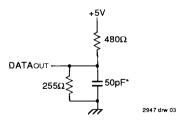

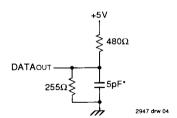

# **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise/Fall Times         | 5ns               |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

| Output Load                   | See Figures 1 & 2 |

# **CAPACITANCE**

$\{TA = +25^{\circ}C, f = 1.0 \text{ MHz}, SOJ \text{ package only}\}$

| Symbol | Parameter <sup>(1)</sup>    | Condition | Max. | Unit |

|--------|-----------------------------|-----------|------|------|

| CIN    | Input Capacitance           | VIN = 0V  | 7    | рF   |

| Ct/O   | Input/Output<br>Capacitance | VOUT = 0V | 7    | pF   |

NOTE:

2947 tbl 09

2947 tbl 10

This parameter is determined by device characterization but is not production tested.

Figure 1. Output Load

Figure 2. Output Load (for tohz, tchz, tolz and tclz)

\*including scope and jig

10.4-3

#### **FUNCTIONAL DESCRIPTION**

The IDT71589 is a very fast 32K x 9 CMOS static Cache-RAM with internal edge-triggered registers dedicated to the support of the 486 CPU. These registers support the fastest systems and allow a 128KB or larger cache to be designed to consume the smallest number of chips, the lowest power and board space, and allow the designer to avoid the use of expensive high-speed cache-tag RAMs and PALs.

The internal registers are designed to support two highspeed functions: Burst read cycles, and a late-abort self-timed write cycle.

Burst read cycles are accomplished through the assertion of the ADS signal with a valid address input during the rising edge of the clock input. This address will be used to access the data in the CacheRAM during the next clock cycle, and data will be output during the following three cycles in accordance with the 486's burst refill sequence (i.e., during the next cycle the address' LSB is inverted, then the second LSB is inverted as the LSB is restored to its original value, etc.). Since the CacheRAM contains this counter internally, the critical clockto-data time of even the fastest CPU speeds can be met by using a slower RAM speed grade without resorting to chipintensive interleaving schemes. Should the ADS signal be sampled as valid after having been sampled as invalid, any bursting in process will be reinitialized to the new address, and a new burst cycle will be started. The burst counter wraps around at the end of the sequence and continues to count until stopped by the ADS or CS inputs. A fast copy-back scheme can harness this capability by reading, then writing the four burst addresses within a single burst cycle.

The self-timed write cycle significantly eases the timing of the address and data inputs during a write cycle, and allows the write/don't write decision to be postponed until the very end of the second cycle of a write cycle. During a write cycle, the address will be strobed into the address register during the first rising edge of the clock after the ADS input becomes valid. Data is sampled into the data input register during the next cycle's rising edge, as is the write enable input. If a write has been enabled the data will be written from the address and input data registers into the CacheRAM during the high phase of the clock of that cycle.

A chip select pin is provided to give control over interruption of write cycles and burst read cycles. When the  $\overline{CS}$  input is used to interrupt a burst cycle, it operates as a synchronous input to the burst counter. A low level must be present on the chip select input and must satisfy data set-up and hold times in order for the counter to progress to its next state. To stop the counter at its current state, the chip select input must be taken high, and must stay high long enough to satisfy the CacheRAM's data set-up and hold times. The  $\overline{CS}$  pin also is used as an auxiliary to the  $\overline{WE}$  input. Writes can only be accomplished if both  $\overline{CS}$  and  $\overline{WE}$  are simultaneously sampled active.

The SOJ package allows for very effective space utilization as illustrated by the IDT Cache-SIMMs. The IDT7MP6086 offers 128KB in a 72-pin SIMM and the IDT7MP6085/7 offer 128KB/256KB in an 80-pin SIMM.

# AC ELECTRICAL CHARACTERISTICS (Vcc = 5.0V ± 5%, All Temperature Ranges)

|        |                                         | 7158 | 71589SA20 |      | 71589SA25 |      | 71589SA35 |      |

|--------|-----------------------------------------|------|-----------|------|-----------|------|-----------|------|

| Symbol | Parameter                               | Min. | Max.      | Min. | Max.      | Min. | Max.      | Unit |

| toyo   | Clock Cycle Time                        | 25   |           | 30   | _         | 40   |           | ns   |

| tch    | Clock Pulse High <sup>(1)</sup>         | 10   | _         | 11   | _         | 14   | _         | ns   |

| toL    | Clock Pulse Low(1)                      | 10   |           | 11   | _         | 14   | _         | ns   |

| tsp    | Set-up Time (ADS, WE, CS, Input Data)   | 3    | T —       | 4    | _         | 5    | _         | ns   |

| tHD    | Hold Time (ADS, WE, CS, Input Data)     | 2    |           | 2    | _         | 2    |           | ns   |

| tsa    | Address Set-up Time                     | 3    |           | 4    | _         | 5    |           | ns   |

| tha    | Address Hold Time                       | 2    |           | 2    |           | 2    | _         | ns   |

| tcD    | Clock to Data Valid                     |      | 19        | =    | 24        |      | 34        | ns   |

| toc    | Data Valid After Clock                  | 4    |           | 4    | _         | 5    | _         | ns   |

| toe    | Output Enable to Output Valid           | _    | 8         | =    | 9         |      | 10        | ns   |

| tolz   | Output Enable to Output in Low-Z(2,3)   | 2    | _         | 2    | _         | 2    |           | ns   |

| tonz   | Output Disable to Output in High-Z(2,3) |      | 8         |      | 9         |      | 10        | ns   |

### NOTES:

- 1. This parameter is measured as a HIGH time above 2.2V and LOW time below 0.8V.

- 2. Transition is measured ±200mV from steady state.

- 3. This parameter is guaranteed with the AC load (Figure 2), but is not production tested.

2947 tbl 11

10

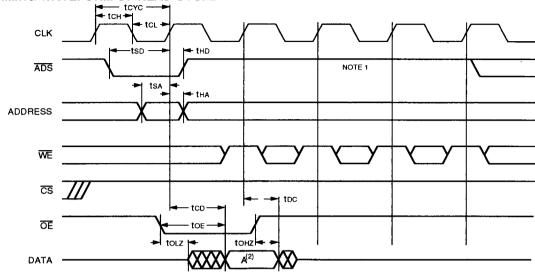

#### TIMING WAVEFORM OF READ CYCLE

#### NOTES:

1. If ADS goes LOW during a burst cycle, a new address will be loaded and another burst cycle will be started.

2947 drw 0

2. A-Data from address, counter is not imcremented to the next addresses. If CS is taken inactive during a burst read cycle, the burst counter will discontinue counting until CS input again goes active. The timing of the CS input for this control of the burst counter must satisfy setup and hold parameters tsp and thib. The output remains unchanged as long as the CS is inactive to advance the counter and as long as the OE reamins active.

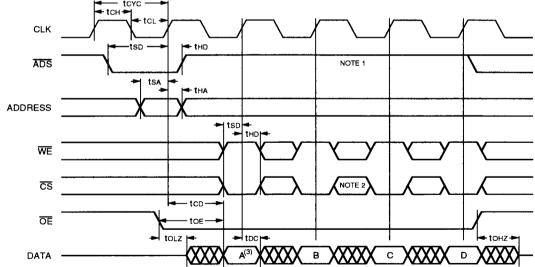

# TIMING WAVEFORM OF BURST READ CYCLE

#### NOTES:

1. If ADS goes LOW during a burst cycle, a new address will be loaded and another burst cycle will be started.

2947 drw 06

If CS is taken inactive during a burst read cycle, the burst counter will discontinue counting until CS input again goes active. The timing of the CS input for this control of the burst counter must satisfy setup and hold parameters tso and tab.

3. A-Data from input address. B-Data from input address except A<sub>0</sub> is now A

0. C-Data from input address except A<sub>1</sub> is now A

1. D-Data from input address except A<sub>2</sub> and A<sub>3</sub> are now A

2. D-Data from input address except A<sub>3</sub> and A<sub>4</sub> are now A

2. D-Data from input address except A<sub>2</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

2. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A<sub>3</sub> is now A

3. D-Data from input address except A

3. D-Data from i

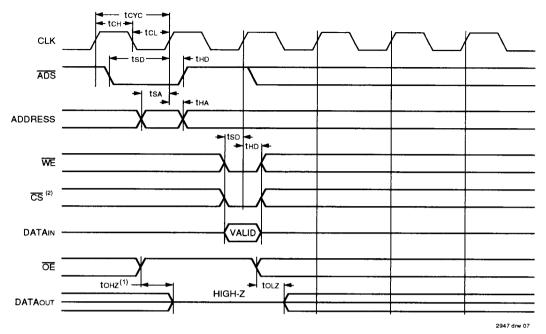

# TIMING WAVEFORM OF WRITE CYCLE

#### NOTES:

- OE must be taken inactive at least as long as toHz + tsA before the second rising clock edge of write cycle. CS timing is the same as any synchronous signal when used to block writes or to stop the burst count sequence.

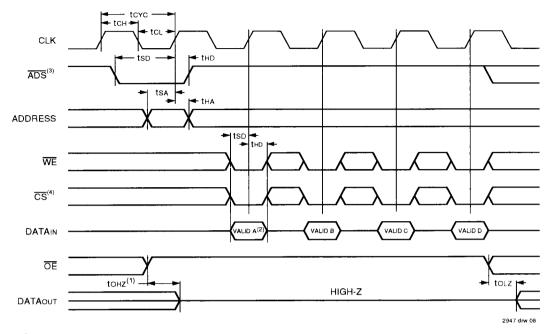

### TIMING WAVEFORM OF BURST WRITE CYCLE

# NOTES:

- 1. OE must be taken inactive at least as long as toHz + tsA before the second rising clock edge of write cycle.

- 2. A-Data to be written to original input address. B-Data to be written to original input address except A<sub>0</sub> is now A<sub>0</sub>. C-Data to be written to original input address except A<sub>0</sub> is now A<sub>0</sub>. C-Data to be written to original input address except A<sub>0</sub> and A<sub>1</sub> are now A<sub>0</sub> and A<sub>1</sub>.

- 3. If ADS goes low during a burst cycle, a new address will be loaded, and another burst cycle will be started.

- 4. If  $\overline{CS}$  is taken inactive during a burst write cycle the burst counter will discontinue counting until the  $\overline{CS}$  input again goes active. The timing of the  $\overline{CS}$  input for this control of the burst counter must satisfy setup and hold parameters tsp and the.  $\overline{CS}$  timing is the same as any synchronous signal when used to block writes or to stop the burst count sequence.

# **TRUTH TABLE**

| CLK      | Previous ADS | ADS | Address     | WE | cs | OE | 1/0     | Function                     |

|----------|--------------|-----|-------------|----|----|----|---------|------------------------------|

| 1        | Н            | L   | Valid Input | X  | Х  |    | -       | Preset Address Counter       |

| <b>1</b> | X            | Н   | _           |    | _  | _  |         | Ignore External Address Pins |

| 1        | L            | Х   | — <u> </u>  | _  |    | _  | _       | Ignore External Address Pins |

| <b>↑</b> | Х            | Н   | _           | _  | L  | _  | _       | Sequence Address Counter     |

| <u></u>  | į.           | Х   |             |    | L  |    | _       | Sequence Address Counter     |

| 1        | Х            | Н   |             |    | Н  |    | _       | Suspend Address Sequencing   |

| 1        | ٦            | X   |             | _  | Н  |    |         | Suspend Address Sequencing   |

|          | _            | _   | _           | _  | _  | H  | High-Z  | Outputs Disabled             |

| -        | _            | _   | _           | Н  |    | L  | DATAOUT | Read                         |

| 1        | X            | Н   |             | L  | L  | Н  | DATAIN  | Write                        |

| 1        | L            | Х   |             | L  | L  | Н  | DATAIN  | Write                        |

| _        | <del>-</del> | _   | _           | L  | L  | L  |         | Not Allowed                  |

NOTE:

H = HIGH L = LOW

X = Don't Care

- = Unrelated

High-Z = High Impedance

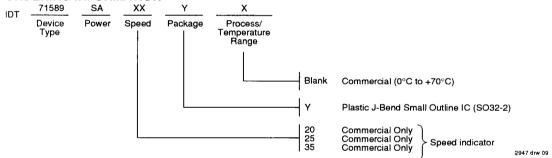

### ORDERING INFORMATION

2947 tbl 12