Data Sheet January 1999 File Number 3652.4

# **Digital Costas Loop**

The Digital Costas Loop (DCL) performs many of the baseband processing tasks required for the demodulation of BPSK, QPSK, 8-PSK, OQPSK, FSK, AM and FM waveforms. These tasks include matched filtering, carrier tracking, symbol synchronization, AGC, and soft decision slicing. The DCL is designed for use with the HSP50110 Digital Quadrature Tuner to provide a two chip solution for digital down conversion and demodulation.

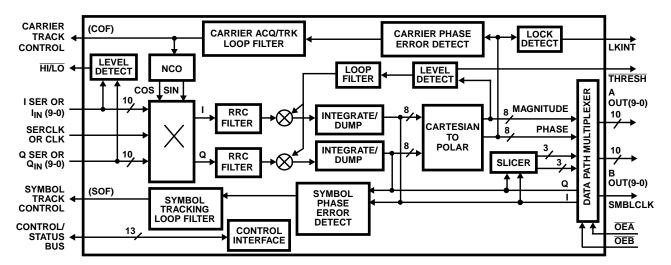

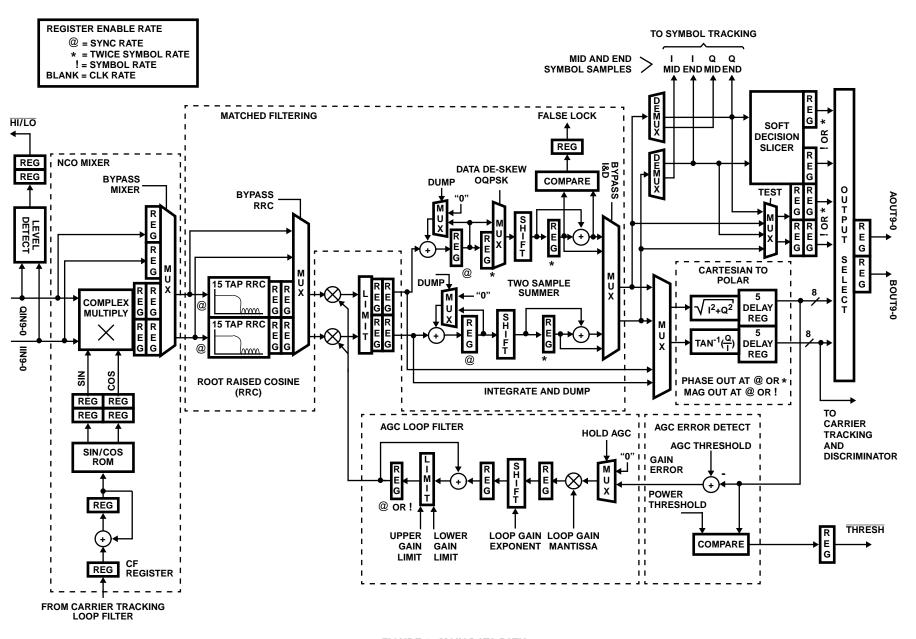

The DCL processes the In-phase (I) and quadrature (Q) components of a baseband signal which have been digitized to 10 bits. As shown in the block diagram, the main signal path consists of a complex multiplier, selectable matched filters, gain multipliers, cartesian-to-polar converter, and soft decision slicer. The complex multiplier mixes the I and Q inputs with the output of a quadrature NCO. Following the mix function, selectable matched filters are provided which perform integrate and dump or root raised cosine filtering ( $\alpha \sim 0.40$ ). The matched filter output is routed to the slicer, which generates 3-bit soft decisions, and to the cartesian-to-polar converter, which generates the magnitude and phase terms required by the AGC and Carrier Tracking Loops.

The PLL system solution is completed by the HSP50210 error detectors and second order Loop Filters that provide carrier tracking and symbol synchronization signals. In applications where the DCL is used with the HSP50110, these control loops are closed through a serial interface between the two parts. To maintain the demodulator performance with varying signal power and SNR, an internal AGC loop is provided to establish an optimal signal level at the input to the slicer and to the cartesian-to-polar converter.

#### **Features**

- · Clock Rates Up to 52MHz

- Selectable Matched Filtering with Root Raised Cosine or Integrate and Dump Filter

- Second Order Carrier and Symbol Tracking Loop Filters

- Automatic Gain Control (AGC)

- Discriminator for FM/FSK Detection and Discriminator Aided Acquisition

- · Swept Acquisition with Programmable Limits

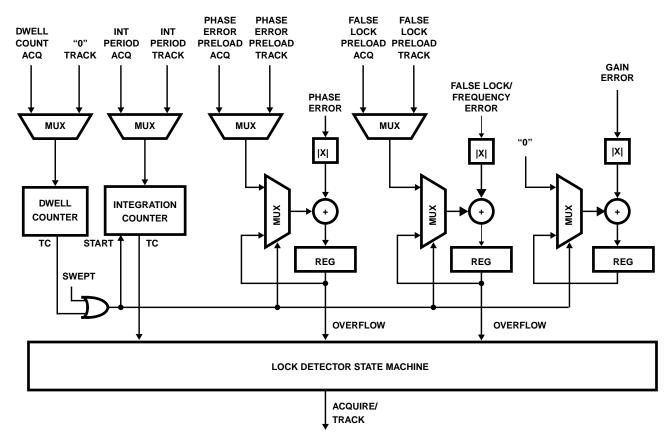

- Lock Detector

- Data Quality and Signal Level Measurements

- · Cartesian to Polar Converter

- 8-Bit Microprocessor Control Status Interface

- Designed to work with the HSP50110 Digital Quadrature Tuner

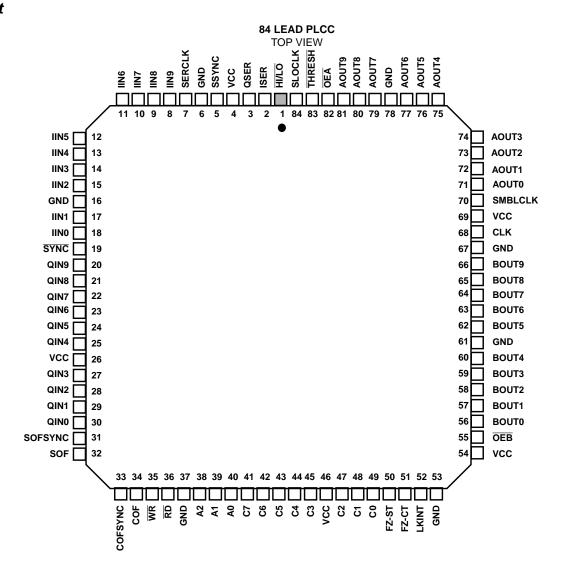

- 84 Lead PLCC

# **Applications**

- Satellite Receivers and Modems

- BPSK, QPSK, 8-PSK, OQPSK, FSK, AM and FM Demodulators

- · Digital Carrier Tracking

- Related Products: HSP50110 Digital Quadrature Tuner, D/A Converters HI5721, HI5731, HI5741

- HSP50110/210EVAL Digital Demod Evaluation Board

# **Block Diagram**

#### **Pinout**

# **Ordering Information**

| PART NUMBER   | TEMP.<br>RANGE (°C) | PACKAGE      | PKG.<br>NO. |

|---------------|---------------------|--------------|-------------|

| HSP50210JC-52 | 0 to 70             | 84 Lead PLCC | N84.1.15    |

| HSP50210JI-52 | -40 to 85           | 84 Lead PLCC | N84.1.15    |

# Pin Description

| NAME            | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | -    | +5V Power Supply.                                                                                                                                                                                                                                                                                                    |

| GND             | -    | Ground.                                                                                                                                                                                                                                                                                                              |

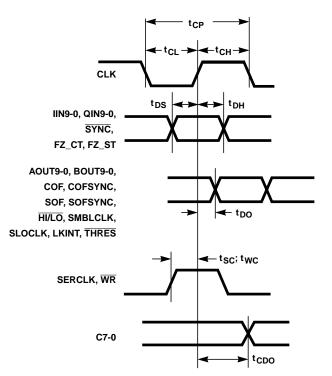

| IIN9-0          | I    | In-Phase Parallel Input. Data may be two's complement or offset binary format (see Table 14). These inputs are sampled by CLK when the SYNC signal is active Low. IIN9 is the MSB. See Input Controller Section.                                                                                                     |

| QIN9-0          | I    | Quadrature Parallel Input. Data may be two's complement or offset binary format (see Table 14). These inputs are sampled by CLK when the SYNC signal is active Low. QIN9 is the MSB. See Input Controller Section.                                                                                                   |

| SYNC            | I    | Data Sync. When SYNC is asserted "Low", data on IIN9-0 and QIN9-0 is clocked into the processing pipeline by the rising edge of CLK.                                                                                                                                                                                 |

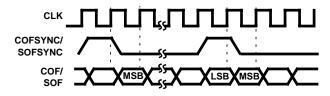

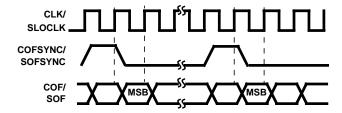

| COF             | 0    | Carrier Offset Frequency. The frequency term generated by the Carrier Tracking Loop Filter is output serially via this pin. The new offset frequency is shifted out MSB first by CLK or SLOCLK starting with the clock cycle after the assertion of COFSYNC.                                                         |

| COFSYNC         | 0    | Carrier Offset Frequency Sync. This signal is asserted one CLK or SLOCLK cycle before the MSB of the serial data word. (Programmable Polarity, see Table 41, bit 11).                                                                                                                                                |

| SOF             | 0    | Sampler Offset Frequency. Sample frequency correction term generated by the Symbol Tracking Loop Filter is output serially via this pin. The frequency word is shifted out MSB first by CLK or SLOCLK starting with the clock cycle after assertion of SOFSYNC.                                                      |

| SOFSYNC         | 0    | Sampler Offset Frequency Sync. This signal is asserted one CLK or SLOCLK cycle before the MSB of the serial data word. (Programmable Polarity, see Table 41, bit 12).                                                                                                                                                |

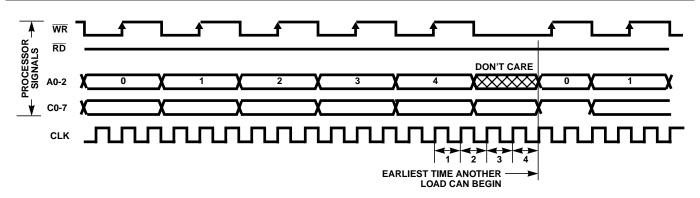

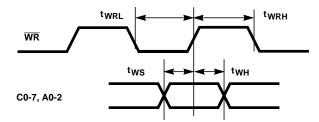

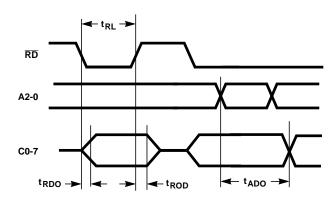

| A2-0            | I    | Address Bus. The address on these pins specify a target register for reading or writing (see Microprocessor Interface Section). A0 is the LSB.                                                                                                                                                                       |

| C7-0            | I/O  | Microprocessor Interface Data Bus. This bi-directional bus is used for reading and writing to the processor interface. These are the data I/O pins for the processor interface. C0 is the LSB.                                                                                                                       |

| WR              | I    | Write. This is the write strobe for the processor interface (see Microprocessor Interface Section).                                                                                                                                                                                                                  |

| RD              | I    | Read. This is the read enable for the processor interface (see Microprocessor Interface Section).                                                                                                                                                                                                                    |

| FZ_ST           | I    | Freeze Symbol Tracking Loop. Asserting this pin "high" zeroes the sampling error into the Symbol Tracking Loop Filter (see Symbol Tracking Loop Filter Section).                                                                                                                                                     |

| FZ_CT           | I    | Freeze Carrier Tracking Loop. Asserting this pin "high" zeroes the carrier Phase Error input to the Carrier Tracking Loop Filter.                                                                                                                                                                                    |

| LKINT           | 0    | Lock Detect Interrupt. This pin is asserted "high" for at least 4 CLK cycles when the Lock Detector Integration cycle is finished (see Lock Detector Section). Used as an interrupt for a processor. The Lock Detect Interrupt may be asserted "high" longer than 4 CLK cycles, depending on the Lock Detector mode. |

| THRESH          | 0    | Threshold Exceeded. This output is asserted "low" when the magnitude out of the Cartesian to Polar converter exceeds the programmable Power Detect Threshold (see Table 15 and AGC Section).                                                                                                                         |

| SLOCLK          | 0    | Slow Clock. Optional serial clock used for outputting data from the Carrier and Symbol Tracking Loop Filters. The clock is programmable and has a 50% duty cycle. <i>Note: Not used when the HSP50110 is used with the HSP50210</i> (see <i>Table 41</i> ).                                                          |

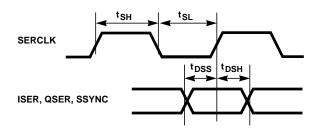

| ISER            | I    | In-Phase Serial Input. Serial data input for In-Phase Data. Data on this pin is shifted in MSB first and is synchronous to SERCLK (see Input Controller Section).                                                                                                                                                    |

| QSER            | I    | Quadrature Serial Input. Serial data input for Quadrature Data. Data on this pin is shifted in MSB first and is synchronous to SERCLK (see Input Controller Section).                                                                                                                                                |

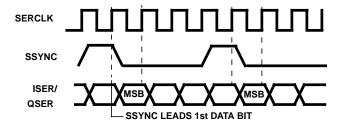

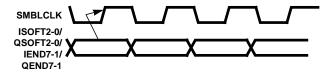

| SSYNC           | I    | Serial Word Sync. This input is asserted "high" one CLK before the first data bit of the serial word (see Figure 2).                                                                                                                                                                                                 |

| SERCLK          | I    | Serial Clock. May be asynchronous to other clocks. Used to clock in serial data (see Input Controller Section).                                                                                                                                                                                                      |

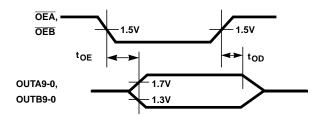

| AOUT9-0         | 0    | A Output. Data on this output depend on the configuration of Output Selector. AOUT9 is the MSB (see Table 42).                                                                                                                                                                                                       |

| BOUT9-0         | 0    | B Output. Data on this output depend on the configuration of Output Selector. BOUT9 is the MSB (see Table 42).                                                                                                                                                                                                       |

| SMBLCLK         | 0    | Symbol Clock. 50% duty cycle clock aligned with soft bit decisions (see Figure 19).                                                                                                                                                                                                                                  |

| OEA             | I    | A Output Enable. This pin is the three-state control pin for the AOUT9-0. When $\overline{\text{OEA}}$ is high, the AOUT9-0 is high impedance.                                                                                                                                                                       |

| ŌĒB             | I    | B Output Enable. This pin is the three-state control pin for the BOUT9-0. When $\overline{\text{OEB}}$ is high, the AOUT9-0 is high impedance.                                                                                                                                                                       |

| HI/LO           | 0    | HI/LO. The output of the Input Level Detector is provided on this pin (see Input Level Detector Section). This signal can be externally averaged and used to control the gain of an amplifier to close an AGC loop around the A/D converter. This type of AGC sets the level based on the median value on the input. |

| CLK             | 1    | System Clock. Asynchronous to the processor interface and serial inputs.                                                                                                                                                                                                                                             |

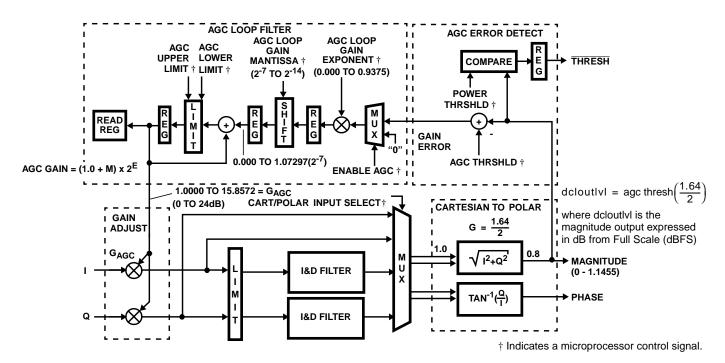

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM OF THE HSP50210

# Functional Description

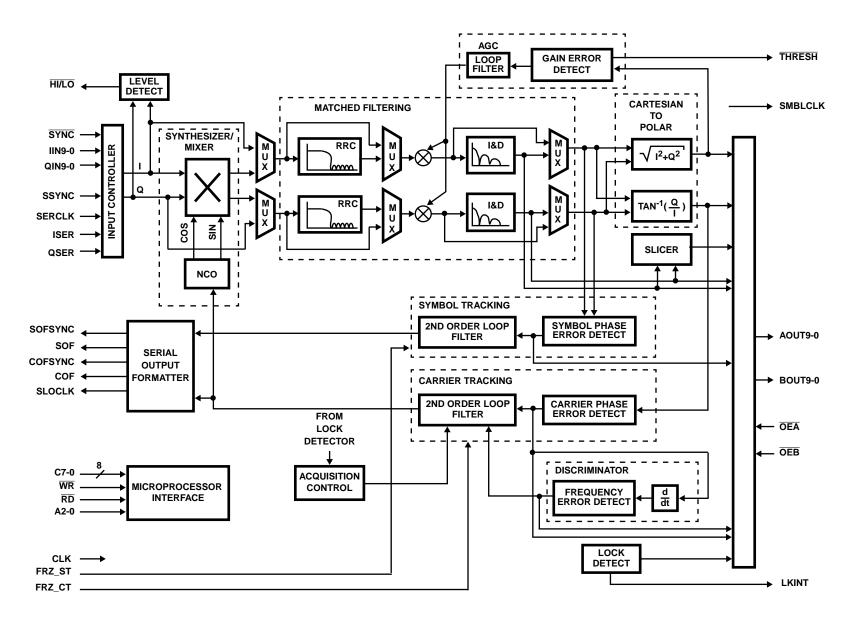

The HSP50210 Digital Costas Loop (DCL) contains most of the baseband processing functions needed to implement a digital Costas Loop Demodulator. These functions include LO generation/mixing, matched filtering, AGC, carrier phase and frequency error detection, timing error detection, carrier loop filtering, bit sync loop filtering, lock detection, acquisition/tracking control, and soft decision slicing for forward error correction algorithms. While the DCL is designed to work with the HSP50110 Digital Quadrature Tuner (DQT) as a variable rate PSK demodulator for satellite demodulation, functions on the chip are common to many communications receivers.

The DCL provides the processing blocks for the three tracking loops commonly found in a data demodulator: the Automatic Gain Control (AGC) loop, the Carrier Tracking Loop, and a Symbol Tracking Loop. The AGC loop adjusts for input signal power variations caused by path loss or signal-to-noise variations. The carrier tracking loop removes the frequency and phase uncertainties in the carrier due to oscillator inaccuracies and doppler. The symbol tracking loop removes the frequency and phase uncertainties in the data and generates a recovered clock synchronous with the received data. Each loop consists of an error detector, a loop filter, and a frequency or gain adjustment/control. The AGC loop is internal to the DCL, while the symbol and carrier tracking loops are closed external to the DCL. When the DCL is used together with the HSP50110, the tracking loops are closed around the baseband filtering to center the signal in the filter bandwidth. In addition, the AGC function is divided between the two chips with the HSP50110 providing the coarse AGC, and the HSP50210 providing the fine or final AGC.

A top level block diagram of the HSP50210 is shown in Figure 1. This diagram shows the major blocks and the multiplexers used to reconfigure the data path for various architectures.

# Input Controller

In-Phase (I) and Quadrature (Q) data enters the part through the Input Controller. The 10-bit data enters in either serial or parallel fashion using either two's complement or offset binary format. The input mode and binary format is set in the Data Path Configuration Control Register, bits 14 and 15 (see Table 14).

If Parallel Input mode is selected, I and Q data are clocked into the part through IIN0-9 and QIN0-9 respectively. Data enters the processing pipeline when the input enable (SYNC) is sampled "low" by the processing clock (CLK). The enable signal is pipelined with the data to the various processing elements to minimize pipeline delay where possible. As a result, the pipeline delay through the AGC, Carrier Tracking, and Symbol Tracking Loop Filters is measured in CLKs; not input data samples.

If serial input mode is selected, the I and Q data enters via the ISER and QSER pins using SERCLK and SSYNC. The beginning of a serial word is designated by asserting SSYNC 'high' one SERCLK prior to the first data bit, as shown in Figure 2. On the following SERCLK's, data is shifted into the register until all 10 bits have been input. Data shifting is then disabled and the contents of the register are held until the next assertion of SSYNC. The assertion of a SSYNC transfers data into the processing pipeline, and the Shift Register is enabled to accept new data on the following SERCLK. When data is transferred to the processing pipeline by SSYNC, a processing enable is generated which follows the data through the pipeline. This enable allows the delay through processing elements (like the loop filters) to be minimized since their pipeline delay is expressed in CLKs not SSYNC periods. Note: SSYNC should not be asserted for more than one SERCLK cycle.

OTE: Data must be loaded MSB first.

IGURE 2. SERIAL INPUT TIMING FOR ISER AND QSER INPUTS

#### Input Level Detector

The Input Level Detector generates a one-bit error signal for an external IF AGC filter and amplifier. The error signal is generated by comparing the magnitude of the input samples to a user programmable threshold. The HI/LO pin is then driven "high" or "low" depending on the relationship of its magnitude to the threshold. The sense of the HI/LO pin is programmable so that a magnitude exceeding the threshold can either be represented as a "high" or "low" logic state. The Input Level Detector (HI/LO output) threshold and the sense are set by the Data Path Configuration Control Register bits 16-23 and 13 (see Table 14). *Note: The Input Level Detector is typically not used in applications which use the HSP50210 with the HSP50110.*

The high/low outputs can be integrated by an external loop filter to close an AGC loop. Using this method, the gain of the loop forces the median magnitude of the input samples to the threshold. When the magnitude of half of the samples is above the threshold (and half is below), the error signal is integrated to zero by the loop filter.

The magnitude of the complex input is estimated by:

Mag (I, Q) =

$$|I|$$

+ 0.375 ×  $|Q|$  if I > Q and (EQ. 1)

Mag (I, Q) =  $|Q|$  + 0.375 ×  $|I|$  if Q > I

3-6

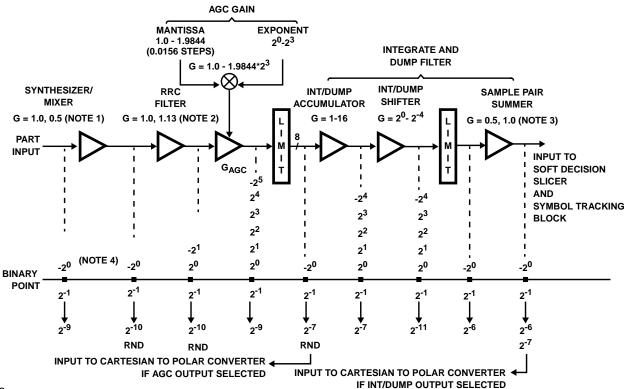

FIGURE 3. MAIN DATA PATH

#### NCO/Mixer

The NCO/Mixer performs a complex multiply between the baseband input and the output of a quadrature NCO (Numerically Controlled Oscillator). When the HSP50210 (DQT) is used with the HSP50110 (DCL), the NCO/Mixer shortens the Carrier Tracking Loop (i.e., minimizes pipeline delay around the loop) while providing wide loop bandwidths. This becomes important when operating at symbol rates near the maximum range of the part.

There are three configurations possible for closing the Carrier Tracking Loop when the DQT and the DCL are used together. The first configuration utilizes the NCO on the DQT and bypasses the NCO in the DCL. The Data Path Configuration Control Register (see Table 14), bit 10, and Carrier Loop Filter Control Register #1 (see Table 20), bit 6, are used to bypass the DCL NCO/Mixer and route the Loop filter outputs, respectively. The DQT provides maximum flexibility in NCO control with respect to frequency and phase offsets.

The second configuration feeds the lead Carrier Loop filter term to the DCL NCO/Mixer, and the lag Loop filter Term to the DQT NCO. This reduces the loop transport delay while maintaining wide loop bandwidths and reasonable loop damping factors. This configuration is especially useful in SATCOM applications with medium to high symbol rates. The Carrier Loop Filter Control Register #1, bit 5, is where the lead/lag destination is set.

The final configuration feeds both the lead and lag Carrier Loop Filter terms back to the DCL NCO/Mixer. This provides the shortest transport delay. The DCL NCO/Mixer provides only for frequency/phase control from the Carrier Loop filter. The center frequency of this NCO/Mixer is set to the average of the Upper and Lower Carrier Loop Limits programmable parameters. These parameters are set in the two control registers bearing their names (see Tables 22 and 23).

The NCO/Mixer uses a complex multiplier to multiply the baseband input by the output of a quadrature NCO. This operation is represented by:

$$I_{OIIT} = I_{IN} \cos(\omega_{C}) - Q_{IN} \sin(\omega_{C})$$

(EQ. 2)

$$Q_{OLIT} = I_{IN} \sin(\omega_C) + Q_{IN} \cos(\omega_C)$$

(EQ. 3)

Equation 3 illustrates how the complex multiplier implicitly performs the summing function when the DCL is configured as a modulator. The quadrature outputs of the NCO are generated by driving a sine/cosine look-up table with the output of a phase accumulator as shown in Figure 3. Each time the phase accumulator is clocked, its sum is incremented by the contents of the Carrier Frequency (CF) Register. As the accumulator sum increments from 0 to  $2^{32}$ , the SIN/COS ROM produces quadrature outputs whose phase advances from 0 to  $360^{\circ}$ . The CF Register contains a 32-bit phase increment which is updated with the output of

Carrier Tracking Loop. Large phase increments take fewer clocks to step through the sine wave cycle, which results in a higher frequency NCO output.

The CF Register sets the NCO frequency with the following equation:

$$F_C = f_{CLK} \times (CF)/2^{32}$$

(EQ. 4)

$CF = INT[(F_C/f_{CLK})2^{32}]H$

where f<sub>CLK</sub> is the CLK frequency, and CF is the 32-bit two's complement hexadecimal value loaded into the Carrier Frequency Register. As an example, if the CF Register is loaded with a value of 4000 0000 (Hex), and the CLK frequency is 40MHz, the NCO would produce quadrature terms with a frequency of 10MHz. When CF is a negative value, a clockwise cos/sin vector rotation is produced. When CF is positive, a counterclockwise vector rotation is produced.

NOTE: The NCO is set to a fixed frequency by programming the upper and lower limits of the Carrier Tracking Loop Filter to the same value and zeroing the lead gain.

# **Matched Filtering**

The HSP50210 provides two selectable matched filters: a Root Raised Cosine Filter (RRC) and an Integrate and Dump (I&D) filter. These are shown in Figure 3. The RRC filter is provided for shaped data pulses and the I&D filter is provided for square wave data. The filters may be cascaded for better adjacent channel rejection for square wave data. If these two filters do not meet baseband filtering requirements, then they can be bypassed and an external digital filter (such as the HSP43168 Dual FIR Filter or the HSP43124 Serial I/O Filter) used to implement the desired matched filter. The desired filter configuration is set in the Data Path Configuration Control Register, bits 1-7 (see Table 14).

The sample rate of the baseband input depends on the symbol rate and filtering configuration chosen. In configurations which bypass both filters or use only the RRC Filter, the input sample rate must be twice the symbol rate. In configurations which use the I&D Filter, the input sample rate is decimated by the I&D Filter, down to two samples per symbol. I&D configurations support input sample rates up to 32 times the input symbol rate.

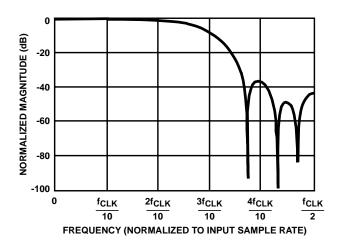

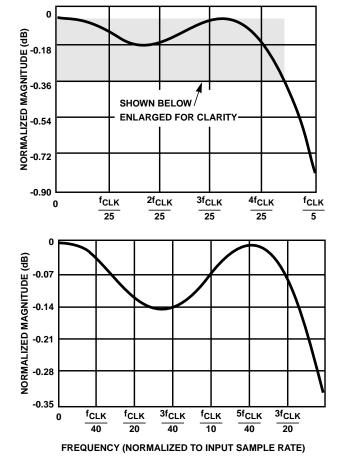

The RRC filter is a fixed coefficient 15 Tap FIR filter. It has ~40% excess bandwidth beyond Nyquist which equates to  $\alpha$  = ~0.4 shape factor. The filter frequency response is shown in Figure 4 and Figure 5. In addition, the 9-bit filter coefficients are listed as integer values in Table 1. The noise equivalent bandwidth of the RRC filter and other filter configurations possible with the HSP50110/210 chipset are given in Appendix A.

FIGURE 4. RRC FILTER IN HSP50210

FIGURE 5. PASSBAND RIPPLE OF RRC FILTER IN HSP50210

**TABLE 1. ROOT RAISED COSINE COEFFICIENTS**

| TABLE 1. ROOT RAISED COSINE COLITICIENTS |             |  |  |  |  |  |

|------------------------------------------|-------------|--|--|--|--|--|

| COEFFICIENT INDEX                        | COEFFICIENT |  |  |  |  |  |

| 0                                        | 2           |  |  |  |  |  |

| 1                                        | -2          |  |  |  |  |  |

| 2                                        | 1           |  |  |  |  |  |

| 3                                        | 8           |  |  |  |  |  |

| 4                                        | -16         |  |  |  |  |  |

| 5                                        | -14         |  |  |  |  |  |

| 6                                        | 86          |  |  |  |  |  |

| 7                                        | 160         |  |  |  |  |  |

| 8                                        | 86          |  |  |  |  |  |

| 9                                        | -14         |  |  |  |  |  |

| 10                                       | -16         |  |  |  |  |  |

| 11                                       | 8           |  |  |  |  |  |

| 12                                       | 1           |  |  |  |  |  |

| 13                                       | -2          |  |  |  |  |  |

| 14                                       | 2           |  |  |  |  |  |

The I&D filter consists of an accumulator, a programmable shifter and a two sample summer as shown in Figure 3. The programmable shifter is provided to compensate for the gain introduced by the accumulator (see Table 14). The accumulator provides Integrate and Dump Filtering for decimation factors up to 16. The two sample summer provides the moving average required for an additional decimation factor of 2. A decimation factor of 1 (bypass), 2, 4, 8, 16, or 32 may be selected. At the maximum decimation rate, a baseband signal sampled at 32 times the symbol rate can be filtered.

The output of the two sample summer is demultiplexed into two sample streams at the symbol rate. The demultiplexed data streams from the I and Q processing paths are fed to the Symbol Tracking Block and Soft decision slicer. The multiplexed data streams on I and Q are provided as one of the selectable inputs for the Cartesian to Polar Converter.

#### Cartesian/Polar Converter

The Cartesian/Polar Converter maps samples on the I and Q processing paths to their equivalent phase/magnitude representation. The magnitude conversion is equivalent to:

Mag (I, Q) =

$$(0.81)*\sqrt{(I^2 + Q^2)}$$

, (EQ. 5)

where 0.81 is the gain of the conversion process. The magnitude output is an 8-bit unsigned value ranging from 0.0 to 1.9922.

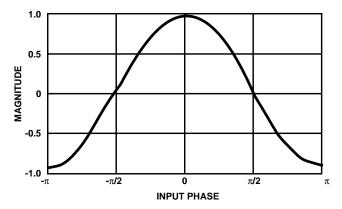

The phase conversion is equivalent to:

Phase (I, Q) =

$$\tan^{-1}(Q/I)$$

, (EQ. 6)

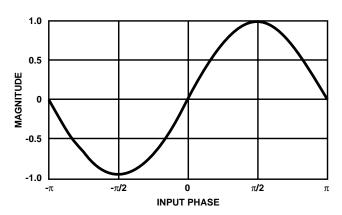

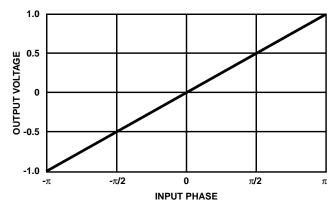

where  $tan^{-1}($ ) is the arctangent function. The phase conversion output is an 8-bit two's complement output which ranges from -1.0 to 0.9922 (80 to 7f HEX, respectively). The -1 to almost 1 range of the phase output represents phase values from - $\pi$  to  $\pi$ , respectively. An example of the I/Q to phase mapping is shown in Figure 6. The phase and magnitude values may be output via the Output Selector bits 0-3 (see Table 42).

FIGURE 6A. I INPUT TO CARTESIAN/POLAR CONVERTER

FIGURE 6B. Q INPUT TO CARTESIAN/POLAR CONVERTER

FIGURE 6C. CARTESIAN/POLAR CONVERTER PHASE OUTPUT

The I/Q data path selected for input to the Cartesian to Polar converter determines the input data rate of the AGC and carrier tracking loops. If the I/Q data path out of the Integrate and Dump Filter is selected, the AGC is fed with magnitude values produced by the end-symbol samples. Magnitude values produced by midsymbol samples are not used because these samples occur on symbol transitions, resulting in poor signal magnitude estimates. The Carrier Tracking block is fed with phase values generated from both the end and mid-symbol samples. The carrier tracking loop filter, however, is only fed with Phase Error terms generated by the end symbol samples. If the input of the I&D is selected for input to the coordinate converter, the control loops are fed with data at the I/Q data rate. The desired data path input to the Cartesian to Polar converter is specified in the Data Path Configuration Control Register, bit 8 (see Table 14).

### **AGC**

The AGC loop operates on the main data path (I and Q) and performs three signal level adjusting functions: 1) maximizing dynamic range, 2) compensating for SNR variations, and 3) maintaining an optimal level into the Soft Decision Slicer. The AGC Loop Block Diagram, shown in Figure 7, consists of an Error Detector, a Loop Filter, and Signal Gain Adjusters (multipliers). The AGC Error Detector generates an error signal by subtracting the programmable AGC threshold from the magnitude output of the Cartesian to Polar Converter. This difference signal is scaled (gain adjusted via multiplier and shifter), then filtered (integrated) by the AGC Loop Filter to generate the gain correction to the I and Q signals at the multipliers. If a fixed gain is desired, set the upper and lower limits equal.

The AGC responds to the magnitude of the sum of all the signals in the bandpass of the narrowest filter preceding the Cartesian to Polar Coordinate Converter. This filter may be the Integrate and Dump filter shown in Figure 8, the RRC filter upstream in the HSP50210 data path, or some other filter outside the DCL chip. The magnitude signal usually contains several components: 1) the signal of interest component, 2) the noise component, and 3) interfering signals component. At high SNR's the signal of interest is significantly greater than the other components. At lower SNR's, components 2 or 3 may become greater than the signal of interest. Narrowing the filter bandwidth is the primary technique used to mitigate magnitude contributions of component 3. This will also improve the SNR by reducing the magnitude contributions of element 2. Consideration of the range of signal amplitudes expected into the HSP50210, in conjunction with a gain distribution analysis, will provide the necessary insight to set the signal level into the Soft Decision Slicer to yield optimum performance. Note: Failure to consider the variations due to noise or interfering signals, can result in signal limiting in the HSP50210 processing algorithms, which will degrade the system Bit Error Rate performance.

The AGC Loop is configured by the Power Detect Threshold and AGC Loop Parameters Control Registers (see Tables 15 and 16). Seven programmable parameters must be set to configure the AGC Loop and its status outputs. Two parameters, the Power Threshold and the AGC Threshold are associated with the Error Detector and are represented in 8-bit fractional unsigned binary format:  $2^0.2^{-1}2^{-2}2^{-3}2^{-4}2^{-1}$ <sup>5</sup>2<sup>-6</sup>2<sup>-7</sup>. While the format provides a range from 0 - 1.9961 for the thresholds, the Cartesian to Polar Converter scales the I and Q input magnitudes by 0.81. Thus, if a full scale (±1) complex (I and Q) input signal is presented to the converter, the output will be  $\sqrt{(0.81)^2 + (0.81)^2} = 1.1455$ . The AGC Threshold parameter value is the desired magnitude of the signal as it enters the Soft Decision Slicer. It is the parameter that will determine the error signal in the AGC loop. The Power Threshold, on the other hand, determines only the power threshold at which the THRESH signal is asserted. If the signal magnitude exceeds the threshold, then the THRESH is asserted. This may be used for signal detection, power detection or external AGC around the A/D converter. The AGC Threshold parameter is set in the AGC Loop Parameters Control Register, bits 16-23 (see Table 16). The Power Threshold parameter is set in the Power Detect Threshold Control Register, bits 0-7 (see Table 15). Note that these two threshold parameters are not required to be set to identical or even related values, since they perform independent functions

The Enable AGC parameter sets the AGC Error Detector output to zero if asserted and to normal error detection output when not asserted. This control bit is set in the AGC Loop Parameter Control Register, bit 31 (see Table 16). This bit is used to disable the AGC loop.

The remaining AGC parameters determine the AGC loop characteristics: gain tracking, tracking rate and tracking limits. The AGC Loop gain is set via two parameters: AGC Loop Gain Exponent and AGC Loop Gain Mantissa. In general, the higher the loop gain, the faster signal level acquisition and tracking, but this must be tempered by the specific signal characteristics of the application and the remaining programmable loop parameters. For the HSP50210, the AGC Loop Gain provides for a variable attenuation of the input to the loop filter. The AGC gain mantissa is a 4-bit value which provides error signal scaling from 0.000 to 0.9375, with a resolution of 0.0625. Table 2 details the discrete set of decimal values possible for the AGC Loop Gain mantissa. The

exponent provides a shift factor scaling from 2<sup>-7</sup> to 2<sup>-14</sup>. Table 3 details the discrete set of decimal values possible for the AGC Loop Gain Exponent. When combined, the exponent and mantissa provide a loop gain defined as:

AGC Loop Gain:

$$G_{AGC} = [(M)(2^{-4})][(2^{-(7+E)})]$$

(EQ. 7)

where M is a binary number with a range from 0 to 15 and E is a 3-bit binary value from 0 to 7. M and E are the parameters set in the AGC Loop Parameters Control Register, bits 24-30 (see Table 16). The composite range of the AGC loop Gain is 0.0000 to [0.9375][2-7]. This will scale the AGC error signal to a range of 0.000 to (1.1455)(0.9375)(2-7) = 1.07297(2-7).

TABLE 2. AGC LOOP GAIN BINARY MANTISSA TO DECIMAL SCALED MANTISSA MAPPING

| BINARY<br>CODE<br>(MMMM) | DECIMAL<br>SCALED<br>MANTISSA | BINARY<br>CODE<br>(MMMM) | DECIMAL<br>SCALED<br>MANTISSA |

|--------------------------|-------------------------------|--------------------------|-------------------------------|

| 0000                     | 0.0000                        | 1000                     | 0.5000                        |

| 0001                     | 0.0625                        | 1001                     | 0.5625                        |

| 0010                     | 0.1250                        | 1010                     | 0.6250                        |

| 0011                     | 0.1875                        | 1011                     | 0.6875                        |

| 0100                     | 0.2500                        | 1100                     | 0.7500                        |

| 0101                     | 0.3125                        | 1101                     | 0.8125                        |

| 0110                     | 0.3750                        | 1110                     | 0.8750                        |

| 0111                     | 0.4375                        | 1111                     | 0.9375                        |

TABLE 3. AGC LOOP BINARY EXPONENT TO SCALED DECIMAL EXPONENT MAPPING

| DEGIMAL EXPONENT MAIL ING |                       |                         |  |  |  |  |  |  |

|---------------------------|-----------------------|-------------------------|--|--|--|--|--|--|

| BINARY CODE<br>(EEE)      | DECIMAL/ HEX EXPONENT | DECIMAL SCALED EXPONENT |  |  |  |  |  |  |

| 000                       | 0                     | 2 <sup>-7</sup>         |  |  |  |  |  |  |

| 001                       | 1                     | 2 <sup>-8</sup>         |  |  |  |  |  |  |

| 010                       | 2                     | 2 <sup>-9</sup>         |  |  |  |  |  |  |

| 011                       | 3                     | 2 <sup>-10</sup>        |  |  |  |  |  |  |

| 100                       | 4                     | 2 <sup>-11</sup>        |  |  |  |  |  |  |

| 101                       | 5                     | 2 <sup>-12</sup>        |  |  |  |  |  |  |

| 110                       | 6                     | 2 <sup>-13</sup>        |  |  |  |  |  |  |

| 111                       | 7                     | 2 <sup>-14</sup>        |  |  |  |  |  |  |

FIGURE 7. AGC LOOP BLOCK DIAGRAM

The AGC Loop Filter integrates the scaled error signal to provide a correction control term to the multipliers in the I and Q path. The loop filter accumulator has internal upper and lower limiters. The upper eight bits of the accumulator output map to an exponent and mantissa format that is used to set these upper and lower limits. The format, illustrated in Figure 8, is used for the AGC Upper Limit, AGC Lower Limit and the Correction Control Term (AGC output). This format should not be confused with the similar format used for the AGC Loop Gain. The input to the AGC Loop Filter is included in Figure 8 to show the relative weighting of the input to output of the loop filter. The loop filter input is represented as the eleven letter "G"s. Lower case "e" and "m" detail the format for the AGC Upper and Lower Limits. This change in type case should help keep the AGC Limits and AGC Gain formats from being confused. The AGC Upper and Lower Limits are set in the AGC Loop Parameters Control Register, bits 0-15, (see Table 16). This 6-bit unsigned mantissa format provides for an AGC output control range from 0.0000 to 0.9844, with a resolution of 0.015625. The 2-bit exponent format provides an AGC output control range from 1 to 8. The decimal values for each of the 64 binary mantissa values is detailed in Table 4, while Table 5 details the decimal value for the 4 exponent values.

The AGC Output is implemented in the multiplier according to Equation 8.

$$Out_{AGC-linear} = (1.0 + m_{AGC})(2^{e})$$

(EQ. 8A)

$$Out_{AGC-dB} = 20 log [(1.0 + m_{AGC})(2^{e})]$$

(EQ. 8B)

where m and e are the binary values for mantissa and exponent found in Tables 4 and 5.

NOTE:This format is identical to the format used to program the AGC Upper and Lower Limits, but in this usage it is not a programmed value. It is a representation of the digital AGC output number which is presented to the Gain Adjuster (multipliers) to correct the gain of the I and Q data signals in the main data path.

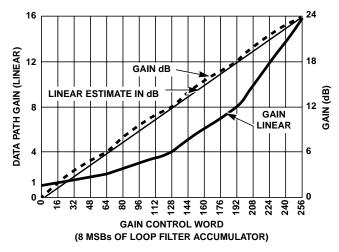

These equations yield a composite (mantissa and exponent) AGC output range of 0.0000 to 1.9844(2<sup>3</sup>) which is a logarithmic range from 0 to 24dB. Figure 9 has graphed the results of Equation 8 for both the linear and logarithmic equations. Figure 9 also has a linear estimate of the logarithmic equation. This linear approximation will be used in calculating the AGC response time.

$$2^1 2^0 .2^{-1} 2^{-2} 2^{-3} 2^{-4} 2^{-5} 2^{-6} 2^{-7} 2^{-8} 2^{-9} 2^{-10} 2^{-11} 2^{-12} 2^{-13} 2^{-14} 2^{-15} 2^{-16} 2^{-17} 2^{-18}$$

e e .m m m m m G G G G G G G G G G

FIGURE 8. AGC OUTPUT AND AGC LIMITS BIT WEIGHTING

TABLE 4. AGC GAIN MANTISSA TO DECIMAL MAPPING

| BINARY CODE<br>(MMMMMM <sub>AGC</sub> ) | DECIMAL<br>VALUE<br>OF AGC<br>MANTISSA | BINARY CODE<br>(MMMMMM <sub>AGC</sub> ) | DECIMAL<br>VALUE<br>OF AGC<br>MANTISSA |

|-----------------------------------------|----------------------------------------|-----------------------------------------|----------------------------------------|

| 000000                                  | 0.000000                               | 100000                                  | 0.500000                               |

| 000001                                  | 0.015625                               | 100001                                  | 0.515625                               |

| 000010                                  | 0.031250                               | 100010                                  | 0.531250                               |

| 000011                                  | 0.046875                               | 100011                                  | 0.546875                               |

| 000100                                  | 0.062500                               | 100100                                  | 0.562500                               |

| 000101                                  | 0.078125                               | 100101                                  | 0.578125                               |

| 000110                                  | 0.093750                               | 100110                                  | 0.593750                               |

| 000111                                  | 0.109375                               | 100111                                  | 0.609375                               |

| 001000                                  | 0.125000                               | 101000                                  | 0.625000                               |

| 001001                                  | 0.140625                               | 101001                                  | 0.640625                               |

| 001010                                  | 0.156250                               | 101010                                  | 0.656250                               |

| 001011                                  | 0.171875                               | 101011                                  | 0.671875                               |

| 001100                                  | 0.187500                               | 101100                                  | 0.687500                               |

| 001101                                  | 0.203125                               | 101101                                  | 0.703125                               |

| 001110                                  | 0.218750                               | 101110                                  | 0.718750                               |

| 001111                                  | 0.234375                               | 101111                                  | 0.734375                               |

| 010000                                  | 0.250000                               | 110000                                  | 0.750000                               |

| 010001                                  | 0.265625                               | 110001                                  | 0.765625                               |

| 010010                                  | 0.281250                               | 110010                                  | 0.781250                               |

| 010011                                  | 0.296875                               | 110011                                  | 0.796875                               |

| 010100                                  | 0.312500                               | 110100                                  | 0.812500                               |

| 010101                                  | 0.328125                               | 110101                                  | 0.828125                               |

| 010110                                  | 0.343750                               | 110110                                  | 0.843750                               |

| 010111                                  | 0.359375                               | 110111                                  | 0.859375                               |

| 011000                                  | 0.375000                               | 111000                                  | 0.875000                               |

| 011001                                  | 0.390625                               | 111001                                  | 0.890625                               |

| 011010                                  | 0.406250                               | 111010                                  | 0.906250                               |

| 011011                                  | 0.421875                               | 111011                                  | 0.921875                               |

| 011100                                  | 0.437500                               | 111100                                  | 0.937500                               |

| 011101                                  | 0.453125                               | 111101                                  | 0.953125                               |

| 011110                                  | 0.468750                               | 111110                                  | 0.968750                               |

| 011111                                  | 0.484375                               | 111111                                  | 0.984375                               |

TABLE 5. AGC GAIN EXPONENT TO DECIMAL MAPPING

| BINARY CODE | DECIMAL/ HEX EXPONENT | DECIMAL SCALED EXPONENT |

|-------------|-----------------------|-------------------------|

| 00          | 0                     | 2 <sup>0</sup>          |

| 01          | 1                     | 2 <sup>1</sup>          |

| 10          | 2                     | 2 <sup>2</sup>          |

| 11          | 3                     | 2 <sup>3</sup>          |

FIGURE 9. GAIN CONTROL TRANSFER FUNCTION

There are two techniques for setting a fixed gain for the AGC. The first is to set Control Word 2 bit 31 = 1. This precludes any error update of present AGC gain value. The second is to set the upper and lower AGC limits to the desired gain using Figure 9. The upper and lower limits have the same value for this case.

The HSP50210 provides two mechanisms for monitoring signal strength. The first, which involved the THRESH signal, has already been described. The second mechanism is via the Microprocessor Interface. The 8 most significant bits of the AGC loop filter output can be read by a microprocessor. Refer to the Microprocessor Interface Section for details of how to read this value. This AGC value has the format described in Figure 8.

# AGC Bit Weighting and Loop Response

The AGC loop response is a function of the programmable gain, the bit weightings inherent in the connection of each element of the loop, the AGC Loop filter limits and the magnitude of the input gain error step. Table 6 details the bit weighting between each element of the AGC Loop from the error detector through the weighting at the gain adjuster in the signal path. The AGC Loop Gain sets the growth rate of the sum in the loop filter accumulator. The Loop filter output growth rate determines how quickly the AGC loop traces the transfer function shown previously in Figure 9. To calculate the rate at which the AGC can adjust over a given period of time, a gain step is introduced to the gain error detector and the amount of change that is observed between clocks at the AGC Level Adjusters (multipliers) is the AGC response time in dB per symbol. This AGC loop will respond immediately with the greatest correction term, then asymptotically approach zero correction.

We begin calculation of the loop response with a full scale error detector input of  $\pm 1$ . This error input is scaled by the Cartesian to Polar converter, the error detector and the AGC Loop Gain, accumulated in the loop filter, limited and output to the gain adjusters. The AGC loop tries to make the error correction as quickly as possible, but is limited by the AGC

Loop Gain and potentially, the AGC limits. The maximum AGC response is the maximum gain adjustment made in any given clock cycle. This involves applying maximum Loop gain and setting the AGC limits as wide as possible. A calculation using

only exponent terms of the various gains will be sufficient to yield a rough order of magnitude of the range of the AGC Loop response. The results are shaded in the last column of Table 6 and provided in detail in Equations 9A and 9B.

**TABLE 6. AGC BIT WEIGHTING**

| AGC<br>ACCUM<br>BIT<br>POSITION | GAIN<br>ERROR<br>INPUT | GAIN<br>ERROR<br>BIT<br>WEIGHT | AGC LOOP<br>FILTER GAIN<br>(MANTISSA) | AGC LOOP<br>FILTER<br>GAIN<br>MULTIPLIER<br>(OUTPUT) | AGC<br>LOOP<br>FILTER<br>GAIN BITS<br>KEPT<br>(rnd) |      | SHIFT<br>= 0            | SHIFT<br>= 7                 | OI<br>AN<br>LIM | AGC<br>JTPUT<br>D AGC<br>ITS BIT<br>EIGHT | AGC GAIN<br>RESOLUTION<br>(dB) |

|---------------------------------|------------------------|--------------------------------|---------------------------------------|------------------------------------------------------|-----------------------------------------------------|------|-------------------------|------------------------------|-----------------|-------------------------------------------|--------------------------------|

| 22                              |                        |                                |                                       |                                                      |                                                     |      |                         | $\text{Shifter} \rightarrow$ | Е               | 1                                         | 12                             |

| 21                              |                        |                                |                                       |                                                      |                                                     |      |                         | $\text{Shifter} \rightarrow$ | Е               | 0                                         | 6                              |

| 20                              |                        |                                |                                       |                                                      |                                                     | М    | ultiplier $ ightarrow$  |                              | М               | -1                                        | 3                              |

| 19                              |                        |                                |                                       |                                                      |                                                     |      |                         |                              | М               | -2                                        | 1.5                            |

| 18                              |                        |                                |                                       |                                                      |                                                     |      |                         |                              | М               | -3                                        | 0.75                           |

| 17                              |                        |                                |                                       |                                                      |                                                     |      |                         |                              | М               | -4                                        | 0.375                          |

| 16                              |                        |                                |                                       |                                                      |                                                     |      |                         |                              | М               | -5                                        | 0.1875                         |

| 15                              |                        |                                |                                       |                                                      |                                                     | М    | ultiplier $\rightarrow$ | 1                            | М               | -6                                        | 0.09375                        |

| 14                              |                        |                                |                                       |                                                      |                                                     |      |                         | 0•                           | •               | 0-7                                       | 0.04688                        |

| 13                              |                        |                                |                                       |                                                      |                                                     |      |                         | 1                            | G               | -8                                        | 0.02344                        |

| 12                              |                        |                                |                                       |                                                      |                                                     |      |                         | 2                            | G               | -9                                        | 0.01172                        |

| 11                              |                        |                                |                                       |                                                      |                                                     |      |                         | 3                            | G               | -10                                       | 0.00586                        |

| 10                              |                        |                                |                                       |                                                      |                                                     |      |                         | 4                            | G               | -11                                       | 0.00293                        |

| 9                               |                        |                                |                                       |                                                      |                                                     |      |                         | 5                            | G               | -12                                       | 0.00146                        |

| 8                               | 8(S)                   | = 1(S)                         | 0.                                    | 12(S)                                                | 12(S)                                               | = 1  | 1                       | 6                            | G               | -13                                       | 0.000732                       |

| 7                               | 7                      | = 0•                           | х                                     | 11                                                   | 11                                                  | = 0• | 0•                      |                              | G               | -14                                       | 0.000366                       |

| 6                               | 6                      | = 1                            | х                                     | 10                                                   | 10                                                  | = 1  | 1                       |                              | G               | -15                                       | 0.000183                       |

| 5                               | 5                      | = 2                            | х                                     | 9                                                    | 9                                                   | = 2  | 2                       |                              | G               | -16                                       | 0.0000916                      |

| 4                               | 4                      | = 3                            | х                                     | 8                                                    | 8                                                   | = 3  | 3                       |                              | G               | -17                                       | 0.0000458                      |

| 3                               | 3                      | = 4                            |                                       | 7                                                    | 7                                                   | = 4  | 4                       |                              | G               | -18                                       | 0.0000229                      |

| 2                               | 2                      | = 5                            |                                       | 6                                                    | 6                                                   | = 5  | 5                       |                              |                 | -19                                       | 0.0000114                      |

| 1                               | 1                      | = 6                            |                                       | 5                                                    | 5                                                   | = 6  | 6                       |                              |                 | -20                                       | 0.00000572                     |

| 0                               | 0                      | = 7                            |                                       | 4                                                    |                                                     |      |                         |                              |                 | -21                                       | 0.00000286                     |

|                                 |                        |                                |                                       | 3                                                    |                                                     |      |                         |                              |                 |                                           |                                |

|                                 |                        |                                |                                       | 2                                                    |                                                     |      |                         |                              |                 |                                           |                                |

|                                 |                        |                                |                                       | 1                                                    |                                                     |      |                         |                              |                 |                                           |                                |

|                                 |                        |                                |                                       | 0                                                    |                                                     |      |                         |                              |                 |                                           |                                |

AGC Response<sub>MAX</sub> = Input (Cartesian to Polar Converter Gain)(Error Detector Gain)(AGC Loop Gain)(AGC Output Weighting)

AGC Response<sub>MAX</sub> =

$$\pm 1(0.5)(0.5)(2^{-7})(24) = \pm 1(2^{-9})(24) = 0.04688$$

dB/symbol time

(EQ. 9A)

where (0.5) is the MSB of the 0.81 scaling in the Cartesian to Polar Coordinate Converter, (0.5) is the MSB of the mantissa of the Loop Gain, (2<sup>-7</sup>) is the maximum shift gain, and 24 is the maximum loop filter gain.

A similar procedure is used to calculate the minimum AGC response rate.

AGC Response<sub>MIN</sub> =

$$\pm 1(0.5)(0.5)(2^{-14})(24) = \pm 1(2^{-16})(24) = 0.000366$$

dB/symbol time

(EQ. 9B)

Thus, the expected range for the AGC rate is approximately 0.0004 to 0.0469dB/symbol time.

#### NOTES:

- 1. If the Mixer is enabled the result of the complex multiply is scaled by two (G = 0.5). If the mixer is bypassed, the data passes unmodified (G = 1.0).

- 2. If the Root Raised Cosine Filter is enabled, a gain of G = 1.13 is introduced. If the RRC filters bypassed, the gain is unity.

- 3. If the integrate and Dump Filter is bypassed the Sample Pair summer has a gain of G = 1.0 and the 2<sup>-7</sup>-bit position is set to 1. If the integrate and dump is enabled, the sample pair sum is scaled by one half (G = 0.5).

- 4. The negative sign on the MSBs indicates use of 2's complement data format.

#### FIGURE 10. GAIN DISTRIBUTION AND INTERMEDIATE BIT WEIGHTINGS

## **Gain Distribution**

The gain distribution in the DCL is shown in Figure 10. These gains consist of a combination of fixed, programmable, and adaptive gains. The fixed gains are introduced by processing elements such as the Mixer and Square Root of Root Raised Cosine Filter. The adaptive gains are set to compensate for variations in input signal strength.

The main signal path, with processing block gains and path bit weightings, is shown in Figure 10. The quadrature inputs to the HSP50210 are 10-bit fractional two's complement numbers with relative bit weightings, as shown in the Figure 10. The first element in the processing chain is the Mixer, which scales the quadrature outputs of the complex multiplier by 1/2 providing a gain of G=0.5. If the Mixer is bypassed, the signal is passed unmodified with a gain of 1.0. Following the mixer, the quadrature signal is passed to the fixed coefficient RRC filtering block, which has a gain of 1.13 if enabled and 1.0 if bypassed. Next, the AGC supplies gain to maintain an optimal signal level at the input to the Soft Decision Slicer, Cartesian to Polar Converter, and the Symbol Tracking Loop. The gain supplied by the AGC ranges from 1.0 to  $1.9844^*2^3$ .

Following the AGC, the signal path is limited to 8 bits and passed through the Integrate and Dump Filter en route to the Soft Decision Slicer and Symbol Tracking Block. The I&D Filter uses an accumulator together with a sample pair summer to achieve the desired decimation rate. The I&D shifter is provided to compensate for the gain introduced by the I&D Accumulator. The accumulator introduces gain equal to the decimation factor R, and the shifter gain can be set to 1/R. For example, if the I&D Filter decimation of 16 is chosen the I&D Accumulator will accumulate 8 samples before dumping, which produces a gain of 8. Thus, for unity gain, the I&D Shifter would be set for a gain of 2<sup>-3</sup>. The Sample Pair Summer is unity gain since its output is scaled by one-half.

# Symbol Tracking

The symbol tracking loop adjusts the baseband sampling frequency to force sampling of the baseband waveform at optimal points for data decisions. The key elements of this loop are the Sampling Error Detector and Symbol Tracking Loop Filter shown in Figure 11. The output of these two blocks is a frequency correction term which is used to adjust the baseband sample frequency external to the HSP50210. In typical applications, the frequency correction term is fed back to the HSP50110 to adjust baseband sampling via the Resampling NCO (see HSP50110 Datasheet).

**REGISTER ENABLE RATE** ! = SYMBOL RATE BLANK = CLK RATE SYMBOL TRACK **LOOP FILTER LEAD GAIN** LEAD **LEAD** LEAD **MANTISSA EXPONENT EXPONENT** ACQ ACQ **TRACK** LEAD **MANTISSA** FRZ\_ST → TRACK REG SAMPLING ERROR DETECTOR REG MUX **ZERO** TRANSITION LEAD MUX MUX DETECT DATA END DECISION **TRANSITION** MID-POINT SOF MID AND END SYMBOL SAMPLES SERIAL MID-SYMBOL MID OUTPUT FORMATTER SOFSYNC TRANSITION MUX DETECT MUX DATA MUX ZERO DECISION **END** TRANSITION то LAG SINGLE/ MUX REG → MID-POINT μP INTERFACE DOUBLE I LOAD REG REG RAIL Q ACC ACC LIMITS INVERT MID UPPER/LOWER MID-SYMBOL I SAMPLING REG REG I ERROR LAG ACCUMULATOR LAG LAG **EXPONENT EXPONENT** ACQ **TRACK** LAG LAG I MANTISSA **MANTISSA** ACQ TRACK LAG GAIN

FIGURE 11. SYMBOL TRACKING

# Sampling Error Detector

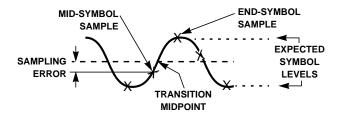

The Sampling Error Detector is a decision based error detector which determines sampling errors on both the I and Q processing paths. The detector assumes that it is fed with samples of the baseband waveform taken in the middle of the symbol period (mid-symbol sample) and between symbols (end-symbol sample) as shown in Figure 12. The sampling error is a measure of how far the mid-symbol sample is from the symbol transition mid-point. The transition mid-point is half way between two symbol decisions. The detector makes symbol decisions by comparing the end-symbol samples against a selectable threshold set (see Modulation Order Select bits 9-10 in Table 28). The error term is generated by subtracting the midsymbol sample from the transition mid-point. The sign of the error term is negated for negatively sloped symbol transitions. If no symbol transitions are detected the error detector output is zeroed. Errors on both the I and Q processing paths are summed and divided by two if Double Rail error detection is selected (see Symbol Tracking Configuration Control Register, bit 8: Table 28).

The sampling Error Detector provides an error accumulator to compensate for the processing rate of the loop filter. The error detector generates outputs at the symbol rate, but the loop filter can only accept inputs every eight  $f_{CLK}$  clocks. Thus, if the symbol rate is faster than 1/8 CLK, the error accumulator should be used to accumulate the error until the loop filter is ready for a new input. If the error accumulator is not used when the symbol rate exceeds 1/8 CLK, some error outputs will be missed. For example, if  $f_{CLK} = 40 \text{MHz}$ , then error accumulation is required for symbol rates greater than 5 MSPS ( $f_{CLK}/8$ ). *Note: The loop filter lead gain term must be scaled accordingly if the accumulator is used.*

FIGURE 12. TRACKING ERROR ASSOCIATED WITH

BASEBAND SAMPLING ON EITHER I OR Q RAIL

(BPSK/QPSK)

# Symbol Tracking Loop Filter

The Symbol Tracking Loop Filter is a second order lead/lag filter. The sampling error is weighted by the lag gain and accumulated to give the integral response (see Figure 11). The Lag Accumulator output is summed with the sampling error weighted by the Lead Gain. The result is a frequency term which is output serially, via the SOF output, to the NCO/VCO controlling the baseband sample rate (see Serial Output Section). In basic configurations, the SOF output of the HSP50210 is connected to the SOF input of the HSP50110.

Two sets of registers are provided to store the loop gain parameters associated with acquisition and tracking. The appropriate loop gain parameters are selected manually via the Microprocessor Interface or automatically via the Carrier Lock Detector. The loop filter's lead and lag gain terms are represented as a mantissa and exponent. The mantissa is a 4-bit value which weights the loop filter input from 1.0 to 1.9375. The exponent defines a shift factor that provides additional weighting from 2<sup>-1</sup> to 2<sup>-32</sup>. Together the loop gain mantissa and exponent provide a gain range between 2<sup>-32</sup> and ~1.0 as given by,

Lead/Lag Gain =

$$(1.0+M^2-^4)^2-(32-E)$$

(EQ. 10)

where M = a 4-bit binary number from 0 to 15, and E is a 5-bit binary value ranging from 0 to 31. For example, if M = 0101 and E = 00110, the Gain =  $1.3125*2^{-26}$ . They are stored in the Control Registers described in Table 31 and Table 32.

A limiter is provided on the lag accumulator output to keep the baseband sample rate within a user defined range (see Table 29 and Table 30). If the lag accumulator exceeds either the upper or lower limit, the accumulator is loaded with the limit. For additional loop filter control, the loop filter output can be frozen by asserting the FZ\_ST pin which null the sampling error term into the loop filter. The lag accumulator can be initialized to a particular value and can be read via the microprocessor interface as described in the Section "Reading from the Microprocessor Interface", and Table 33. The symbol tracking loop filter bit weighting is identical to the carrier tracking loop bit weighting, shown in Figures 9 and 10.

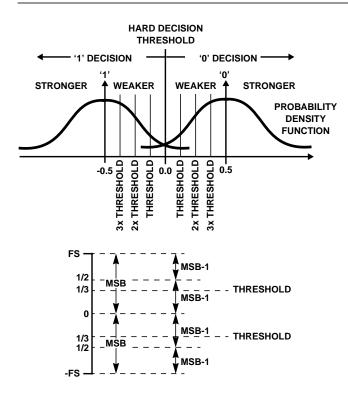

#### Soft Decision Slicer

The Soft Decision Slicer encodes the I/Q end-symbol samples into 3-bit soft decisions. The input to the slicer is assumed to be a bi-polar (2ary) baseband signal representing encoded values of either '1' or '0'. The most significant bit of the 3-bit soft decision represents a hard decision with respect to the mid-point between the expected symbol values. The 2 LSBs represent a level of confidence in the decision. They are determined by comparing the magnitude of the slicer input to multiples (1x, 2x, and 3x) of a programmable soft decision threshold (see Figure 13).

FIGURE 13. OVERLAY OF THE HARD/SOFT DECISION

THRESHOLDS ON THE SYMBOL PROBABILITY

DENSITY FUNCTIONS (PDFs) FOR BPSK/QPSK

SIGNALS)

The soft decision threshold represents a range of magnitude values from 0.0 to ~0.5. *Note: Since the input* to the slicer has a range of 0.0 to ~1.0, the threshold setting should be set to less than 1.0/3 = 0.33. This avoids saturation. The slicer decisions are output in either a two's complement or sign/magnitude format (see Soft Decision Slicer Configuration Control Register, bit 7: Table 40). The slicer input to output mapping for a range of input magnitudes is given in Table 7. For example, a negative input to the slicer whose magnitude is greater than twice the programmable threshold but less than 3x the threshold would produce a sign/magnitude output of 110 (BINARY). The I and Q inputs to the slicer are encoded into 3-bit soft decisions ISOFT(2-0) and QSOFT(3-0). These signals are routed to the OUTA(9-4) outputs by the Output Configuration Control Register Selector bits 0-3 (see Table 42).

TABLE 7. SLICER INPUT TO OUTPUT MAPPING

| RITY                     |                 | NPUT MAC        |                 | E L                      |                               |  |

|--------------------------|-----------------|-----------------|-----------------|--------------------------|-------------------------------|--|

| SIGNAL<br>INPUT POLARITY | 1x<br>THRESHOLD | 2x<br>THRESHOLD | 3x<br>THRESHOLD | SIGN/MAGNITUDE<br>OUTPUT | TWO'S<br>COMPLEMENT<br>OUTPUT |  |

| +                        | >               | >               | >               | 011                      | 011                           |  |

| +                        | >               | >               | ≤               | 010                      | 010                           |  |

| +                        | >               | ≤               | <               | 001                      | 001                           |  |

| +                        | ≤               | <               | <               | 000                      | 000                           |  |

| -                        | ≤               | <               | <               | 100                      | 111                           |  |

| -                        | >               | ≤               | <               | 101                      | 110                           |  |

| -                        | >               | >               | ≤               | 110                      | 101                           |  |

| -                        | >               | >               | >               | 111                      | 100                           |  |

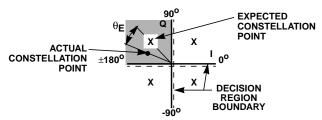

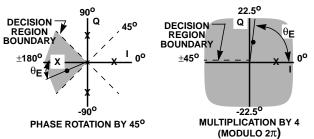

#### Carrier Phase Error Detector

The Carrier Phase Error is computed by removing the phase modulation from the phase output of the Cartesian to Polar Converter. To remove the modulation, the phase term is rotated and multiplied (modulo  $2\pi$ ) to fold the Phase Error into an arc centered about 00 but encompasses the whole plane, as shown in Figure 14. The phase rotation is performed by adding a 4-bit two's complement phase offset (resolution 22.5°) to the 4 MSBs of the 8-bit phase term. The multiplication is performed by left shifting the result from 0-3 positions with the MSB's discarded and zeros inserted into the LSB's. For example, Carrier Phase Error produces I/Q constellation points which are rotated from the expected constellation points as shown in Figure 14. By adding an offset of 45° (0010 0000 binary) and multiplying by 4 (left shift by two positions) the phase modulation is removed, and the error is folded into a 90° arc centered at  $0^{\circ}$ . The left axis represents a decision boundary of  $\pm 45^{\circ}$ C. implying the vertical axis is  $\pm 22.5^{\circ}$  as shown in Figure 14. The phase offset and shift factors required for different PSK orders is given in Table 8. Configuration of the Carrier Phase Error Detector is done via the Carrier Phase Error Detector Control Register, bits 0-5, (see Table 17). The Phase Error term may be selected for output via the Output Selector Configuration Control Register, bits 0-3 (see Table 42).

In applications where Phase Error terms are generated faster than the processing rate of the Carrier Loop Filter, an error accumulator is provided to accumulate errors until the loop filter is ready for a new input. Phase Error terms are generated at the rate I/Q samples are input to the Cartesian to Polar Converter. However, the Carrier Loop Filter can not accept new input faster than CLK/6 since six CLK(f<sub>CLK</sub>) clock edges are required to complete its processing cycle. If the error accumulator is not used and the I/Q sample rate exceeds CLK/6, error terms will be missed.

NOTE: The carrier Phase Error terms input to the loop filter are only generated from the end-symbol samples when the output of the I&D filter is selected for input to the Cartesian-to-Polar converter.

NOTE: The loop filter lead gain term must be scaled accordingly if the accumulator is used.

INPUT TO CARTESIAN/POLAR CONVERTER

PROJECTION OF PHASE ERROR (θ<sub>E</sub>) ABOUT 0°

FIGURE 14. PHASE ERROR DETECTOR OPERATION (QPSK)

TABLE 8. BASIC PHASE ERROR DETECTOR SETTINGS

| IABLE 6. DAGIC I HAGE ENNOW DETECTOR SETTINGS |                            |                  |                           |  |  |  |  |  |

|-----------------------------------------------|----------------------------|------------------|---------------------------|--|--|--|--|--|

| MODULATION<br>TYPE                            | PHASE<br>OFFSET            | SHIFT<br>FACTOR  | PHASE ER-<br>ROR<br>RANGE |  |  |  |  |  |

| CW                                            | 0° (00 HEX)                | 0 (no shift)     | ±180                      |  |  |  |  |  |

| BPSK                                          | 0° (00 HEX)                | 1 (left shift 1) | ±90                       |  |  |  |  |  |

| QPSK                                          | 45° (20 HEX)               | 2 (left shift 2) | ±45                       |  |  |  |  |  |

| 8-PSK                                         | 22.5 <sup>o</sup> (10 HEX) | 3 (left shift 3) | ±22                       |  |  |  |  |  |

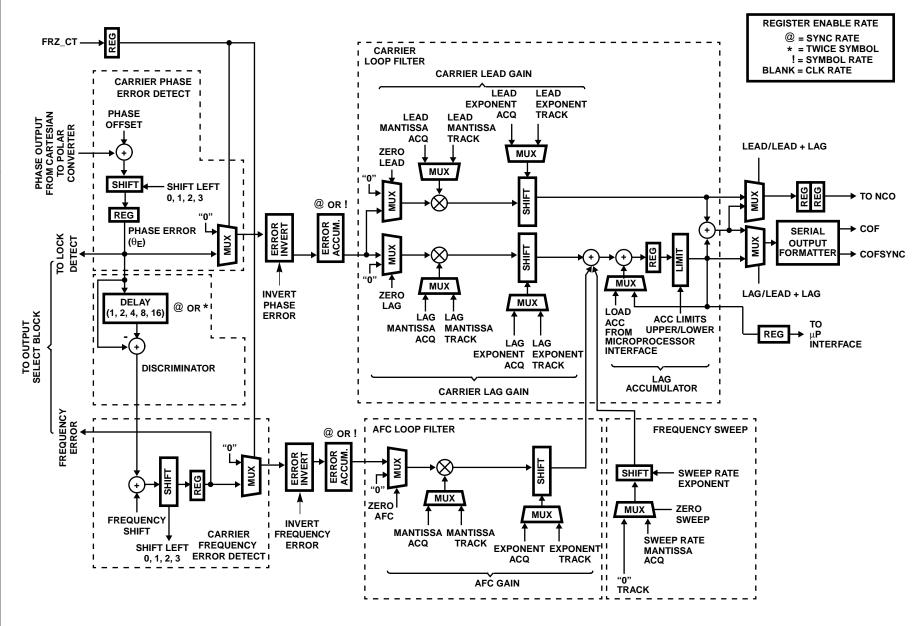

### Carrier Loop Filter

The Carrier Loop Filter is second order lead/lag filter as shown in Figure 14. The loop filter is similar to the Symbol Tracking Loop Filter except for the additional terms from the AFC Loop Filter and the Frequency Sweep Block. The output of the Lag Accumulator is summed with the weighted Phase Error term on the lead path to produce a frequency control term. The Carrier Loop Filter is configured for operation by the Control Registers described in Tables 20 to 27.

The Carrier Tracking Loop is closed by using the loop filter output to control the NCO or VCO used to down convert the channel of interest. In basic configurations, the frequency correction term controls the Synthesizer NCO in the HSP50110 Digital Quadrature Tuner via the COF and COFSYNC pins of the HSP50210's serial interface (see Serial Output Section). In applications where the carrier tracking is performed using the NCO on board the HSP50210, the loop filter output is fed to the on-board NCO as a frequency control.

The gain for the lead and lag paths of the Carrier Loop Filter are set through a programmable mantissa and exponent. The mantissa is a 4-bit value which weights the loop filter input from 1.0 to 1.9375. The exponent defines a shift factor that provides additional weighting from  $2^{-1}$  to  $2^{-32}$ . Together the loop gain mantissa and exponent provide a gain range between  $2^{-32}$  and  $\sim 1.0$  as given by,

Lead/Lag Gain =

$$(1.0+M^2-^4)^2-(32-E)$$

(EQ. 11)

where M = a 4-bit binary number from 0 to 15, and E is a 5-bit binary value ranging from 0 to 31. For example, if M = 0101 and E = 00110, the Gain =  $1.3125*2^{-26}$ . The loop gain mantissa and exponent are set in the Carrier Loop Gain Control Registers (see Tables 24 - 25).

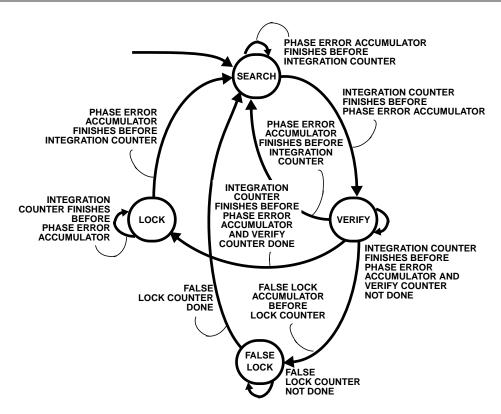

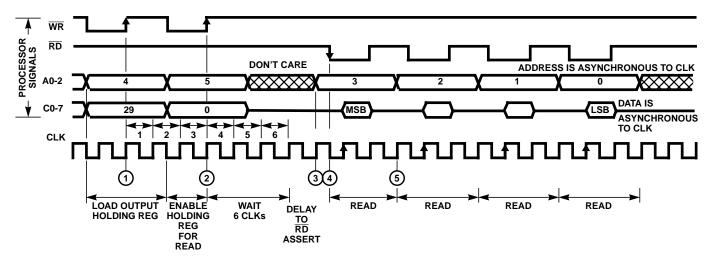

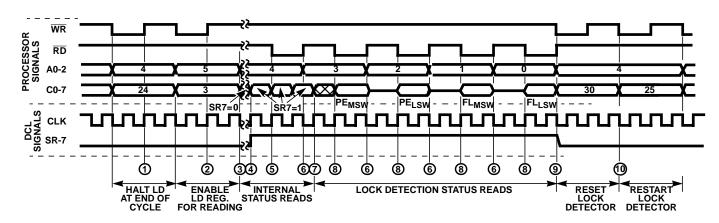

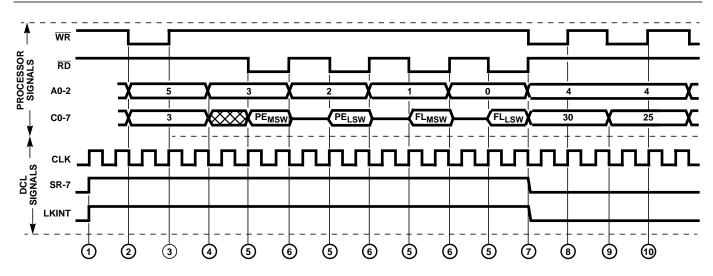

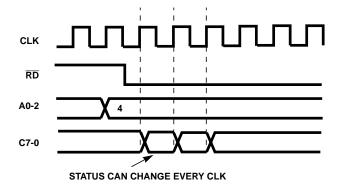

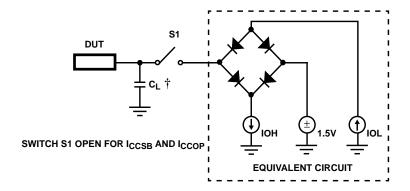

The Phase Error input to the Carrier Loop Filter is an 8-bit fractional two's complement number between ~1.0 to -1.0 (Format -2<sup>0</sup>. 2<sup>-1</sup>2<sup>-2</sup>2<sup>-3</sup>2<sup>-4</sup>2<sup>-5</sup>2<sup>-6</sup>2<sup>-7</sup>). Some LSB's are zero for BPSK, QPSK and 8-PSK. If minimum loop gain is used, the Phase Error is shifted in significance by 2<sup>-32</sup>. With maximum loop gain, the Phase Error is passed almost unattenuated. The output of the Carrier Loop filter is a 40-bit fractional two's complement number between ~1.0 and -1.0 (Format -2<sup>0</sup>. 2<sup>-1</sup>2<sup>-2</sup>2<sup>-3</sup>..... 2<sup>-39</sup>2<sup>-40</sup>). In typical applications, the 32 MSBs of the loop filter output represent the frequency control word needed to adjust the down converting NCO for phase lock. Tables 9 and 10 illustrate the bit weighting of the Carrier Loop Filter into the NCO for both tracking and acquisition sweep modes.