# Am186<sup>™</sup>CC/CH/CU

**Microcontrollers User's Manual**

This document amends the *Am186™CC/CH/CU Microcontrollers User's Manual*, order #21914B. It consists of these parts:

- "Documentation Defects and Corrections" on page 1 lists corrections to be made in page number order.

- "Changed Figures" on page 10 provides edited versions of changed tables and figures.

- An Index is included at the end of this amendment.

#### DOCUMENTATION DEFECTS AND CORRECTIONS

Table 1 on page 2 lists defects that have been found in the  $Am186 \ ^{\text{TM}}CC/CH/CU$  Microcontrollers User's Manual, order #21914B. Defects are listed in page order. Each entry lists the following:

- page number

- item to be corrected

- original text (or description of text to change)

- corrected text (or description of change to make)

- comment explaining the change

Entries that correct text in a diagram or figure do not contain the entire diagram or figure. If graphical

information is changed, the table refers to the page in this amendment where the changed figure can be found.

Square brackets ([]) are used to indicate a description of the text or change to be made, as opposed to the actual text.

Unchanged portions of a paragraph are replaced by an ellipsis (...) in entries where this might make the change easier to find. The whole paragraph is included if it is useful for understanding why the change was made.

| Page   | Item                                                                                          | Original Text                                                                                                                                                                                                                                                                                                                                                        | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Comment                                                                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapte | r 1 Architectural Overv                                                                       | view                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

| 1-10   | <b>1.4.3.2 General-<br/>Purpose DMA</b><br><b>Channels (Chapter 8)</b> ,<br>2nd paragraph     | External peripherals support DMA<br>transfers through the external DMA<br>request pins (DRQ1–DRQ0). Each<br>general-purpose channel accepts a<br>DMA request from one of three<br>sources: the DMA request signals<br>(DRQ1–DRQ0), Timer 2, or the<br>UARTs. (Note that Timer 2 acts only<br>as a DMA request source; no data is<br>transferred to or from Timer 2.) | External peripherals support DMA<br>transfers through the external DMA<br>request pins (DRQ1–DRQ0). Each<br>general-purpose channel can accept<br>synchronized DMA requests from<br>these sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, or<br>the UARTs. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.) In addition, system<br>software can initialize and start<br>unsynchronized DMA transfers | Note that this<br>paragraph<br>intentionally<br>omits USB as<br>a DMA<br>request<br>source. USB<br>requests are<br>mentioned<br>in the<br>subsequent<br>paragraph in<br>the manual. |

| Chapte | r 3 System Overview                                                                           |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

| 3-5    | <b>3.4 Initialization and</b><br><b>Reset</b> , 3rd paragraph<br>from bottom, 2nd<br>sentence | Pins are latched on the deassertion<br>of RES, and therefore are not<br>affected by an internal watchdog-<br>timer-generated reset.                                                                                                                                                                                                                                  | Some pin states are latched only on<br>the deassertion of RES, and<br>therefore are not affected by an<br>internal watchdog-timer-generated<br>reset.                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| 3-16   | Table 3-7 SignalDescriptions, Reservedpins                                                    | On the Am186CH HDLC<br>microcontroller, the RSVD_75 pin<br>should be tied externally to V <sub>SS</sub> .                                                                                                                                                                                                                                                            | Some pins are reserved only on certain microcontrollers or in a particular pinstrap configuration.                                                                                                                                                                                                                                                                                                                                                                       | Clarify<br>reserved pin<br>usage.                                                                                                                                                   |

|        |                                                                                               | On the Am186CH HDLC<br>microcontroller, pins RSVD_75,<br>RSVD_76, RSVD_80, RSVD_81,<br>and RSVD_101–RSVD_104 and are<br>reserved.                                                                                                                                                                                                                                    | On the Am186CH HDLC<br>microcontroller, pins RSVD_75,<br>RSVD_76, RSVD_80, RSVD_81,<br>and RSVD_101–RSVD_104 are<br>reserved.                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                     |

|        |                                                                                               | On the Am186CC and Am186CU<br>microcontrollers, pins RSVD_101–<br>RSVD_104 are reserved unless<br>pinstrap {USBXCVR} is sampled Low<br>on the rising edge of RESET.                                                                                                                                                                                                  | On the Am186CC and Am186CU<br>microcontrollers, pins RSVD_101–<br>RSVD_104 are reserved unless<br>pinstrap {USBXCVR} is sampled Low<br>on the rising edge of RESET.                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                     |

|        |                                                                                               | On the Am186CU USB<br>microcontroller, pins RSVD_119–<br>RSVD_116 are reserved.                                                                                                                                                                                                                                                                                      | On the Am186CU USB<br>microcontroller, pins RSVD_119–<br>RSVD_116 are reserved.                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

|        |                                                                                               | All other reserved pins should not be connected.                                                                                                                                                                                                                                                                                                                     | With one exception, all reserved pins<br>should be left unconnected. The<br>exception is that, on the Am186CH<br>HDLC microcontroller, the RSVD_75<br>pin should be tied externally to V <sub>SS</sub> .                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

| Chapte | r 7 Interrupts                                                                                |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

| 7-20   | 7.5.7 Software-Related<br>Considerations,<br>second bullet                                    | Writing a zero to the appropriate<br>channel bit in the Interrupt Request<br>(REQST) register clears the pending<br>interrupt. This facility provides a<br>simple way to clear a spurious edge-<br>triggered interrupt that may have<br>occurred when initially configuring a<br>PIO pin as an interrupt source.                                                     | Writing a zero to the appropriate<br>channel bit in the Interrupt Request<br>(REQST) register clears the pending<br>edge-triggered interrupt. This facility<br>provides a simple way to clear a<br>spurious edge-triggered interrupt that<br>may have occurred when initially<br>configuring a PIO pin as an interrupt<br>source. Note that for level-triggered<br>interrupts, the interrupt source must<br>be cleared to clear the interrupt.                           |                                                                                                                                                                                     |

Table 1. Corrections to the Am186™CC/CH/CU Microcontrollers User's Manual, Rev. B

| Page   | Item                                                                                                     | Original Text                                                                                                                                                                                                                                                                                     | Change To                                                                                                                                                                                                                                                                                                                                                                                           | Comment                                          |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

| Chapte | Chapter 8 DMA Controller                                                                                 |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  |  |  |  |

| 8-1    | <b>8.1 Overview</b> , end of fourth paragraph, marked "CC"                                               | Each general-purpose channel<br>accepts a DMA request from one of<br>four sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, the<br>UARTs, or the USB peripheral<br>controller. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.) | Each general-purpose channel can<br>accept synchronized DMA requests<br>from four sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, the<br>UARTs, or the USB peripheral<br>controller. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.) In addition, system<br>software can initialize and start<br>unsynchronized DMA transfers. |                                                  |  |  |  |

| 8-1    | 8.1 Overview, end of<br>fifth paragraph, marked<br>"CH"                                                  | Each general-purpose channel<br>accepts a DMA request from one of<br>three sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, or<br>the UARTs. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.)                                  | Each general-purpose channel can<br>accept synchronized DMA requests<br>from four sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, or<br>the UARTs. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.) In addition, system<br>software can initialize and start<br>unsynchronized DMA transfers.                                   |                                                  |  |  |  |

| 8-2    | End of partial first<br>paragraph (marked<br>"CU" on the manual's<br>previous page)                      | Each general-purpose channel<br>accepts a DMA request from one of<br>four sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, the<br>UARTs, or the USB peripheral<br>controller. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.) | Each general-purpose channel can<br>accept synchronized DMA requests<br>from four sources: the DMA request<br>signals (DRQ1–DRQ0), Timer 2, the<br>UARTs, or the USB peripheral<br>controller. (Note that Timer 2 acts<br>only as a DMA request source; no<br>data is transferred to or from<br>Timer 2.) In addition, system<br>software can initialize and start<br>unsynchronized DMA transfers. |                                                  |  |  |  |

| 8-18   | Figure 8-4 Source-<br>Synchronized<br>General-Purpose<br>DMA Transfers, cycle<br>labels at top of figure | Fetch Cycle Fetch Cycle                                                                                                                                                                                                                                                                           | Fetch Cycle Deposit Cycle                                                                                                                                                                                                                                                                                                                                                                           | Second phase<br>of transfer is<br>deposit cycle. |  |  |  |

| 8-19   | Last paragraph on page                                                                                   | A DMA request is not acknowledged<br>from the same source for four<br>processor clock cycles after the end<br>of the deposit cycle. In a source-<br>synchronized DMA transfer, the DRQ<br>signal must be deasserted at least<br>four clocks before the end of the<br>transfer                     | In a source-synchronized DMA<br>transfer, the DRQ signal must be<br>deasserted at least four clocks before<br>the end of the transfer                                                                                                                                                                                                                                                               | Delete first<br>sentence of<br>paragraph.        |  |  |  |

Table 1. Corrections to the Am186<sup>™</sup>CC/CH/CU Microcontrollers User's Manual, Rev. B (Continued)

| Table 1. Corrections to the Am186™CC/CH/CU Microcontrollers User's Manual, Rev. B (Continued) |

|-----------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------|

| Page | Item                                                     | Original Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Comment                |

|------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 8-20 | First paragraph on page                                  | A destination-synchronized transfer<br>differs from a source-synchronized<br>transfer in that the four cycle delay<br>allows the destination device to<br>deassert its DRQ signal four clocks<br>before another request is latched.<br>Without this delay, the destination<br>device would not have time to<br>deassert its DRQ signal. Because of<br>the four extra cycles, a destination-<br>synchronized DMA channel allows<br>other bus masters to take the bus<br>during the idle states. | A destination-synchronized transfer<br>differs from a source-synchronized<br>transfer in that a destination-<br>synchronized DRQ is masked off for<br>four cycles after the deassertion of<br>the WR signal. This allows an<br>external or internal device to use WR,<br>in conjunction with chip selects or<br>address lines, to signal the end of the<br>deposit cycle. The destination-<br>synchronized device must then<br>deassert DRQ within four cycles in<br>order to signal that the device is not<br>ready for the next DMA transfer.<br>While the destination-synchronized<br>DRQ is masked off, the bus can be<br>accessed by the CPU or other,<br>possibly lower priority, bus masters. | Rewrite the paragraph. |

| 8-25 | Next to last paragraph<br>on page, last two<br>sentences | For this reason, the High-Speed<br>UART has an additional Overrun<br>Error-Immediate (OERIM) interrupt<br>bit that is not placed in the FIFO.<br>Software can monitor or interrupt on<br>OERIM to detect and correct this sort<br>of system programming error.                                                                                                                                                                                                                                 | For this reason, the High-Speed<br>UART has additional Overrun Error-<br>Immediate (OERIM) and Break<br>Immediate (BRKIM) interrupt bits that<br>are not placed in the FIFO. When the<br>receive FIFO is enabled, software<br>can monitor or interrupt on OERIM or<br>BRKIM to detect and correct this sort<br>of system programming error.                                                                                                                                                                                                                                                                                                                                                          | Add BRKIM<br>bit.      |

|      |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>Note:</b> The BRKIM bit is not available<br>in parts released prior to revision C1.<br>For processor revision information,<br>see the PRL register description in<br>the Am186CC/CH/CU Register Set<br>Manual, order #21916B [and its<br>amendment, order #21916B/1].                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

| 8-28 | 8.5.7.3 SmartDMA™                                        | [Existing third paragraph]                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | [Add note after paragraph]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |

|      | Channel Memory<br>Overview, third<br>paragraph           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note: The SmartDMA channel<br>descriptor rings must reside in 16-bit<br>memory. The buffers pointed to by<br>the descriptors can be in either 8-bit<br>or 16-bit memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

| Table 1. | Corrections to the A | Am186™CC/CH/CU | Microcontrollers | User's Manual | Rev. B | (Continued) |

|----------|----------------------|----------------|------------------|---------------|--------|-------------|

| Page   | Item                                                                             | Original Text                                                                                                                                                                                                                                                                                                                                                         | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Comment                                |

|--------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 8-43   | 8.5.9 Software-Related<br>Considerations                                         | Software must stop DMA operation<br>before writing to the GDxCON1<br>register, or the results are<br>unpredictable. Stopping the<br>SmartDMA channel has no effect<br>while a request is pending on the<br>channel. Before stopping the<br>channel, make sure the requesting<br>peripheral (HDLC channel or USB<br>endpoint) is stopped.                              | Software must stop DMA operation<br>before writing to the GDxCON1<br>register, or the results are<br>unpredictable.<br>Stopping the SmartDMA channel has<br>no effect while a request is pending<br>on the channel. Before stopping the<br>channel, make sure the requesting<br>peripheral (HDLC channel or USB<br>endpoint) is stopped.<br>If the requesting peripheral is<br>stopped by an error, the error handler<br>should stop the SmartDMA channel<br>before clearing the status bit.<br>Otherwise the SmartDMA request<br>might be reasserted before software<br>can stop the channel.                                                                                                                                                     |                                        |

| Chapte | r 9 Programmable I/O S                                                           | ignals                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                      |

| 9-2    | Figure 9-1 PIO<br>Operation Block<br>Diagram, pullup/<br>pulldown resistor value | 100K                                                                                                                                                                                                                                                                                                                                                                  | 50 k-Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Correct resistor value.                |

| 9-5    | 9.5.2 Defining the PIO<br>Signal as Input or<br>Output, last sentence<br>on page | The internal pullup and pulldown resistors each have a value of approximately 10 K $\Omega$ .                                                                                                                                                                                                                                                                         | The internal pullup and pulldown resistors each have a value of approximately 50 k Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| Chapte | r 11 Watchdog Timer                                                              |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| 11-1   | <b>11.1 Overview</b> , last sentence of first paragraph.                         | RESOUT signal, which is pulled<br>Low during an external reset and can<br>be pulled Low during an internal<br>reset.                                                                                                                                                                                                                                                  | RESOUT signal, which is pulled<br>High during an external reset and can<br>be pulled High during an internal<br>reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RESOUT is active High, not active Low. |

| Chapte | r 13 Asynchronous Ser                                                            | al Ports                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| 13-5   | 13.5.1.1.2<br>Transmitting Data,<br>steps 1 and 2.                               | <ol> <li>Verify that the THRE bit in the<br/>(H)SPSTAT register is set to 1 to<br/>ensure the transmit register can be<br/>written without loss of data.</li> <li>If FIFOs are being used (High-<br/>Speed UART only), instead of polling<br/>the THRE bit, verify that the FIFO is<br/>not yet full (TTHRSH bit in the<br/>HSPSTAT register is set to 1).</li> </ol> | <ol> <li>Verify that the THRE bit in the<br/>(H)SPSTAT register is set to 1 to<br/>ensure the transmit register can be<br/>written without loss of data.</li> <li>Note: If FIFOs are not used, software<br/>must verify that the THRE bit is set<br/>to 1 even if the TEMT bit was set in<br/>the (H)SPSTAT register before the<br/>previous write.</li> <li>If FIFOs are being used (High-<br/>Speed UART only), software can<br/>omit polling the THRE bit only if it is<br/>certain there is space in the FIFO.<br/>The FIFO contains 16 empty slots if<br/>the TEMT bit is set. The FIFO<br/>contains at least eight empty slots if<br/>hardware sets the TTHRSH bit in the<br/>HSPSTAT register after software has<br/>cleared it.</li> </ol> |                                        |

Table 1. Corrections to the Am186<sup>™</sup>CC/CH/CU Microcontrollers User's Manual, Rev. B (Continued)

| Page  | Item                                                                       | Original Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Comment  |

|-------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 13-7  | 13.5.1.3 Autobaud<br>Mode, step 7                                          | 7. Wait for the ABAUD bit in the<br>HSPCON1 register to go to 0 to<br>indicate that the autobaud operation<br>is complete. The computed baud<br>divisor is automatically copied into<br>the HSPBDV register, and the<br>autobaud (ABAUD) bit in the<br>HSPCON1 register is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7. Wait for the ABAUD bit in the<br>HSPCON1 register to go to 0 to<br>indicate that the autobaud operation<br>is complete. The computed baud<br>divisor is automatically copied into<br>the HSPBDV register, and the<br>autobaud (ABAUD) bit in the<br>HSPCON1 register is cleared. This<br>also sets the ABDONE bit in the<br>HSPSTAT register.<br><b>Note:</b> The ABDONE bit is not<br>available in parts released prior to<br>revision C1. For processor revision<br>information, see the PRL register<br>description in the Am186CC/CH/CU<br>Register Set Manual, order #21916B<br>[and its amendment, order<br>#21916B/1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 13-13 | 13.5.4 CTS/RTR<br>Hardware Flow<br>Control, second and<br>third paragraphs | In the CTS/RTR protocol, the<br>receiver asserts clear-to-send (CTS)<br>whenever there is room in the<br>receiver for more data. The<br>transmitting device should sample<br>CTS before beginning transmission<br>of each frame. CTS is deasserted<br>when the start bit is detected for the<br>last frame that can be read without<br>data loss. When FIFOs are disabled,<br>CTS is deasserted after the start bit<br>for each frame is detected and<br>remains deasserted until the data is<br>read from the receive data register.<br>When the receive FIFO is enabled,<br>CTS is deasserted after the start bit is<br>received for the last frame that will fit<br>in the FIFO.<br>The transmitter samples ready-to-<br>receive (RTR) before transmitting the<br>start bit of each frame. The RTR<br>signal is not sampled during frame<br>transmission. This allows the<br>receiving device to deassert RTR any<br>time before the end of the stop bit.<br>The transmitter does not begin<br>transmitting the start bit for the next<br>frame while RTR is deasserted. | In the CTS/RTR protocol, the UART's<br>ready-to-receive (RTR) output is<br>connected to the attached device's<br>clear-to-send (CTS) input, and the<br>attached device's RTR output is<br>connected to the UART's CTS input.<br>(I.e., the CTS and RTR signals are<br>cross-connected.)<br>The receiver asserts RTR whenever<br>there is room in the receiver for more<br>data. The transmitting device should<br>sample this signal (at its CTS input)<br>before beginning transmission of<br>each frame. The receiver deasserts<br>RTR when the start bit is detected for<br>the last frame that can be read<br>without data loss. When FIFOs are<br>disabled, the receiver deasserts RTR<br>after the start bit for each frame is<br>detected, and holds RTR deasserted<br>until the data is read from the receive<br>data register. When the receive FIFO<br>is enabled, the receiver deasserts<br>RTR after the start bit is received for<br>the last frame that will fit in the FIFO.<br>The transmitter samples its CTS<br>input before transmitting the start bit<br>of each frame. The CTS input is not<br>sampled during frame transmission.<br>This allows the receiving device to<br>deassert its RTR output any time<br>before the end of the stop bit. The<br>transmitter does not begin<br>transmitting the start bit for the next<br>frame while its CTS input is<br>deasserted. | Clarify. |

| Page            | Item                                                            | Original Text                               | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Comment                       |

|-----------------|-----------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

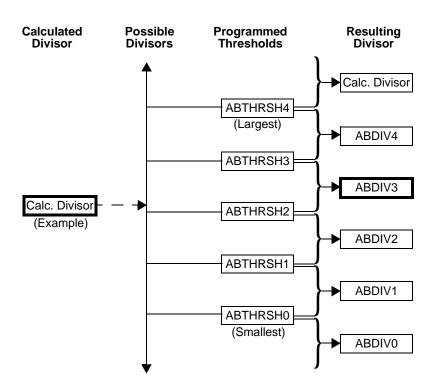

| 13-17–<br>13-19 | Discussion of autobaud<br>enhancement; changes<br>throughout    | [References to registers HSPAB0–<br>HSPAB3] | [Add a new register HSPAB4 at offset<br>27E, and modify text accordingly.<br>Wherever the text states that the<br>ABTHRSH3 bit field in the HSPAB3<br>register must contain the largest<br>threshold, specify the ABTHRSH4 bit<br>field in the HSPAB4 register instead.<br>Also add the following note:]                                                                                                                                                                                                                                                          |                               |

|                 |                                                                 |                                             | <b>Note:</b> The HSPAB4 register is not<br>available in parts released prior to<br>revision C1. For processor revision<br>information, see the PRL register<br>description in the Am186CC/CH/CU<br>Register Set Manual, order #21916B<br>[and its amendment, order<br>#21916B/1].                                                                                                                                                                                                                                                                                 |                               |

|                 |                                                                 |                                             | To maintain compatibility with<br>existing software that does not<br>initialize the HSPAB4 register, the<br>HSPAB3 register can contain the<br>largest ABTHRSHx value, in which<br>case the HSPAB4 register must be<br>cleared or left in its default disabled<br>state (00h).                                                                                                                                                                                                                                                                                    |                               |

| 13-18           | Figure 13-9 Autobaud<br>Enhancement                             | [Existing figure]                           | [Replace with Figure 13-9 on page 10 of this amendment.]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Update and<br>clarify figure. |

| 13-19           | Table 13-5 UARTs<br>Interrupt Sources                           | [Existing table]                            | [Add new row before "Overrun error<br>on receive FIFO":]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Add BRKIM<br>bit.             |

|                 |                                                                 |                                             | Break on receive FIFO,<br>RSIE (Off),<br>BRKIM (Off)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| 13-20           | 13.5.7 Break<br>Detection and<br>Generation, first<br>paragraph | [Existing first paragraph.]                 | [Add new sentence and note:]<br>If the receive FIFO is enabled (High-<br>Speed UART only), the break<br>immediate (BRKIM) status bit<br>indicates the break condition as soon<br>as it occurs; the FER and BRK status<br>bits are not set until the<br>corresponding character is loaded<br>into the HSPRXD register.<br><b>Note:</b> The BRKIM bit is not available<br>in parts released prior to revision C1.<br>For processor revision information,<br>see the PRL register description in<br>the Am186CC/CH/CU Register Set<br>Manual, order #21916B [and its | Add BRKIM<br>bit.             |

Table 1. Corrections to the Am186<sup>™</sup>CC/CH/CU Microcontrollers User's Manual, Rev. B (Continued)

Table 1. Corrections to the Am186<sup>™</sup>CC/CH/CU Microcontrollers User's Manual, Rev. B (Continued)

| Page   | Item                                                               | Original Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Change To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comment                                                                    |

|--------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Chapte | r 14 Synchronous Seria                                             | l Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 14-4   | <b>14.5.1 Usage</b> , item #5                                      | 5. Wait for the DR/DT bit in the SSSTAT register to go to 0 to indicate the transmit or receive has completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5. Wait for the DR/DT bit in the SSSTAT register to go to 1 to indicate the transmit or receive has completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| Chapte | r 16 HDLC External Seri                                            | al Interface Configuration (TSAs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 16-5   | <b>16.3 System Design</b> , first sentence                         | lists the signals that are multiplexed with other microcontroller functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 16-1 lists the signals that are multiplexed with other microcontroller functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| Chapte | r 17 General Circuit Inte                                          | rface (GCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

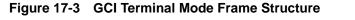

| 17-8   | Figure 17-3 GCI<br>Terminal Mode Frame<br>Structure                | [Existing figure]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [Change to new figure 17-3, shown<br>on page 10 of this amendment.]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Change FSC<br>signal<br>waveform.                                          |

| Chapte | r 18 Universal Serial Bu                                           | s (USB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

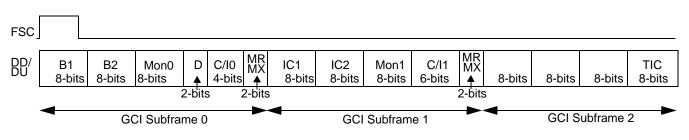

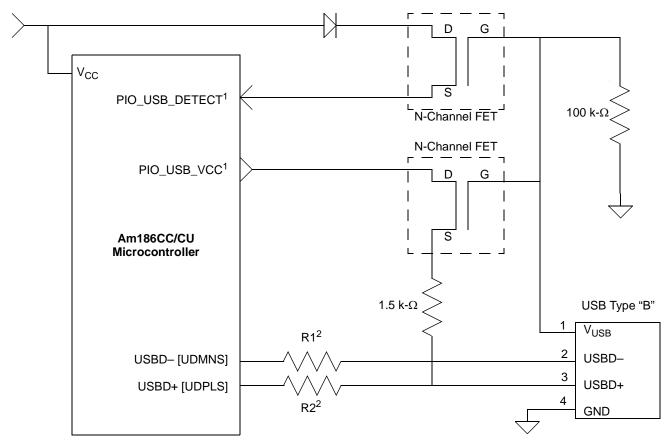

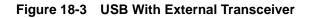

| 18-4   | Last paragraph before                                              | [Existing text]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | [Add the following sentence:]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clarify PIO                                                                |

|        | figure                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | In these examples, software defines a PIO input (PIO_USB_DETECT) to monitor the USB's $V_{USB}$ signal, and a PIO output (PIO_USB_VCC) to control the 1.5 k- $\Omega$ pullup on USBD+.                                                                                                                                                                                                                                                                                                                                                                                                                                 | use in<br>example.                                                         |

|        | Figure 18-2 USB With<br>Internal Transceiver                       | [Existing figure]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [Change to new figure 18-2, shown<br>on page 11 of this amendment.]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Add pulldown<br>to V <sub>USB</sub> .<br>Clarify PIO<br>use in<br>example. |

| 18-5   | Figure 18-3 USB With<br>External Transceiver                       | [Existing figure]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [Change to new figure 18-3, shown on page 12 of this amendment.]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Add pulldown<br>to V <sub>USB</sub> .                                      |