DT-52-33-09

## Am95C60

Quad Pixel Dataflow Manager

#### **PRELIMINARY**

## DISTINCTIVE CHARACTERISTICS

- Generates mixed text and graphics within Display Memory

- Draws vectors up to 3.3 million pixels per second, or places text at 50,000 characters per second

- One chip handles four Display Memory planes of any size up to 4K x 4K bits and screen sizes to 2K x 2K pixels

- Capable of cascading to handle multiple memory planes without system performance degradation

- Reflects GKS, CGI and NAPLPS software standards

- · Supports windowing, panning and scrolling

- Supports drawing of anti-aliased vectors, circles and arcs with various user-definable line styles

- Fills arbitrary polygons

- Supports dual-port video DRAMs

- CMOS technology

- Provides memory and video refresh at user-definable rates

- Interfaces to any 8- or 16-bit system bus

- Comprehensive instruction set

#### **GENERAL DESCRIPTION**

The Am95C60 Quad Pixel Dataflow Manager (QPDM) is a CMOS graphics processor which contains the necessary circuitry and control functions for driving four bit-mapped memory arrays. Featuring a maximum system clock speed of 20 MHz, the Am95C60 can interface to any 8- or 16-bit system bus and can draw vectors up to 3.3 million pixels per second, or place text at a rate of 50,000 characters per second. Such performance allows the user to efficiently mix text and graphics within the bit map. The Am95C60 QPDM also contains graphics primitives which smoothly interface with the GKS, CGI and NAPLPS software standards.

The Am95C60 interfaces directly to memory planes consisting of dual-port video dynamic memories (VRAMs) and is capable of supporting four planes up to 4K by 4K bits and display screens up to 2K by 2K pixels. The Am95C60 is fully cascadable and can manage up to 256 memory planes with no system performance degradation.

The Am95C60 QPDM provides support for the drawing of anti-aliased vectors, circles and arcs with various user-defined linestyles. Other features include windowing, independent X and Y zoom factors, pan and scroll, picking, clipping and logical PEL. The Am95C60 is packaged in a 145-pin Pin Grid Array (PGA).

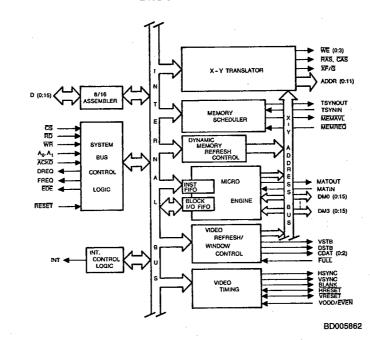

#### **BLOCK DIAGRAM**

Publication # Rev. Amendment 07013 B /0 Issue Date: April 1987 Am95C60

**Advanced Micro Devices**

## 0257525 ADVANCED MICRO DEVICES 89D 25232 T-52-33-09 **ORDERING INFORMATION** Standard Products AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number b. Speed Option (if applicable) c. Package Type d. Temperature Range e. Optional Processing AM95C60 OPTIONAL PROCESSING Blank = Standard processing d. TEMPERATURE RANGE C = Commercial (0 to +70°C) E = Extended Commercial (-55 to +125°C) c. PACKAGE TYPE G = 145-Terminal Pin Grid Array (CGX145) b. SPEED OPTION -12 = 12 MHz -16 = 16 MHz

| Valid Combinations |            |  |  |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|--|--|

| AM95C60-12         |            |  |  |  |  |  |  |  |

| AM95C60-16         | GC, GE     |  |  |  |  |  |  |  |

| AMORCEO DO         | <b>-</b> 1 |  |  |  |  |  |  |  |

DEVICE NUMBER/DESCRIPTION Am95C60 Quad Pixel Dataflow Manager

#### Valid Combinations

-20 = 20 MHz

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

T-52-33-09

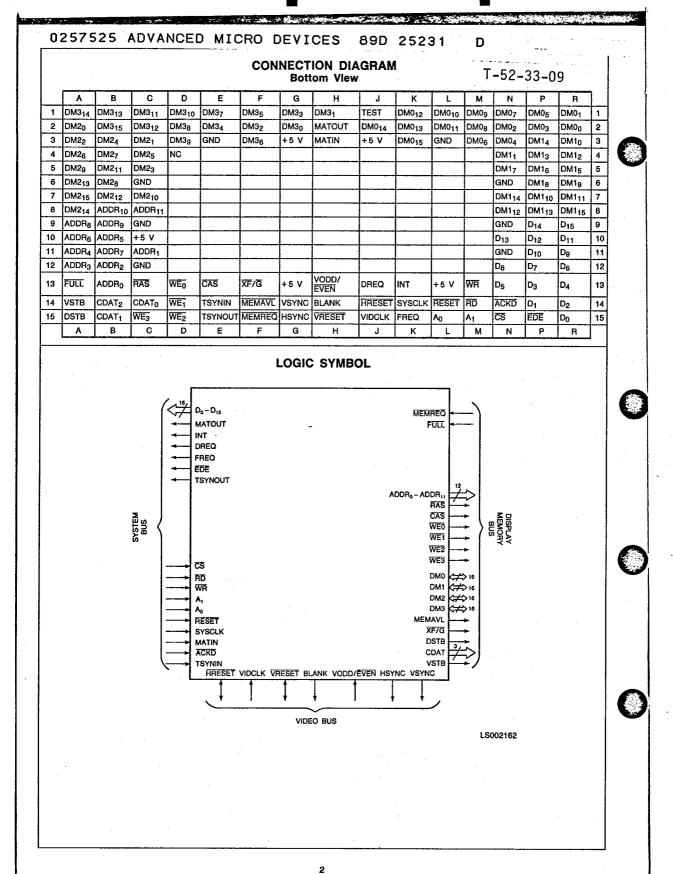

The Am95C60 interfaces through three buses: the System Bus, the Display Memory Bus and the Video Bus.

#### System Bus

#### D (0:15) Command/Data/Status (Input/Output; Three-State)

These sixteen lines are used for transferring commands/ data/status on the System Bus. The nature of the information transferred on the D(0.15) lines is specified with the port address pins  $A_0$ ,  $A_1$ .

### RD Read (Input; Active LOW)

Signal used for reading information (data/status) from the Am95C60 QPDM on the *D* (0:15) lines by a bus master.

#### WR Write (Input; Active LOW)

Signal used for strobing information (commands/data) into the Am95C60 from the D (0:15) lines.

#### CS Chip Select (input; Active LOW)

Signal used for selecting the Am95C60 from several peripherals connected to the same system bus.

#### A<sub>0</sub>, A<sub>1</sub> Port Address (Input)

These two inputs are used for selecting the appropriate port to be read or written.

#### SYSCLK System Clock (input)

20 MHz maximum frequency clock. Controls the Am95C60 QPDM internal timing except for video timing.

#### INT Interrupt (Output; Active HIGH)

High-level interrupt output used to signal that an exception has occurred. The nature of the exception can be determined by reading the Status register.

#### DREQ Data FIFO Request (Output; Open Drain) Signal used to start and suspend a transfer of data between the System Memory and the Display Memory.

#### ACKD Acknowledge DMA (Input; Active LOW)

The external DMA device may drive this pin LOW in response to a DMA request to strobe in or read out data in fly-by DMA transfer format.

FREQ Instruction FIFO request (Output; Open Drain)

This signal is used to start and suspend a transfer of instructions from the system memory into the QPDM instruction FIFO.

### EDE External Driver Enable (Output; Active LOW)

This pin is used to enable external data bus drivers on the system bus.  $\overline{EDE}$  is inactive (HIGH) during an output block operation on those Am95C60 devices that do not participate in the output. This signal eliminates contention on the system bus

## MATOUT Match Out (Output; Active HIGH)

This pin is used in multiple-QPDM applications to search for a matching color pattern. As long as the pattern is not found, this pin stays LOW. When the matching pattern is found the pin is driven HIGH. Since all the MATOUT outputs are logically ANDed externally, a match in a multiple-QPDM environment is visible on MATIN when all the MATOUT outputs are HIGH. This pin is also used for instruction-execution synchronization by re-aligning the Am95C60 devices in a system at the beginning of each instruction execution and at the beginning of each word transfer in Block I/O instruction.

## MATIN Match In (Input, Active HIGH)

This pin is connected to the output of the AND gate connected to the MATOUT outputs.

TSYNOUT Timing Synchronization (Output, Active HIGH) In conjunction with TSYN/N, this pin is used to synchronize Display Memory Bus activities. The TSYNOUT pins of all Am95C60 devices in a system are ANDed together and connected to the TSYN/N input pins of all Am95C60s. Usertransparent information signals all Am95C60 devices about Display Memory Bus activities.

TSYNIN Timing Synchronization (Input; Active HIGH)

All TSYNIN input pins are connected to the AND of the TSYNOUT.

#### RESET System Reset (Input; Active LOW)

The RESET signal brings all Am95C60s in the system to the same initial state. All the outputs are brought into the inactive state. If RESET is activated during the time when the Am95C60 was active, all the activities will be suspended.

#### **Display Memory Bus**

#### ADDR (0:11) Address (Output)

The twelve lines of address are used for addressing bit-map planes each up to 4K x 4K bits. The addresses are multiplexed and contain row and column addresses and bank-select bits.

#### DM (0:3) (0:15) Display Memory Bus (Input/Output)

These 64 lines are used for transferring data between the Am95C60 and the Display Memory. There are sixteen lines for each of the four planes.

## RAS Row Address Strobe (Output; Active LOW)

This line is used to strobe the Row address from the multiplexed ADDR lines into the array.

# CAS Column Address Strobe (Output; Active LOW) This line is used to strobe the column address from the multiplexed ADDR lines into the array.

## XF/G Transfer/Output Enable (Output; Active LOW)

This pin interfaces directly to the video DRAM. During a transfer cycle this pin indicates a transfer to the video DRAMs. During a random read cycle, this pin enables the output buffer of the video DRAMs.

#### WE (0:3) Write Enable (Output; Active LOW)

The Write Enable, when active, signifies that the current transaction on the Display Memory Bus is a write to the corresponding bit plane.

## MEMREQ Memory Request (Input; Active LOW)

This asynchronous signal is used by an external device to request access to the Display Memory Bus.

# MEMAVL Memory Bus Available (Output; Active LOW) This line is used to inform external devices that are requesting the bus that the Am95C60 is not driving the data lines.

#### Video Control Bus

## VODD/EVEN Vertical Odd/Even (input)

This input is optionally used in the interlaced Display mode to distinguish between the even frame and the odd frame specified by an external device.

## VSTB Video Strobe (Output, Active HIGH)

This strobe signal is used in a system with video dynamic RAMs (VRAMs) and an external VDAF (Am8171/8172 Video Data Assembly FIFO or a similar circuit built of discrete components) to shift video data out of the Video Memory. With every strobe, a 16-bit-wide word is shifted out of the Video Memory.

#### DSTB Data Strobe (Output; Active HIGH)

This clock signal loads 8 bits of video data into the VDAF. DSTB is synchronous with SYSCLK and has twice the frequency of VSTB.

#### CDAT (0:2) Control Data (Output; Active HIGH)

These lines are used to output three bits of information to the VDAF. Information is sent to the VDAF during the transfer cycle and at VSTB time.

#### FULL Full (input; Active LOW)

This input alerts the Am95C60 that the VDAF cannot accept more video data. If the FULL signal is active, the Am95C60 stops generating the VSTB and DSTB signals.

#### VIDCLK Video Clock (Input)

15 MHz maximum frequency clock. Clock used for generating video synchronization signals.

#### HSYNC Horizontal Sync (Output; Active HIGH)

HSYNC is an active HIGH output used to cause horizontal retrace of the CRT's electron beam. This output is held LOW when the Am95C60 is reset to prevent any uncontrolled synchronization to the CRT which may cause damage to the tube.

#### VSYNC Vertical Sync (Output; Active HIGH)

VSYNC is an active HIGH output used to cause vertical retrace of the CRT's electron beam. This output is held LOW when the Am95C60 is reset.

## BLANK Blank Video (Output; Active HIGH)

BLANK is an active HIGH output which serves to blank out inactive display areas of the CRT. This output is held HIGH when the Am95C60 is reset.

## HRESET Horizontal Reset (Input/Output; Active LOW)

This pin is an output for horizontal video masters, and an input for horizontal video slaves. It is used for vertical video synchronization to other Am95C60s or to an external video source.

#### VRESET Vertical Reset (Input/Output; Active LOW)

This pin is an output for vertical video masters and an input for vertical video slaves. It is used for vertical video synchronization to other Am95C60 devices or to an external video source.

#### **Power Connections**

#### V<sub>CC</sub> Power Supply

Each VCC must be connected to a +5-V power supply.

#### GND Ground

Each GND pin must be connected to the power supply ground.

#### **FUNCTIONAL DESCRIPTION**

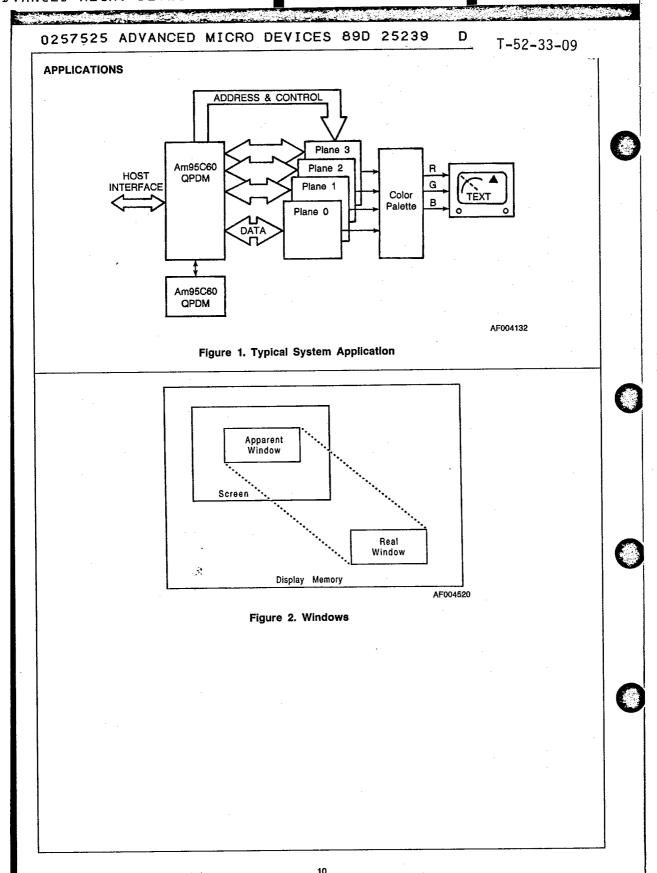

The Am95C60 Quad Pixel Dataflow Manager is a graphics processor which maintains, updates and displays information in four bit-mapped video planes. As depicted in Figure 1, the System Interface communicates with either an 8- or 16-bit host CPU while the Display Memory Interface controls four bit-mapped memory planes. These planes consist of dual-port video dynamic memories (VRAM). The Am95C60 connects to the random ports while the serial ports are used to access video information for the screen refresh. When used in conjuction with the Am8172 Video Data Assembly FIFO, the Am95C60 is capable of displaying a hardware window with the associated features of smooth pan and soft scroll.

The Am95C60 QPDM performs three fundamental functions described below:

### Video Refresh

The Am95C60 QPDM manages the screen (display) refresh function by generating the addresses to the bit-map VRAMs as required to access data for display on the screen. The data from the VRAMs are serialized externally to the Am95C60.

The Video Refresh operation is fully programmable allowing the user to tailor the system as required. The screen display can be aligned on any pixel boundary and can also include one hardware window overlay. Additionally, the total video process can be externally synchronized to any external source at the horizontal or vertical synchronization rate. Video Refresh can be disabled for operation as a slave device.

#### **Dynamic Memory Refresh**

The Am95C60 performs the Dynamic Memory Refresh function for the Display Memory. The Dynamic Memory Refresh process is interleaved with the Video Refresh and with the Display Memory updating. The refresh rate is programmed by loading the 10-bit Dynamic Memory Refresh Rate register. This register holds the number of SYSCLK cycles between two refresh cycles.

The Dynamic Memory Refresh Rate register is loaded into a counter, which is down counted by the *SYSCLK*. When the counter reaches its zero state, it sends a refresh request to the Memory Scheduler. As soon as the Memory Scheduler arbitrates a time slice for the Dynamic Memory Refresh block, a refresh cycle is initiated.

The Am95C60 executes CAS before RAS refresh cycles.

#### Display Memory Update

The Am95C60 has access to the Display Memory Bus for updating purposes, except those times when it is performing Video or Dynamic Memory Refresh.

Placing an instruction in the execution FIFO (see Block Diagram) signals the Micro Engine to begin operation. If the execution of the instruction requires access to the Display Memory Bus (this is the case in most instructions), the Am95C60 continues the instruction execution unless the Display Memory Bus is occupied by the Video Refresh or the Dynamic Memory Refresh process. If the Display Memory Bus cannot be accessed momentarily, the execution is suspended until the Display Memory is available.

The drawing instruction set includes Line, Circle, Filled Triangle, String and many others which will be briefly described in the following pages.

#### **Feature Description**

#### Window Display Mechanism

The Am95C60 QPDM, in conjunction with the Am8171/8172 Video Data Assembly FIFO (VDAF) or the equivalent, can support a single non-destructive hardware window. The image to appear in the window is located in some other area of Display Memory than that visible on the screen (this is shown in Figure 2). The size and position of the window is programmed into a set of registers on the Am95C60. Since the window position is dynamically programmable, it is easy to 'drag' a rectangular area containing an object. It is also easy to perform soft scrolling and smooth panning of either background or foreground.

D

T-52-33-09

#### Clipping

The clipping feature on the Am95C60 allows a rectangular region to be defined outside of which vectors and arcs will not be drawn, blocks will not be moved or modified, and polygons will not be filled. The clipping window is specified by the user, and remains in effect until changed or disabled.

#### Picking

If a drawing consists of a large number of objects and each object is defined by a number of drawing primitives, any object can be identified by the following picking process.

First, the picking area is defined as a rectangular region in Display Memory. Whenever a drawing intersects the picking area, a 'Pick Detect' bit in the status register is set. Objects to be displayed are labeled by using the Signal instruction which will return the label of the object that intersected the picking area.

#### Multiple Am95C60 Operation

In order to accomodate systems requiring access to more than four bit-planes, the Am95C60 is designed to be fully cascadable with no performance degradation. Multiple Am95C60 devices can communicate with each other to share timing information for synchronization purposes and status information for color comparisons in depth.

Instructions are broadcast to all Am95C60 devices at once. Each plane will use the instruction in conjunction with its own activity and color bits to decide whether to execute or to ignore the instruction. Each plane may execute the instruction differently, depending on the contents of the individual memory plane and the contents of plane-specific status information.

Broadcasting is accomplished by chip-selecting all Am95C60 QPDMs simultaneously and writing to Port 0. (Write to the instruction FIFO.)

TSYNOUT and TSYNIN are used to synchronize Display Memory operations in a multiple Am95C60 system.

MATOUT and MATIN are used to exchange color searching information in a multiple Am95C60 device system and to synchronize instruction execution.

#### Interface Description

### System Bus Interface

The host connects to the system side of the Am95C60 as depicted in the Logic Symbol diagram. There is a 16-bit data path, and the 8- or 16-bit option allows the Am95C60 QPDM to be connected to an 8- or 16-bit host processor.

The normal bus interface control lines are supported through CS, RD, WR and two address bits. The address bits are decoded to select one of four ports:

#### A<sub>1</sub> A<sub>0</sub> WRITE FUNCTION

#### **READ FUNCTION**

| 0 | 0 | Write | Instruction FIFO  |

|---|---|-------|-------------------|

| 0 | 1 | Write | Block Input FIFO  |

| 1 | 0 | Write | Register Addresss |

**Read Status** Read Block Output FIFO

1 Write Register

Read Register Address Read Register

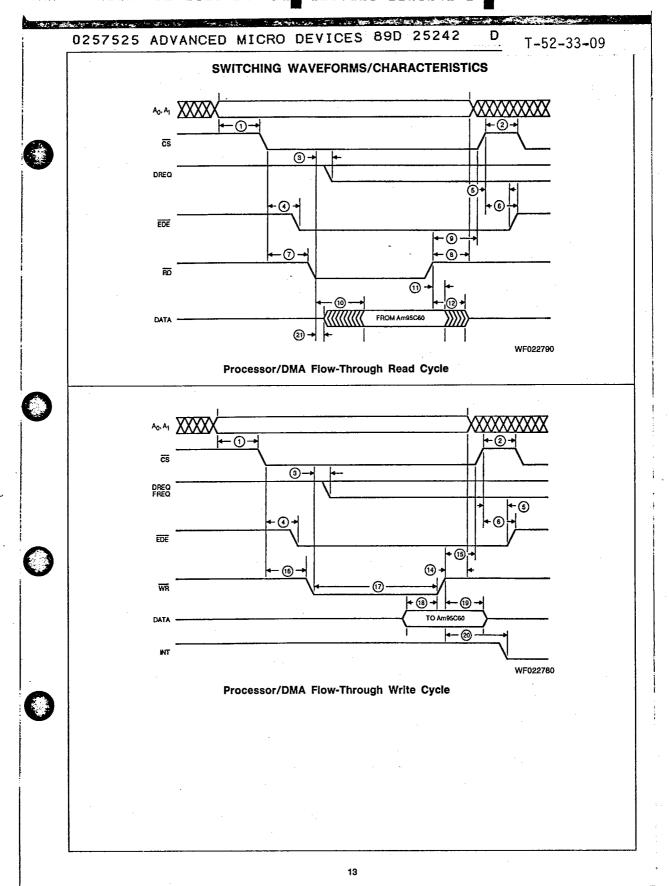

The Am95C60 QPDM can be supported with a DMA controller allowing blocks of information or instructions to be transferred without tying up the host. In addition to the normal flowthrough DMA operations, the Am95C60 also supports fly-by operations.

The Am95C60 also can use interrupts to signal the occurrence of certain events. Some events are repetitive (e.g., Frame), some indicate error conditions (e.g., Stack Overflow), and some merely report status (e.g., Idle). There are registers for masking interrupts, reading interrupt requests and acknowledging interrupts.

#### Display Memory Bus Interface

On the Display Memory side, the Am95C60 is capable of controlling four bit planes. Addresses,  $\overline{\it RAS}$  and  $\overline{\it CAS}$  are common signals to all the bit planes while each plane has its own set of data lines and write enable (WE). Typically, eight or nine address lines (multiplexed Row/Column) go to the VRAM devices while the others may be used for bank select. If multiple banks of memory are used for each bit plane, row addresses must be decoded to select the proper bank.

Each bit plane has a 16-bit data bus used for the Display Memory Update function. Typically, to write a single pixel, (one bit in each plane), the Am95C60 would perform simultaneous 16-bit reads from all planes, followed by simultaneous 16-bit writes to all planes. Logic is also provided in the Am95C60 to perform individual pixel writes.

The Am95C60 is intended to be used with a variety of dualported Video RAMS (VRAM). Prior to the beginning of each scan line, the Am95C60 executes a transfer cycle which copies the contents of the scan line into shift registers on the VRAM devices. The scan line image is then shifted out of the VRAM devices 16 bits at a time and further serialized at the dot clock rate for display purposes. The primary VRAM port is available during this time for Display Memory Update.

#### Display Memory/RAM Size Examples

|              |           | VRAMS/ | VRAMS/  |

|--------------|-----------|--------|---------|

| BIT MAP SIZE | VRAM SIZE | PLANE  | Am95C60 |

| 1024 x 1024  | 64K x 4   | 4      | 16      |

| 1024 x 2048  | 64K x 4   | 8      | 32      |

| 2048 x 2048  | 64K x 4   | 16     | 64      |

| 4096 x 4096  | 256K x 4  | 16     | 64      |

MEMREQ and MEMAVL are used to allow another processor direct access to the Display Memory.

## Video Bus Interface

The Am95C60 generates video timing. Horizontal timing is programmed in terms of VIDCLK cycles and vertical timing is programmed in terms of 1/2 scan lines.

HRESET and VRESET are either inputs or output depending on the Am95C60's master/slave status. In the case where multiple Am95C60s control the display, one Am95C60 would be programmed as the timing master and the others would be programmed as timing slaves

#### **Power Connections**

The Am95C60 uses +5 volts only.

### Performance Figures

Working with VRAMs, the Am95C60 can easily manage high resolution screen formats requiring dot clock rates up to 160 MHz. Moreover, it performs the bit-map update function as indicated in Table 1.

TABLE 1. PERFORMANCE FIGURES OF Am95C60

| Instruction      | Instruction<br>Overhead | Intermediate<br>Overhead | Execution<br>Time    | Comments                                |

|------------------|-------------------------|--------------------------|----------------------|-----------------------------------------|

| Line             | 12.9 µs                 | (Not Applicable)         | 300 nx/pixel         |                                         |

| Line             | 12.9 μs                 | (Not Applicable)         | 4750 ns/pixel        | Anti-Aliased                            |

| Polyline         | 10.6 μs                 | 4.8 μs/segment           | 300 ns/pixel         | Connected Segments                      |

| Arc              | 28.2 µs                 | 2.7 μs/octant            | 750 ns/pixel         |                                         |

| Arc              | 28.2 µs                 | 2.7 µs/octant            | 4750 ns/pixel        | Anti-Aliased                            |

| Circle           | 9.9 µs                  | 2.7 µs/octant            | 750 ns/pixel         |                                         |

| Circle           | 9.9 µs                  | 2.7 μs/octant            | 4750 ns/pixel        | Anti-Aliased                            |

| Copy Block       | 10.9 μs                 | 1.8 μs/scan line         | 55 ns/pixel          | BITBLT                                  |

| Transform Block  | 11.0 μs                 | (Included)               | 1280 ns/pixel        | 3X Zoom                                 |

| Seed Fill        | 10.0 μs                 | 12.1 μs/scan line        | 280 ns/pixel         | Intermediate Overhead varies with shape |

| Filled Rectangle | 11.9 μs                 | 2.2 µs/scan line         | 19 ns/pixel          | Graphical SET                           |

| Filled Triangle  | 54.9 μs                 | 8.0 μs/scan line         | 19 ns/pixel          | Intermediate Overhead varies with shape |

| String           | 6.3 µs                  | 9.4 μs/character         | 2000 ns/scan<br>line |                                         |

The Am95C60 provides extremely fast access at the host interface. A host write requires as little as 80 ns, while a register may be read in as little as 120 ns.

Consult the technical manual (Order No. 07785) to see how these performance measurements are determined.

### **Register Description**

The Am95C60 QPDM contains a number of registers which are programmable from the host. These registers are listed below:

Video Control uses nine registers which define video operation parameters:

Horizontal Sync Pulse Width (HSYNC)

Horizontal Scan Delay (HDEL)

Horizontal Active (HACT)

Horizontal Total Count (HTOT)

Vertical Sync Pulse Width (VSYNC)

Vertical Scan Delay Odd (VDELODD)

Vertical Scan Delay Even (VDELEVEN)

Vertical Active Lines (VACT)

Vertical Total Lines (VTOT)

Visible Screen Coordinates use four registers which contain the (x,y) address in real memory of the top-left and bottomright corner of the visible screen in Display Memory:

Screen X Start

Screen Y Start

Screen X Terminate

Screen Y Terminate

Window Control uses six registers which specify where the window is on the screen (the apparent window) and where it begins in memory (the real window):

Window Apparent X Start

Window Apparent Y Start

Window Apparent X Terminate

Window Apparent Y Terminate

Window Real X

Window Real Y

Video Mode Register is used to indicate to each Am95C60 whether it is a timing master or slave, and whether or not interlaced display mode is to be used.

Memory Mode Register specifies Display Memory configuration in terms of memory width and device size (e.g.; 4K wide/ 256K devices).

Dynamic Memory Refresh Rate Register specifies the number of SYSCLK clock cycles between row refreshes in Dynamic Memory Refresh.

Interrupt Enable Register indicates which conditions are allowed to cause interrupts to the host.

Interrupt Acknowledge Register indicates that a specific interrupt condition is known to the host and that the request is to be cancelled in the Am95C60.

Video Timing Enable is a 1-bit register used to enable and disable video sync and output.

Video Refresh Enable is a 1-bit register used to enable and disable the collection of video information from the Display RAM

System Bus Width Register configures the Am95C60 to 8-bit system bus modes.

#### Instruction Set

The Am95C60 QPDM is a graphics processor with a powerful instruction set oriented toward graphics processing. One may use any of four addressing modes to specify locations in the display memory: 1) Absolute, 2) Relative, 3) Viewpoint, or 4) Indirect. Each member of the Am95C60 QPDM instruction set is briefly described as follows:

Arc draws the image of a circular arc in Display Memory. The parameters are the center of the arc, the radius of the arc and the two end-points. The image may be drawn using antialiasing, line style and a logical PEL.

Arc Current draws the image of a circular arc in Display Memory. It is similar to Arc except the start point is taken to be the current pen position (rather than being specified).

Call begins fetching instructions from Display Memory rather than from the instruction FIFO. The parameters specify the

location of the program to be executed. A stack in Display Memory is used to contain the return location.

Circle draws the image of a circle in Display Memory. The parameters are the circle's center and radius. The image may be drawn using anti-aliasing, line style and a logical PEL.

Circle Current draws the image of a circle in Display Memory. It is similar to Circle, except the center is taken to be the current pen position.

Control Clipping enables or disables the clipping function. When clipping is enabled, all drawing primitives will change only that portion of Display Memory which lies within the rectangular clipping region.

Control Picking enables or disables the picking function. When picking is enabled, drawing primitives will not execute any writes to the Display Memory. The Pick Detect status bit is set whenever a drawing primitive intersects the picking area.

Copy Block moves a block of data within Display Memory and may optionally combine the source image with the destination image. The size of the block will have been determined by a Set Block Size instruction. The location of each block, source and destination, is determined by the instruction.

Copy Block Current is identical to the Copy Block instruction except that the source operand is the current pen position.

Define Logical PEL specifies the logical PEL (pen size and content) used by the drawing primitives. This can be used to draw thick lines.

Fill Bounded Region fills an arbitrary polygon with a specific color. The polygon is defined as the group of dots completely contained within a boundary of pixels of the edge color. All pixels will be changed to the current drawing color. The location of the seed is specified in the instruction.

Fill Bounded Region Current fills an arbitrary polygon with a specific color. The polygon is defined as the group of dots completely contained within a boundary of pixels of the edge color. All pixels in the region will be changed to the current drawing color. The location of the seed is the current pen position.

Fill Connected Region fills an arbitrary polygon with a specific color. The polygon is defined as any group of connected dots of the seed's color. All pixels connected to the seed point having the same color will be changed to the current drawing color. The location of the seed is specified in the instruction.

Fill Connected Region Current fills an arbitrary polygon with a specific color. The polygon is defined as any group of connected dots of the seed's color. All pixels connected to the seed point having the same color will be changed to the current drawing color. The location of the seed is the current pen position.

Filled Rectangle creates the image of a rectangle and fills it. The parameters specify two opposite corners of the rectangle. The color of the filled rectangle is the current drawing color.

Filled Rectangle Current is similar to Fill Rectangle except the current pen position is taken to be the starting corner of the rectangle. The other corner is specified by the instruction.

Filled Triangle creates the image of a triangle and fills it. The parameters specify the three vertices of the triangle. The color of the filled triangle is the current drawing color.

Filled Triangle Current creates the image of a triangle and fills it. The parameters specify two vertices of the triangle. The current pen position is taken to be the third vertex of the triangle. The color of the filled triangle is the current drawing color.

Input Block transfers a rectangular block of data from the host to Display Memory. The size of the block will have been determined by a Set Block Size instruction. The destination address in the Display Memory is specified in the instruction. The data to be stored in Display Memory is written into the Data FIFO.

D

Input Block Current transfers a rectangular block of data from the host to Display Memory. The size of the block will have been determined by a Set Block Size instruction. The destination address in the Display Memory is the current pen position. The data to be stored in Display Memory is written into the Data FIFO.

Jump unconditionally changes the location counter when executing instructions from Display Memory.

Line draws the image of a line in Display Memory. The input parameters are the two ends of the line. The image may be drawn using anti-aliasing, line style and a logical PEL. Multiple lines may be drawn with a single line instruction.

Line Current is similar to Line, except the current drawing position is taken to be the starting point of the line.

Move Pen sets the current pen position.

No Operation ensures that no operation is performed.

Output Block transfers a rectangular block of data from Display Memory to the host. The size of the block will have been determined by a Set Block Size instruction. The source address in the Display Memory is specified in the instruction. The host is expected to remove the data from the Data FIFO.

Output Block Current transfers a rectangular block of data from Display Memory to the host. The size of the block will have been determined by a Set Block Size instruction. The source address in the Display Memory is the current pen position. The host is expected to remove the data from the Data FIFO.

Point draws the image of the current logical PEL at the location specified in the instruction.

Point Current draws the image of the current logical PEL at the current pen position.

Return exits from a subroutine or from program mode when executing instructions from Display Memory.

Set Activity Bits indicates which of the four Display Memory planes, controlled by the Am95C60, are to be written into.

Set Anti-Aliasing Distance programs the anti-aliasing distance deviation from the ideal line.

Set Block Size specifies the number of pixels moved in any block operation. This is used for Input Block, Output Block, Copy Block, Transform Block, and the logical PEL.

Set Character Font Base specifies the character font address in the Display Memory. The character font contains the patterns of letters and numbers used by the String instruction.

Set Character Font Base Current specifies the character font addresses in Display Memory.

Set Clipping Boundary specifies where the clipping region is in Display Memory. When clipping is enabled, all drawing primitives will change only that portion of Display Memory which lies within the rectangular clipping region. The parameters are the addresses of two opposite corners of the clipping rectangle.

Set Clipping Boundary Current specifies where the clipping region is in Display Memory. When clipping is enabled, all drawing primitives will change only that portion of Display Memory which lies within the rectangular clipping region. The

D

T-52-33-09

current pen position is taken to be the start corner of the clipping rectangle.

Set Color Bits sets the current drawing color.

Set Search Color specifies the edge color used in Fill instructions.

Set Line Style specifies the line style. This defines the dash length, the interspace length, and the dot length.

Set Line Style Phase indicates where the line begins within the linestyle cycle.

Set Listen Bits indicates which planes take part in polygon and color change operations. If set, the corresponding plane doesn't participate in the color matching.

Set Picking Region specifies the rectangular area to be picked. The parameters are two opposite corners of the picking rectangle. When picking is enabled, drawing primitives that intersect the picking region will cause the "Pick Detect" bit in the status register to be set and no writes will be executed to Display Memory.

Set Picking Region Current specifies the rectangular area to be picked. The parameters are two opposite corners of the picking rectangle. The current pen position is taken to be the start corner of the picking region. When picking is enabled, drawing primitives that interest the picking region will cause the "Pick Detect" bit in the status register to be set and no writes will be executed to Display Memory.

Set QPDM Position specifies the logical addresses for each Display Memory plane.

Set Scale Factor provides values used to multiply the operands of instructions which address the bit-map.

Set Search Color specifies the color of the boundary for Fill Boundary Area operations.

Set Stack Boundaries specifies to the Am95C60 which area of Display Memory has been set aside for the stack. Stack overflow is detected and signaled to the host with an interrupt.

Set Viewpoint Location specifies the base address for Viewpoint Addressing Mode.

Signal is used to indicate to the host when a particular point in the instruction stream has been reached, to delimit objects during picking, or to pause operation pending a signal from the best

Store Immediate deposits a specified number of 16-bit words in the Display Memory.

Store Immediate Current deposits a specified number of 16-bit words in Display Memory beginning at the current pen position.

String is used to create the image of a string of text in the Display Memory. The parameters are the address at which the string should begin, followed by a variable length list of 16-bit pointers. Each pointer is used to look up a pattern in the character font table.

String Current is similar to String except the address at which the string should begin is set to the current pen position.

Transform Block allows a block of data to be taken from Display Memory, operated on, and written to a different area of Display Memory. The operations which may be performed are Rotate (90 degree increments), Zoom (by pixel replication), and Mirror. The Zoom in X, and Zoom in Y are independently specified. The size of the source block (prior to rotation and zooming) will have been specified by a Set Block Size instruction.

Transform Block Current is similar to Transform Block except the source operand is at the current pen position.

D T-52-33-09

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature6                                  | 5 t | o  | +150 | °C |

|-------------------------------------------------------|-----|----|------|----|

| Ambient Operating Temperature5                        | 5 t | o  | +125 | °C |

| Maximum V <sub>CC</sub> Relative to V <sub>SS</sub> 0 | .3  | to | +7.0 | ٧  |

| DC Voltage Applied to Any                             |     |    |      |    |

Pin Relative to VSS.....-0.5 to VCC +0.3 V

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

Commercial (C) Devices Temperature (T<sub>A</sub>)...... 0 to +70°C Supply Voltage (VCC) .....+4.75 to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description  | Test Conditions          | Min. | Max.                               | Unite    |

|---------------------|------------------------|--------------------------|------|------------------------------------|----------|

| V <sub>IL</sub>     | Input LOW Voltage      |                          | -0.3 | +0.8                               | V        |

| VIH                 | Input HIGH Voltage     |                          | +2.0 | V <sub>CC</sub> + <sub>c</sub> 0.3 | €/ V     |

|                     | Output LOW Voltage     | I <sub>OL</sub> = 2.0 mA | (A)  | -0.4                               | / v      |

| V <sub>OL</sub>     | (CAS and XF/G)         | IOL = 4.0 mA             |      | -6.4                               | <u> </u> |

| VoH                 | Output HIGH Voltage    | 10H = 250 μA             | 2.4  | B M                                | 3 V      |

| loz                 | Output Leakage Current | 0.4 × Vout < Vcc         | Et V | ±10                                | μΑ       |

| يسب ا               | Input Current          | 0.4 CIVIN CIVCO          |      | ±10                                | μΑ       |

| lcc                 | Power Supply Surrent   | MUDE                     |      |                                    | mA       |

| E.1.                |                          |                 |      |      |       |

|---------------------|--------------------------|-----------------|------|------|-------|

| Parameter<br>Symbol | Parameter<br>Description | Test Conditions | Min. | Max. | Units |

| CIN                 | Input Capacitance        |                 |      | 15   | pF    |

| C <sub>I/O</sub>    | I/O Pin Capacitance      |                 |      | 25   | pF    |

| Соит                | Output Pin Capacitance   |                 |      | 25   | pF    |

<sup>\*</sup>Parameters are not "Tested."

12

T-52-33-09

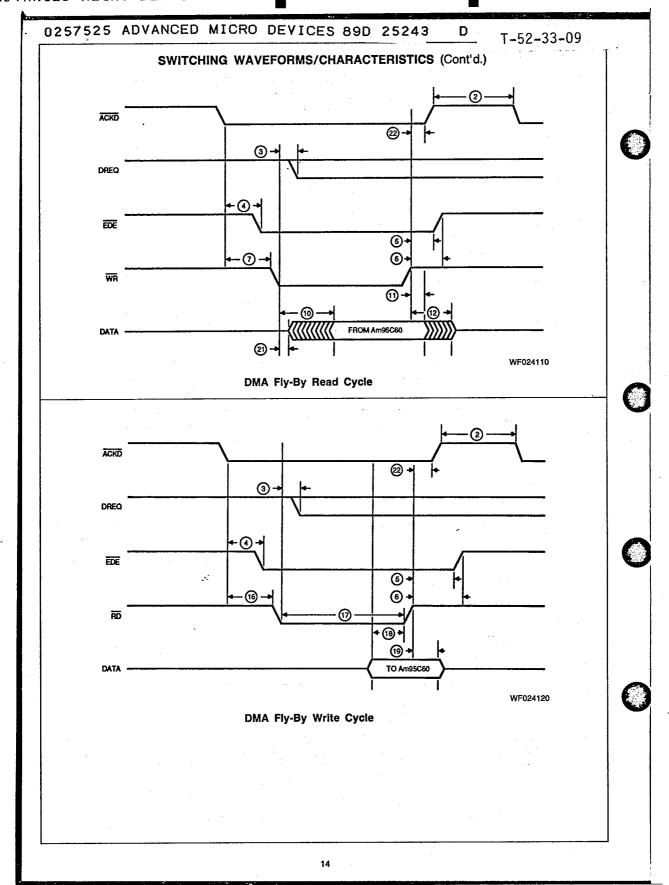

# SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) System Bus Timing

|     |                              |                                                                                                                                                                                                                                                         | -:   | 20   |      | 16   |      | 12   |       |

|-----|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------|

| No. | Parameter<br>Symbol          | Parameter Description                                                                                                                                                                                                                                   | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| 1   | ts                           | Requires that the address be valid a minimum of {} ns before CS begins to fall.                                                                                                                                                                         | 0    |      | 0    |      | 0    |      | ns    |

| 2   | tw<br>(Note 1)               | Requires that both CS and ACKD be not active a minimum of {} ns before either can go active.                                                                                                                                                            | 65   |      | 95   |      | 125  |      | ns    |

| 3   | t <sub>PHL</sub>             | Guarantees that DREQ will become not active a maximum of $\{\}$ ns after $\overline{\text{RD}}$ or $\overline{\text{WR}}$ becomes active.                                                                                                               |      | 50   |      | 60   | _    | 70   | ns    |

| 4   | t <sub>PHL</sub><br>(Note 1) | Guarantees that EDE will become active a maximum of<br>{} ns after CS becomes active. Also guarantees that EDE<br>will become active a maximum of {} ns after ACKO<br>becomes active.                                                                   |      | 50   |      | 60   |      | 70   | ns    |

| 5   | tрцн<br>(Notes 1, 3)         | Guarantees that EDE will remain active a minimum of {} ns after CS becomes not active. Also guarantees that EDE will remain active a minimum of {} ns after RD has become not active.                                                                   | 10   |      | 10   |      | 10   | 3    | ns    |

| 6   | tрцн<br>(Notes 1, 3)         | Guarantees that EDE will have gone not active no more than () is after CS has become not active. Also guarantees that EDE will have gone pot active in more than () is after RD has become not active.                                                  |      | 66   |      | 70   |      | 75   | ns    |

| 7   | ts<br>(Notes 1, 2)           | Requires that CS be valid a minimum of 1 ns before RD can begin to go active Also requires that ACKD be valid a minimum of 1 sefore WR can begin to go active.                                                                                          | 0    |      | 0    |      | 0    |      | ns    |

| 8   | ч                            | Requires that the address remain valid a minimum of [] ns_affer RD has gone not active.                                                                                                                                                                 | 10   |      | 10   |      | 10   |      | ns    |

| 9   | Ч                            | Hequires that CS remain active a minimum of [] ns after RD has gone not active.                                                                                                                                                                         | 0    |      | 0    |      | 0    |      | ns    |

| 10  | tpD (Note 2)                 | Guarantees that the read data will be valid within [] ns of RD becoming active. Also guarantees that the read data will be valid within [] ns of WR becoming active in a Fly-By Read Cycle.                                                             |      | 110  |      | 110  |      | 120  | ns    |

| 11  | t <sub>H</sub> (Notes 2, 3)  | Guarantees that the read data will remain valid a minimum of [} ns after RD has gone not active. Also guarantees that the read data will remain valid a minimum of [} ns after WR has gone not active in a Fly-By Read Cycle.                           | 10   |      | 10   |      | 10   |      | ns    |

| 12  | tpD<br>(Notes 2, 3)          | Guarantees that the read buffers will begin to enter high impedance within   ns of RD having gone not active. Also guarantees that the read buffers will begin to enter high impedance within   ns of WR having gone not active in a Fly-By Read Cycle. |      | 35   |      | 40   |      | 45   | ns    |

Notes: See notes at end of this section.

ź,

n

T-52-33-09

# SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) System Bus Timing (Cont'd.)

|       | Parameter          |                                                                                                                                                                                                                                                            | :    | 20   |      | 16   |             | 12   |       |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------------|------|-------|

| No.   | Symbol             | Parameter Description                                                                                                                                                                                                                                      | Min. | Max. | Min. | Max. | Min.        | Max. | Units |

| 13    | (Not used)         | NOT USED                                                                                                                                                                                                                                                   |      |      |      |      |             |      |       |

| 14    | ч                  | Requires that the address remain valid a minimum of [] ns after WR has gone not active.                                                                                                                                                                    | 10   |      | 20   |      | 20          |      | ns    |

| 15    | tH                 | Reguires that $\overline{\text{CS}}$ remain active a minimum of {} ns after $\overline{\text{WR}}$ has gone not active.                                                                                                                                    | 10   |      | 20   |      | 20          |      | ns    |

| 16    | ts<br>(Notes 1, 2) | Requires that $\overline{CS}$ be active a minimum of $\{\}$ ns before $\overline{WR}$ can begin to go active. Also requires that $\overline{ACKD}$ be active a minimum of $\{\}$ ns before $\overline{RD}$ can begin to go active in a Fly-By Write Cycle. | 0    |      | 0    |      | 0           |      | ns    |

| 17    | ₩                  | Requires that WR be active for a minimum of {} ns. Also requires that RD be active a minimum of {} ns in the case of a Fly-By Write Cycle. Also requires that ACKD remain active a minimum of {} ns after RD has gone active in a Fly-By Write Cycle.      | 70   |      | 90   |      |             |      | ns    |

| 18    | ts<br>(Notes 2, 3) | Requires that the write data be active for a minimum of a before WR begins to go not active. Also requires that the write data be active for a minimum of this before RDCor ACRD (whichever is with begins to be not active in a Fly-By Write Cycle.       | 500  |      | 75   | لناد | <b>W6</b> 0 |      | ns    |

| 19    | (Notes 2, 3)       | Requires that the write data be kept valid for Word a minimum of ] in after WR has gone not Mode hactive. Who requires that the write data be                                                                                                              | 0    |      | 0    |      | 0           |      | ns    |

|       |                    | kept valid to a minimum of {} ns after RD or ACKD (Whichever is first) has gone not active Mode in a Fly-By Write Cycle.                                                                                                                                   | 15   |      | 25   |      | 25          |      | ψs    |

| 20    | t <sub>PHL</sub>   | Guarantees that the INT line will become not active no more than [] ns after WR has gone not active                                                                                                                                                        |      | 120  |      | 150  |             | 180  | ns    |

| 21    | t₽D                | Guarantees that the data buffers will not become active before RD goes active. Also guarantees that the data buffers will not become active before WR goes active in a Fly-By Read Cycle.                                                                  | 0    |      | 0    |      | 0           |      | ns    |

| 22    | ч                  | Requires that $\overline{ACKD}$ be active a minimum of $\{\}$ ns after $\overline{RD}$ or $\overline{WR}$ has gone not active.                                                                                                                             | 0    |      | 0    |      | 0           |      | ns    |

| 23-29 | (Not used)         | NOT USED                                                                                                                                                                                                                                                   |      |      |      |      |             | ļ    |       |

Notes: See notes at end of this section.

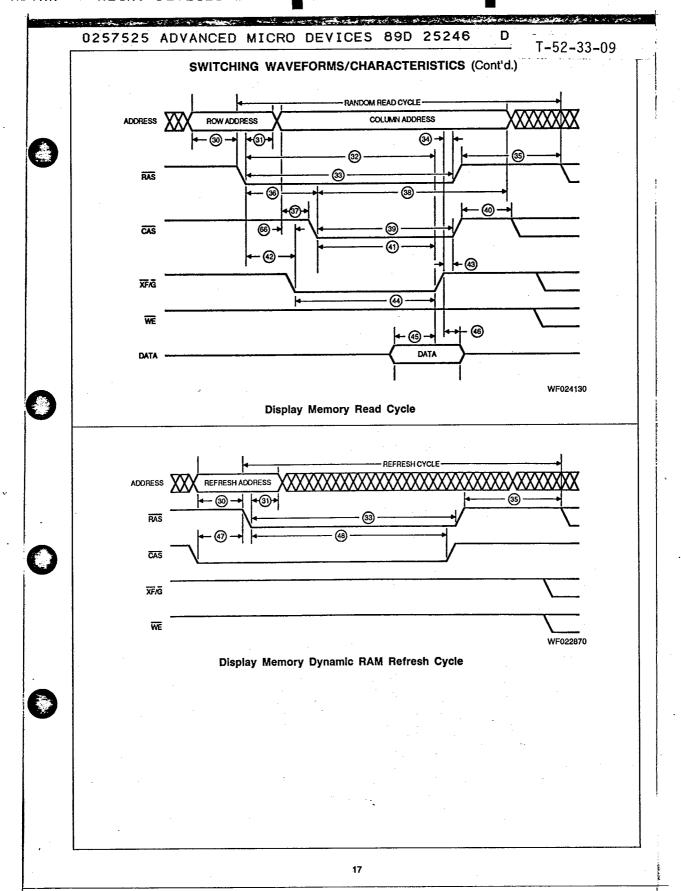

# **SWITCHING WAVEFORMS/CHARACTERISTICS** (Cont'd.) Display Memory Interface

T-52-33-09

|     | Parameter                  |                                                                                                                                      |            | 20     | -    | 16   |       | 12   |       |

|-----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------|------|-------|------|-------|

| No. | Symbol                     | Parameter Description                                                                                                                | Min.       | Max.   | Min. | Max. | Min.  | Max. | Units |

| 30  | ts<br>(Note 4)             | Guarantees the row addess will be stable (valid) a minimum of {} ns before RAS begins to go active.                                  | 15         |        | 16   |      | 21.5  |      | ns    |

| 31  | t <sub>H</sub><br>(Note 4) | Guarantees the row address will remain valid a minimum of {} ns after RAS has gone active.                                           | 35         |        | 45   |      | 63    | -    | ns    |

| 32  | tpD<br>(Note 4)            | Guarantees that $\overline{XF}/\overline{G}$ will not go active until a minimum of $\{\}$ ns after $\overline{RAS}$ has gone active. | 160        |        | 202  | ~    | 270.5 |      | ns    |

| 33  | tw<br>(Note 4)             | Guarantees that RAS will be active for a minimum of [] ns.                                                                           | 180        |        | 225  | ),   | 307   |      | ns    |

| 34  | t <sub>H</sub><br>(Note 4) | Guarantees that RAS will remain active for a minimum of [] ns after XF/G has gone not active.                                        | 14         |        | 15   |      | 21.5  |      | ns    |

| 35  | tw<br>(Note 4)             | Guarantees that RAS will remain not active for a minimum of {} ns.                                                                   | 95         |        | 109  | >    | 146   |      | ns    |

| 36  | tpD<br>(Note 4)            | Guarantees that CAS will not become active until a minimum of [] ns after RAS has gone active. See parameter 56 for write cycles.    | 65         | الحطار | 78   |      | 104.5 |      | กร    |

| 37  | ts<br>(Note 4)             | Guarantees that the column address will be valid and stable a minimum of {} ns before CAS will go active.                            | <b>3</b> 3 |        | 15   |      | 21.5  |      | ns    |

| 38  | t <sub>H</sub><br>(Note 4) | Guarantees that the column address will remain valid and stable a minimum of {  ps after CAS has gone active.                        | 80         |        | 104  |      | 144   |      | ns    |

| 39  | t <sub>W</sub><br>(Note 4) | Guarantees that CAS will be active a minimum of [] ns for a read cycle or a transfer cycle. See parameter 57 for writes cycles       | 100        |        | 130  |      | 180   |      | ns    |

| 40  | tw<br>(Note 4)             | Guarantees that CAS will remain not active for a minimum of 17 ns. This is important when a refresh cycle follows any cycle.         | 40         |        | 47   |      | 63    |      | ns    |

| 41  | t <sub>PD</sub> (Note ()   | Guarantées that XFVG will not have gone not active until                                                                             | 80         |        | 100  |      | 140   | •    | ns    |

| 42  | tpD<br>(Note 4)            | Guarantees that XF/G will not begin to go active until a minimum of {} ns after RAS has gone active.                                 | 39         |        | 46   |      | 60    |      | ns    |

| 43  | t <sub>H</sub> (Note 4)    | Guarantees that CAS will remain active until a minimum of [] ns after XF/G has gone not active.                                      | 13         |        | 16   |      | 21.5  |      | ns    |

| 44  | tw<br>(Note 4)             | Guarantees that $\overline{XF}/\overline{G}$ will be active a minimum of [] ns for a read cycle.                                     | 110        |        | 125  |      | 180   |      | ns    |

| 45  | ts                         | Requires that the read data be valid a minimum of $\{\}$ ns before $\overline{XF/G}$ begins to go not active.                        | 20         |        | 30   |      | 45    |      | ns    |

Notes: See notes at end of this section.

1

SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) Display Memory Interface (Cont'd.)

T-52-33-09

D

|     | Parameter                  |                                                                                                                                                                          |      | 20   |      | 16   |       | 12   |       |

|-----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|------|-------|

| No. | Symbol                     | Parameter Description                                                                                                                                                    | Min. | Max. | Min. | Max. | Min.  | Max. | Units |

| 46  | Ч                          | Requires that the read data remain valid a minimum of [] ns after XF/G has gone not active.                                                                              | 0    |      | 0    |      | 0     | -    | ns    |

| 47  | ts<br>(Note 4)             | Guarantees that RAS will not begin to go active until a minimum of {} ns after CAS has become active in a refresh cycle.                                                 | 37   |      | 45   |      | 63    |      | ns    |

| 48  | t <sub>H</sub><br>(Note 4) | Guarantees that CAS will not begin to go not active until a minimum of {} ns after RAS has gone active in a refresh cycle.                                               | 185  |      | 230  | 3    | 307   |      | ns    |

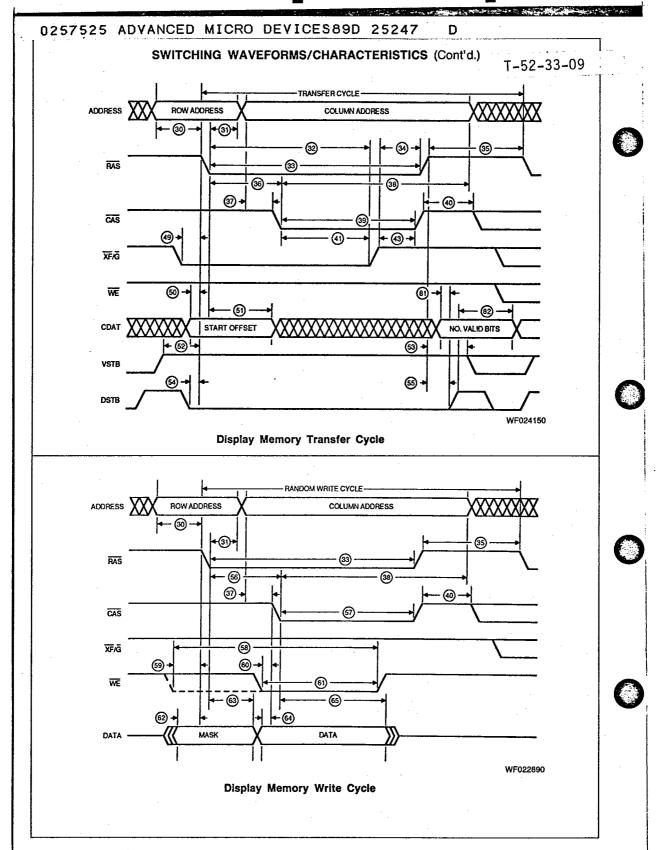

| 49  | ts<br>(Note 4)             | Guarantees that RAS will not begin to go active until a minimum of {} ns after XF/G is active in a transfer cycle.                                                       | 12   |      | 13   |      | 215   |      | ns    |

| 50  | ts<br>(Note 4)             | Guarantees that the Start Offset on CDAT will be valid and stable a minimum of {} ns before RAS begins to 30 active in a transfer cycle.                                 | tad. |      | ্যু  | 4    | 21.5  |      | ns    |

| 51  | t <sub>H</sub><br>(Note 4) | Guarantees that the Start Offset on CDAT will remain. valid and stable a minimum of {} ns-after HAS has gone active in a transfer cycle.                                 | 65   | الأذ | 78   |      | 104.5 |      | ns    |

| 52  | ts<br>(Note 4)             | Guarantees that VSTB will be HIGH a minimum of 1) before RAS begins to go active in a transfer cycle.                                                                    | 90   |      | 109  |      | 146   |      | ns    |

| 53  | t <sub>H</sub><br>(Note 4) | Guarantees that VSTB will remain \tag{\text{HIGH, a minimum of \}} ns after FAS has gone\noting active in a transfer cycle.                                              | 40   |      | 47   |      | 63    |      | ns    |

| 54  | ts<br>(Note 4)             | Guarantees that DSTB will be LOW a minimum of {} ns before RAS begins to go active in a transfer cycle.                                                                  | 90   |      | 109  |      | 146   |      | ns    |

| 65  | t <sub>H</sub><br>(Note 4) | Guarantees that DSTB will remain LOW a minimum of {} hs after RAS has gone not active in a transfer cycle.                                                               | 40   |      | 47   |      | 63    |      | ns    |

| 56  | (Note, 4)                  | Giarantees that CAS will not become active until a minimum of () ns after RAS has gone active. This is for a write cycle. See parameter 36 for read and transfer cycles. | 90   |      | 109  |      | 140   |      | ns    |

| 57  | t <sub>W</sub><br>(Note 4) | Guarantees that CAS will be active a minimum of {} ns for a write cycle. See parameter 39 for read and transfer cycles.                                                  | 80   |      | 100  |      | 312   |      | ns    |

| 58  | tw<br>(Note 4)             | Guarantees that WEO-WE3 will be active a minimum of [] in the case of a masked write,                                                                                    | 180  |      | 225  |      | 312   |      | ns    |

| 59  | ts<br>(Notes 4, 5)         | Guarantees that WEO-WE3 will be active a minimum of [] before RAS begins to fall in the case of masked write.                                                            | 11   |      | 14   |      | 21.5  |      | ns    |

A

T-52-33-09

SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) Display Memory Interface (Cont'd.)

|       |                             |                                                                                                                      | _          | 20       | _              | 16       |       | 12            |          |

|-------|-----------------------------|----------------------------------------------------------------------------------------------------------------------|------------|----------|----------------|----------|-------|---------------|----------|

| No.   | Parameter<br>Symbol         | Parameter Description                                                                                                | Min.       | Max.     | Min.           | Max.     | Min.  | Max.          | Units    |

| 60    | ts<br>(Note 4)              | Guarantees that WEO-WE3 will be active a minimum of<br>{} before CAS begins to fall in the case of a unmasked write. | 13         |          | 14<br><u>~</u> |          | 21.5  | $\mathcal{M}$ | ns       |

| 61    | tw<br>(Notes 4, 5)          | Guarantees that WEO-WE3 will be active a minimum will [] in the case of an unmasked write.                           | 78         |          | /100           |          | 740   |               | ns       |

| 62    | ts                          | Guarantees that the write mask will be valid and stable on the DM pins [] before RAS begins to go active.            | 12         |          | 7              |          | 115   |               | ns       |

| 63    | (Notes 4 5)                 | Guarantees that the write mask will remain active [1] after RAS has gone active.                                     | <u></u> 60 | سنة وإي  | 73             |          | 104.5 |               | ns       |

| 64    | 18                          | Guarantees that the write data will be valid and stable on the DM pine [] before CAS begins to go active.            | 2          |          | 7              |          | 15    |               | ns       |

| 65    | t <sub>H</sub> (Notes 4, 5) | Guarantees that the write data will remain active [] ns after CAS has gone active.                                   | 60         |          | 73             |          | 104.5 |               | ns       |

| 66    | ts                          | Guarantees that the column address will be valid $\{\}$ ns before $\overline{XF} - \overline{G}$ goes active.        | -8         |          | -12            |          | -16   |               | ns       |

| 67-79 | (Not used)                  | NOT USED                                                                                                             | <u></u>    | <u> </u> | <u> </u>       | <u>L</u> |       |               | <u> </u> |

Notes: See notes at the end of this section.

## T-52-33-09

D

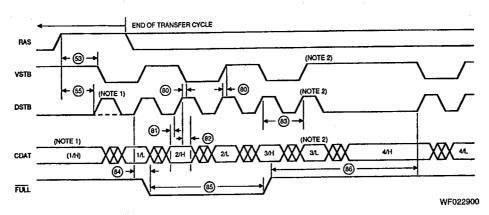

## SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) **VDAF Interface Timing**

|       |                     |                                                                                                                                                                                                                                   | -20        |                        | ~16      |          | -12               |          |       |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|----------|----------|-------------------|----------|-------|

| No.   | Parameter<br>Symbol | Parameter Description                                                                                                                                                                                                             | Min.       | Max.                   | Min.     | Max.     | Min.              | Max.     | Units |

| 80    | tpD                 | Guarantees that VSTB will change to the new state within 0-{} ns following the positive edge of DSTB.                                                                                                                             | 0          | 10                     | 0        | 10       | 0                 | ¶0       | ns    |

| 81    | ts                  | Guarantees the value on CDAT will be valid and stable a minimum of {} before DSTB begins to rise.                                                                                                                                 | 0          | $\mathcal{E}^{\gamma}$ | 0        | 1)       | 1. 6              | J        | ns    |

| 82    | tн                  | Guarantees the value on CDAT will remain valid a minimum of {} after the rising edge of DSTB.                                                                                                                                     | 20         |                        | 30       |          | \ <sup>40</sup> \ | 3        | ns    |

| 83    | tpD<br>(Note 4)     | Guarantees the positive edges on DSTB will occur with the same period as SYSCLK.                                                                                                                                                  | \$50       | J.                     | 657      |          | 83                |          | ns    |

| 84    | 5                   | Guarantees that FULE will be recognized at the current by SYSCLK, oxide if it is valid a minimum of 13 as before the edge. This is not an operating parameter, if this set-up time, is, not met, the part will not go metastable. | ) <u> </u> | 25                     |          | 50       |                   | 75       | ns    |

| 85    | (Note 4)            | Regulires that FULL remain active at least one SYSCLK period.                                                                                                                                                                     | 50         |                        | 62       |          | 83                |          | ns    |

| 86    | tPLH<br>(Note 4)    | Guarantees that a positive edge will not occur on DSTB until a minimum of [] ns following FULL going not active.                                                                                                                  | 150        |                        | 186      |          | 249               |          | ns    |

| 87-89 | (Not used)          | NOT USED                                                                                                                                                                                                                          | <u> </u>   | L                      | <u> </u> | <u> </u> |                   | <u> </u> | L     |

Notes: See notes at the end of this section.

Notes: 1. DSTB & CDAT for (1/H) only occurs on even boundaries.

2. One less byte may be strobed after FULL active.

3. CDAT 1/H = CDAT for 1st word HIGH byte.

**VDAF Interface Timing**

## 0257525 0025252 6 0257525 ADVANCED MICRO DEVICES 89D 25252 D T-52-33-09 SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) **VDAF Interface Timing** -20 Paramete Min. Max. Max. Min. Max. Units Min. Symbol No. Guarantees that the Am95C60 will make MEMAVE not active within [] ns of MEMREO going not active. · 180 242.5 (Note 4) Guarantees that the Am95C80 will not begin a memory cycle for a minimum of [] ns following the rising edge of MEMAVL. 558 747 450 91 (Notes 4, 6) NOT USED 92-99 (Not used) Notes: See notes at the end of this section. MEMREQ ← NOTE 1 4 MEMAVL EXTERNAL DEVICE DISPLAY MEMORY BUS EXTERNAL DEVICE Am95C60 VIDEO REFRESH AND/OR DRAM REFRESH WF022910 Notes: 1. MREQ to MEMAVL DELAY = Minimum 6C for arbitration cycle Not an Operating Parameter = Maximum 12C if DRAM Refresh Lower Priority Provided for Reference only = Maximum 18C if DRAM Refresh Higher Priority 2. Display Memory Bus = ADDR, RAS, CAS, XF/G, WE, DATA 3. Parameter 91 is Referenced to RAS Falling Edge, which defines the Start of the QPDM Cycle **Display Memory Arbitration Timing**

SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) Miscellaneous Timing

T-52-33-09

D

|     | Parameter       |                                                                                                                                                                                                            | -20       |      | -16        |      | -12  |      |       |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------------|------|------|------|-------|

| No. | Symbol          | Parameter Description                                                                                                                                                                                      | Min. Max. |      | Min.       | Max. | Min. | Max. | Units |

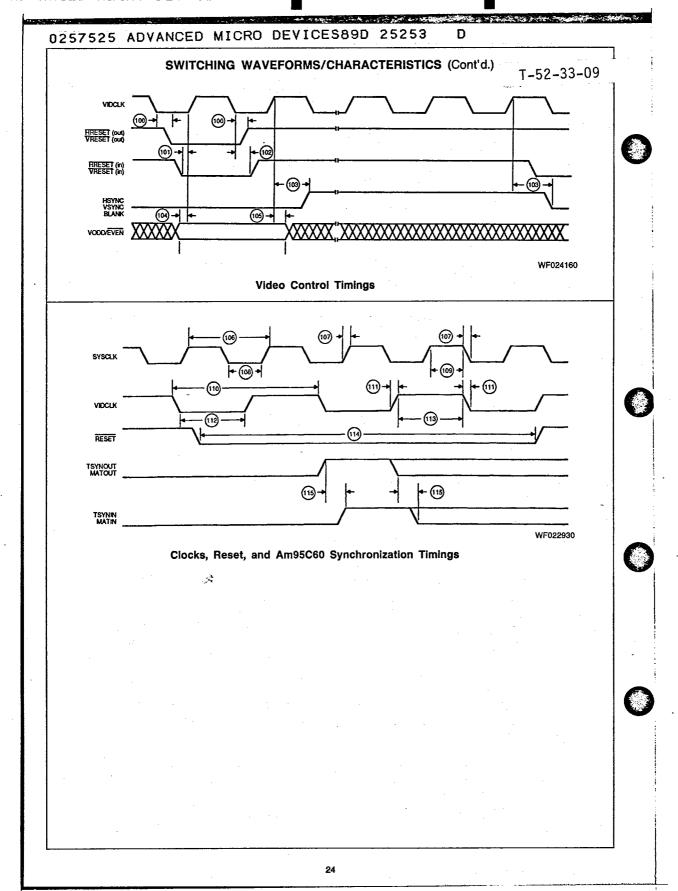

| 100 | t <sub>PD</sub> | Guarantees that transitions on TRESET and VRESET will occur a maximum of [] ns following the HIGH-to-LOW transition of VIDCLK. This is only if HRESET and VRESET are programmed as output(s).              |           | 25   |            | 31   |      | 41   | ns    |

| 101 | ts              | Requires that HRESET and VRESET be valid a minimum of 1) prior to the rising edge of VIDCLK. This is not an operational parameter. If this set-up time is not met, the Am95C60 will not become metastable. | 0         |      | o <b>k</b> | R    | 0    |      | ns    |

| 102 | ч               | Requires that HRESET and VRESET remain valid a minimum of {} ns after VIDCLK has fallen. This is not an operational parameter. If this hold time is not met, the Am95C60 will not become metastable.       | 15        |      | 20         | 1    | 25   |      | ns    |

| 103 | tpD             | Guarantees that transitions on BLANK, HSYNG and VSYNC will occur within a maximum of 1) ns of the rising edge of VIDCLK.                                                                                   | 1         |      |            | 40   |      | 50   | ns    |

| 104 | ts              | Requires that VODD/EVEN be valid a minimum of his prior to the rising edge of VIDCLIC.                                                                                                                     | 15        |      | 20         |      | 25   |      | ns    |

| 105 | th (            | Requires that VODD/EVEN remain valid minimum of ()                                                                                                                                                         | 15        |      | 20         |      | 25   | -    | ns    |

| 106 | lerc -          | Requires that the period of SYSCLK be between [] and                                                                                                                                                       | 50        | 500  | 62         | 500  | 83   | 500  | ns    |

| 107 | 17              | Requires that SYSCLK transition times be a maximum of Lins.                                                                                                                                                |           | 5    |            | 5    |      | 5    | ns    |

| 108 | tw []           | Requires that SYSCLK LOW time be a minimum of {} ns.                                                                                                                                                       | 18        |      | 23         |      | 32   |      | ns    |

| 109 | tw              | Requires that SYSCLK HIGH time be a minimum of [] ns.                                                                                                                                                      | 18        |      | 23         |      | 32   |      | ns    |

| 110 | tcyc            | Requires that the period of VIDCLK be between {} and {}.                                                                                                                                                   | 66        | 4000 | 72         | 4000 | 83   | 4000 | ns    |

| 111 | tτ              | Requires that the VIDCLK transition time be a maximum of {} ns.                                                                                                                                            |           | 5    |            | 5    |      | 5    | ns    |

| 112 | tw '            | Requires that the VIDCLK LOW time be a minimum of [] ns.                                                                                                                                                   | 25        |      | 27         |      | 32   |      | ns    |

## T-52-33-09

## SWITCHING WAVEFORMS/CHARACTERISTICS (Cont'd.) Miscellaneous Timing

|     | · .              |                                                                                                                            | -:   | 20   |      | 16   | -    | 12   |       |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------|

| No. | Parameter Symbol | Parameter Description                                                                                                      | Min. | Max. | Min. | Max. | Min. | Мах. | Units |

| 113 | W. Y             | Requires that VIDCLK HIGH time to a minimum of [] ns.                                                                      | 25   |      | 27   | R T  | 32   | 1    | пѕ    |

| 114 | Note 4)          | Requires that RESET remain active a minimum of [] hs                                                                       | 200  | 1    | 248  |      | 332  |      | ns    |

| 115 | 90               | Requires that the external delay from TSYNOUT to TSYNIN and the external delay from MATOUT to MATIN be a maximum of [] ns. |      | 20   |      | 25   | -    | 30   | ns    |

Notes: 1. Timings are relative to CS or ACKD.

2. RD and WR reverse operations in Fly-By DMA cycles.

3. Timings are relative to RD/WR or ACKD rising edge, whichever occurs first.

4. See Switching Characteristics Formulas.

5. This timing applies for Masked Writes.

6. All display memory cycles are exactly six SYSCLK cycles.

7. The units of all Switching parameters are ns.

8. Tests for parameters 12, 21, 42, 66, 107, 108, 109, 111, 112, 113, and 115 are not being performed in manufacturing.

## **Switching Characteristics Formulas**

All the Switching Characteristics which reference Note 4 are calculated with the formulas which follow. Each parameter is some number of SYSCLK cycles (or parts of SYSCLK cycles.) In addition, there is an adder for each of the three speed classes.

The numbers which are given in the Switching Characteristics are derived by evaluating the formulas assuming a minimum SYSCLK period. Users who wish to operate the Am95C60 at more than the minimum SYSCLK period may use these formulas to calculate the Switching Characteristics for their actual system.

D

## **Switching Characteristics Formulas**

T-52-33-09

| Parameter No. | Nominal | -20  | -16 | -12        |

|---------------|---------|------|-----|------------|

| 30            | c/2     | -10  | 15  | -20        |

| 31            | C       | 15   | 17  | -20        |

| 32            | 7c/2    | -15  | -15 | -20        |

| 33            | 4c      | -20  | -23 | -25        |

| 34            | c/2     | -11  | -16 | -20        |

| 35            | 2c      | -5   | -15 | -20        |

| 36            | 3c/2    | -10  | -15 | <b>∸20</b> |

| 37            | c/2     | -12  | -16 | -20        |

| 38            | 2c      | -20  | -20 | -22        |

| 39            | 5c/2    | ~25  | -25 | -27        |

| 40            | С       | -10  | -15 | -20        |

| 41            | 2c      | -20  | -24 | -26        |

| 42            | c       | -10  | -15 | -20        |

| 43            | c/2     | -12  | -15 | -20        |

| 44            | 5c/2    | -15  | -25 | 27         |

| 47            | С       | -13  | -17 | -20        |

| 48            | 4c      | -15  | -23 | -25        |

| 49            | c/2     | -13  | -18 | -20        |

| 50            | c/2     | -15  | -20 | -20        |

| 51            | 3c/2    | -10  | -15 | -20        |

| 52            | 2c      | -10  | -15 | -20        |

| 53            | С       | -10  | -15 | -20        |

| 54            | 2c      | -10  | 15  | <b>-20</b> |

| 55            | С       | -10  | -15 | -20        |

| 56            | 2c      | -10  | -15 | -20        |

| 57            | 2c      | -20  | -24 | -26        |

| 58            | 4c      | 15   | -18 | -20        |

| 59            | c/2     | -14  | -17 | -20        |

| 60            | c/2     | -12  | -17 | -20        |

| 61            | 2c      | -22  | -24 | -26        |

| 63            | 3c/2    | 15   | -20 | 20         |

| 65            | 3c/2    | -15  | -20 | -20        |

| 83            | С       | +0   | +0  | +,0        |

| 85            | С       | +0   | +0  | +0         |

| 86            | 3c      | +0   | +0  | +0         |

| 90            | 5c/2    | + 35 | +35 | +35        |

| 91            | 9c      | +0   | +0  | +0         |

| 114           | 4c      | +0   | +0  | +0         |

## **Parameter Type Definitions**

The following letter(s) specify the parameter type:

| Н   | Hold                                                                       | S   | Setup           |

|-----|----------------------------------------------------------------------------|-----|-----------------|

| PHL | Propagation Delay where the output is going from HIGH to LOW               | w   | Width           |

| PLH | Propagation Delay where the output is going from LOW to HIGH               | Т   | Transition Time |

| PD  | Propagation Delay where the output(s) go either HIGH or LOW or LOW to HIGH | CYC | Cycle Time      |

\* Reference Pin No. 145

#### 0257525 ADVANCED MICRO DEVICES 89D 25257 D T-52-33-09 **PHYSICAL DIMENSIONS\* CGX145** BOTTOM VIEW 1.400 BSC .075 x 45° REF. (REFERENCE CORNER) 0000000000000000 000000000000000 0000 000 000 000 000 **ത** ത ത 000 000 <del>@ @ @</del> 000 000 000 000 HEATSINK (OPTION) 000 000 000 000 .100 BSC .030 x 45" REFERENCE (3 PLACES)

PID ## 07321B

\*For reference only.