|                                 |            |        |               |              |                                               |                 |        |                | REVIS | IONS                                                                                 |      |       |                                                  |                |         |            |       |      |       |          |

|---------------------------------|------------|--------|---------------|--------------|-----------------------------------------------|-----------------|--------|----------------|-------|--------------------------------------------------------------------------------------|------|-------|--------------------------------------------------|----------------|---------|------------|-------|------|-------|----------|

| LTR                             |            |        |               | _            | (                                             | DESCI           | RIPTIC | N N            |       |                                                                                      |      |       | D                                                | ATE (          | YR-MO-  | DA)        | T     | APP  | ROVE  | D        |

| В                               | Add<br>Red | led d  | levio<br>enti | e ty         | pe C                                          | 5.<br>ent.      | Adde   | d ca           | se o  | utli                                                                                 | ne Y | •     | <del>                                     </del> | 96-04          |         |            | к.    |      | ottor |          |

|                                 |            |        |               |              |                                               |                 |        |                |       |                                                                                      |      |       |                                                  |                |         |            |       |      |       |          |

| REV                             |            |        | <u> </u>      | Ī .          | <del></del>                                   | <u> </u>        |        | <u> </u>       |       |                                                                                      | Γ    |       |                                                  |                |         | ı —        | I     | _    | Г     | <u> </u> |

| SHEET                           |            |        |               |              |                                               |                 |        |                | _     | -                                                                                    |      |       |                                                  |                | -       |            |       | -    |       |          |

| REV                             | В          | В      | В             | В            | В                                             | В               | В      |                |       |                                                                                      |      |       |                                                  | -              |         |            |       |      | -     | <u> </u> |

| SHEET                           | 15         | 16     | 17            | 18           | 19                                            | 20              | 21     |                |       |                                                                                      |      |       |                                                  |                |         |            |       |      |       |          |

| REV STATUS<br>OF SHEETS         | 6          |        |               | RE           | /                                             |                 | В      | В              | В     | В                                                                                    | В    | В     | В                                                | В              | В       | В          | В     | В    | В     | В        |

| OF OFFICE TO                    |            |        |               | SH           | ET                                            |                 | 1      | 2              | 3     | 4                                                                                    | 5    | 6     | 7                                                | 8              | 9       | 10         | 11    | 12   | 13    | 14       |

| PMIC N/A                        |            |        |               |              | PAREC<br>e L. Du                              |                 |        |                |       |                                                                                      | DE   | EFENS | E ELI                                            | ECTR           | ONICS   | SUP        | PLY C | ENTE | R     | <u>!</u> |

| STAN<br>MICRO<br>DRA            | CIR        | CUI    | T             |              | CKED<br>ael Jon                               |                 |        |                |       | DAYTON, OHIO 45444                                                                   |      |       |                                                  |                | <u></u> |            |       |      |       |          |

| THIS DRAWING<br>FOR US<br>DEPAR | G IS AV    | VAILAI | BLE           | APPI<br>Kend | ROVEC                                         | O BY<br>Cottong | im     |                |       | MICROCIRCUIT, HYBRID, MEMORY, 512K<br>ELECTRICALLY ERASABLE PROGRAMMA<br>ONLY MEMORY |      |       | K X 8<br>IABLE                                   | -BIT,<br>E REA | 'D      |            |       |      |       |          |

| AND AGENO<br>DEPARTMEN          | CIES C     | F THE  | SE            | DRA          | DRAWING APPROVAL DATE 93-01-22 SIZE CAGE CODE |                 |        | SIZE CAGE CODE |       |                                                                                      |      |       | -                                                |                |         |            |       |      |       |          |

| AMSC N                          | N/A        |        |               | REVI         | SION                                          | EVEL            |        |                |       |                                                                                      |      |       | 726                                              |                |         | <b>5</b> 9 | 62-   | 930  | 91    |          |

|                                 |            |        |               |              |                                               |                 | !      | В              |       | SHE                                                                                  | ET   | 1     |                                                  | OF             | 21      | 1          |       |      |       |          |

JUL 94

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

5962-E356-96

■ 9004708 0020936 7T1 ■ ·

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). This drawing describes device requirements for hybrid microcircuits to be processed in accordance with MIL-H-38534. Two product assurance classes, military high reliability (device class K) and space application (device class K) and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of radiation hardness assurance levels are reflected in the PIN.

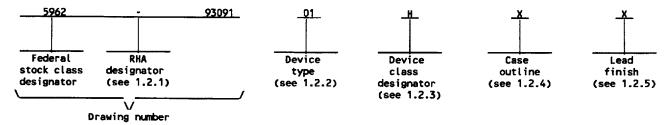

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes H and K RHA marked devices shall meet the MIL-PRF-38534 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | <u>Generic number</u> | <u>Circuit function</u> | Access time |

|-------------|-----------------------|-------------------------|-------------|

| 01          | WE-512K8-150CQ        | EEPROM, 512K x 8-bit    | 150 ns      |

| 02          | WE-512K8-300CQ        | EEPROM, 512K x 8-bit    | 300 ns      |

| 03          | WE-512K8-250CQ        | EEPROM. 512K x 8-bit    | 250 ns      |

| 04          | WE-512K8-200CQ        | EEPROM. 512K x 8-bit    | 200 ns      |

| 05          | WE-512K8-200CQ        | EEPROM, 512K x 8-bit    | 200 ns      |

1.2.3 <u>Device class designator</u>. This device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

H or K

Certification and qualification to MIL-PRF-38534

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| <u>Outline letter</u> | <u>Descriptive designator</u> | <u>Terminals</u> | <u>Package style</u>        |

|-----------------------|-------------------------------|------------------|-----------------------------|

| x                     | See figure 1                  | 32               | Dual-in-line, dual cavity   |

| Y                     | See figure 1                  | 32               | Dual-in-line, single cavity |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-PRF-38534 for classes H and K. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-93091 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>B | SHEET 2    |

DESC FORM 193A JUL 94

**■** 9004708 0020937 638 **■**

| 1.3 Absolute maximum ratings. 1/                                                                                                                                                             |                                                              | -                                                      |                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|----------------------------------|

| Supply voltage range Input voltage range Power dissipation (PD) Storage temperature range Lead temperature (soldering, 10 seconds) Thermal resistance, Junction to case (OJC) Data retention | 0.6 V dc tc<br>. 1.6 W<br>65°C to +15<br>. +300°C            | 0+6.25 V dc<br>0-c                                     |                                  |

| 1.4 <u>Recommended operating conditions</u> .                                                                                                                                                |                                                              |                                                        |                                  |

| Supply voltage range                                                                                                                                                                         | 0.3 V dc tc<br>. +2.2 V dc tc<br>. +2.4 V dc<br>. +0.45 V dc | 0 +0.8 V dc<br>0 V <sub>CC</sub> + 0.3 V dc            |                                  |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                      |                                                              |                                                        |                                  |

| 2.1 <u>Government specification, standards, and handbook</u> . Is standards, and handbook of the issue listed in that issue of Standards specified in the solicitation, form a part of this  | f the Department                                             | of Defense Index of Speci-                             | specification,<br>ifications and |

| SPECIFICATION                                                                                                                                                                                |                                                              |                                                        |                                  |

| PERFORMANCE                                                                                                                                                                                  |                                                              |                                                        |                                  |

| MIL-PRF-38534 - Hybrid Microcircuits, General Spec                                                                                                                                           | ification for.                                               |                                                        |                                  |

| STANDARDS                                                                                                                                                                                    |                                                              |                                                        |                                  |

| MILITARY                                                                                                                                                                                     |                                                              |                                                        |                                  |

| MIL-STD-883 - Test Methods and Procedures for Mic<br>MIL-STD-973 - Configuration Management.<br>MIL-STD-1835 - Microcircuit Case Outlines.                                                   | roelectronics.                                               |                                                        |                                  |

| HANDBOOK                                                                                                                                                                                     |                                                              |                                                        |                                  |

| MILITARY                                                                                                                                                                                     |                                                              |                                                        |                                  |

| MIL-HDBK-780 - Standardized Military Drawings.                                                                                                                                               |                                                              |                                                        |                                  |

| (Copies of the specification, standards, and handbook requestion functions should be obtained from the contraction                                                                           | uired by manufacting activity or as                          | turers in connection with<br>s directed by the contrac | specific<br>ting activity.)      |

| <ol> <li>2.2 <u>Order of precedence</u>. In the event of a conflict betherein, the text of this drawing shall take precedence.</li> </ol>                                                    | ween the text of                                             | this drawing and the ref                               | erences cited                    |

|                                                                                                                                                                                              |                                                              |                                                        |                                  |

|                                                                                                                                                                                              |                                                              |                                                        |                                  |

|                                                                                                                                                                                              |                                                              |                                                        |                                  |

| Stresses above the absolute maximum rating may cause pe<br>maximum levels may degrade performance and affect relia                                                                           | rmanent damage to<br>bility.                                 | o the device. Extended o                               | peration at the                  |

|                                                                                                                                                                                              |                                                              |                                                        |                                  |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER                                                                                                                              | SIZE<br>A                                                    |                                                        | 5962-93091                       |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                         |                                                              | REVISION LEVEL<br>B                                    | SHEET 3                          |

| DESC FORM 193A                                                                                                                                                                               |                                                              |                                                        |                                  |

9004708 0020938 574

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38534 and as specified herein.

- 3.2 <u>Design. construction. and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38534 and herein.

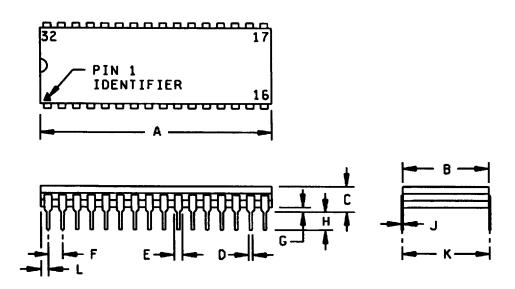

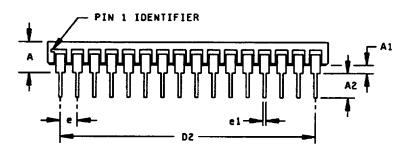

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 <u>Ierminal connections</u>. The terminal connections shall be as specified on figure 2.

- 3.2.3 <u>Iruth table(s)</u>. The truth table(s) shall be as specified on figure 3.

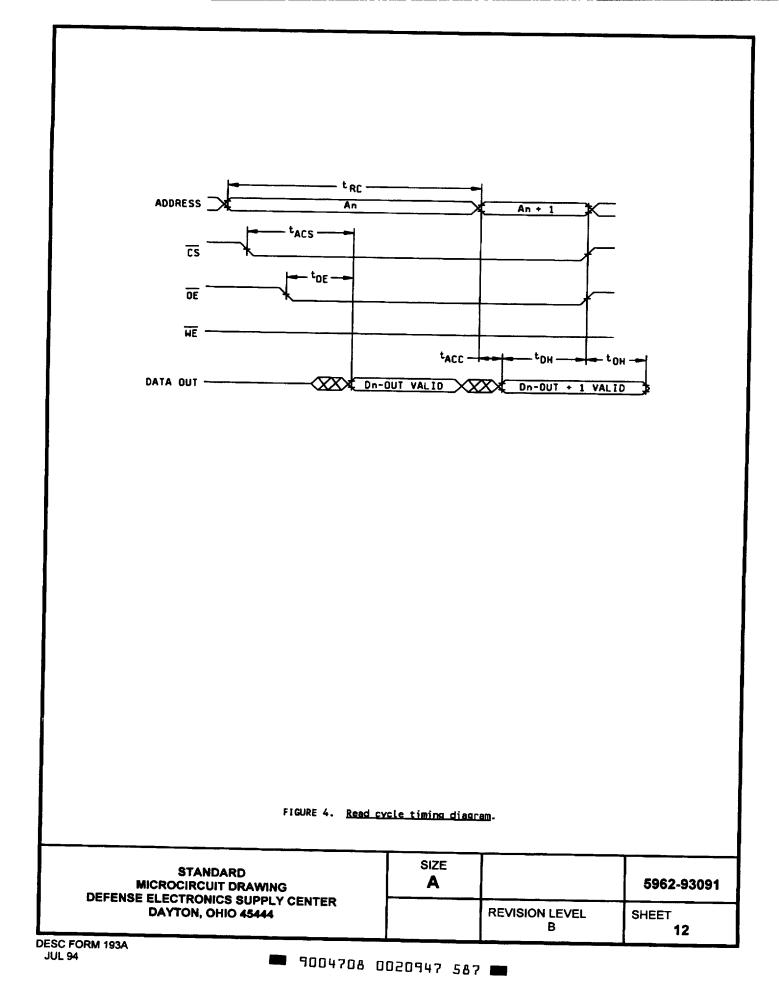

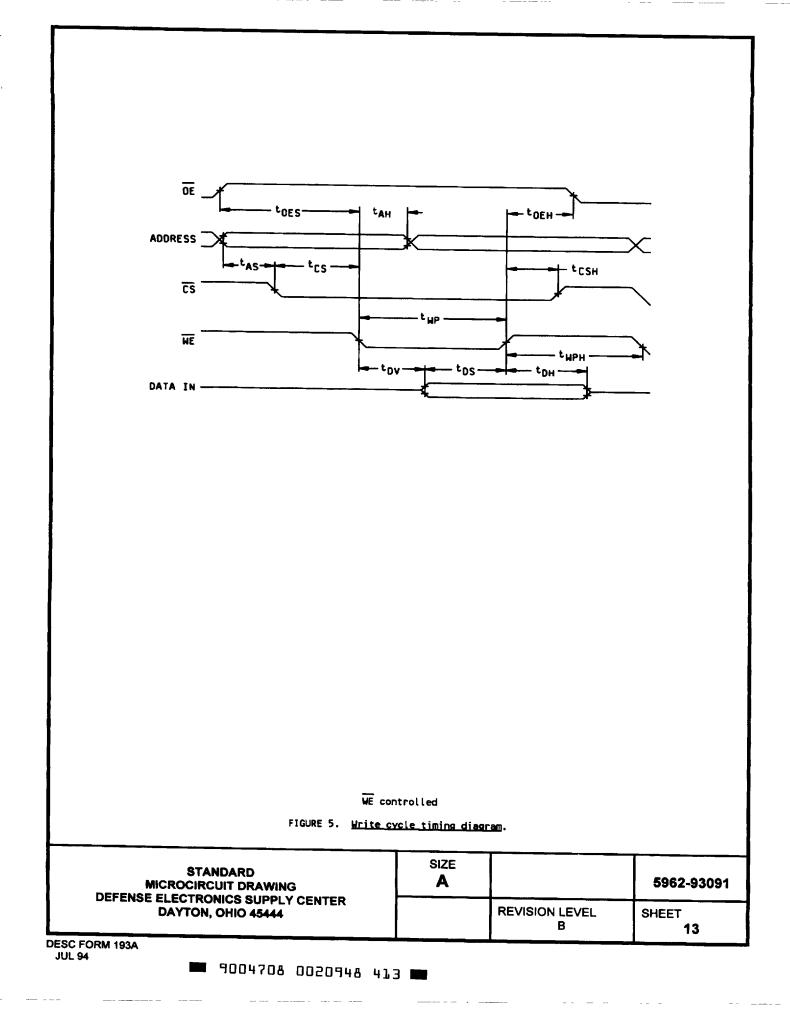

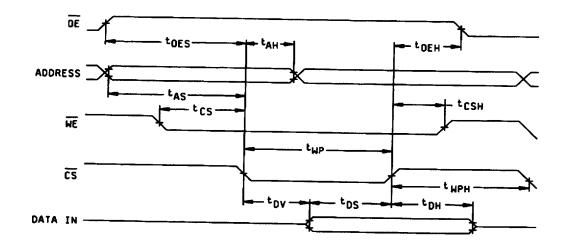

- 3.2.4 <u>Timing diagram(s)</u>. The timing diagram(s) shall be as specified on figures 4, 5, 6, 7, and 8.

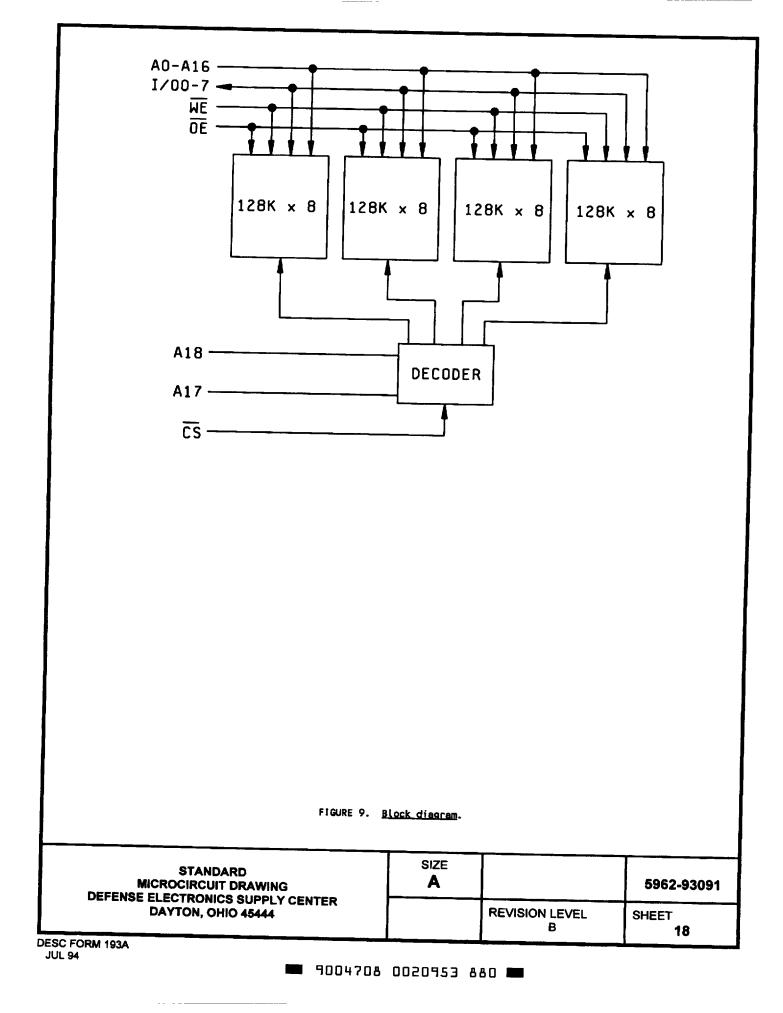

- 3.2.5 Block diagram. The block diagram shall be as specified on figure 9.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full specified operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38534. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in QML-38534.

- 3.6 Manufacturer eligibility. In addition to the general requirements of MIL-PRF-38534, the manufacturer of the part described herein shall maintain the electrical test data (variables format) from the initial quality conformance inspection group A lot sample, produced on the certified line, for each device type listed herein. The data should also include a summary of all parameters manually tested, and for those which, if any, are guaranteed. This data shall be maintained under document revision level control by the manufacturer and be made available to the preparing activity (DESC-EL) upon request.

- 3.7 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to supply to this drawing. The certificate of compliance submitted to DESC-EL shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38534 and the requirements herein.

- 3.8 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38534 shall be provided with each lot of microcircuits delivered to this drawing.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-93091

REVISION LEVEL

B

SHEET

4

DESC FORM 193A JUL 94

**---** 9004708 0020939 400 **---**

| Test                                            | Symbol           | Conditions 1/<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                                                                                   | Group A<br>subgroups | Device<br>type | Limits  |      | Uni t |

|-------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------|------|-------|

|                                                 |                  | V <sub>SS</sub> = Ö V dc<br>+4.5 V dc ≤ V <sub>CC</sub> ≤ +5.5 V dc<br>unless otherwise specified                                                  |                      |                | Min Max |      |       |

| DC PARAMETERS                                   |                  |                                                                                                                                                    |                      |                |         |      |       |

| Supply current                                  | 1 CC             | CS = OE = V <sub>IL</sub> , WE = V <sub>IH</sub> , I/O O through I/O 7 = open, inputs = V <sub>CC</sub> = 5.5 V dc, AO through A18 change at 5 MHz | 1, 2, 3              | All            |         | 180  | mA    |

| Standby current                                 | ISB              | CS = V <sub>CC</sub> , I/O 0 through I/O 7 = open, inputs = V <sub>CC</sub> = 5.5 V dc, A0 through A18 change at 5 MHz                             | 1, 2, 3              | All            |         | 10   | mA    |

| Input leakage current                           | ILI              | VIN = VSS to VCC                                                                                                                                   | 1, 2, 3              | All            |         | 80   | μΑ    |

| Output leakage current                          | ILO              | V <sub>OUT</sub> = V <sub>SS</sub> to V <sub>CC</sub> , cs = V <sub>IH</sub>                                                                       | 1, 2, 3              | ALL            |         | 80   | μΑ    |

| Input low voltage                               | VIL              |                                                                                                                                                    | 1, 2, 3              | All            |         | 0.8  | v     |

| Input high voltage                              | v <sub>IH</sub>  |                                                                                                                                                    | 1, 2, 3              | ALL            | 2.0     |      | v     |

| Output low voltage                              | v <sub>OL</sub>  | I <sub>OL</sub> = 2.1 mA, V <sub>CC</sub> = +4.5 V                                                                                                 | 1, 2, 3              | All            |         | 0.45 | v     |

| Output high voltage                             | VOH              | I <sub>OH</sub> = -400 μA,<br>V <sub>CC</sub> = +4.5 V                                                                                             | 1, 2, 3              | ALL            | 2.4     |      | v     |

| FUNCTIONAL TESTING                              |                  |                                                                                                                                                    | 1                    |                |         |      |       |

| Functional tests                                |                  | See 4.3.1c                                                                                                                                         | 7, 8A, 8B            | All            |         |      |       |

| V <sub>CC</sub> sense write inhibit             | VSENS            | See 4.3.1c                                                                                                                                         | 7, 8A, 8B            | 05             | 3.0     | 4.3  | ٧     |

| V <sub>CC</sub> Power on delay<br>write inhibit | V <sub>POD</sub> | See 4.3.1c                                                                                                                                         | 7, 8A, 8B            | 05             |         | 10   | mS    |

| DYNAMIC CHARACTERISTICS                         | ,                |                                                                                                                                                    |                      | •              |         |      |       |

| Input capacitance                               | CIN              | V <sub>IN</sub> = 0 V dc <u>2</u> /                                                                                                                | 4                    | All            |         | 90   | pF    |

| Output capacitance                              | COUT             | V <sub>OUT</sub> = 0 V dc 2/                                                                                                                       | 4                    | ALL            |         | 120  | pF    |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-93091 |

|------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET 5    |

DESC FORM 193A JUL 94

**9**004708 0020940 122 **1**

| Test                                                                | Symbol           | Conditions 1/<br>-55°C ≤ T <sub>C</sub> ≤ +125°C<br>V <sub>SS</sub> = 0 V dc | Group A<br>subgroups | Device<br>type          | Limits                   |                          | Unit     |

|---------------------------------------------------------------------|------------------|------------------------------------------------------------------------------|----------------------|-------------------------|--------------------------|--------------------------|----------|

|                                                                     |                  | +4.5 V dc < V <sub>CC</sub> < +5.5 V dc unless otherwise specified           |                      |                         | Min                      | Min Max                  |          |

| READ CYCLE AC TIMING CHA                                            | RACTERIST        | ics                                                                          |                      |                         |                          |                          |          |

| Read cycle time                                                     | <sup>t</sup> RC  | See figure 4                                                                 | 9, 10, 11            | 01<br>02<br>03<br>04.05 | 150<br>300<br>250<br>200 |                          | ns       |

| Address access time                                                 | † <sub>ACC</sub> | See figure 4                                                                 | 9, 10, 11            | 01<br>02<br>03<br>04.05 |                          | 150<br>300<br>250<br>200 | ns       |

| Chip select access time                                             | tACS             | See figure 4                                                                 | 9, 10, 11            | 01<br>02<br>03<br>04.05 |                          | 150<br>300<br>250<br>200 | ns       |

| Output ho <u>ld</u> fro <u>m</u> address<br><u>change OE or C\$</u> | <sup>t</sup> OH  | See figure 4                                                                 | 9, 10, 11            | Ail                     | 0                        |                          | ns       |

| Output enable to output valid                                       | t <sub>OE</sub>  | See figure 4                                                                 | 9, 10, 11            | 01,04,05<br>02<br>03    |                          | 85<br>125<br>100         | ns       |

| BYTE WRITE AC TIMING CHA                                            | RACTERIST        | ics                                                                          | <del>,</del>         |                         |                          |                          |          |

| Address setup time                                                  | t <sub>AS</sub>  | See figure 5                                                                 | 9, 10, 11            | ALL                     | 10                       |                          | ns       |

| Write pulse width                                                   | t <sub>WP</sub>  | See figure 5                                                                 | 9, 10, 11            | 01-04                   | 150                      |                          | _ ns     |

|                                                                     |                  | See figure 5, t <sub>CS</sub> > 50 ns                                        |                      | 05                      | 110                      |                          |          |

| Chip select setup time                                              | <sup>t</sup> cs  | See figure 5                                                                 | 9, 10, 11            | ALL                     | 0                        |                          | ns       |

| Address hold time                                                   | t <sub>AH</sub>  | See figure 5 3/                                                              | 9, 10, 11            | Alt                     | 125                      |                          | ns       |

| Data valid to end of write                                          | t <sub>DV</sub>  | See figure 5                                                                 | 9, 10, 11            | ALL                     | 100                      |                          | ns       |

| Output enable setup<br>time                                         | <sup>t</sup> OES | See figure 5                                                                 | 9, 10, 11            | ALL                     | 10                       |                          | ns       |

| Data hold time                                                      | <sup>t</sup> DH  | See figure 5                                                                 | 9, 10, 11            | All                     | 10                       |                          | ns       |

| Output enable hold time                                             | <sup>t</sup> OEH | See figure 5                                                                 | 9, 10, 11            | ALL                     | 10                       |                          | ns       |

| See footnotes at end of t                                           | able.            |                                                                              |                      |                         |                          |                          |          |

|                                                                     | TANDARI          |                                                                              | SIZE<br>A            |                         |                          | 55                       | 062-9309 |

DESC FORM 193A JUL 94

**■ 9004708 0020941 069 ■**

**REVISION LEVEL**

В

SHEET

6

MICROCIRCUIT DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER**

DAYTON, OHIO 45444

| Test                             | Symbol            | Conditions $1/$ -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C $V_{SS} = 0$ V dc | Group A<br>subgroups | Device<br>type | Limits                         |     | Unit |

|----------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------|----------------|--------------------------------|-----|------|

|                                  |                   | +4.5 V dc & V <sub>CC</sub> & +5.5 V dc<br>unless otherwise specified       |                      |                | Min                            | Max |      |

| BYTE WRITE AC TIMING CHA         | RACTERIST         | ICS - Continued                                                             |                      |                |                                |     |      |

| Chip select hold time            | <sup>t</sup> CSH  | See figure 5                                                                | 9, 10, 11            | ALL            | 0 4/<br>25 <b>5</b> /          |     | ns   |

| Write pulse width high           | t <sub>WPH</sub>  | See figure 5                                                                | 9, 10, 11            | Ali            | 50                             |     | ns   |

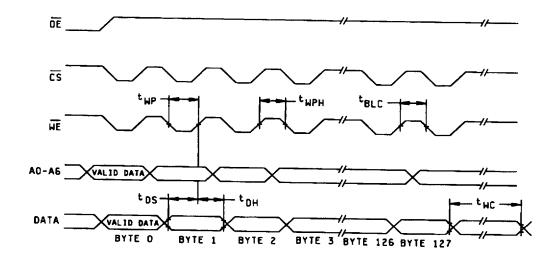

| PAGE MODE WRITE AC TIMIN         | G CHARACT         | ERISTICS                                                                    |                      |                |                                |     |      |

| Data setup time                  | t <sub>DS</sub>   | See figure 6                                                                | 9, 10, 11            | ALL            | 100                            |     | ns   |

| Data hold time                   | t <sub>DH</sub>   | See figure 6                                                                | 9, 10, 11            | ALL            | 10                             |     | ns   |

| Write pulse width                | t <sub>WP</sub>   | See figure 6                                                                | 9, 10, 11            | ALL            | 150                            |     | ns   |

| Byte load cycle time             | tBLC              | See figure 6                                                                | 9, 10, 11            | ALL            |                                | 150 | μs   |

| Write pulse width high           | twen              | See figure 6                                                                | 9, 10, 11            | ALL            | 50                             |     | ns   |

| Write cycle time                 | twc               | See figure 6                                                                | 9, 10, 11            | ALL            |                                | 10  | ms   |

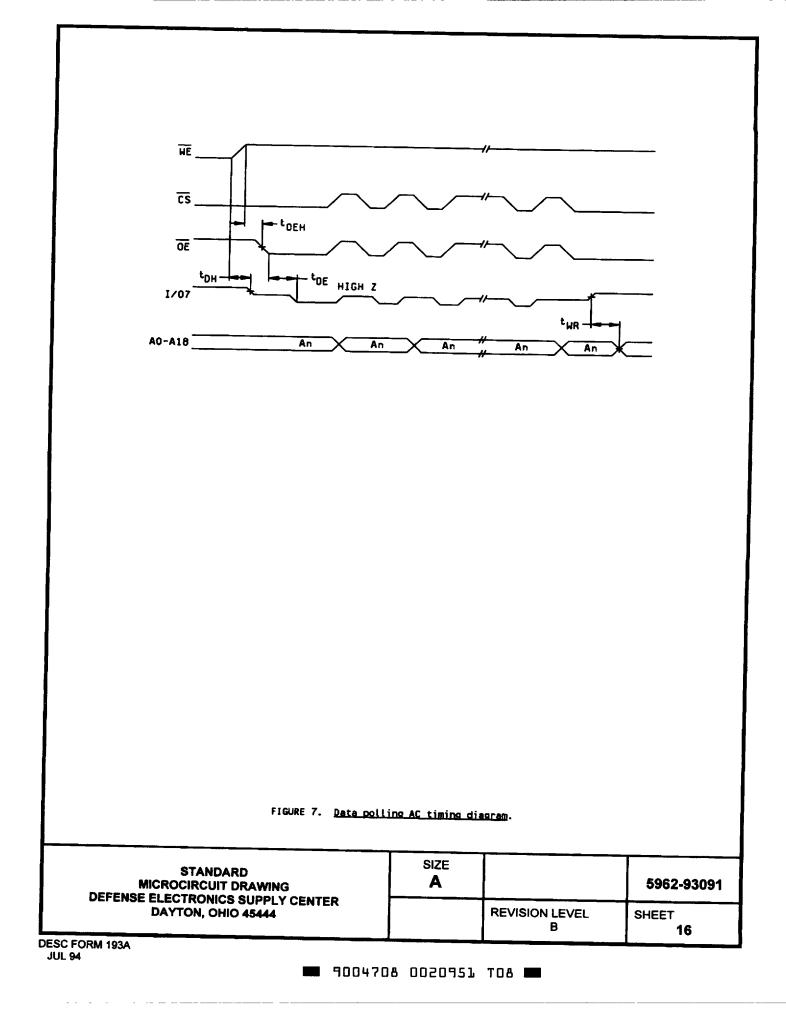

| DATA POLLING AC TIMING C         | <u>HARACTER I</u> | STICS                                                                       |                      |                | ·                              |     |      |

| Data hold time                   | t <sub>DH</sub>   | See figure 7                                                                | 9, 10, 11            | ALL            | 10 4/<br>35 <b>5</b> /         |     | ns   |

| Output enable hold time          | <sup>t</sup> OEH  | See figure 7                                                                | 9, 10, 11            | ALL            | 10 <u>4</u> /<br>35 <u>5</u> / |     | ns   |

| Output enable to output<br>delay | t <sub>OE</sub>   | See figure 7                                                                | 9, 10, 11            | ALL            |                                | 100 | ns   |

| Write recovery time              | twR               | See figure 7                                                                | 9, 10, 11            | ALL            | 0                              |     | ns   |

See footnotes at end of table

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-93091

REVISION LEVEL

B

7

DESC FORM 193A JUL 94

9004708 0020942 TT5

| Test                   | Symbol         | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                          | Group A<br>subgroups | Device<br>type                        | Limits |      | Unit |

|------------------------|----------------|---------------------------------------------------------------------------------------------------|----------------------|---------------------------------------|--------|------|------|

|                        |                | V <sub>SS</sub> = 0 V dc<br>+4.5 V dc ≤ V <sub>CC</sub> ≤ +5.5 V dc<br>unless otherwise specified |                      |                                       | Min    | Max  |      |

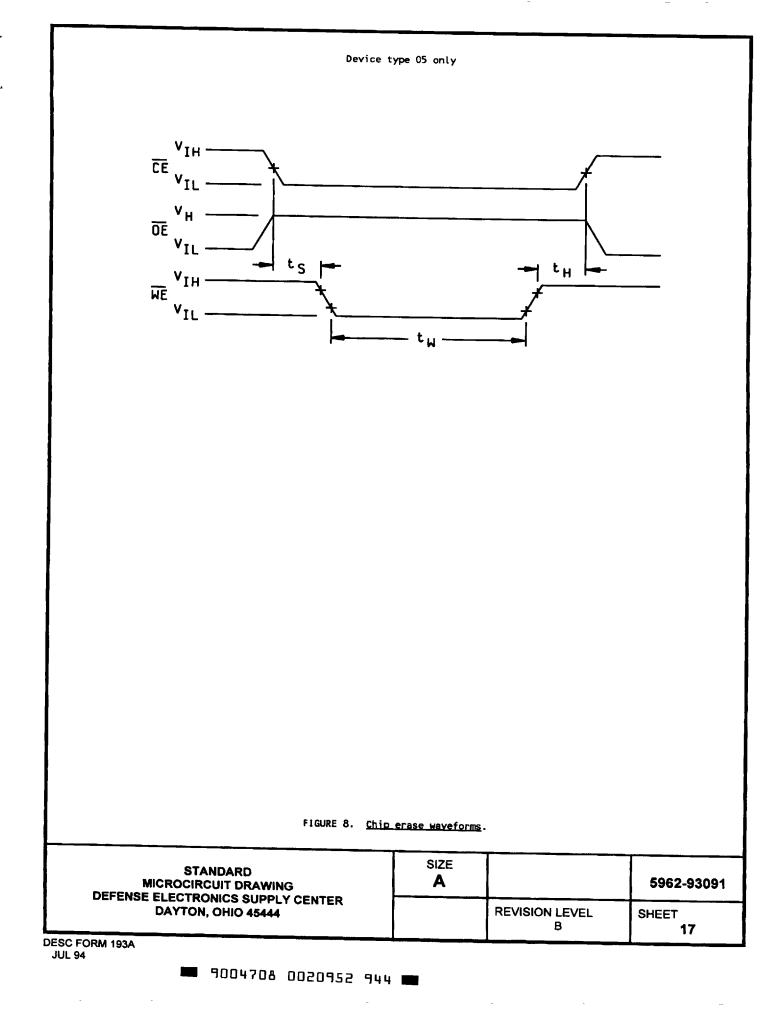

| CHIP ERASE CHARACTERIS | STICS          | · · · · · · · · · · · · · · · · · · ·                                                             |                      | · · · · · · · · · · · · · · · · · · · |        | 1    |      |

| Setup time 6/          | <sup>t</sup> s | See figure 8                                                                                      | 7,8A,8B              | 05                                    | 5      |      | μs   |

| Pulse width 6/         | tu             | See figure 8                                                                                      | 7,8A,8B              | 05                                    | 10     |      | ms   |

| Chip erase voltage     | v <sub>H</sub> |                                                                                                   | 7,8A,8B              | 05                                    | 11.4   | 12.6 | v    |

| Hold time <u>6</u> /   | t <sub>H</sub> | See figure 8                                                                                      | 7,8A,8B              | 05                                    | 5      |      | μs   |

1/ Unless otherwise specified; the AC test conditions are as follows:

Input pulse levels:  $V_{IL} = 0$  V and  $V_{IH} = 3.0$  V. Input rise and fall times: 5 ns.

Input and output timing reference levels: 1.5 V.

2/ Parameters shall be tested as part of device characterization and after design and process changes. Parameters shall be guaranteed to the limits specified in table I for all lots not specifically tested.

A17 and A18 must remain valid through the WE or CS low pulse.

WE controlled CS controlled

6/ Data FF for all addresses following sequence.

**STANDARD** MICROCIRCUIT DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444**

SIZE 5962-93091 Α **REVISION LEVEL** SHEET 8

**DESC FORM 193A JUL 94**

**■** 9004708 0020943 931 **■**

| Symbol | Inch  | nes   | Milli     | meters |  |

|--------|-------|-------|-----------|--------|--|

|        | Min   | Max   | Min       | Max    |  |

| A      | 1.654 | 1.686 | 42.01     | 42.82  |  |

| В      | 0.580 | 0.600 | 14.73     | 15.24  |  |

| С      | 0.235 | 0.275 | 5.97      | 6.99   |  |

| D      | 0.016 | 0.020 | 0.41      | 0.51   |  |

| ε      | 0.045 | 0.055 | 1.14      | 1.40   |  |

| F      | 0.100 | TYP.  | 2.54 TYP. |        |  |

| G      | 0.015 | 0.060 | 0.38      | 1.52   |  |

| н      | 0.125 | MIN.  | 3.18      | MIN.   |  |

| J      | 0.008 | 0.012 | 0.20      | 0.30   |  |

| K      | 0.590 | 0.610 | 14.99     | 15.49  |  |

| L      | 0.085 | TYP.  | 2.16 TYP. |        |  |

FIGURE 1. Case outline.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br><b>A</b> |                     | 5962-93091 |

|------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>B | SHEET<br>9 |

DESC FORM 193A JUL 94

**=** 9004708 0020944 878 **=**

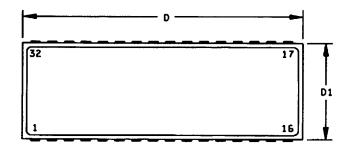

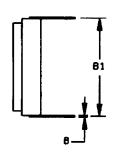

#### Case outline Y

| Symbol | Inches     |       | Millimeters |       |

|--------|------------|-------|-------------|-------|

|        | Min        | Max   | Min         | Max   |

| D      | 1.654      | 1.686 | 42.01       | 42.82 |

| D1     | 0.580      | 0.600 | 14.73       | 15.24 |

| Α      | 0.161      | 0.181 | 4.10        | 4.60  |

| e1     | 0.016      | 0.020 | 0.41        | 0.51  |

| D2     | 1.492      | 1.508 | 38.02       | 38.30 |

| e      | 0.100 TYP. |       | 2.54 TYP.   |       |

| A1     | 0.027      | 0.047 | 0.69        | 1.14  |

| A2     | 0.125 MIN. |       | 3.18        | MIN.  |

| В      | 0.009      | 0.012 | 0.23        | 0.30  |

| B1     | 0.590      | 0.610 | 14.99       | 15.49 |

NOTE: The U.S. government preferred system of measurement is the metric SI. These case outlines were designed using inch-pound units of measurement. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

FIGURE 1. <u>Case outlines</u> - Continued.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                     | 5962-93091  |

|------------------|---------------------|-------------|

|                  | REVISION LEVEL<br>B | SHEET<br>10 |

DESC FORM 193A JUL 94

**9004708 0020945 704**

| Device types                                                           | 01-05                               |

|------------------------------------------------------------------------|-------------------------------------|

| Case outline                                                           | X and Y                             |

| Terminal number                                                        | Terminal connection                 |

| Terminal number  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 | Terminal connection                 |

| 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32         | A10 OE A11 A9 A8 A13 A14 A17 WE VCC |

FIGURE 2. <u>Terminal connections</u>.

| cs  | ŌĒ | WE | A0-A18 | MODE          | DATA I/O        | DEVICE<br>CURRENT |

|-----|----|----|--------|---------------|-----------------|-------------------|

| _#_ | X  | Х  | х      | Standby       | High Z          | Standby           |

|     |    |    | Stable | Read          | Data Out        | Active            |

|     | H  |    | Stable | Write         | Data In         | Active            |

| X   | H  | X  | Х      | Out Disable   | High Z          | Active            |

| _X_ | X_ | Н  | X      | Write inhibit | High Z/Data out | Active            |

| X   |    | X_ | Х      | Write inhibit | High Z/Data out | Active            |

#### NOTES:

- 1. H = V<sub>IH</sub> = High Logic Level

2. L = V<sub>IL</sub> = Low Logic Level

3. X = Do not care (either High or Low)

4. High Z = High Impedance state

FIGURE 3. <u>Iruth table</u>.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-93091      |

|------------------------------------------------------------------------------------|------------------|---------------------|-----------------|

|                                                                                    |                  | REVISION LEVEL<br>B | SHEET <b>11</b> |

DESC FORM 193A JUL 94

**9**004708 0020946 640 **1**

#### NOTES:

1. A write cycle is initiated when OE is high and WE or CS is pulsed low when CS or WE is low. The address

A Write cycle is initiated when DE\_IS high and WE or CS is pulsed low when CS or WE is low. The address is latched on the falling edge of WE or CS, whichever occurs first. In either case, the address setup requirement applies to the falling edge of CS due to the inclusion of an address decoder in the device.

Due to the inclusion of the address decoder in the device, the WE and CS write control timings will vary. When utilizing the CS controlled write operation, all hold timings must be extended by the 25 ns propagation delay of the address decoder. For a WE controlled write operation, CS must be a minimum of 125 ns to accommodate the additional setup time required.

3. The delay required from the previous write operation to the next must be a minimum of 10  $\mu s$ .

#### CS controlled

# FIGURE 5. Write cycle timing diagram - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-93091  |

|---------------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                             |                  | REVISION LEVEL<br>B | SHEET<br>14 |

| C FORM 1934                                                                                 |                  |                     |             |

DESC F **JUL 94**

9004708 0020949 35T **=**

### NOTES:

- 1. A17 and A18 are used to select one of four separate blocks within the device.

- 2. A7 through A16 are used to specify the page address and must be the same throughout a single page mode

- 3. A0 through A6 are used to address specific bytes within a page.

- 5. A write cycle is initiated when OF is high and WE or CS is pulsed low when CS or WE is low. The address is latched on the falling edge of WE or CS, which ever occurs last. In either case, the address setup requirement applies to the falling edge of CS due to the inclusion of an address decoder in the device, (See figure 5).

- 6. The delay required from the previous write operation to the next must be a minimum of 10  $\mu$ s.

FIGURE 6. Page mode write timing diagram.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br>A |                     | 5962-93091  |

|------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>B | SHEET<br>15 |

DESC FORM 193A **JUL 94**

9004708 0020950 071 🖿

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with MIL-PRF-38534.

- 4.2 <u>Screening</u>. Screening shall be in accordance with MIL-PRF-38534. The following additional criteria shall apply:

- Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D or E. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DESC-EL or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2) TA as specified in accordance with table I of method 1015 of MIL-STD-883.

- (3) Prior to burn-in all devices shall be programmed with a 00 hex data pattern to the entire memory array. The resulting pattern shall be verified before and after burn-in. Devices having bits not in the proper state after burn-in shall constitute a device failure and shall not be delivered.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with MIL-PRF-38534 and as specified herein.

- 4.3.1 Group A inspection. Group A inspection shall be in accordance with MIL-PRF-38534 and as follows:

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 shall be omitted.

- c. Subgroups 7, 8A, and 88 shall include verification of the truth table on figure 3.

- d. The following data patterns shall be verified during subgroups 7, 8A, and 8B:

- (1) 0's to all memory cell locations.

- (2) 1's to all memory cell locations.

- (3) Checkerboard pattern to entire memory array.

- (4) Checkerboard compliment to entire memory array.

- 4.3.2 Group B inspection. Group B inspection shall be in accordance with MIL-PRF-38534.

- 4.3.3 Group C inspection. Group C inspection shall be in accordance with MIL-PRF-38534 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. All devices requiring end-point electrical testing shall be programmed with a checkerboard pattern of alternate rows of AA hex and 55 hex.

- Steady-state life test, method 1005 of MIL-STD-883.

- (1) Test condition B. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DESC-EL or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- (2) TA as specified in accordance with table I of method 1005 of MIL-STD-883.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- (4) The checkerboard data pattern shall be verified after burn-in as part of end-point electrical testing.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br><b>A</b> |                     | 5962-93091  |

|------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                    |                  | REVISION LEVEL<br>B | SHEET<br>19 |

DESC FORM 193A JUL 94

9004708 0020954 717

## TABLE II. Electrical test requirements.

| MIL-PRF-38534 test requirements                                            | Subgroups<br>(in accordance with<br>MIL-PRF-38534, group<br>A test table) |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Interim electrical parameters                                              | 1, 4, 9                                                                   |

| Final electrical test parameters                                           | 1*, 2, 3, 4, 7, 8A, 8B, 9, 10, 11                                         |

| Group A test requirements                                                  | 1, 2, 3, 4, 7, 8A,<br>8B, 9, 10, 11                                       |

| Group C end-point electrical parameters                                    | 1, 2, 3, 4, 7, 8A,<br>8B, 9, 10, 11                                       |

| MIL-STD-883, Group E end point<br>electrical parameters for RHA<br>devices | Subgroups ** (in accordance with method 5005, group A test table)         |

\* PDA applies to subgroup 1.

- 4.3.4 Group D inspection. Group D inspection shall be in accordance with MIL-PRF-38534.

- 4.3.5 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes H and K shall be M, D, R, and H. RHA quality conformance inspection sample tests shall be performed at the RHA level specified in the acquisition document.

- a. RHA tests for device classes H and K for levels M, D, R, and H shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- b. End-point electrical parameters shall be as specified in table II herein.

- c. Prior to total dose irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table II herein.

- d. For device classes H and K, the devices shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38534 for RHA level being tested, and meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A = +25^{\circ}\text{C}$  ±5 percent, after exposure.

- e. Prior to and during total dose irradiation testing, the devices shall be biased to establish a worst case condition as specified in the radiation exposure circuit.

- f. For device classes H and K, subgroups 1 and 2 in table V, method 5005 of MIL-STD-883 shall be tested as appropriate for device construction.

- g. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-PRF-38534.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE |                     | 5962-93091 |

|---------------------------------------------------------------------------------------------|------|---------------------|------------|

|                                                                                             |      | REVISION LEVEL<br>B | SHEET 20   |

DESC FORM 193A JUL 94

**■ 9004708 0020955 653 ■**

<sup>\*\*</sup> When applicable to this standardized military drawing, the subgroups shall be defined.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-EL, telephone (513) 296-6047.

- 6.5 <u>Comments</u>. Comments on this drawing should be directed to DESC-EL, Dayton, Ohio 45444, or telephone

- 6.6 One part one part number system. The one part one part number system described below has been developed to allow for transitions between identical generic devices covered by the three major microcircuit requirements documents MIL-PRF-38534, MIL-PRF-38535, and 1.2.1 of MIL-STD-883) without the necessity for the generation of unique PIN's. The three military requirements documents represent different class levels, and previously when a device manufacturer upgraded military product from one class level to another, the benefits of the upgraded product were unavailable to the Original Equipment Manufacturer (OEM), that was contractually locked into the original unique PIN. By available for a given generic device to meet system needs without modifying the original contract parts selection criteria.

| Military documentation format                              | Example PIN<br>under new system | Manufacturing<br>Source listing | Document<br>Listing |

|------------------------------------------------------------|---------------------------------|---------------------------------|---------------------|

| New MIL-PRF-38534 Standard Microcircuit<br>Drawings        | 5962-XXXXXZZ(H or K)YY          | QML-38534                       | MIL-HDBK-103        |

| New MIL-PRF-38535 Standard Microcircuit<br>Drawings        | 5962-XXXXXZZ(Q or V)YY          | QML-38535                       | MIL-HDBK-103        |

| New 1.2.1 of MIL-STD-883 Standard<br>Microcircuit Drawings | 5962-XXXXXZZ(M)YY               | MIL-HDBK-103                    | MIL-HDBK-103        |

6.7 <u>Sources of supply for device classes H and K</u>. Sources of supply for device classes H and K are listed in QML-38534. The vendors listed in QML-38534 have submitted a certificate of compliance (see 3.7 herein) to DESC-EL and

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE **5962-93091**REVISION LEVEL SHEET **21**

DESC FORM 193A JUL 94