## PRELIMINARY

## **Network Buffer Management Unit NBMU**

| F | F | Δ | Т | II | R | F | ç |

|---|---|---|---|----|---|---|---|

|   |   |   |   |    |   |   |   |

☐ Auto refresh cycle generation

☐ Refresh 64K DRAM

☐ Compatible with SMC's COM90C56 Enhanced Local Area Network Controller (ELANC)

☐ Low power CMOS

☐ Replaces several MSI/LSI devices

☐ Simplifies the interface of COM90C56 to lower cost DRAM

☐ Single +5v supply

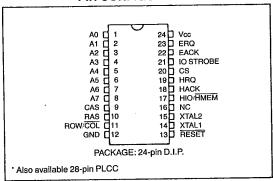

## **PIN CONFIGURATION\***

Pin configuration subject to change, contact factory for details.

## **GENERAL DESCRIPTION**

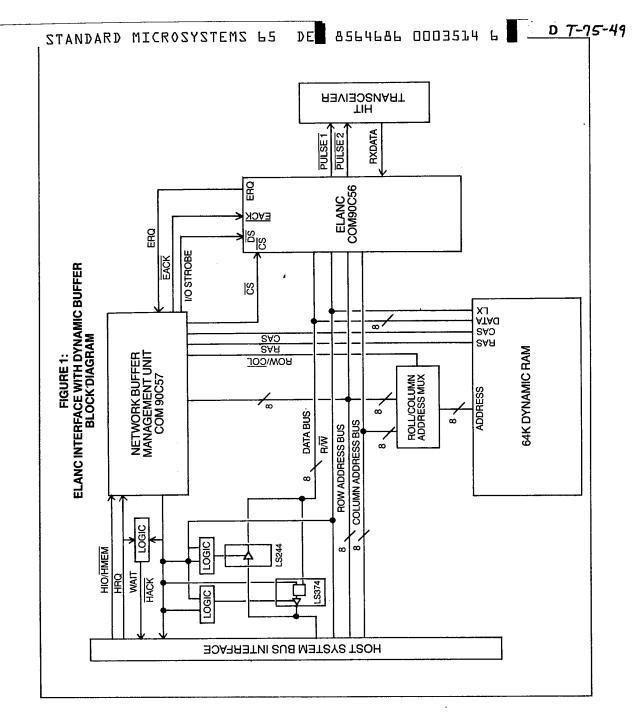

The NBMU provides the arbitration and memory control required to manage a dynamic memory buffer which is shared by the ELANC and a Host processor. Both access arbitration and dynamic memory refresh are taken care of by the NBMU so that minimal additional circuitry is required

to construct an efficient shared dynamic memory buffer interface between the ELANC and a Host system. Figure 1 shows how such an interface might be constructed using the NBMU.

Circuit diagrams utilizing SMC products are included as a means of illustrating typical applications; consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the products described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.