## U441 MONOLITHIC DUAL N-CHANNEL JFET

# Linear Systems replaces discontinued Siliconix U441

## The U441 is a tightly matched Monolithic Dual N-Channel JFET

The U441 are monolithic dual JFETs mounted in a single TO-71 package. The monolithic dual chip design reduces parasitics and gives better performance at very high frequencies while ensuring extremely tight matching. These devices are an excellent choice for use as wideband differential amplifiers in demanding test and measurement applications. The U441 is a direct replacement for discontinued Siliconix U441.

The hermetically sealed TO-71 is well suited for military applications.

(See Packaging Information).

### **U441 Applications:**

- Wideband Differential Amps

- High-Speed,Temp-Compensated Single-Ended Input Amps

- High-Speed Comparators

- Impedance Converters and vibrations detectors.

| FEATURES                              |                        |  |  |  |  |  |  |

|---------------------------------------|------------------------|--|--|--|--|--|--|

| Direct Replacement for SILICONIX U441 |                        |  |  |  |  |  |  |

| HIGH CMRR                             | CMRR ≥ 85dB            |  |  |  |  |  |  |

| LOW GATE LEAKAGE                      | I <sub>GSS</sub> ≤1 pA |  |  |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup> |                        |  |  |  |  |  |  |

| @ 25°C (unless otherwise noted)       |                        |  |  |  |  |  |  |

| Maximum Temperatures                  |                        |  |  |  |  |  |  |

| Storage Temperature                   | -65°C to +150°C        |  |  |  |  |  |  |

| Operating Junction Temperature        | -55°C to +135°C        |  |  |  |  |  |  |

| Maximum Power Dissipation             |                        |  |  |  |  |  |  |

| Continuous Power Dissipation (Total)  | 500mW                  |  |  |  |  |  |  |

| Maximum Currents                      |                        |  |  |  |  |  |  |

| Gate Current                          | 50mA                   |  |  |  |  |  |  |

| Maximum Voltages                      |                        |  |  |  |  |  |  |

| Gate to Drain                         | -25V                   |  |  |  |  |  |  |

| Gate to Source                        | -25V                   |  |  |  |  |  |  |

| Gate to Gate                          | ±50V                   |  |  |  |  |  |  |

MATCHING CHARACTERISTICS @ 25°C (unless otherwise stated)

| SYMBOL                                | CHARACTERISTIC                              | MIN | TYP  | MAX | UNITS | CONDITIONS                                         |

|---------------------------------------|---------------------------------------------|-----|------|-----|-------|----------------------------------------------------|

| $ V_{GS1} - V_{GS2} $                 | Differential Gate to Source Cutoff Voltage  |     |      | _20 | mV    | $V_{DG} = 10V, I_{D} = 5mA$                        |

| $\Delta  V_{GS1} - V_{GS2} /\Delta T$ | Differential Gate to Source Cutoff          |     | 20   |     | μV/°C | $V_{DG} = 10V, I_{D} = 5mA$                        |

|                                       | Voltage Change with Temperature             |     |      |     |       | T <sub>A</sub> = -55°C to +125°C                   |

| I <sub>DSS1</sub> / I <sub>DSS2</sub> | Gate to Source Saturation Current Ratio     |     | 0.07 |     | %     | $V_{DS} = 10V$ , $V_{GS} = 0V$                     |

| G <sub>fs1</sub> / G <sub>fs2</sub>   | Forward Transconductance Ratio <sup>2</sup> |     | 0.97 |     | %     | $V_{DS} = 10V, I_{D} = 5mA, f = 1kHz$              |

| CMRR                                  | Common Mode Rejection Ratio                 |     | 85   |     | dB    | $V_{DG} = 5 \text{ to } 10V, I_{D} = 5 \text{ mA}$ |

### ELECTRICAL CHARACTERISTICS @ 25°C (unless otherwise noted)

| SYMBOL           | CHARACTERISTICS                   | MIN. | TYP. | MAX. | UNITS  | CONDITIONS                                   |

|------------------|-----------------------------------|------|------|------|--------|----------------------------------------------|

| $BV_GSS$         | Gate to Source Breakdown Voltage  | -25  |      |      | V      | $I_{G} = -1\mu A$ , $V_{DS} = 0V$            |

| $V_{GS(off)}$    | Gate to Source Cutoff Voltage     | -1   | -3.5 | -6   | V      | $V_{DS} = 10V, I_{D} = 1nA$                  |

| I <sub>DSS</sub> | Gate to Source Saturation Current | 6    | 15   | 30   | mA     | $V_{DS} = 10V, V_{GS} = 0V$                  |

| I <sub>GSS</sub> | Gate Leakage Current <sup>3</sup> |      | -1   | -500 | pА     | $V_{GS} = -15V, V_{DS} = 0V$                 |

| I <sub>G</sub>   | Gate Operating Current            |      | -1   | -500 | pA     | $V_{DG} = 10V, I_D = 5mA$                    |

| <b>g</b> fs      | Forward Transconductance          | 4.5  | 6    | 9    | mS     | $V_{DS} = 10V, I_{D} = 5mA, f = 1kHz$        |

| g <sub>os</sub>  | Output Conductance                |      | 70   | 200  | μS     |                                              |

| C <sub>ISS</sub> | Input Capacitance                 |      | 3    |      | pF     | $V_{DS} = 10V$ , $I_D = 5mA$ , $f = 1MHz$    |

| $C_{RSS}$        | Reverse Transfer Capacitance      |      | 1    |      | pF     |                                              |

| e <sub>n</sub>   | Equivalent Input Noise Voltage    |      | 4    |      | nV/√Hz | $V_{DS} = 10V$ , $I_{D} = 5mA$ , $f = 10kHz$ |

#### Notes:

- 1. Absolute Maximum ratings are limiting values above which serviceability may be impaired

- 2. Pulse Test: PW ≤ 300µs Duty Cycle ≤ 3%

- 3. Assumes smaller value in numerator

Available Packages:

U441 in TO-71 U441 available as bare die micross

Please contact Micross for full package and die dimensions:

Email: <a href="mailto:chipcomponents@micross.com">chipcomponents@micross.com</a>

Web: <a href="mailto:www.micross.com/distribution.aspx">www.micross.com/distribution.aspx</a>

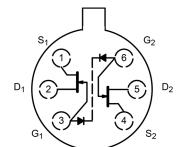

TO-71 (Top View)

Information furnished by Linear Integrated Systems and Micross Components is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.