## Philips Components-Signetics

| Document No.  | 853-1380              |

|---------------|-----------------------|

| ECN No.       | 01043                 |

| Date of Issue | November 12, 1990     |

| Status        | Product Specification |

| Memory Produ  | icts                  |

# **27C210**1 MEG CMOS EPROM (64K × 16)

## DESCRIPTION

Philips Components-Signetics 27C210 CMOS EPROM is a 1,048,576-bit 5V read only memory organized as 65,536 words of 16 bits each. It employs advanced CMOS circuitry for systems requiring low power, high-performance speeds, and immunity to noise. The 27C210 has a non-multiplexed addressing interface and is plug-compatible with the industry standard 27210.

Quick-pulse programming is employed on plastic devices which may speed up programming by as much as one hundred times. In the absence of quick-pulse programming equipment, the intelligent programming algorithm may be utilized.

The 27C210 is offered in windowed Ceramic Dual In-Line, Plastic Dual In-Line and Plastic Leaded Chip Carrier (PLCC) packages. This device can be programmed with standard EPROM programmers.

## **FEATURES**

- Low power consumption

- 100µA maximum CMOS standby current

- High-performance speed

- 120ns maximum access time

- Noise immunity features

- ±10% V<sub>CC</sub> tolerance

- Maximum latch-up immunity through Epitaxial processing

- Quick-pulse programming algorithm

#### PIN DESCRIPTION

| FIN DESCRI      | III DEGGIIII 11011 |  |  |  |  |

|-----------------|--------------------|--|--|--|--|

| A0 - A15        | Address            |  |  |  |  |

| O0 - O15        | Outputs            |  |  |  |  |

| <u>OE</u>       | Output Enable      |  |  |  |  |

| CE              | Chip Enable        |  |  |  |  |

| PGM             | Program Enable     |  |  |  |  |

| NC              | No Connection      |  |  |  |  |

| GND             | Ground             |  |  |  |  |

| V <sub>PP</sub> | Program voltage    |  |  |  |  |

| V <sub>CC</sub> | Power supply       |  |  |  |  |

| DU              | Don't Use          |  |  |  |  |

|                 |                    |  |  |  |  |

#### PIN CONFIGURATIONS

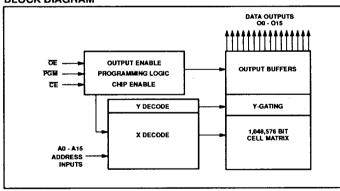

## **BLOCK DIAGRAM**

27C210

#### **READ MODE**

The 27C210 has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip enable (ĈE) is the power control and should be used for device selection. Output Enable (ÕE) is the output control and should be used to gate

data from the output pins. Data is available at the outputs after a delay of  $t_{\rm CE}$  from the falling edge of  ${\rm OE}$ , assuming that  ${\rm CE}$  has been low and addresses have been stable for at least  $t_{\rm ACC}$  -  $t_{\rm OE}$ .

#### STANDBY MODE

The 27C210 has a standby mode which reduces the maximum  $V_{CC}$  current to 100 $\mu$ A. It is placed in the Standby mode when  $\overline{CE}$  is in the High state. When in the Standby mode, the outputs are in a high-impedance state, independent of the  $\overline{OE}$  input.

#### ORDERING INFORMATION

| DESCRIPTION                                                | ORDE                                         | R CODE                       |

|------------------------------------------------------------|----------------------------------------------|------------------------------|

|                                                            | COMMERCIAL                                   | INDUSTRIAL                   |

| 40-Pin Ceramic Dual In-Line with quartz window 600mil-wide | 27C210-12 FA<br>27C210-15 FA<br>27C210-20 FA | 27C210I15 FA<br>27C210I20 FA |

| 40-Pin Plastic Dual In-Line<br>600mil-wide                 | 27C210-12 N<br>27C210-15 N<br>27C210-20 N    | 27C210I15 N<br>27C210I20 N   |

| 44-Pin Plastic Leaded Chip Carrier 0.69 × 0.6              | 27C210-12 A<br>27C210-15 A<br>27C210-20 A    | 27C210I15 A<br>27C210I20 A   |

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL                          | PARAMETER                                                                | RATING        | UNIT |

|---------------------------------|--------------------------------------------------------------------------|---------------|------|

| T <sub>stg</sub>                | Storage temperature range                                                | -65 to +125   | °C   |

| V <sub>I</sub> , V <sub>O</sub> | Voltage inputs and outputs                                               | -0.6 to 6.5   | V    |

| V <sub>H</sub>                  | Voltage on A9 <sup>2</sup> (during intelligent identifier interrogation) | -0.6 to +13.0 | V    |

| Vpp                             | Voltage on V <sub>PP</sub> <sup>2</sup> (during programming)             | -0.6 to +14.0 | V    |

| V <sub>CC</sub>                 | Supply voltage <sup>2</sup>                                              | -0.6 to +7.0  | V    |

## NOTES:

2. All voltages are with respect to network ground.

## **DEVICE OPERATION<sup>1</sup>**

| MODE           | CE              | ŌΕ              | PGM             | V <sub>PP</sub> <sup>2</sup> | OUTPUTS          |

|----------------|-----------------|-----------------|-----------------|------------------------------|------------------|

| Read           | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>CC</sub>              | D <sub>OUT</sub> |

| Output Disable | VIL             | V <sub>IH</sub> | VIH             | Vcc                          | Hi-Z             |

| Standby        | VIH             | X <sup>3</sup>  | X <sup>3</sup>  | Vcc                          | Hi-Z             |

## **OPERATING TEMPERATURE RANGE**

| PARAMETER                         | RATING (°C)              |

|-----------------------------------|--------------------------|

| Operating temperature range: Tamb | COMMERCIAL<br>0 to +70   |

| Operating temperature range. Tamb | INDUSTRIAL<br>-40 to +85 |

- 1. All voltages are with respect to network ground.

- V<sub>PP</sub> may be one diode voltage drop below V<sub>CC</sub>, and can be connected directly to V<sub>CC</sub>.

- 3. X can be VIH or VIL.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

Over operating temperature range, +4.5V ≤ V<sub>CC</sub> ≤ +5.5V

| SYMBOL               | PARAMETER                              | TEST CONDITIONS                                                           | 1                     | LIMITS | •                     | UNIT             |

|----------------------|----------------------------------------|---------------------------------------------------------------------------|-----------------------|--------|-----------------------|------------------|

|                      |                                        |                                                                           | MIN                   | TYP3   | MAX                   |                  |

| Input curren         | t                                      |                                                                           |                       |        |                       |                  |

| l <sub>iH</sub>      | Leakage High                           | V <sub>IN</sub> = 5.5V = V <sub>CC</sub>                                  |                       | 0.01   | 1.0                   | μΑ               |

| I <sub>IL</sub>      | Leakage Low                            | V <sub>IL</sub> = 0V                                                      |                       | 0.01   | -1.0                  | μΑ               |

| Ірр                  | V <sub>PP</sub> read                   | V <sub>PP</sub> = V <sub>CC</sub>                                         |                       |        | 10                    | μА               |

| Output curre         | ent                                    |                                                                           |                       |        |                       |                  |

| lo                   | Leakage                                | OE or CE = V <sub>IH,</sub> V <sub>OUT</sub> = 5.5V = V <sub>CC</sub>     | -10.0                 |        | 10.0                  | μΑ               |

| los                  | Short circuit 7, 9                     | V <sub>OUT</sub> = 0V                                                     |                       |        | 100                   | mA               |

| Supply curre         | ent                                    |                                                                           |                       |        |                       |                  |

| I <sub>CC</sub> TTL  | Operating (TTL inputs) <sup>4, 6</sup> | $CE = OE = V_{IL}$ , $f = 8.3MHz$<br>$V_{PP} = V_{CC}$ , $OO - O15 = OmA$ |                       |        | 50                    | mA               |

| I <sub>CC</sub> CMOS | Operating (CMOS inputs)4,6             | CE = GND, f = 8.3MHz<br>Inputs = V <sub>CC</sub> or GND, I/O = 0mA        |                       |        | 30                    | mA               |

| I <sub>SB</sub> TTL  | Standby (TTL inputs)4                  | CE = V <sub>IH</sub>                                                      |                       |        | 1.0                   | mA               |

| I <sub>SB</sub> CMOS | Standby (CMOS inputs)5                 | CE = V <sub>IH</sub>                                                      |                       |        | 100                   | μА               |

| Input voltag         | e <sup>2</sup>                         |                                                                           |                       |        |                       |                  |

| V <sub>IL</sub>      | Low (TTL)                              | V <sub>PP</sub> = V <sub>CC</sub>                                         | -0.5                  |        | 0.8                   | ٧                |

| V <sub>IL</sub>      | Low (CMOS)                             | V <sub>PP</sub> = V <sub>CC</sub>                                         | -0.2                  |        | 0.2                   | V                |

| V <sub>IH</sub>      | High (TTL)                             | V <sub>PP</sub> = V <sub>CC</sub>                                         | 2.0                   |        | V <sub>CC</sub> + 0.5 | ٧                |

| V <sub>IH</sub>      | High (CMOS)                            | V <sub>PP</sub> = V <sub>CC</sub>                                         | V <sub>CC</sub> - 2.0 |        | V <sub>CC</sub> + 0.2 | ٧                |

| V <sub>PP</sub>      | Read <sup>8</sup>                      | (Operating)                                                               | V <sub>CC</sub> - 0.7 |        | V <sub>.CC</sub>      | ٧                |

| Output volta         | ige <sup>2</sup>                       |                                                                           |                       |        |                       | , and the second |

| V <sub>OL</sub>      | Low                                    | I <sub>OL</sub> = 2.1mA                                                   |                       |        | 0.45                  | ٧                |

| V <sub>OH</sub>      | High                                   | I <sub>OH</sub> = -2.5mA                                                  | 3.5                   |        |                       | ٧                |

| Capacitance          | 9 T <sub>amb</sub> = 25°C              |                                                                           |                       |        |                       |                  |

| CiN                  | Address and control                    | V <sub>CC</sub> ≈ 5.0V, f = 1.0MHz                                        |                       |        | 6                     | pF               |

| C <sub>OUT</sub>     | Outputs                                | V <sub>IN</sub> = 0V, V <sub>OUT</sub> = 0V                               |                       |        | 12                    | pF               |

- 1. Minimum DC input voltage is -0.5V. During transitions the inputs may undershoot to -2.0V for periods less than 20ns.

- 2. All voltages are with respect to network ground.

- Typical limits are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = 25°C.

TTL inputs: Spec V<sub>IL</sub> V<sub>H</sub> levels.

CMOS inputs: GND ±0.2V to V<sub>CC</sub> ±0.2V.

CE is V<sub>CC</sub> ±0.2V. All other inputs can have any value within spec.

Maximum active power usage is the sum of |p<sub>P</sub> + |<sub>CC</sub> and is measured at a frequency of 8.3MHz.

- Test one output at a time, duration should not exceed 1 second.

- V<sub>PP</sub> may be one diode voltage drop below V<sub>CC</sub>, and can be connected directly to V<sub>CC</sub>.

- Guaranteed by design, not 100% tested.

27C210

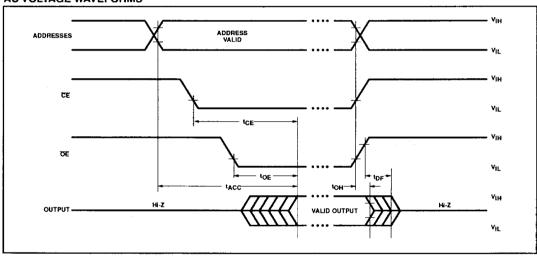

## **AC ELECTRICAL CHARACTERISTICS**

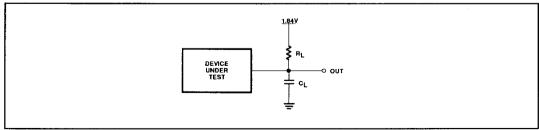

Over operating temperature range,  $+4.5V \le V_{CC} \le +5.5V$ ,  $R_L = 660\Omega$ ,  $C_L = 100pF$

| SYMBOL                    | то          | FROM              | FROM 27C210-12 |     | 27C210-15<br>27C210I15 |     | 27C210-20<br>27C210I20 |     | UNIT |

|---------------------------|-------------|-------------------|----------------|-----|------------------------|-----|------------------------|-----|------|

|                           |             |                   | MIN            | MAX | MIN                    | MAX | MIN                    | MAX |      |

| Access time <sup>1</sup>  |             |                   |                |     | •                      |     |                        |     |      |

| tacc                      | Output      | Address           |                | 120 |                        | 150 |                        | 200 | ns   |

| t <sub>CE</sub>           | Output      | CE                |                | 120 |                        | 150 |                        | 200 | ns   |

| t <sub>OE</sub> 3         | Output      | OE                |                | 50  |                        | 60  |                        | 70  | ns   |

| Disable time <sup>2</sup> |             |                   |                |     |                        |     |                        |     |      |

| t <sub>DF</sub>           | Output Hi-Z | OE .              | T              | 30  |                        | 50  |                        | 60  | ns   |

| tон                       | Output hold | Address, CE or OE | 0              |     | 0                      |     | 0                      |     | ns   |

#### NOTES:

- 1. AC characteristics are tested at  $V_{IH}$  = 2.4V and  $V_{IL}$  = 0.45V. Timing measurements made at  $V_{OL}$  = 0.8V and  $V_{OH}$  = 2.0V.

- Guaranteed by design, not 100% tested.

- 3. OE may be delayed up to t<sub>CE</sub> t<sub>OE</sub> after the falling edge of CE without impact on t<sub>CE</sub>.

## **AC VOLTAGE WAVEFORMS**

## **AC TESTING LOAD CIRCUIT**

November 12, 1990

## 27C210

#### PROGRAMMING INFORMATION

Complete programming system specifications for both the intelligent programming method and for the quick-pulse programming method are available upon request from Signetics.

Signetics encourages the purchase of programming equipment from a manufacturer who has a full line of programming products to offer. Signetics also encourages the manufacturers of 27C210 programming equipment to submit their equipment for verification of electrical parameters and programming procedures. Information on manufacturers offering equipment certified by Signetics is available upon request from Signetics Memory Marketing.

## PROGRAMMING THE 27C210

Caution: Exceeding 14.0V on V<sub>PP</sub> pin may permanently damage the 27C210.

Initially, all bits of the 27C210 are in the "1" state. Data is introduced by selectively programming "0"s into the desired bit locations. Although only "0"s will be programmed, both "1"s and "0"s can be present in the data word.

The data to be programmed is applied 16 bits in parallel to the data output pins. The levels required for the address and data inputs are standard TTL logic levels.

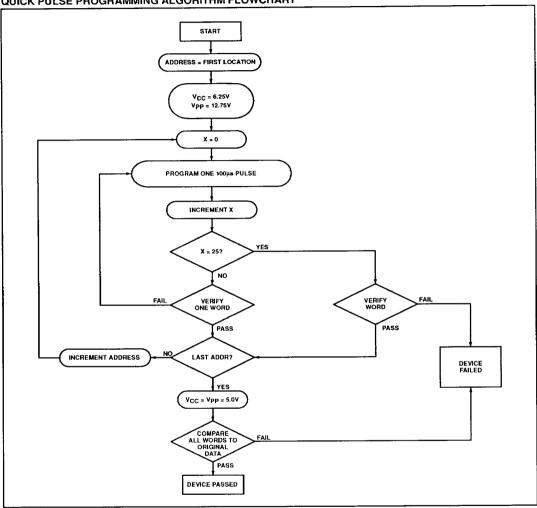

# QUICK-PULSE PROGRAMMING ALGORITHM

Signetics plastic EPROMs can be programmed using the quick-pulse programming algorithm to substantially reduce the throughput time in the production environment. This algorithm typically allows plastic devices to be programmed in under twelve seconds, a significant improvement over previous algorithms. Actual programming time is a function of the PROM programming equipment being used.

The quick-pulse programming algorithm uses initial pulses of 100µs followed by a byte verification to determine when the address byte has been successfully programmed. Up to 25 100µs pulses per byte are provided before a failure is recognized (refer to the following pages for algorithm specifications).

#### **ERASURE CHARACTERISTICS**

The erasure characteristics of the 27C210 are such that erasure begins to occur upon exposure to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000 - 4000 Å range. Data shows that constant exposure to room level fluorescent lighting could erase the typical 27C210 in approximately three years, while it would take approximately one week to cause erasure when exposed to direct sunlight. If the 27C210 is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the window to prevent unintentional erasure.

The recommended erasure procedure for the 27C210 is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (A). The integrated dose (i.e., UV intensity × exposure time) for erasure should be minimum of 15Wsec/cm<sup>2</sup>. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12,000μW/cm² power rating. The 27C210 should be placed within one inch of the lamp tubes during erasure. The maximum integrated dose a 27C210 can be exposed to without damage is 7258Wsec/cm2 (1 week @ 12000µW/cm2). Exposure of these CMOS EPROMs to high intensity UV light for longer periods may cause permanent damage.

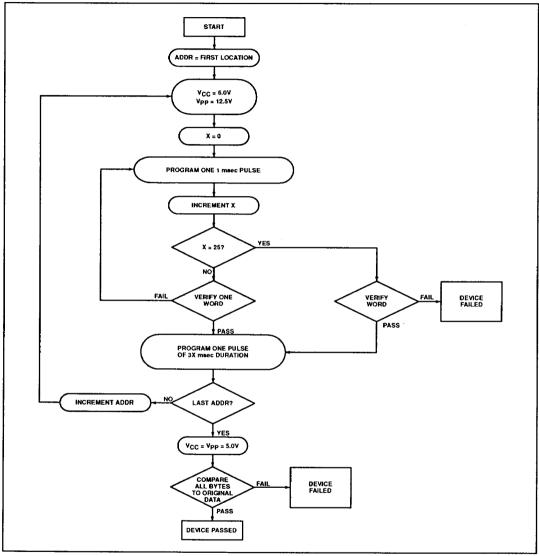

# INTELLIGENT PROGRAMMING ALGORITHM

The 27C210 intelligent programming algorithms rapidly program CMOS EPROMs using an efficient and reliable method particularly suited to the production programming environment. Actual programming times may vary due to differences in programming equipment.

The intelligent identifier also provides the reading out of a binary code from an EPROM that will identify its manufacturer and type. This is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the 25° ± 5°C ambient temperature range that is required when programming the 27C210. To activate this mode, the programming equipment must force 11.5V to 12.5V on address A9 of the 27C210. Two bytes may then be read from the device outputs by toggling address line A0 from VIL to VIH. The CE, OE and all other address lines must be at VIL during interrogation.

The identifier information for Signetics 27C210 is as follows:

When A0 ≈ V<sub>IL</sub>

FF15<sub>(HEX)</sub>

data is "Manufacturer"

When A0 = V<sub>IH</sub>

data is "Product"

FF17<sub>(HEX)</sub>

Programming reliability is also ensured as the incremental program margin of each byte is continually monitored to determine when it has been successfully programmed. The programming algorithm utilizes two different pulse types: initial and overprogram. The duration of the initial PGM pulse(s) is 1ms, which is then followed by a longer overprogram pulse of 3Xms. X is an iteration counter and is equal to the number of the initial 1ms pulses applied to a particular location before a correct verify occurs. Up to 25 1ms pulses per byte are provided for before the overprogram pulse is applied (refer to the following pages for algorithm specifications).

## CMOS NOISE CHARACTERISTICS

Special epitaxial processing techniques have enabled Signetics to build CMOS with features that add to system reliability. These include input/output protection to latch-up for stresses up to 100mA on Address and Data pins that range from -1V to (V<sub>CC</sub> + 1V). In addition, the V<sub>PP</sub> (Programming) pin is designed to resist latch-up to the 14V maximum device limit.

## SIGNETICS DISCOURAGES THE CONSTRUCTION AND USE OF "HOMEMADE" PROGRAMMING EQUIPMENT

In order to consistently achieve excellent programming yields, periodic calibration of the programming equipment is required. Consult the equipment manufacturer for the recommended calibration interval. Signetics warranty for programmability extends only to product that has been programmed on certified equipment that has been serviced to the manufacturers recommendation.

November 12, 1990

27C210

#### INTELLIGENT PROGRAMMING ALGORITHM

## DC PROGRAMMING CHARACTERISTICS

$T_{amb} = 25^{\circ}C \pm 5^{\circ}C$ ,  $V_{CC} = 6.0V \pm 0.25V$ ,  $V_{PP} = 12.5V \pm 0.5V$

| SYMBOL           | PARAMETER                                | TEST CONDITIONS                                      | LIM  | UNIT |    |

|------------------|------------------------------------------|------------------------------------------------------|------|------|----|

|                  |                                          |                                                      | MIN  | MAX  | ]  |

| 1,               | Input current (all inputs)               | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> |      | 1.0  | μА |

| V <sub>IL</sub>  | Input low level (all inputs)             |                                                      | -0.1 | 0.8  | ٧  |

| V <sub>IH</sub>  | Input high level                         |                                                      | 2.4  | 6.5  | V  |

| Vol              | Output low voltage during verify         | I <sub>OL</sub> = 2.1mA                              |      | 0.45 | V  |

| V <sub>OH</sub>  | Output high voltage during verify        | I <sub>OH</sub> = -2.5mA                             | 3.5  |      | V  |

| Icc2             | V <sub>CC</sub> supply current           | O0 - 15 = 0mA                                        |      | 50   | mA |

| I <sub>PP2</sub> | V <sub>PP</sub> supply current (program) | CE = V <sub>IL</sub>                                 |      | 50   | mA |

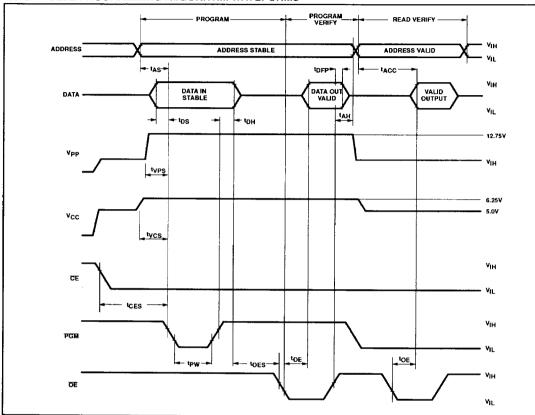

#### AC PROGRAMMING CHARACTERISTICS

| SYMBOL             | PARAMETER                      | TEST CONDITIONS |      | LIMITS |       | UNIT |

|--------------------|--------------------------------|-----------------|------|--------|-------|------|

|                    |                                |                 | MIN  | TYP    | MAX   |      |

| t <sub>AS</sub>    | Address setup time             |                 | 2    |        |       | μs   |

| toes               | OE setup time                  |                 | 2    |        |       | μs   |

| t <sub>DS</sub>    | Data setup time                |                 | 2    |        |       | μs   |

| t <sub>AH</sub>    | Address hold time              |                 | 0    |        |       | μs   |

| t <sub>DH</sub>    | Data hold time                 |                 | 2    |        |       | μs   |

| t <sub>DFP</sub> 3 | OE high to output float delay  |                 | 0    |        | 130   | ns   |

| t <sub>VPS</sub>   | V <sub>PP</sub> setup time     |                 | 2    |        |       | μs   |

| t <sub>VCS</sub>   | V <sub>CC</sub> setup time     |                 | 2    |        |       | μs   |

| t <sub>CES</sub>   | CE setup time                  |                 | 2    |        |       | μs   |

| t <sub>PW</sub>    | CE initial program pulse width | Note 1          | 0.95 | 1.0    | 1.05  | ms   |

| topw               | CE overprogram pulse width     | Note 2          | 2.85 |        | 78.75 | ms   |

| toE                | Data valid from OE             |                 |      |        | 150   | μs   |

## AC CONDITIONS OF TEST

| AO COMBINONO OF TEO:                   |               |

|----------------------------------------|---------------|

| Input Rise and Fall Times (10% to 90%) | 20ns          |

| Input Pulse Levels                     |               |

| Input Timing Reference Level           |               |

| Outout Timing Reference Level          | 0.8V and 2.0V |

- Initial program pulse width tolerance is 1ms ±5%.

- The length of the overprogram pulse may vary from 2.85msec to 78.75msec as a function of iteration counter value X.

The parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven see timing diagram.

- During programming, a 0.1μf capacitor is required from V<sub>PP</sub> to GND node, to suppress voltage transients that can damage the device.

٧IL

# 1 MEG CMOS EPROM (64K × 16)

## INTELLIGENT PROGRAMMING ALGORITHM WAVEFORMS PROGRAM VERIFY PROGRAM READ VERIFY ADDRESS STABLE ADDRESS VALID ADDRESS -tas**tDFP** ٧н DATA OUT VALID OUTPUT DATA IN STABLE DATA VIL LAH tos <sup>‡</sup>DH 12.5V Vpp VIH tvps 6.0V 5.0V ٧н VIL \*CES ٧н PGM VIL †OE <sup>1</sup>OE toes: ٧н

Œ

27C210

## INTELLIGENT PROGRAMMING ALGORITHM FLOWCHART

27C210

## QUICK PULSE PROGRAMMING ALGORITHM

## DC PROGRAMMING CHARACTERISTICS

$T_{amb} = 25^{\circ}C \pm 5^{\circ}C$ ,  $V_{CC} = 6.25V \pm 0.25V$ ,  $V_{PP} = 12.75V \pm 0.25V$

| SYMBOL           | PARAMETER                                | TEST CONDITIONS          | LIN  | IITS | UNIT     |

|------------------|------------------------------------------|--------------------------|------|------|----------|

|                  |                                          |                          | MIN  | MAX  | <u> </u> |

| i <sub>1</sub>   | Input current (all inputs)               | VIN = VIL or VIH         |      | 1.0  | μA       |

| V <sub>IL</sub>  | Input low level (all inputs)             |                          | -0.1 | 0.8  | V        |

| V <sub>IH</sub>  | Input high level                         |                          | 2.4  | 6.5  | V        |

| VOL              | Output low voltage during verify         | I <sub>OL</sub> = 2.1mA  |      | 0.45 | V        |

| V <sub>OH</sub>  | Output high voltage during verify        | I <sub>OH</sub> = -2.5mA | 3.5  |      | V        |

| lcc2             | V <sub>CC</sub> supply current           | O0 - 15 = 0mA            |      | 50   | mA       |

| I <sub>PP2</sub> | V <sub>PP</sub> supply current (program) | CE = V <sub>IL</sub>     |      | 50   | mA       |

| V <sub>PP</sub>  | Programming voltage                      |                          | 12.5 | 13.0 | V        |

## AC PROGRAMMING CHARACTERISTICS

| SYMBOL             | PARAMETER                      | TEST CONDITIONS | LIMITS |          |       | UNIT |

|--------------------|--------------------------------|-----------------|--------|----------|-------|------|

|                    |                                |                 | MIN    | TYP      | MAX   |      |

| tas                | Address setup time             |                 | 2      |          |       | μs   |

| toes               | OE setup time                  |                 | 2      |          |       | μs   |

| tos                | Data setup time                |                 | 2      | <u> </u> |       | μs   |

| t <sub>AH</sub>    | Address hold time              |                 | 0      | <u> </u> |       | μs   |

| <sup>‡</sup> OH    | Data hold time                 |                 | 2      |          |       | μs   |

| t <sub>OFP</sub> 3 | OE high to output float delay  |                 | 0      |          | 130   | ns   |

| typs               | V <sub>PP</sub> setup time     |                 | 2      |          |       | μs   |

| t <sub>vcs</sub>   | V <sub>CC</sub> setup time     |                 | 2      |          |       | μs   |

| tрw                | CE initial program pulse width | Note 1          | .095   | 0.100    | 0.105 | ms   |

| topw               | CE overprogram pulse width     | Note 2          | 2.85   | 1        | 78.8  | ms   |

| toe                | Data valid from OE             |                 |        |          | 150   | μs   |

## AC CONDITIONS OF TEST

| AC CONDITIONS OF TEST                  |               |

|----------------------------------------|---------------|

| Input Rise and Fall Times (10% to 90%) |               |

| Input Pulse Levels                     | 0.45V to 2.4V |

| Input Timing Reference Level           | 0.8V and 2.0V |

| Output Timing Reference Level          | 0.8V and 2.0V |

- 1. Initial program pulse width tolerance is 1ms ±5%.

- The length of the overprogram pulse may vary from 2.85msec to 78.75msec as a function of iteration counter value X.

The parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven see timing

- 4. During programming, a 0.1μf capacitor is required from V<sub>PP</sub> to GND node, to suppress voltage transients that can damage the device.

27C210

## QUICK PULSE PROGRAMMING ALGORITHM WAVEFORMS

## QUICK PULSE PROGRAMMING ALGORITHM FLOWCHART

138