| REV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                   |        |             |        |             |                   |              |    | R   | EVISIO | ONS                                                 |      |       |      |       |      |      |      |    |    |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|-------------|--------|-------------|-------------------|--------------|----|-----|--------|-----------------------------------------------------|------|-------|------|-------|------|------|------|----|----|----|

| SHEET   35   36   37   38   39   40   41   42   43   44   45                                                                                                                                                                                                                                                                                                                                                                                                                                            | LTR                                                               |        | DESCRIPTION |        |             |                   |              |    |     |        |                                                     |      | DATE  | YR-M | O-DA) |      | APPR | OVED |    |    |    |

| SHEET   35   36   37   38   39   40   41   42   43   44   45                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |        |             |        |             |                   |              |    |     |        |                                                     |      |       |      |       |      |      |      |    |    |    |

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | REV                                                               |        |             |        |             |                   |              |    |     |        |                                                     |      |       |      |       |      |      |      |    |    |    |

| SHEET   15   16   17   18   19   20   21   22   23   24   25   26   27   28   29   30   31   32   33   34                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   | 35     | 36          | 37     | 38          | 39                | 40           | 41 | 42  | 43     | 44                                                  | 45   |       |      |       |      |      |      |    |    |    |

| REV   SHEET   1   2   3   4   5   6   7   8   9   10   11   12   13   14                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                   |        |             |        |             |                   |              |    |     |        |                                                     |      |       |      |       |      |      |      |    |    |    |

| SHEET 1 2 3 4 5 6 7 8 9 10 11 12 13 14  PMIC N/A  PREPARED BY Thanh V. Nguyen  CHECKED BY Thanh V. Nguyen  CHECKED BY Thanh V. Nguyen  APPROVED BY Charles Saffle  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  SHEET 1 2 3 4 5 6 7 8 9 10 11 12 13 14  DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216 http://www.dscc.dla.mil  MICROCIRCUIT, DIGITAL, 32-BIT SPARC PROCESSOR, MONOLITHIC SILICON  SIZE CAGE CODE A 67268  5962-00540 |                                                                   | 15     | 16          | 17     |             |                   | 20           | 21 | 22  | 23     | 24                                                  | 25   | 26    | 27   | 28    | 29   | 30   | 31   | 32 | 33 | 34 |

| PMIC N/A  PREPARED BY Thanh V. Nguyen  CHECKED BY Thanh V. Nguyen  CHECKED BY Thanh V. Nguyen  APPROVED BY Charles Saffle  DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  PREPARED BY Thanh V. Nguyen  CHECKED BY Thanh V. Nguyen  APPROVED BY Charles Saffle  DRAWING APPROVAL DATE 01-08-02  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-00540                                                                                   |                                                                   |        |             |        |             |                   |              | 1  | 2   | 3      | 4                                                   | 5    | 6     | 7    | 8     | 9    | 10   | 11   | 12 | 13 | 14 |

| MICROCIRCUIT DRAWING  APPROVED BY Charles Saffle  DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  Thanh V. Nguyen  APPROVED BY Charles Saffle  DRAWING APPROVAL DATE 01-08-02  REVISION LEVEL  Thanh V. Nguyen  MICROCIRCUIT, DIGITAL, 32-BIT SPARC PROCESSOR, MONOLITHIC SILICON  SIZE CAGE CODE A 67268  5962-00540                                                                                                                              |                                                                   | ID A E | חפ          |        | PREI<br>Tha | PARED<br>anh V. N | lguyen       |    |     |        | DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216 |      |       |      |       |      | I    |      |    |    |    |

| THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  DRAWING APPROVAL DATE 01-08-02  PROCESSOR, MONOLITHIC SILICON  SIZE CAGE CODE  A 67268  5962-00540                                                                                                                                                                                                                                                                                            | MICROCIRCUIT<br>DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL |        |             |        | Tha<br>APPF | anh V. N          | lguyen<br>BY |    |     |        | MIC                                                 | ·ROC | IRCUI |      |       |      |      |      | `  |    |    |

| AND AGENCIES OF THE DEPARTMENT OF DEFENSE AMSC N/A  REVISION LEVEL  SIZE CAGE CODE  A 67268  5962-00540                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                   |        |             | BLE    |             |                   | APPRO        |    | ATE |        |                                                     |      |       |      |       |      |      |      | ,  |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AND AGENCIES OF THE                                               |        | REVI        | SION L | EVEL        |                   |              |    |     |        |                                                     |      |       |      | 59    | 962- | 005  | 40   |    |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AMS                                                               | SC N/A |             |        |             |                   |              |    |     |        | SHE                                                 | ET   | 1     | OF   | = !   | 45   |      |      |    |    |    |

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

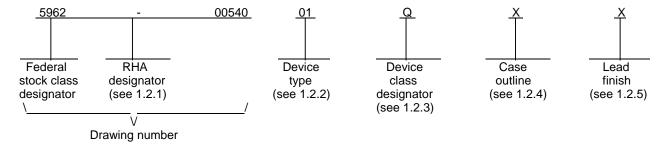

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function       | <u>Frequency</u> |

|-------------|----------------|------------------------|------------------|

| 01          | 695F           | 32-bit SPARC processor | 25 MHz           |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

M

Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A

Q or V

Certification and qualification to MIL-PRF-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style             |

|----------------|------------------------|------------------|---------------------------|

| X              | See figure 1           | 256              | Ceramic quad flat package |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

| STANDARD                       |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|

| MICROCIRCUIT DRAWING           |  |  |  |  |  |

| DEFENSE SUPPLY CENTER COLUMBUS |  |  |  |  |  |

| COLUMBUS, OHIO 43216-5000      |  |  |  |  |  |

| SIZE<br><b>A</b> |                | 5962-00540 |

|------------------|----------------|------------|

|                  | REVISION LEVEL | SHEET 2    |

## 1.3 Absolute maximum ratings. 1/

| Supply voltage range (V <sub>DD</sub> )                  | -0.5 V dc to +7.0 V dc <u>2</u> /                    |

|----------------------------------------------------------|------------------------------------------------------|

| Input voltage range (V <sub>IN</sub> )                   | $-0.5 \text{ V dc to V}_{DD} + 0.5 \text{ V dc}  3/$ |

| Output current (I <sub>OUT</sub> )                       | 50 mA 4/                                             |

| Maximum power dissipation (continuous) (P <sub>D</sub> ) | 1.5 W                                                |

| Storage temperature range (T <sub>STG</sub> )            | -65°C to +150°C                                      |

| Lead temperature (soldering, 10 seconds)                 | +265°C <u>5</u> /                                    |

| Thermal resistance, junction-to-case (⊖ <sub>JC</sub> )  | 3°C/W                                                |

| Junction temperature (T <sub>J</sub> )                   | +165°C                                               |

## 1.4 Recommended operating conditions.

| Operating supply voltage range (V <sub>DD</sub> )  | +4.5 V dc to +5.5 V dc |

|----------------------------------------------------|------------------------|

| Case operating temperature range (T <sub>C</sub> ) | -55°C to +125°C        |

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation.

## **SPECIFICATION**

## DEPARTMENT OF DEFENSE

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

## **STANDARDS**

#### DEPARTMENT OF DEFENSE

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

## **HANDBOOKS**

## DEPARTMENT OF DEFENSE

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>3 |

<sup>1/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

<sup>2/</sup> Device is functional from +4.5 V to +5.5 V with reference to ground.

$<sup>\</sup>frac{3}{2}$  (V<sub>DD</sub> + 0.5 V) should not exceed +7.0 V.

<sup>4/</sup> This is the maximum current of any single output.

Duration 10 seconds maximum at a distance not less than 1.5 mm from the device body, and the same lead shall not be resoldered until 3 minutes have elapsed.

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DOD adopted are those listed in the issue of the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation.

## INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

IEEE Standard 1149.1 - IEEE Standard Test Access Port and Boundary Scan Architecture.

(Applications for copies should be addressed to the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, Piscataway, NJ 08854-4150.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents may also be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 <u>Case outline</u>. The case outline shall be in accordance with 1.2.4 herein and figure 1 herein.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

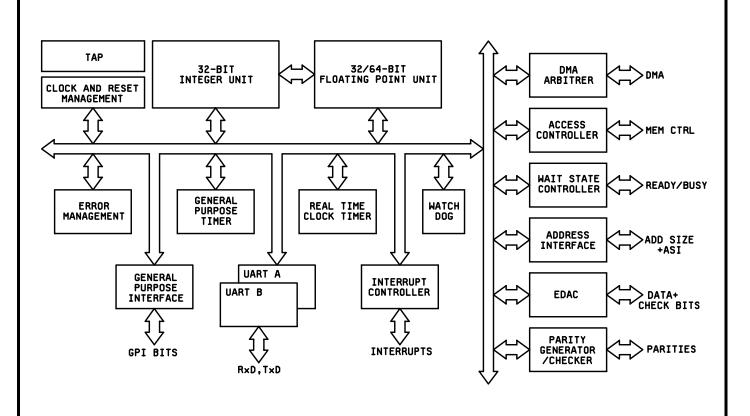

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

- 3.2.4 Boundary scan instruction codes. The boundary scan instruction codes shall be as specified on figure 4.

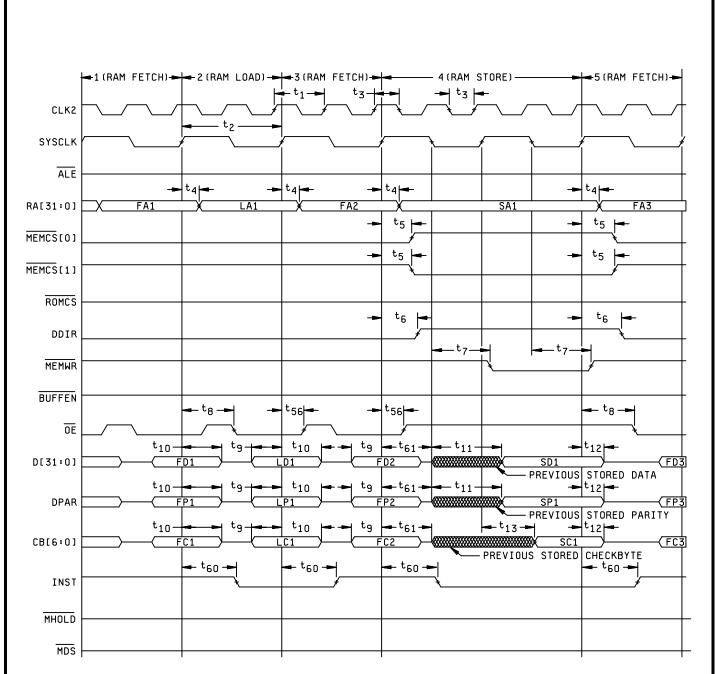

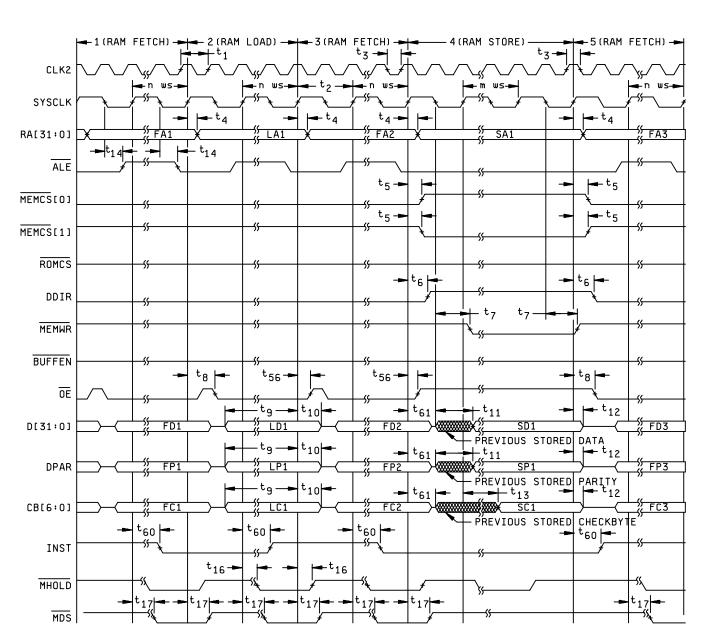

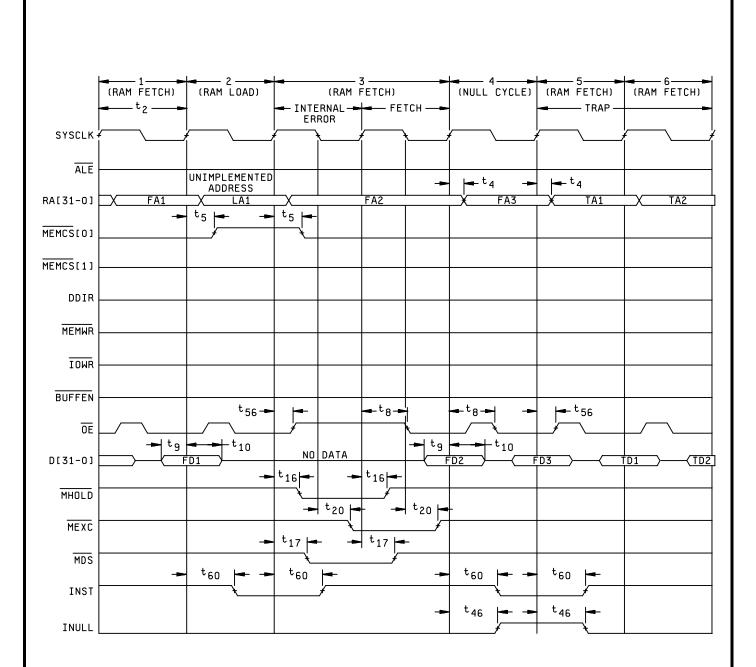

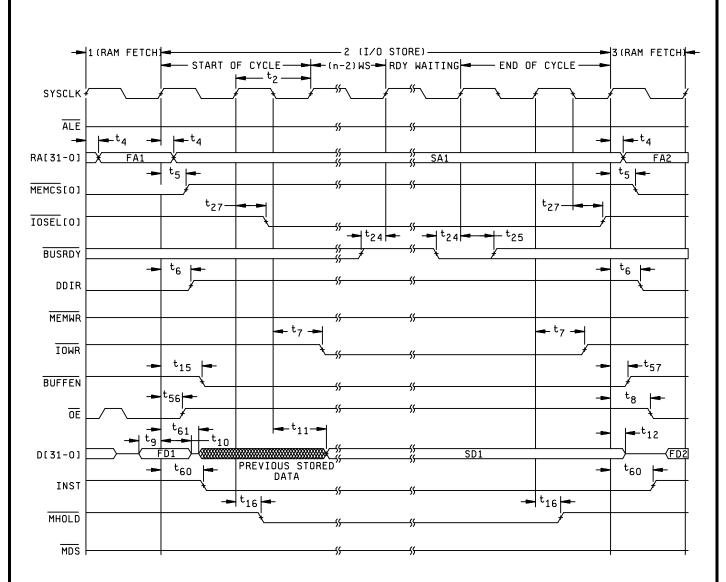

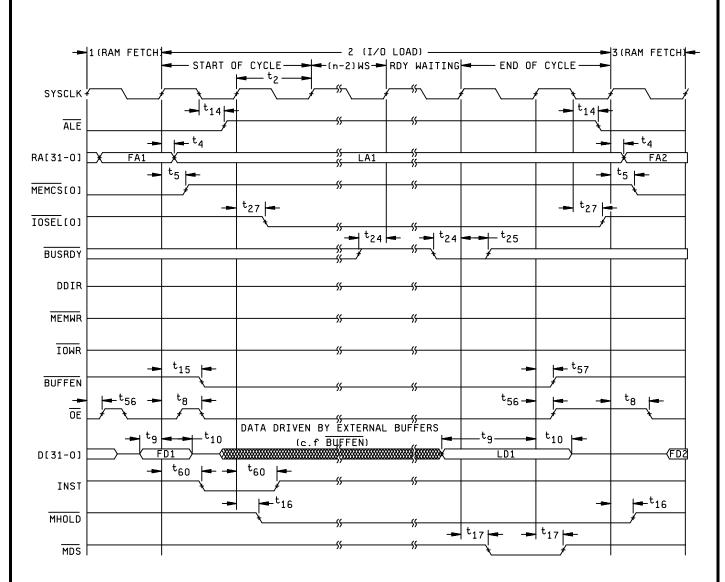

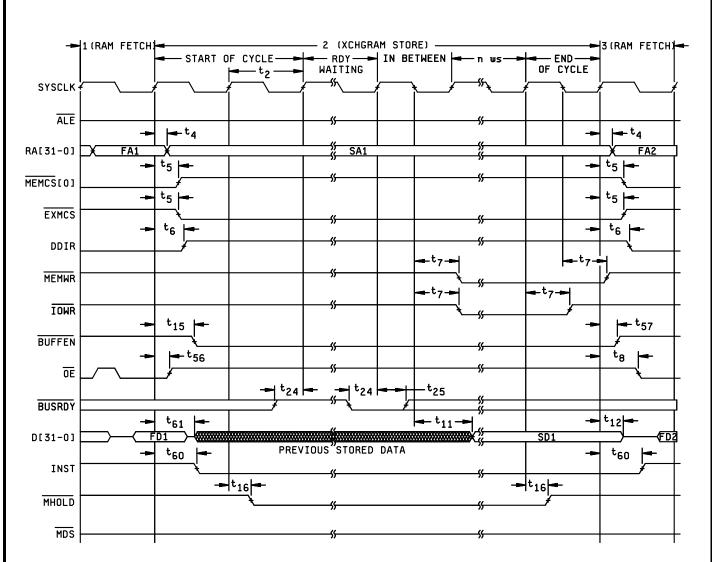

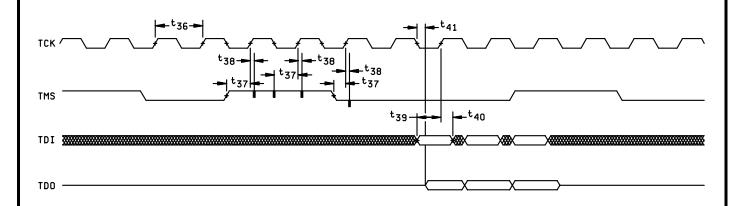

- 3.2.5 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 5.

- 3.2.6 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maitained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activities upon request.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 4    |

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M.</u> For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-PRF-38535, appendix A.

- 3.9 <u>Verification and review for device class M.</u> For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 132 (see MIL-PRF-38535, appendix A).

- 3.11 IEEE 1149.1 compliance. These devices shall be compliant to IEEE 1149.1.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. For device class M, sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

- 4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>5 |

|                                                 | -                   | TABLE I. Electrical performance ch                                                                                                                                                                                            | aracteristics.    |                |          |     |      |

|-------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|----------|-----|------|

| Test                                            | Symbol              | Conditions $-55^{\circ}C \le T_C \le +125^{\circ}C$                                                                                                                                                                           | Group A subgroups | Device<br>type | e Limits |     | Unit |

|                                                 |                     | $+4.5 \text{ V} \le \text{V}_{DD} \le +5.5 \text{ V}$ unless otherwise specified                                                                                                                                              |                   |                | Min      | Max |      |

| High level input voltage                        | V <sub>IH</sub>     | $V_{DD} = 5.5 \text{ V}  \underline{1}/  \underline{2}/$                                                                                                                                                                      | 1, 2, 3           | All            | 2.2      |     | V    |

|                                                 | V <sub>IHCR</sub>   | $V_{DD} = 5.5 \text{ V}  \underline{1} /  \underline{3} /$                                                                                                                                                                    | 1, 2, 3           | All            | 3.0      |     |      |

| Low level input voltage                         | V <sub>IL</sub>     | $V_{DD} = 5.5 \text{ V}  \underline{1}/  \underline{2}/  \underline{3}/$                                                                                                                                                      | 1, 2, 3           | All            |          | 0.8 | V    |

| High level output voltage                       | V <sub>ОН</sub>     | V <sub>DD</sub> =4.5 V, I <sub>OH</sub> = -6.0 mA <u>4/</u><br>Minimum and maximum values<br>recorded                                                                                                                         | 1, 2, 3           | All            | 2.4      |     | V    |

|                                                 | V <sub>OHB</sub>    | V <sub>DD</sub> =4.5 V, I <sub>OH</sub> = -16.0 mA <u>5/</u><br>Minimum and maximum values<br>recorded                                                                                                                        | 1, 2, 3           | All            | 2.4      |     |      |

| Low level output voltage                        | V <sub>OL</sub>     | V <sub>DD</sub> =4.5 V, I <sub>OL</sub> = 4.0 mA <u>4/</u><br>Minimum and maximum values recorded                                                                                                                             | 1, 2, 3           | All            |          | 0.4 | V    |

|                                                 | V <sub>OLB</sub>    | V <sub>DD</sub> =4.5 V, I <sub>OL</sub> = 12.0 mA <u>5/</u><br>Minimum and maximum values recorded                                                                                                                            | 1, 2, 3           | All            |          | 0.4 |      |

| High level input current                        | I <sub>IH</sub>     | $V_{DD} = 5.5 \text{ V}, V_{IN} = V_{DD}$<br><u>6</u> /                                                                                                                                                                       | 1, 2, 3           | All            |          | 10  | μΑ   |

| Low level input current                         | I <sub>IL</sub>     | $V_{DD} = 5.5 \text{ V}, V_{IN} = 0.0 \text{ V}$ $Z/$                                                                                                                                                                         | 1, 2, 3           | All            |          | 10  | μА   |

|                                                 | I <sub>ILT</sub>    | $V_{DD} = 5.5 \text{ V}, V_{IN} = 0.0 \text{ V}$ 8/                                                                                                                                                                           | 1, 2, 3           | All            |          | 350 |      |

| Three-state leakage current                     | I <sub>OZH</sub>    | $V_{DD} = 5.5 \text{ V}, V_{IN} = V_{DD}$ $\underline{9}/$                                                                                                                                                                    | 1, 2, 3           | All            |          | 10  | μА   |

| Three-state leakage current                     | I <sub>OZL</sub>    | $V_{DD} = 5.5 \text{ V}, V_{IN} = 0.0 \text{ V}$<br>9/                                                                                                                                                                        | 1, 2, 3           | All            |          | 10  | μА   |

| Supply current (idle) IV <sub>DD</sub> pins     | I <sub>DDIDLE</sub> | V <sub>DD</sub> = 5.5 V, f = 25 MHz                                                                                                                                                                                           | 1, 2, 3           | All            |          | 41  | mA   |

| Supply current (internal) IV <sub>DD</sub> pins | I <sub>DDIN</sub>   | V <sub>DD</sub> = 5.5 V, f = 25 MHz                                                                                                                                                                                           | 1, 2, 3           | All            |          | 230 | mA   |

| Input capacitance                               | C <sub>IN</sub>     | $V_{IN} = 2.5 \text{ V}$ $T_{C} = 25^{\circ}\text{C}$ $f_{IN} = 1.0 \text{ MHz}$ See 4.4.1c                                                                                                                                   | 4                 | All            |          | 10  | pF   |

| Functional test                                 |                     | $V_{IL} = 0.0 \text{ V}, V_{IH} = 3.0 \text{ V} \\ V_{OL} = 1.45 \text{ V}, V_{OH} = 1.55 \text{ V} \\ V_{DD} = 4.5 \text{ V}, 5.0 \text{ V}, \text{ and } 5.5 \text{ V} \\ f = 25 \text{ MHz} \\ \text{See } 4.4.1 \text{b}$ | 7, 8              | All            |          |     |      |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 6    |

|                                                                         | TABLE I.        | Electrical performance characteris                                               | stics - Continue  | d.             |         |      |      |

|-------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------|-------------------|----------------|---------|------|------|

| Test                                                                    | Symbol          | Conditions $-55^{\circ}C \le T_C \le +125^{\circ}C$                              | Group A subgroups | Device<br>type | Lin     | nits | Unit |

|                                                                         |                 | $+4.5 \text{ V} \le \text{V}_{DD} \le +5.5 \text{ V}$ unless otherwise specified |                   |                | Min     | Max  |      |

| CLK2 period 10/                                                         | t <sub>1</sub>  | V <sub>DD</sub> = 4.5 V                                                          | 9, 10, 11         | All            | 20      |      | ns   |

| SYSCLK period 10/                                                       | t <sub>2</sub>  | SYSCLK frequency = 25 MHz<br>See figure 5                                        | 9, 10, 11         | All            | 40      |      | ns   |

| CLK2 high and how pulse width 10/                                       | t <sub>3</sub>  | Geo ligare o                                                                     | 9, 10, 11         | All            | 9.75    |      | ns   |

| RA[31:0], RAPAR, RSIZE,<br>RLDSTO, and LOCK<br>output delay <u>11</u> / | t <sub>4</sub>  |                                                                                  | 9, 10, 11         | All            |         | 6.5  | ns   |

| MEMCS[9:0], ROMCS,                                                      | t <sub>5</sub>  |                                                                                  | 9, 10, 11         | All            |         | 12.5 | ns   |

| EXMCS output delay 10/ 11/                                              |                 |                                                                                  |                   |                |         |      |      |

| DDIR, DDIR output delay 10/ 11/                                         | t <sub>6</sub>  |                                                                                  | 9, 10, 11         | All            |         | 15   | ns   |

| MEMWR and IOMWR output delay 11/ 12/                                    | t <sub>7</sub>  |                                                                                  | 9, 10, 11         | All            |         | 23.5 | ns   |

| OE (HL) output delay 11/                                                | t <sub>8</sub>  |                                                                                  | 9, 10, 11         | All            |         | 20.5 | ns   |

| Data setup time during load 11/                                         | t <sub>9</sub>  |                                                                                  | 9, 10, 11         | All            | 11.5    |      | ns   |

| Data hold time during load 10/ 11/                                      | t <sub>10</sub> |                                                                                  | 9, 10, 11         | All            | 5       |      | ns   |

| Data output delay 12/                                                   | t <sub>11</sub> |                                                                                  | 9, 10, 11         | All            |         | 28   | ns   |

| Data output valid 10/ 11/                                               | t <sub>12</sub> |                                                                                  | 9, 10, 11         | All            | 8       |      | ns   |

| CB output delay 10/ 11/                                                 | t <sub>13</sub> |                                                                                  | 9, 10, 11         | All            |         | 19   | ns   |

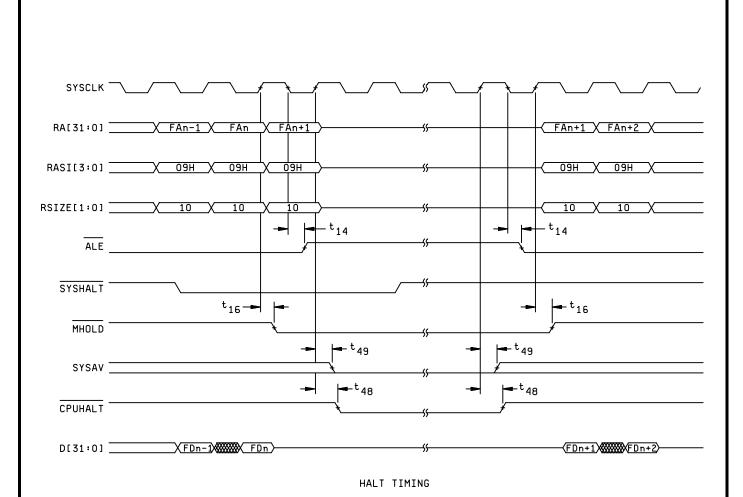

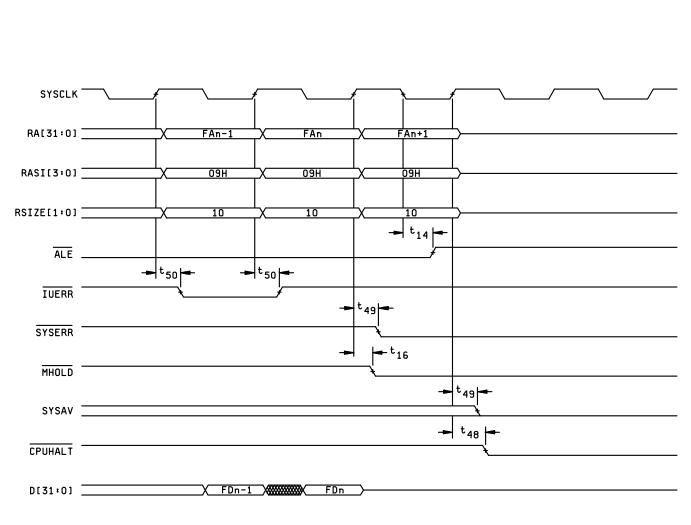

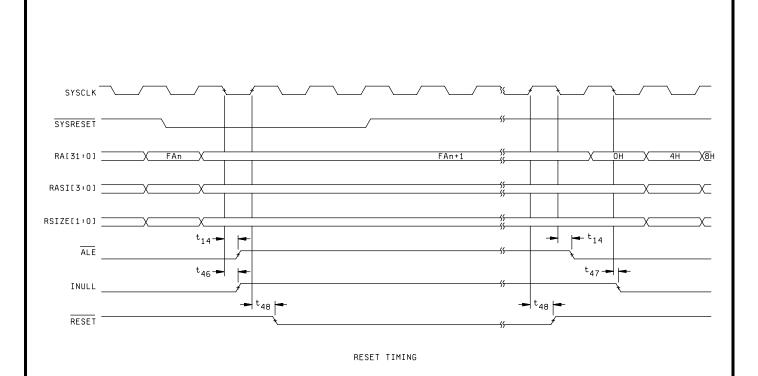

| ALE output delay 10/ 12/                                                | t <sub>14</sub> |                                                                                  | 9, 10, 11         | All            | <u></u> | 13   | ns   |

| BUFFEN (HL) output<br>delay <u>10</u> / <u>11</u> /                     | t <sub>15</sub> |                                                                                  | 9, 10, 11         | All            |         | 21   | ns   |

| MHOLD output delay  10/ 11/                                             | t <sub>16</sub> |                                                                                  | 9, 10, 11         | All            |         | 12   | ns   |

| MDS , DRDY output delay                                                 | t <sub>17</sub> |                                                                                  | 9, 10, 11         | All            |         | 15   | ns   |

| MEXC output delay 10/ 12/                                               | t <sub>20</sub> |                                                                                  | 9, 10, 11         | All            |         | 15   | ns   |

| RASI[3:0], RSIZE[1:0],<br>RASPAR setup time<br>10/ 11/                  | t <sub>21</sub> |                                                                                  | 9, 10, 11         | All            | 10      |      | ns   |

| RASI[3:0], RSIZE[1:0],<br>RASPAR hold time<br>10/ 11/                   | t <sub>22</sub> |                                                                                  | 9, 10, 11         | All            | 3       |      | ns   |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 7    |

|                                                             | TABLE I.                                         | Electrical performance characteris                                               | stics - Continue         | d.  |     |      |          |

|-------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|--------------------------|-----|-----|------|----------|

| Test                                                        | Test Symbol Condition $-55^{\circ}C \le T_C \le$ |                                                                                  | Group A<br>5°C subgroups |     | Lin | nits | Unit     |

|                                                             |                                                  | $+4.5 \text{ V} \le \text{V}_{DD} \le +5.5 \text{ V}$ unless otherwise specified |                          |     | Min | Max  |          |

| BOOT PROM address output delay 10/ 11/                      | t <sub>23</sub>                                  | V <sub>DD</sub> = 4.5 V<br>SYSCLK frequency = 25 MHz                             | 9, 10, 11                | All |     | 13   | ns       |

| BUSRDY setup time                                           | t <sub>24</sub>                                  | See figure 5                                                                     | 9, 10, 11                | All | 12  |      | ns       |

| BUSRDY hold time                                            | t <sub>25</sub>                                  |                                                                                  | 9, 10, 11                | All | 0   |      | ns       |

| <u>10</u> / <u>11</u> /                                     | <u> </u>                                         |                                                                                  |                          |     |     |      | <u> </u> |

| IOSEL output delay 10/ 11/                                  | t <sub>27</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 15   | ns       |

| DMAAS setup time 10/ 11/                                    | t <sub>28</sub>                                  |                                                                                  | 9, 10, 11                | All | 12  | 20   | ns       |

| DMAAS hold time 10/ 12/                                     | t <sub>29</sub>                                  |                                                                                  | 9, 10, 11                | All | 0   | 20   | ns       |

| DMAREQ setup time                                           | t <sub>30</sub>                                  |                                                                                  | 9, 10, 11                | All | 12  |      | ns       |

| DMAGNT output delay                                         | t <sub>31</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 15   | ns       |

| <u>10</u> / <u>11</u> /                                     | <u> </u>                                         |                                                                                  |                          |     |     |      | <u> </u> |

| RA[31:0], RAPAR, CPAR<br>setup time <u>10</u> / <u>11</u> / | t <sub>32</sub>                                  |                                                                                  | 9, 10, 11                | All | 10  |      | ns       |

| RA[31:0], RAPAR, CPAR<br>hold time <u>10</u> / <u>11</u> /  | t <sub>33</sub>                                  |                                                                                  | 9, 10, 11                | All | 3   |      | ns       |

| TCK period 10/                                              | t <sub>36</sub>                                  |                                                                                  | 9, 10, 11                | All | 100 |      | ns       |

| TMS setup time <u>10</u> / <u>13</u> /                      | t <sub>37</sub>                                  |                                                                                  | 9, 10, 11                | All | 10  |      | ns       |

| TMS hold time <u>10</u> / <u>13</u> /                       | t <sub>38</sub>                                  |                                                                                  | 9, 10, 11                | All | 4   |      | ns       |

| TDI setup time <u>10</u> / <u>13</u> /                      | t <sub>39</sub>                                  |                                                                                  | 9, 10, 11                | All | 10  |      | ns       |

| TDI hold time <u>10</u> / <u>13</u> /                       | t <sub>40</sub>                                  |                                                                                  | 9, 10, 11                | All | 10  |      | ns       |

| TDO output delay 10/ 14/                                    | t <sub>41</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 20   | ns       |

| INULL output delay 10/ 11/                                  | t <sub>46</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 22   | ns       |

| RESET , CPUHALT output delay 10/ 11/                        | t <sub>48</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 22   | ns       |

| SYSERR , SYSAV output delay 10/ 11/                         | t <sub>49</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 20   | ns       |

| IUERR output delay 10/ 11/                                  | t <sub>50</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 20   | ns       |

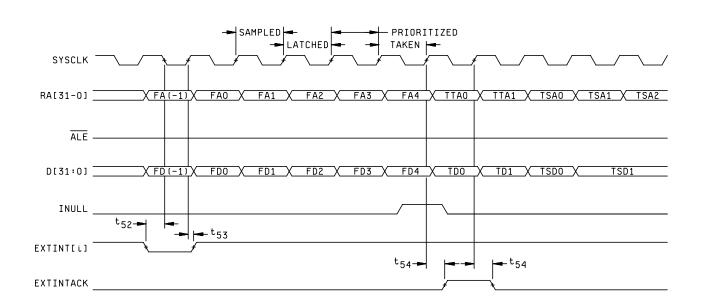

| EXTINT[4:0] setup time 10/ 12/                              | t <sub>52</sub>                                  |                                                                                  | 9, 10, 11                | All | 12  |      | ns       |

| EXTINT[4:0] hold time  10/ 11/                              | t <sub>53</sub>                                  |                                                                                  | 9, 10, 11                | All | 0   |      | ns       |

| EXTINTACK output delay  10/ 11/                             | t <sub>54</sub>                                  |                                                                                  | 9, 10, 11                | All |     | 15   | ns       |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>8 |

| TABLE I. <u>Electrical performance characteristics</u> - Continued. |                 |                                                                                      |           |                |        |     |      |  |

|---------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------|-----------|----------------|--------|-----|------|--|

| Test                                                                | Symbol          | Symbol Conditions $-55^{\circ}\text{C} \le T_{\text{C}} \le +125^{\circ}\text{C}$ si |           | Device<br>type | Limits |     | Unit |  |

|                                                                     |                 | +4.5 V ≤ V <sub>DD</sub> ≤ +5.5 V unless otherwise specified                         |           |                | Min    | Max |      |  |

| OE (LH) output delay (no<br>DMA mode) 10/ 11/                       | t <sub>56</sub> | V <sub>DD</sub> = 4.5 V<br>SYSCLK frequency = 25 MHz<br>See figure 5                 | 9, 10, 11 | All            |        | 8.5 | ns   |  |

| BUFFEN (LH) output delay 10/ 11/                                    | t <sub>57</sub> | Goo ligate o                                                                         | 9, 10, 11 | All            |        | 9   | ns   |  |

| INST output delay 10/ 11/                                           | t <sub>60</sub> |                                                                                      | 9, 10, 11 | All            |        | 22  | ns   |  |

| Data output delay to low-Z 10/ 11/                                  | t <sub>61</sub> |                                                                                      | 9, 10, 11 | All            | 20     |     | ns   |  |

- 1/ Not recorded Tested go/no-go during functional test.

- 2/ Applies to RA[31:0], RAPAR, RASI[3:0], RSIZE[1:0], RASPAR, CPAR, D[31:0], CB[6:0], DPAR, RLDSTO, DXFER, LOCK, RD, WE, WRT, PROM8, ROMWRT, BUSRDY, BUSERR, DMAREQ, DMAAS, SYSHALT, NOPAR, IWDE, WDCLK, CLK2, TMODE[1:0], DEBUG, TCK, TRST, TMS, TDI.

- 3/ Applies to RxA, RxB, GPI[7:0], EXTINT[4:0], EWDINT, SYSRESET.

- Applies to RAPAR, RASI[3:0], RSIZE[1:0], RASPAR, CPAR, D[31:0], CB[6:0], DPAR, RLDSTO, ALE, DXFER, LOCK, RD, WE, WRT, MHOLD, MDS, MEXC, BA[1:0], ROMCS, MEMCS[9:0], BUFFEN, DDIR, DDIR, DDIR, DOIR, DDIR, DOIR, DDIR, DOIR, DDIR, DOIR, DDIR, DOIR, TXA, TXB, GPIINT, EXTINTACK, SYSCLK, RESET, TDO.

- 5/ Applies to RA[31:0], MEMWR, OE.

- 6/ Applies to PROM8, ROMWRT, BUSRDY, BUSERR, DMAREQ, DMAAS, SYSHALT, NOPAR, RXA, RXB, EXTINT[4:0], IWDE, EWDINT, WDCLK, CLK2, SYSRESET, TMODE[1:0], DEBUG, TCK, TRST, TMS, TDI.

- 7/ Applies to PROM8, ROMWRT, BUSRDY, BUSERR, DMAREQ, DMAAS, SYSHALT, NOPAR, RxA, RxB, EXTINT[4:0], IWDE, EWDINT, WDCLK, CLK2, SYSRESET, TMODE[1:0], DEBUG TCK, TRST.

- 8/ Applies to TMS, TDI.

- 9/ Applies to RA[31:0], RAPAR, RASI[3:0], RSIZE[1:0], RASPAR, CPAR, D[31:0], CB[6:0], DPAR, RLDSTO, DXFER, LOCK, RD, WE, WRT, GPI[7:0].

- 10/ Tested during AC tests but not recorded.

- 11/ With reference edge of SYSCLK+.

- 12/ With reference edge of SYSCLK-.

- 13/ With reference edge of TCK+.

- 14/ With reference edge of TCK-.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 9    |

# Case outline X A1 -D1 N2 E E1 256 1 INDEX CORNER A2 → N1-FIGURE 1. Case outline. SIZE **STANDARD** 5962-00540 Α **MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS REVISION LEVEL** SHEET COLUMBUS, OHIO 43216-5000 10

# Case outline X - Continued

| Symbol | Millim    | neters | Inches   |       |  |

|--------|-----------|--------|----------|-------|--|

|        | Min       | Max    | Min      | Max   |  |

| А      | 2.41      | 3.18   | .095     | .125  |  |

| A1     | 2.06      | 2.56   | .081     | .101  |  |

| A2     | 0.05 0.36 |        | .002     | .014  |  |

| b      | 0.15      | 0.25   | .006     | .010  |  |

| С      | 0.10      | 0.20   | .004     | .008  |  |

| D/E    | 53.23     | 55.74  | 2.095    | 2.195 |  |

| D1/E1  | 36.83     | 37.34  | 1.450    | 1.470 |  |

| е      | 0.508     | BSC    | .020 BSC |       |  |

| L      | 8.20      | 9.20   | .323     | .362  |  |

| N1/N2  | 6         | 4      | 6        | 4     |  |

FIGURE 1. <u>Case outline</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>11 |

|               |                  |               | Cas              | se X          |                  |               |                  |

|---------------|------------------|---------------|------------------|---------------|------------------|---------------|------------------|

| Pin<br>number | Pin name         |

| 1             | GPIINT           | 33            | D[20]            | 65            | D[0]             | 97            | RA[18]           |

| 2             | GPI[7]           | 34            | D[19]            | 66            | RSIZE[1]         | 98            | V <sub>cco</sub> |

| 3             | Vcco             | 35            | D[18]            | 67            | RSIZE[0]         | 99            | V <sub>SSO</sub> |

| 4             | V <sub>SSO</sub> | 36            | Vcco             | 68            | RASI[3]          | 100           | RA[17]           |

| 5             | GPI[6]           | 37            | V <sub>SSO</sub> | 69            | V <sub>cco</sub> | 101           | RA[16]           |

| 6             | GPI[5]           | 38            | D[17]            | 70            | V <sub>SSO</sub> | 102           | RA[15]           |

| 7             | GPI[4]           | 39            | D[16]            | 71            | RASI[2]          | 103           | Vcco             |

| 8             | GPI[3]           | 40            | V <sub>CCI</sub> | 72            | RASI[1]          | 104           | $V_{SSO}$        |

| 9             | V <sub>CCO</sub> | 41            | $V_{SSI}$        | 73            | RASI[0]          | 105           | RA[14]           |

| 10            | $V_{SSO}$        | 42            | D[15]            | 74            | RA[31]           | 106           | V <sub>CCI</sub> |

| 11            | GPI[2]           | 43            | D[14]            | 75            | RA[30]           | 107           | V <sub>SSI</sub> |

| 12            | GPI[1]           | 44            | V <sub>cco</sub> | 76            | V <sub>CCO</sub> | 108           | RA[13]           |

| 13            | GPI[0]           | 45            | $V_{SSO}$        | 77            | $V_{SSO}$        | 109           | RA[12]           |

| 14            | D[31]            | 46            | D[13]            | 78            | RA[29]           | 110           | Vcco             |

| 15            | D[30]            | 47            | D[12]            | 79            | RA[28]           | 111           | $V_{SSO}$        |

| 16            | V <sub>CCO</sub> | 48            | D[11]            | 80            | RA[27]           | 112           | RA[11]           |

| 17            | $V_{SSO}$        | 49            | D[10]            | 81            | $V_{CCO}$        | 113           | RA[10]           |

| 18            | D[29]            | 50            | V <sub>cco</sub> | 82            | $V_{SSO}$        | 114           | RA[9]            |

| 19            | D[28]            | 51            | $V_{SSO}$        | 83            | RA[26]           | 115           | V <sub>cco</sub> |

| 20            | $V_{CCI}$        | 52            | D[9]             | 84            | RA[25]           | 116           | $V_{SSO}$        |

| 21            | $V_{SSI}$        | 53            | D[8]             | 85            | RA[24]           | 117           | RA[8]            |

| 22            | D[27]            | 54            | D[7]             | 86            | V <sub>CCI</sub> | 118           | RA[7]            |

| 23            | D[26]            | 55            | D[6]             | 87            | $V_{SSI}$        | 119           | RA[6]            |

| 24            | $V_{CCO}$        | 56            | $V_{CCO}$        | 88            | $V_{CCO}$        | 120           | $V_{CCO}$        |

| 25            | $V_{SSO}$        | 57            | $V_{SSO}$        | 89            | $V_{SSO}$        | 121           | $V_{SSO}$        |

| 26            | D[25]            | 58            | D[5]             | 90            | RA[23]           | 122           | RA[5]            |

| 27            | D[24]            | 59            | D[4]             | 91            | RA[22]           | 123           | RA[4]            |

| 28            | D[23]            | 60            | D[3]             | 92            | RA[21]           | 124           | RA[3]            |

| 29            | D[22]            | 61            | D[2]             | 93            | V <sub>cco</sub> | 125           | Vcco             |

| 30            | V <sub>CCO</sub> | 62            | V <sub>cco</sub> | 94            | V <sub>SSO</sub> | 126           | V <sub>SSO</sub> |

| 31            | V <sub>SSO</sub> | 63            | V <sub>SSO</sub> | 95            | RA[20]           | 127           | RA[2]            |

| 32            | D[21]            | 64            | D[1]             | 96            | RA[19]           | 128           | RA[1]            |

FIGURE 2. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>12 |

|               | Case X           |               |                  |               |                  |               |                  |  |

|---------------|------------------|---------------|------------------|---------------|------------------|---------------|------------------|--|

| Pin<br>number | Pin name         |  |

| 129           | RA[0]            | 161           | SYSERR           | 193           | DXFER            | 225           | MEMCS[3]         |  |

| 130           | Vcco             | 162           | SYSAV            | 194           | MEXC             | 226           | Vcco             |  |

| 131           | $V_{SSO}$        | 163           | EXTINT[4]        | 195           | Vcco             | 227           | V <sub>SSO</sub> |  |

| 132           | RAPAR            | 164           | EXTINT[3]        | 196           | $V_{SSO}$        | 228           | MEMCS[2]         |  |

| 133           | RASPAR           | 165           | EXTINT[2]        | 197           | RESET            | 229           | MEMCS[1]         |  |

| 134           | DPAR             | 166           | EXTINT[1]        | 198           | SYSRESET         | 230           | MEMCS[0]         |  |

| 135           | V <sub>CCO</sub> | 167           | EXTINT[0]        | 199           | BA[1]            | 231           | V <sub>CCI</sub> |  |

| 136           | V <sub>SSO</sub> | 168           | V <sub>CCI</sub> | 200           | BA[0]            | 232           | V <sub>SSI</sub> |  |

| 137           | SYSCLK           | 169           | $V_{SSI}$        | 201           | CB[6]            | 233           | ŌĒ               |  |

| 138           | TDO              | 170           | EXTINTACK        | 202           | CB[5]            | 234           | V <sub>CCO</sub> |  |

| 139           | TRST             | 171           | IUERR            | 203           | Vcco             | 235           | $V_{SSO}$        |  |

| 140           | TMS              | 172           | Vcco             | 204           | $V_{SSO}$        | 236           | MEMWR            |  |

| 141           | TDI              | 173           | V <sub>SSO</sub> | 205           | CB[4]            | 237           | BUFFEN           |  |

| 142           | TCK              | 174           | CPAR             | 206           | CB[3]            | 238           | DDIR             |  |

| 143           | CLK2             | 175           | TXA              | 207           | CB[2]            | 239           | V <sub>cco</sub> |  |

| 144           | DRDY             | 176           | RXA              | 208           | CB[1]            | 240           | $V_{SSO}$        |  |

| 145           | DMAAS            | 177           | RXB              | 209           | V <sub>cco</sub> | 241           | DDIR             |  |

| 146           | Vcco             | 178           | TXB              | 210           | V <sub>sso</sub> | 242           | MHOLD            |  |

| 147           | $V_{SSO}$        | 179           | ĪOWR             | 211           | CB[0]            | 243           | MDS              |  |

| 148           | DMAGNT           | 180           | IOSEL[3]         | 212           | ALE              | 244           | WDCLK            |  |

| 149           | EXMCS            | 181           | V <sub>cco</sub> | 213           | V <sub>CCI</sub> | 245           | IWDE             |  |

| 150           | V <sub>CCI</sub> | 182           | $V_{SSO}$        | 214           | $V_{SSI}$        | 246           | EWDINT           |  |

| 151           | $V_{SSI}$        | 183           | IOSEL[2]         | 215           | PROM8            | 247           | TMODE[1]         |  |

| 152           | DMAREQ           | 184           | IOSEL[1]         | 216           | ROMCS            | 248           | TMODE[0]         |  |

| 153           | BUSERR           | 185           | IOSEL[0]         | 217           | MEMCS[9]         | 249           | DEBUG            |  |

| 154           | BUSRDY           | 186           | WRT              | 218           | $V_{CCO}$        | 250           | INULL            |  |

| 155           | ROMWRT           | 187           | WE               | 219           | $V_{SSO}$        | 251           | DIA              |  |

| 156           | NOPAR            | 188           | Vcco             | 220           | MEMCS[8]         | 252           | V <sub>cco</sub> |  |

| 157           | SYSHALT          | 189           | $V_{SSO}$        | 221           | MEMCS[7]         | 253           | V <sub>SSO</sub> |  |

| 158           | CPUHALT          | 190           | RD               | 222           | MEMCS[6]         | 254           | FLUSH            |  |

| 159           | V <sub>CCO</sub> | 191           | RLDSTO           | 223           | MEMCS[5]         | 255           | INST             |  |

| 160           | V <sub>SSO</sub> | 192           | LOCK             | 224           | MEMCS[4]         | 256           | RTC              |  |

FIGURE 2. <u>Terminal connections</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>13 |

FIGURE 3. Block diagram.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>14 |

| Device type 01         |                  |  |

|------------------------|------------------|--|

| Instruction name       | Instruction code |  |

| BYPASS                 | 11.1111          |  |

| EXTEST                 | 00.0000          |  |

| SAMPLE/PRELOAD         | 00.0001          |  |

| INTEST                 | 00.0011          |  |

| ID code                | 10.0000          |  |

| Reserved for emulation | 01.1000          |  |

| Reserved for emulation | 01.1001          |  |

| Reserved for emulation | 01.1010          |  |

| Reserved for emulation | 01.1100          |  |

| Reserved for emulation | 01.1101          |  |

| Reserved for emulation | 01.1110          |  |

FIGURE 4. Boundary scan instruction codes.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>15 |

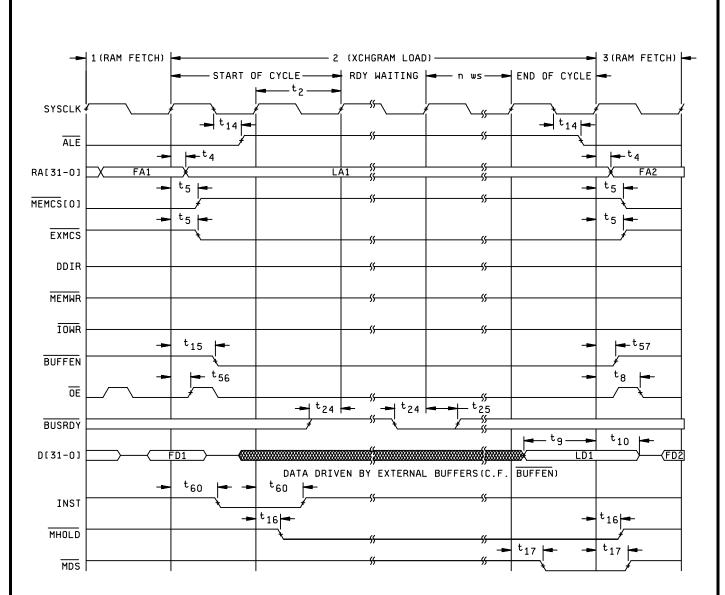

RAM FETCH, RAM LOAD, RAM FETCH AND RAM STORE SEQUENCE -O WAITSTATE

FIGURE 5. Timing waveforms.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>16 |

RAM FETCH, RAM LOAD AND RAM STORE SEQUENCE - N WAITSTATES FOR READ, M WAITSTATES FOR WRITE

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>17 |

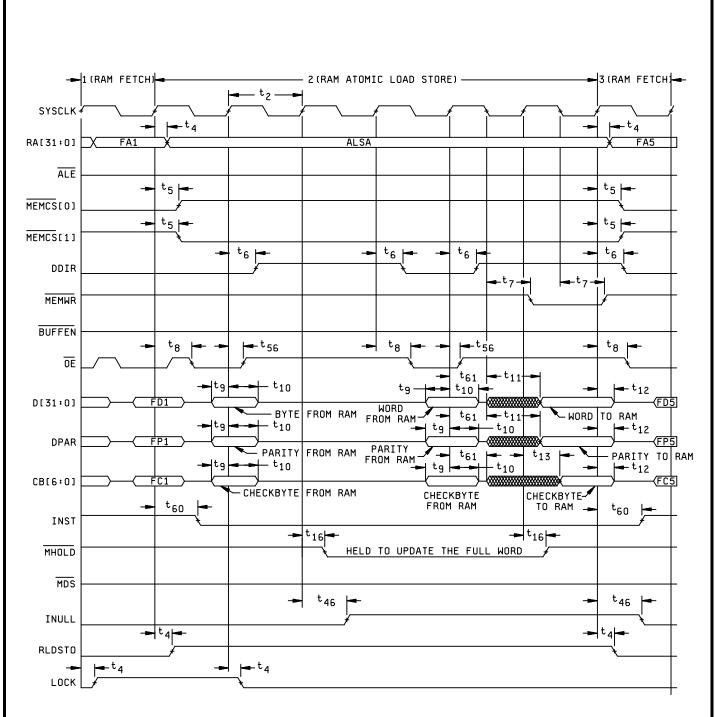

RAM ATOMIC-LOAD-STORE BYTE SEQUENCE-O WAITSTATE

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>18 |

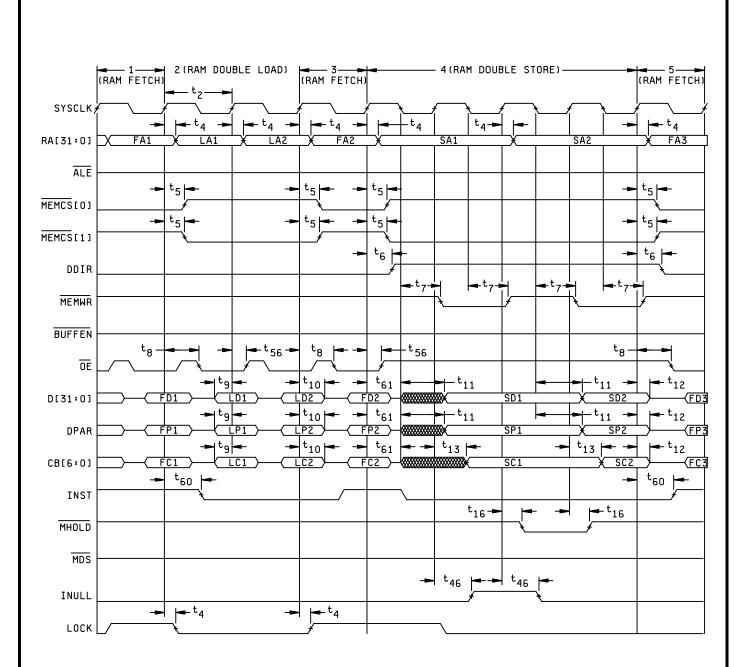

RAM LOAD-DOUBLE AND RAM STORE-DOUBLE SEQUENCE - O WAITSTATE

FIGURE 5. <u>Timing waveforms</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>19 |

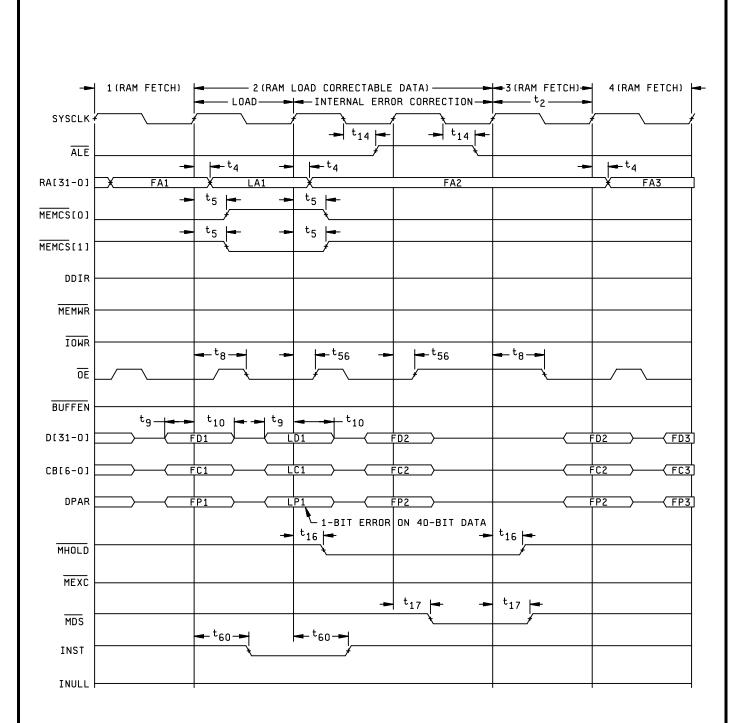

RAM LOAD WITH CORRECTABLE ERROR - O WAITSTATE

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 20   |

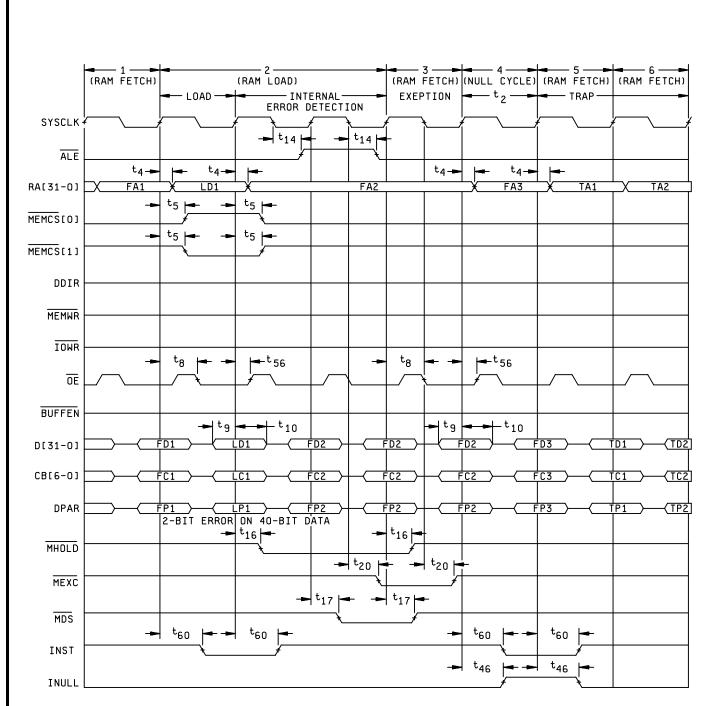

RAM LOAD WITH UNCORRECTABLE ERROR - O WAITSTATE

FIGURE 5. <u>Timing waveforms</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 21   |

RAM LOAD WITH UNIMPLEMENTED AREA ACCESS - O WAITSTATE

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 22   |

I/O STORE SEQUENCE WITH BUSRDY AND n WAITSTATES (TIMING FOR O OR 1 WAITSTATE = TIMING FOR 2 WAITSTATES)

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 23   |

I/O LOAD SEQUENCE WITH BUSRDY AND n WAITSTATES (TIMING FOR 0 OR 1 WS = TIMING FOR 2 WS)

FIGURE 5. Timing waveforms - Continued.

| STANDARD MICROCIRCUIT DRAWING                               | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 24   |

EXCHANGE RAM STORE WITH BUSDRY AND n WAITSTATES

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 25   |

EXCHANGE RAM LOAD WITH BUSDRY AND n WAITSTATES

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 26   |

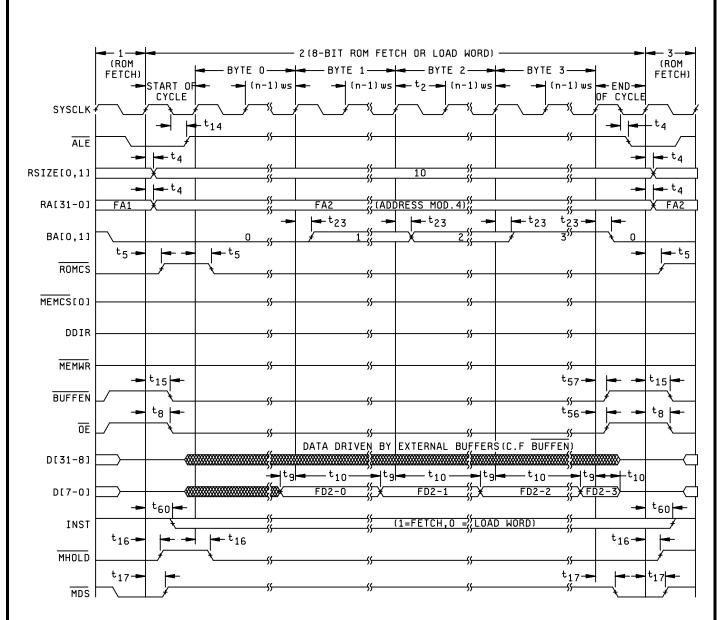

8-BIT BOOT PROM FETCH(OR LOAD WORD) - n WAITSTATES

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 27   |

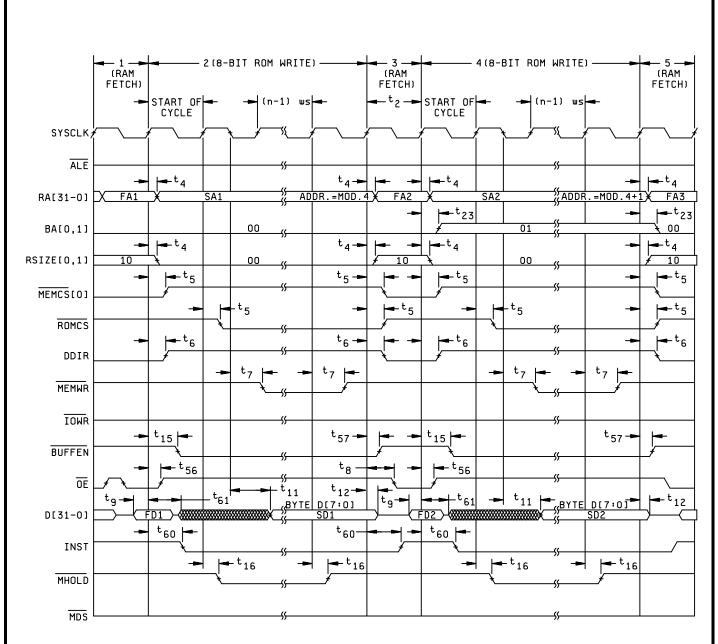

8-BIT BOOT PROM 2x STORE BYTE - n WAITSTATES

FIGURE 5. Timing waveforms - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>28 |

EDGE TRIGGERED INTERRUPT TIMING

FIGURE 5. <u>Timing waveforms</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 30   |

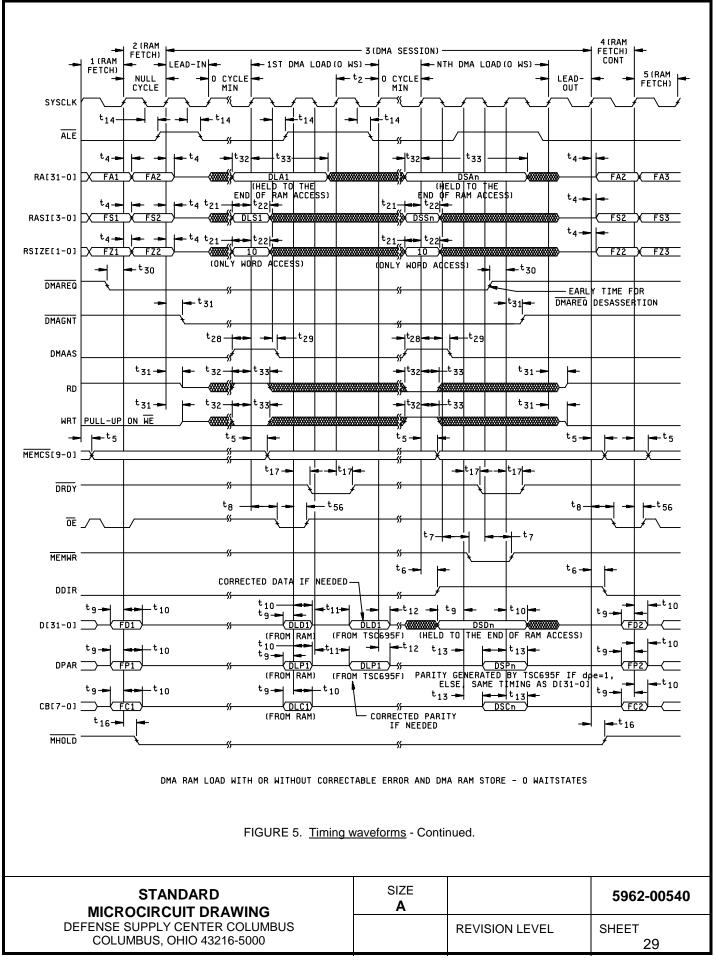

FIGURE 5. <u>Timing waveforms</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>31 |

EXTERNAL ERROR WITH HALT TIMING

FIGURE 5. <u>Timing waveforms</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 32   |

FIGURE 5. <u>Timing waveforms</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>33 |

## 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

- 4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections and as specified herein. Quality conformance inspection for device class M shall be in accordance with MIL-PRF-38535, appendix A and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

## 4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. For device class M, subgroups 7 and 8 tests shall verify the instruction set. The instruction set forms a part of the vendor's test tape and shall be maintained and available for review from the approved sources of supply. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device.

- c. Subgroup 4 (C<sub>IN</sub> measurement) shall be measured only for the initial test and after process or design changes which may affect input capacitance. A minimum sample of 3 devices with zero rejects shall be required.

- 4.4.2 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.2.1 Additional criteria for device class M. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- 4.4.2.2 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-00540  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>34 |

## TABLE IIA. Electrical test requirements.

| Test requirements                                 | Subgroups<br>(in accordance with<br>MIL-STD-883,<br>method 5005, table I) | Subgroups<br>(in accordance with<br>MIL-PRF-38535, table III) |                                                  |

|---------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------|

|                                                   | Device<br>class M                                                         | Device<br>class Q                                             | Device<br>class V                                |

| Interim electrical parameters (see 4.2)           |                                                                           |                                                               | 1, 7, 9                                          |

| Final electrical parameters (see 4.2)             | 1, 2, 3, 7, 8, 9,<br>10, 11 <u>1</u> /                                    | 1, 2, 3, 7, 8, 9,<br>10, 11 <u>1</u> /                        | 1, 2, 3, 7, 8, 9,<br>10, 11 <u>2/</u> <u>3</u> / |

| Group A test requirements (see 4.4)               | 1, 2, 3, 4, 7, 8, 9,<br>10, 11                                            | 1, 2, 3, 4, 7, 8, 9,<br>10, 11                                | 1, 2, 3, 4, 7, 8, 9,<br>10, 11                   |

| Group C end-point electrical parameters (see 4.4) | 2, 8A, 10                                                                 | 2, 8A, 10                                                     | 2, 8A, 10<br><u>3</u> /                          |

| Group D end-point electrical parameters (see 4.4) | 1, 7, 9                                                                   | 1, 7, 9                                                       | 1, 7, 9                                          |

| Group E end-point electrical parameters (see 4.4) | 1, 7, 9                                                                   | 1, 7, 9                                                       | 1, 7, 9                                          |

TABLE IIB. Delta limits.

| Parameter <u>1</u> / | Limit | Unit |

|----------------------|-------|------|

| V <sub>OH</sub>      | ±0.1  | V    |

| V <sub>OL</sub>      | ±0.1  | V    |

| I <sub>IH</sub>      | ±0.1  | μΑ   |

| I <sub>IL</sub>      | ±0.1  | μΑ   |

| I <sub>OZH</sub>     | ±0.1  | μΑ   |

| l <sub>OZL</sub>     | ±0.1  | μΑ   |

<sup>1/</sup> The parameters shall be recorded before and after the required burn-in and life test to determine the delta limits.