| REVISIONS |                                                                                     |                 |                |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------|-----------------|----------------|--|--|--|--|--|

| LTR       | DESCRIPTION                                                                         | DATE (YR-MO-DA) | APPROVED       |  |  |  |  |  |

| A         | Add device types 03, 04, 05, and 06. Add packages U and Z. Rewrite entire document. | 94-02-04        | K. A. Cottongi |  |  |  |  |  |

## THE ORIGINAL FIRST PAGE OF THIS DRAWING HAS BEEN REPLACED.

|                                                                                |                   |                | I  |                                                             |     |          | Ι                 |                                                                       |    |            |       | T     | Ţ   |     |    |     |    |    |    |    |

|--------------------------------------------------------------------------------|-------------------|----------------|----|-------------------------------------------------------------|-----|----------|-------------------|-----------------------------------------------------------------------|----|------------|-------|-------|-----|-----|----|-----|----|----|----|----|

| REV                                                                            | A                 | A              | Α  | A                                                           | A   | A        | Α                 | Α                                                                     | Α  |            |       |       |     |     |    |     |    |    |    |    |

| SHEET                                                                          | 35                | 36             | 37 | 38                                                          | 39  | 40       | 41                | 42                                                                    | 43 |            |       |       |     |     |    |     |    |    |    |    |

| REV                                                                            | A                 | A              | Α  | A                                                           | A   | A        | A                 | A                                                                     | A  | A          | A     | A     | A   | A   | A  | A   | A  | A  | A  | A  |

| SHEET                                                                          | 15                | 16             | 17 | 18                                                          | 19  | 20       | 21                | 22                                                                    | 23 | 24         | 25    | 26    | 27  | 28  | 29 | 30  | 31 | 32 | 33 | 34 |

| REV STATUS<br>OF SHEETS                                                        |                   |                | RE | V                                                           |     | A        | A                 | A                                                                     | A  | A          | A     | A     | A   | A   | A  | A   | A  | A  | A  |    |

|                                                                                |                   |                | SH | EET                                                         |     | 1        | 2                 | 3                                                                     | 4  | 5          | 6     | 7     | 8   | 9   | 10 | 11  | 12 | 13 | 14 |    |

| PMIC N/A                                                                       | DEFENSE ELECTRONI |                |    |                                                             |     |          | CS SUPPLY CENTER  |                                                                       |    |            |       |       |     |     |    |     |    |    |    |    |

| MILITARY                                                                       |                   |                |    | CHECKED BY<br>Steve Duncan                                  |     |          |                   |                                                                       |    | 1          | DATIC | JN, C | нто | 454 | 44 |     |    |    |    |    |

| DRAWING  THIS DRAWING IS AVAILABLE                                             |                   |                |    | APPROVED BY Monica Poelking  DRAWING APPROVAL DATE 91-09-19 |     |          |                   | MICROCIRCUIT, DIGITAL, MIL-STD-1553, MUX BUS, REMOTE TERMINAL, HYBRID |    |            |       |       |     |     |    | 53, |    |    |    |    |

| FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A |                   |                |    |                                                             |     |          |                   |                                                                       |    |            |       |       |     |     |    |     |    |    |    |    |

|                                                                                |                   | REVISION LEVEL |    |                                                             |     | SIZ<br>A | CAGE CODE A 67268 |                                                                       |    | 5962-91687 |       |       |     |     |    |     |    |    |    |    |

|                                                                                | A                 |                |    | SH                                                          | EET |          | 1                 |                                                                       | ,  | OF         |       | 43    |     |     |    |     |    |    |    |    |

| DESC FORM 193                                                                  |                   |                |    |                                                             |     |          |                   |                                                                       |    |            |       |       |     |     |    |     |    |    |    |    |

DESC FORM 193

JUL 91

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E067-94

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). This drawing describes device requirements for hybrid microcircuits to be processed in accordance with MIL-H-38534. Two product assurance classes, military high reliability (device class H) and space application (device class K) and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of radiation hardness assurance levels are reflected in the PIN.

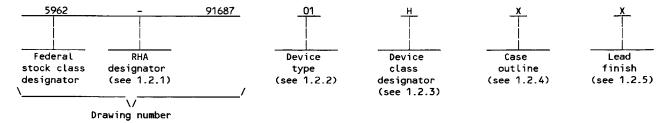

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes H and K RHA marked devices shall meet the MIL-H-38534 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>                                                                                                           |

|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 01          | NHI-1553RT     | MIL-STD-1553, dual redundant, remote terminal, seperate V <sub>CC</sub> for internal RAM, hybrid transceivers                     |

| 02          | NHI-1554RT     | MIL-STD-1553, dual redundant, remote terminal, seperate input pin for<br>SSFlag/Terminal Flag, hybrid transceivers                |

| 03          | NHI-1561RT     | MIL-STD-1553, dual redundant, remote terminal, multichip, monolithic transceivers                                                 |

| 04          | NHI-1562RT     | MIL-STD-1553, dual redundant, remote terminal, multichip, monolithic transceivers, MacAir                                         |

| 05          | NHI-1572RT     | MIL-STD-1553, dual redundant, remote terminal, seperate V <sub>CC</sub> for internal RAM, multichip, monolithic transceivers      |

| 06          | NHI-1576RT     | MIL-STD-1553, dual redundant, remote terminal, seperate input pin for<br>SSFlag/Terminal Flag, multichip, monolithic transceivers |

1.2.3 <u>Device class designator</u>. This device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

H or K

Certification and qualification to MIL-H-38534

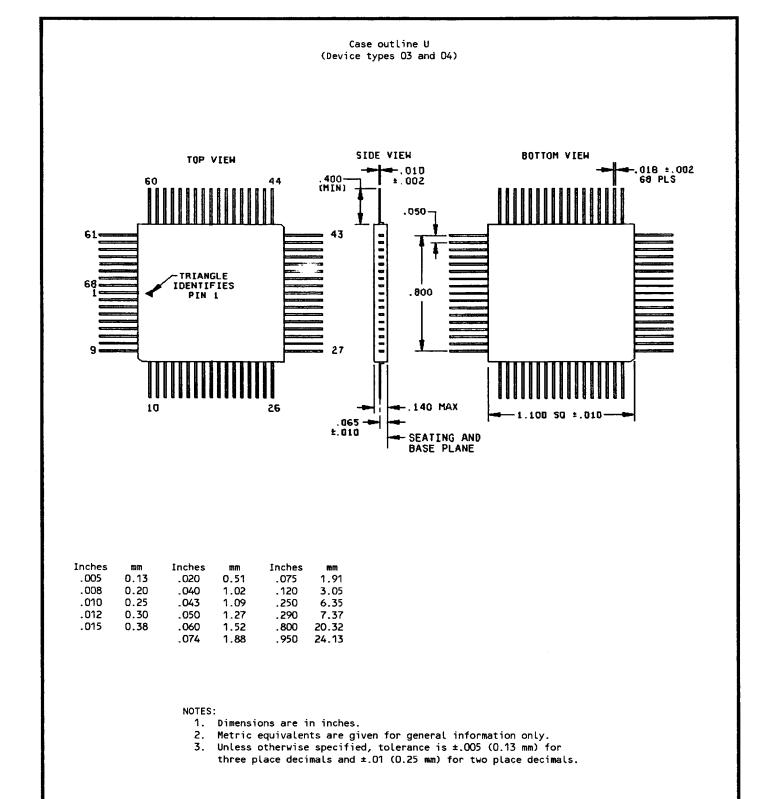

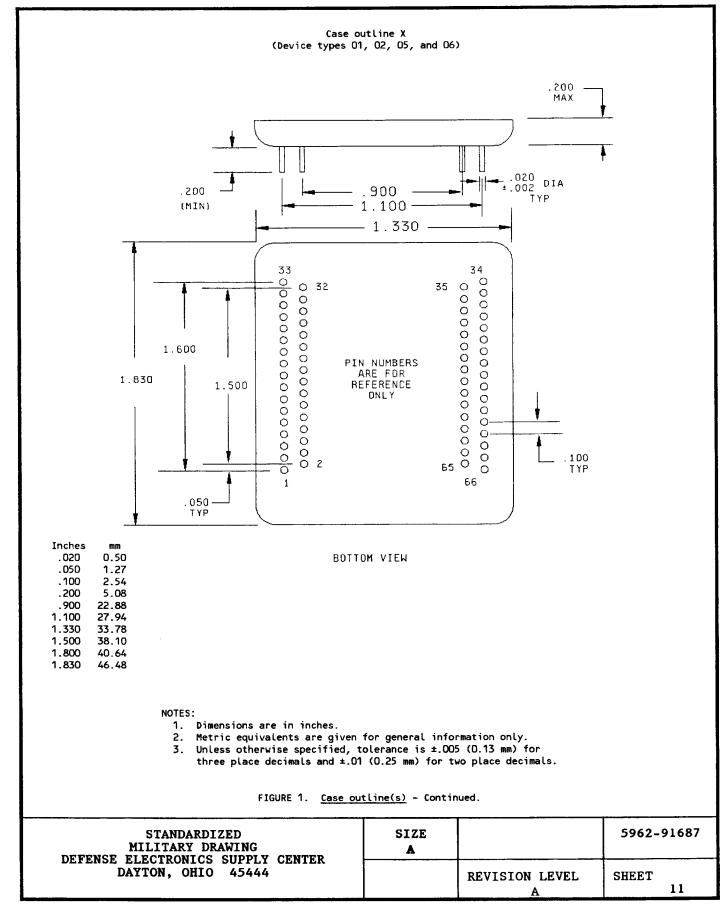

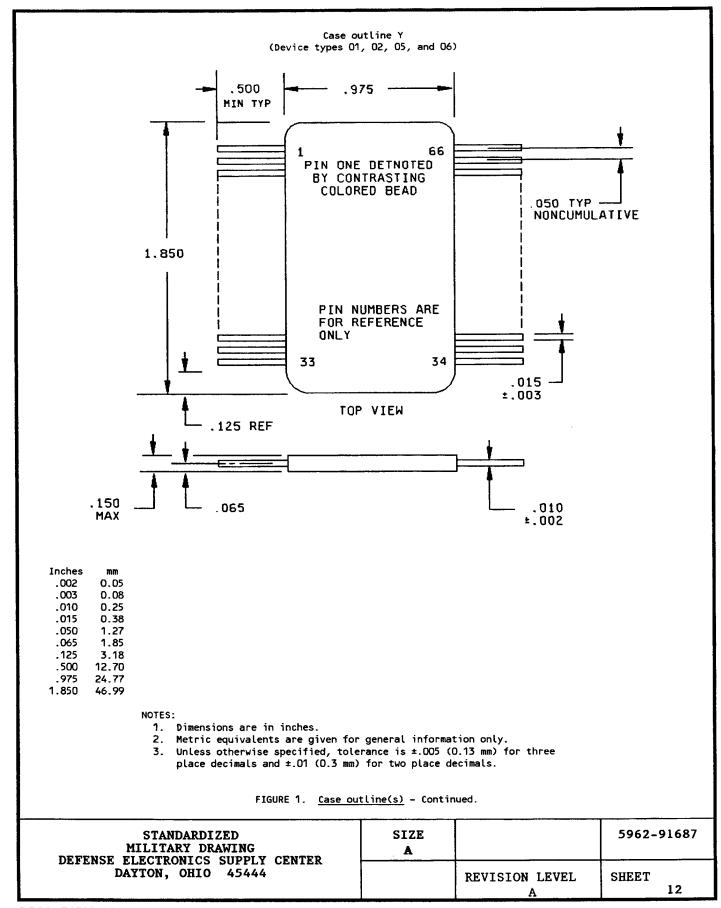

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | <u>Descriptive</u> designator | <u>Terminals</u> | Package style |

|----------------|-------------------------------|------------------|---------------|

| U              | See figure 1                  | 68               | Flat pack     |

| X              | See figure 1                  | 66               | Dual-in-line  |

| Y              | See figure 1                  | 66               | Flat pack     |

| Z              | See figure 1                  | 69               | Grid array    |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-H-38534 for classes H and K. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687 |

|-----------------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL<br>A | SHEET<br>2 |

| 1.3 Absolute maximum ratings. 1/                                                                                                                                                                                  |                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Supply voltage range (V <sub>CC</sub> )                                                                                                                                                                           | -0.3 V dc to +7 V dc<br>-65°C to +150°C<br>+15°C/W<br>+300°C                 |

| Lead soldering temperature (10 seconds)                                                                                                                                                                           |                                                                              |

| Device types 01 and 02, (T <sub>C</sub> = +125°C) Device types 03, 04, 05, and 06:                                                                                                                                | 1.3 W                                                                        |

| Hottest die (100% duty cycle)                                                                                                                                                                                     | 0.500 W                                                                      |

| Total hybrid (standby)                                                                                                                                                                                            | 0.550 ₩<br>1.05 ₩                                                            |

| Thermal resistance, junction-to-case $(	heta_{	extsf{JC}})$                                                                                                                                                       | 4°C/W                                                                        |

| 1.4 Recommended operating conditions.                                                                                                                                                                             |                                                                              |

| Supply voltage range (V <sub>CC</sub> ):  Device types 01 and 02                                                                                                                                                  | +4.75 V dc to +5.50 V dc<br>+4.50 V dc to +5.50 V dc<br>+2 V dc<br>+0.8 V dc |

| Maximum logic low input voltage (V <sub>IL</sub> )                                                                                                                                                                | -55°C to +125°C                                                              |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                           |                                                                              |

| 2.1 <u>Government specification, standards, and handbook</u> . Unless of standards, and handbook of the issue listed in that issue of the De Standards specified in the solicitation, form a part of this drawing | epartment of Defense Index of Specifications and                             |

| SPECIFICATION                                                                                                                                                                                                     |                                                                              |

| MILITARY                                                                                                                                                                                                          |                                                                              |

| MIL-H-38534 - Hybrid Microcircuits, General Specification                                                                                                                                                         | for.                                                                         |

| STANDARDS                                                                                                                                                                                                         |                                                                              |

| MILITARY                                                                                                                                                                                                          |                                                                              |

| MIL-STD-883 - Test Methods and Procedures for Microelectro<br>MIL-STD-973 - Configuration Management.<br>MIL-STD-1835 - Microcircuit Case Outlines.                                                               | onics.                                                                       |

| HANDBOOK                                                                                                                                                                                                          |                                                                              |

| MILITARY                                                                                                                                                                                                          |                                                                              |

| MIL-HDBK-780 - Standardized Military Drawings.                                                                                                                                                                    |                                                                              |

| (Copies of the specification, standards, and handbook required by acquisition functions should be obtained from the contracting activ                                                                             |                                                                              |

| 2.2 Order of precedence. In the event of a conflict between the<br>herein, the text of this drawing shall take precedence.                                                                                        | e text of this drawing and the references cited                              |

| 1/ Stresses above the absolute maximum rating may cause permanent operation at the maximum levels may degrade performance and af                                                                                  |                                                                              |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                             | 1                                                                            |

|                                                      |           | •              |            |

|------------------------------------------------------|-----------|----------------|------------|

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-91687 |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET      |

3

### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-H-38534 and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-H-38534 and herein.

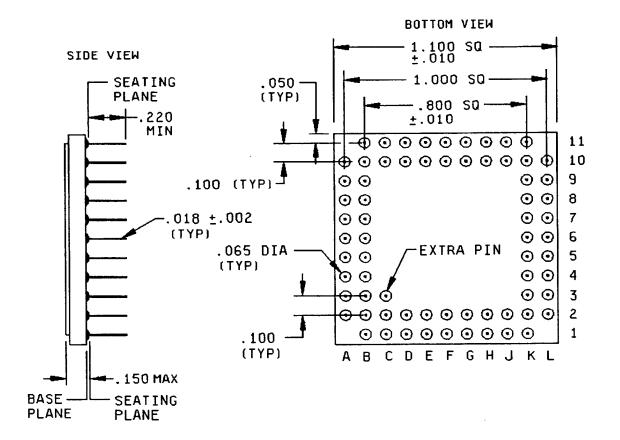

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

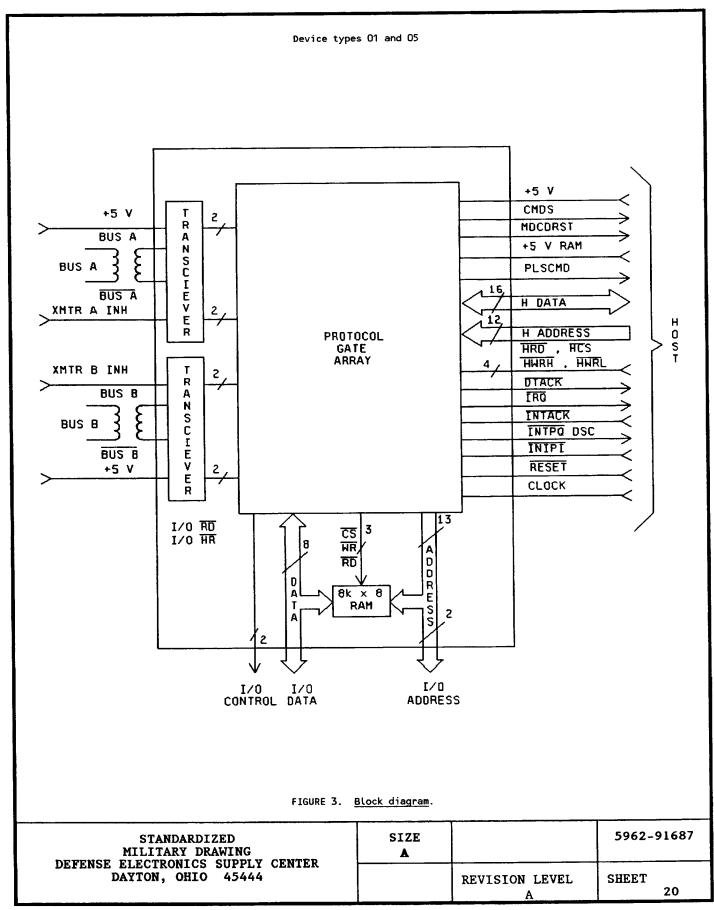

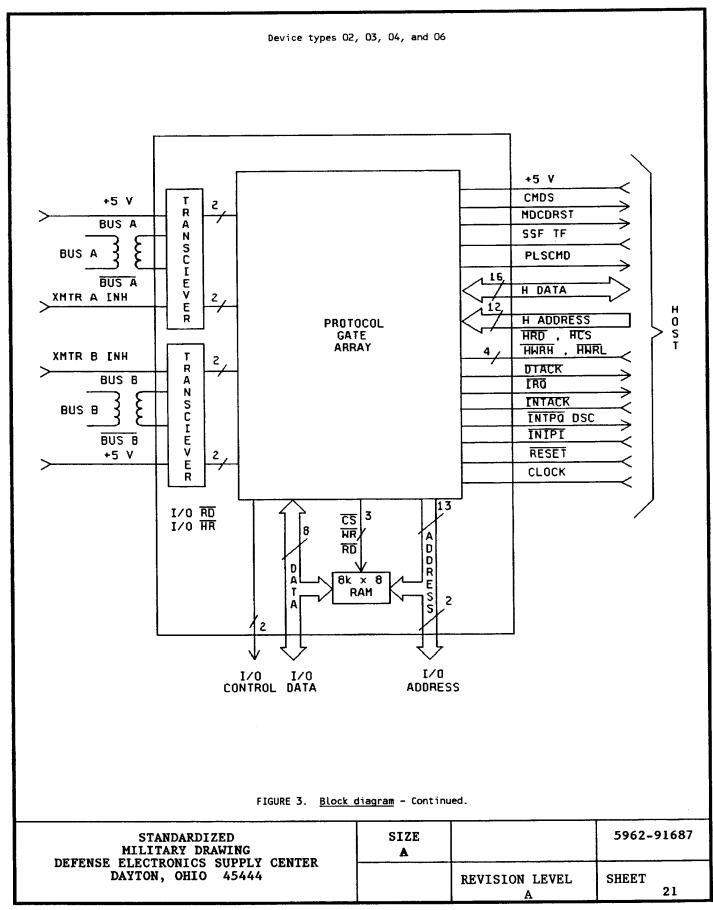

- 3.2.3 Block diagram(s). The block diagram(s) shall be as specified on figure 3.

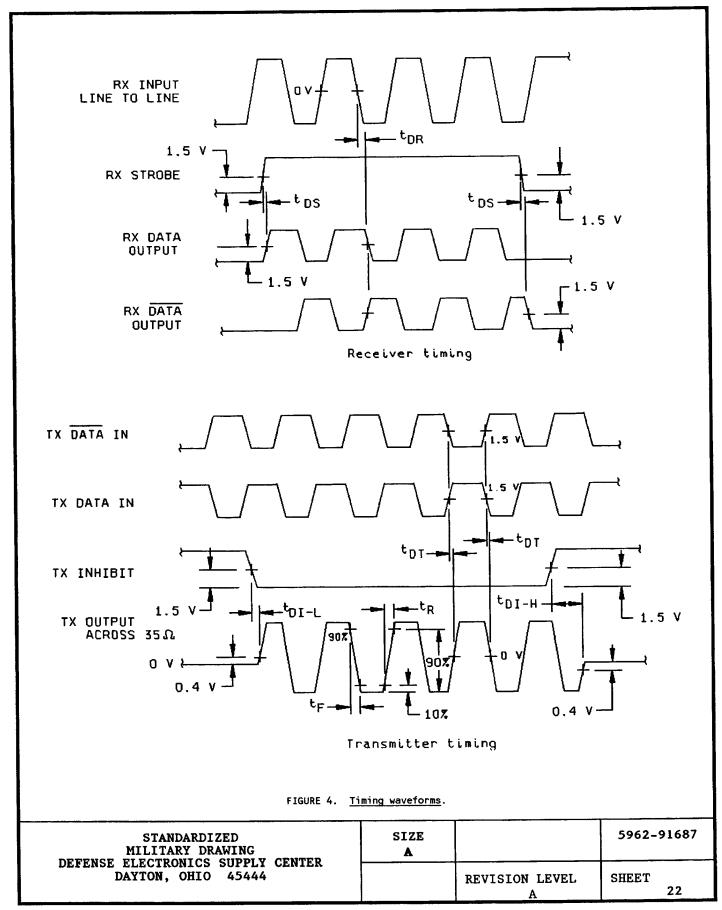

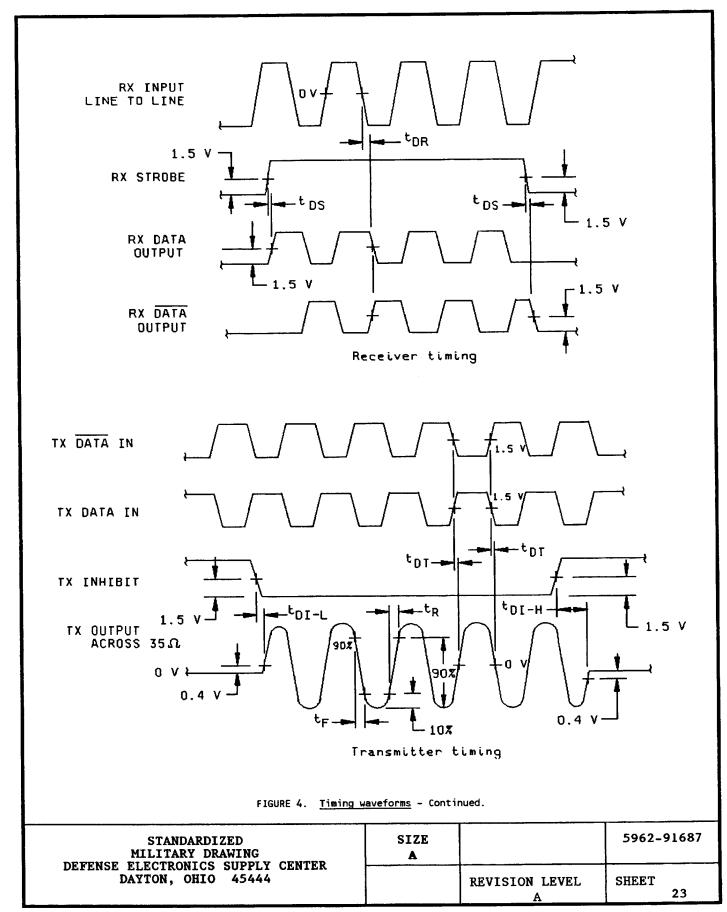

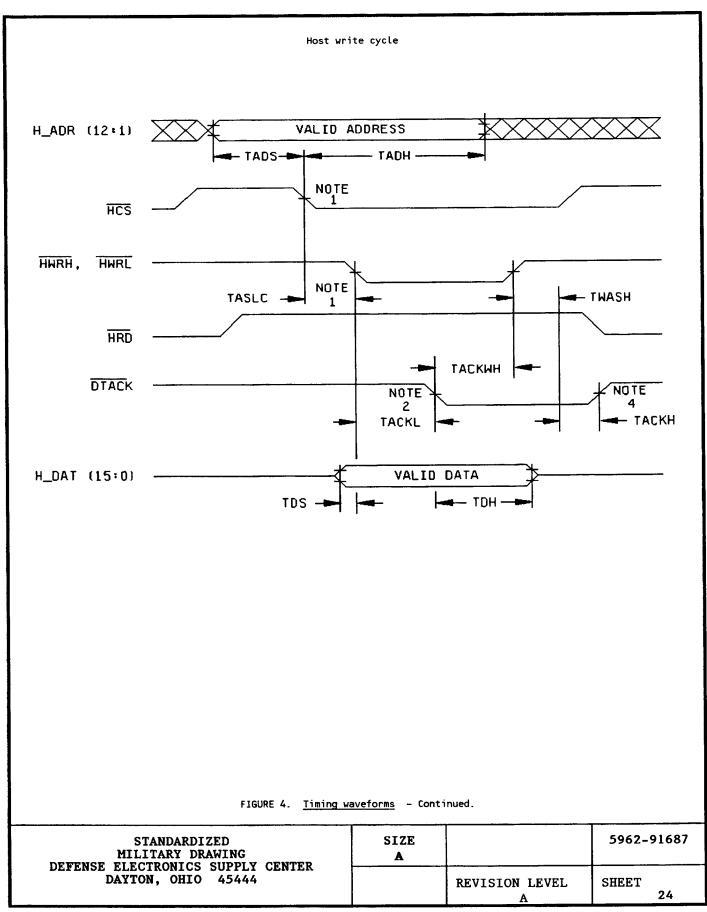

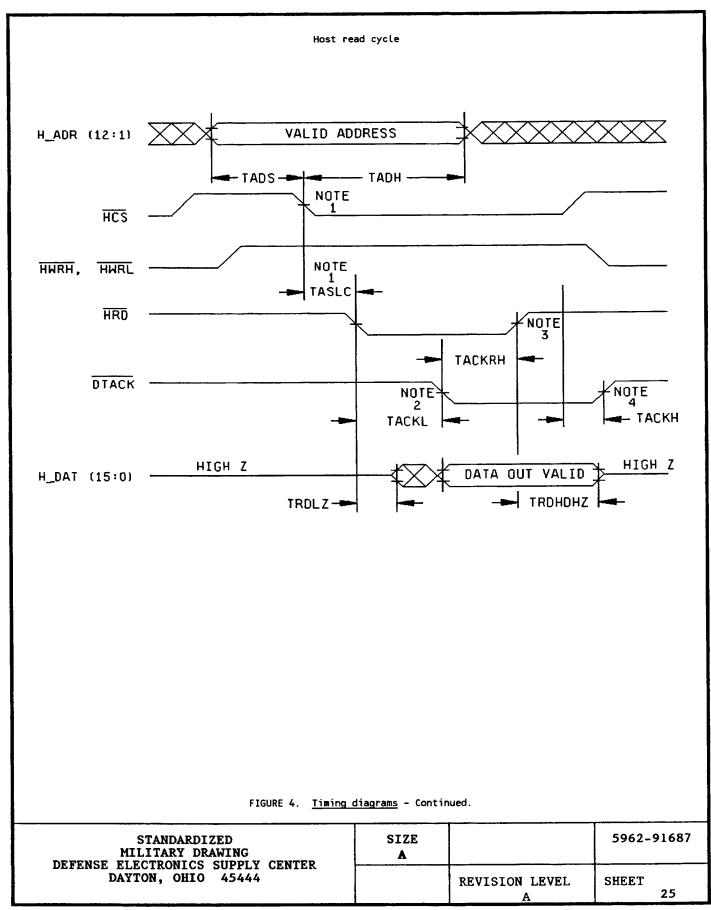

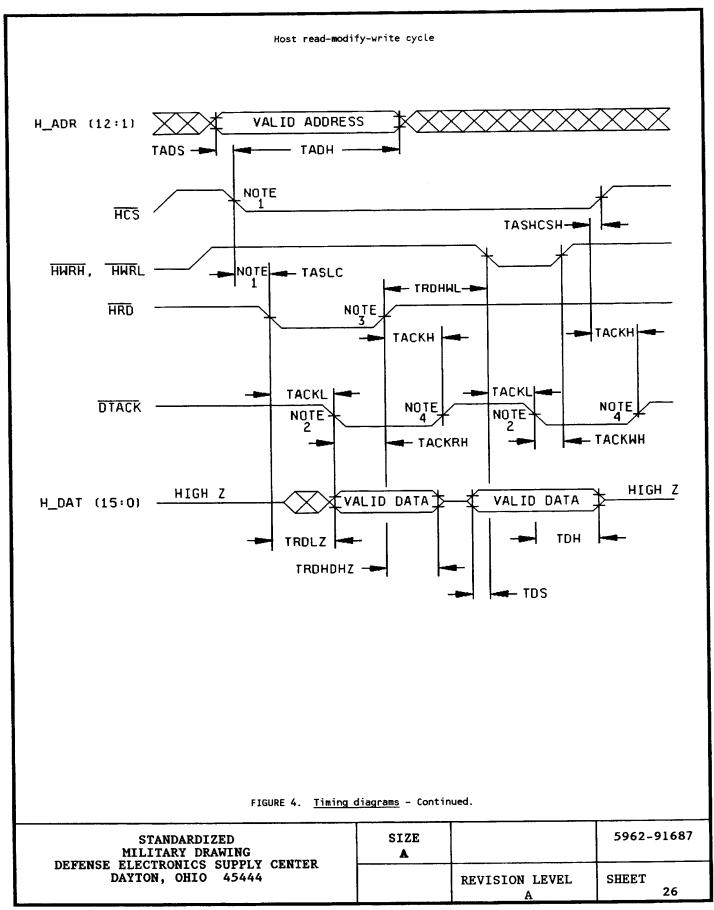

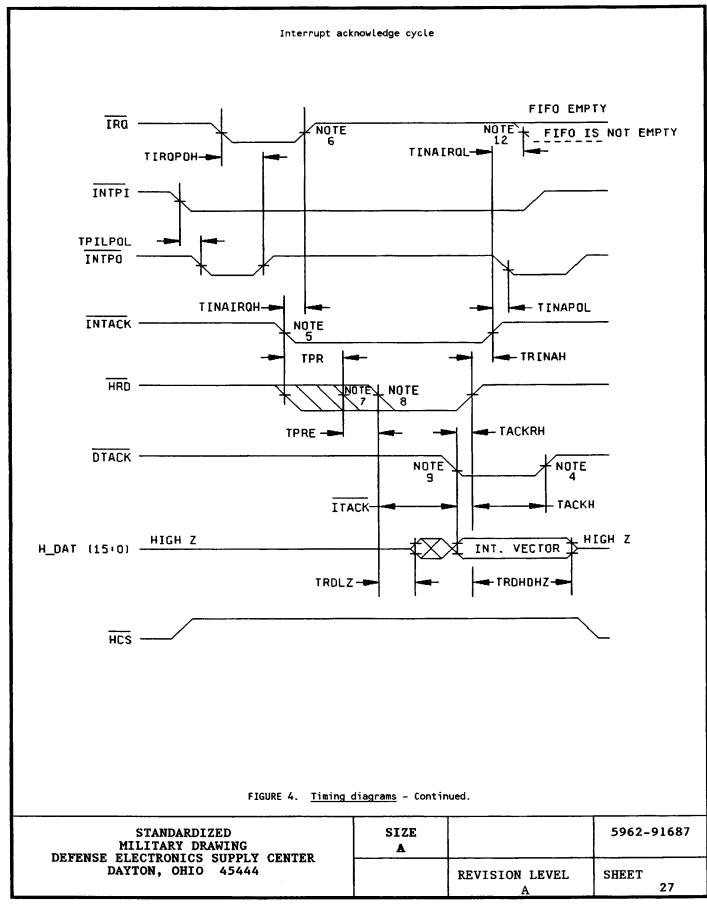

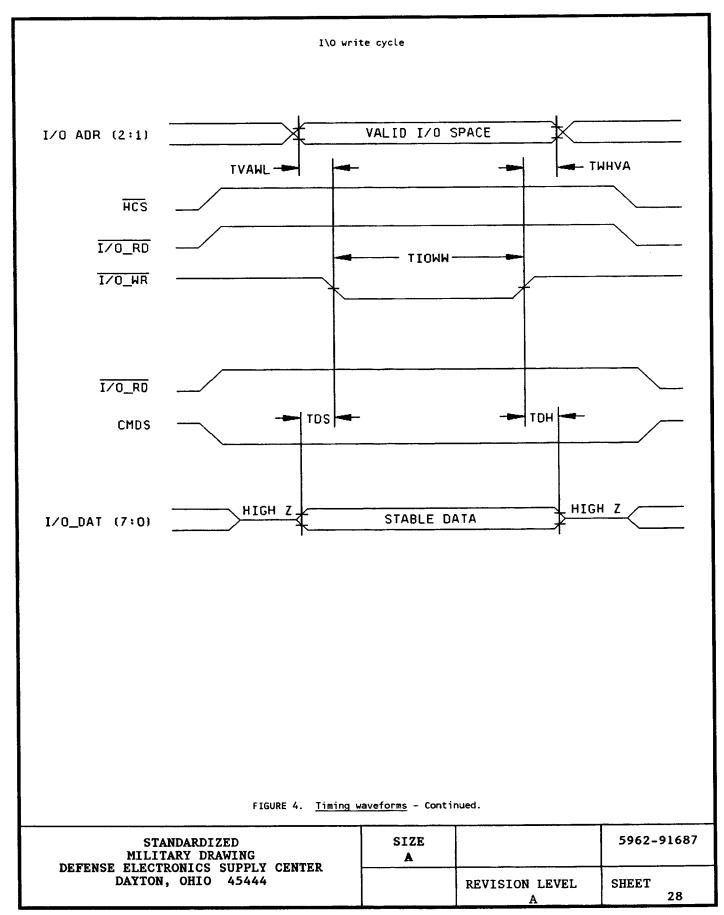

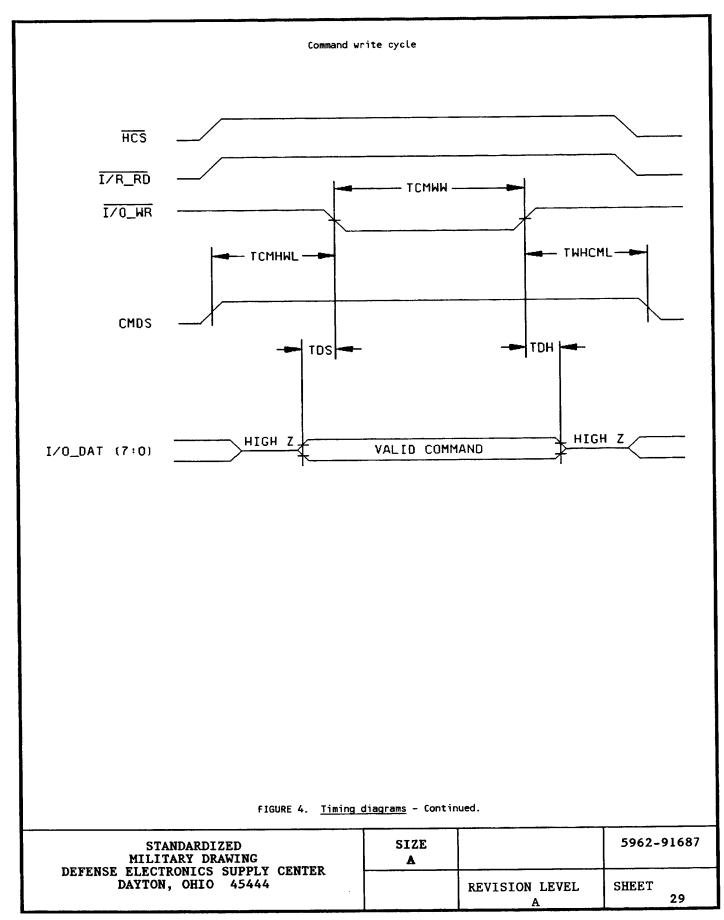

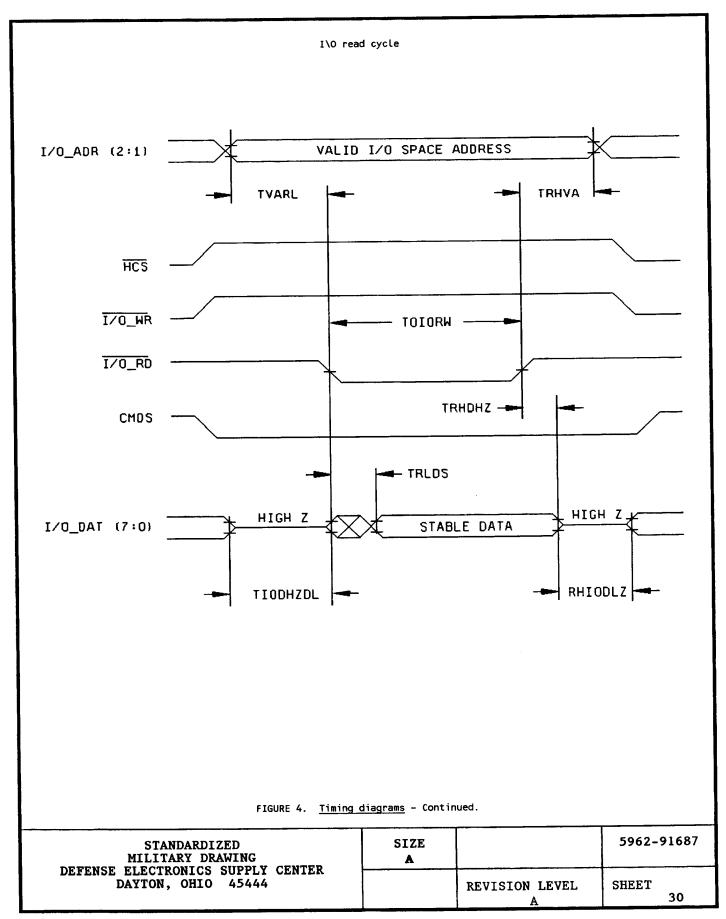

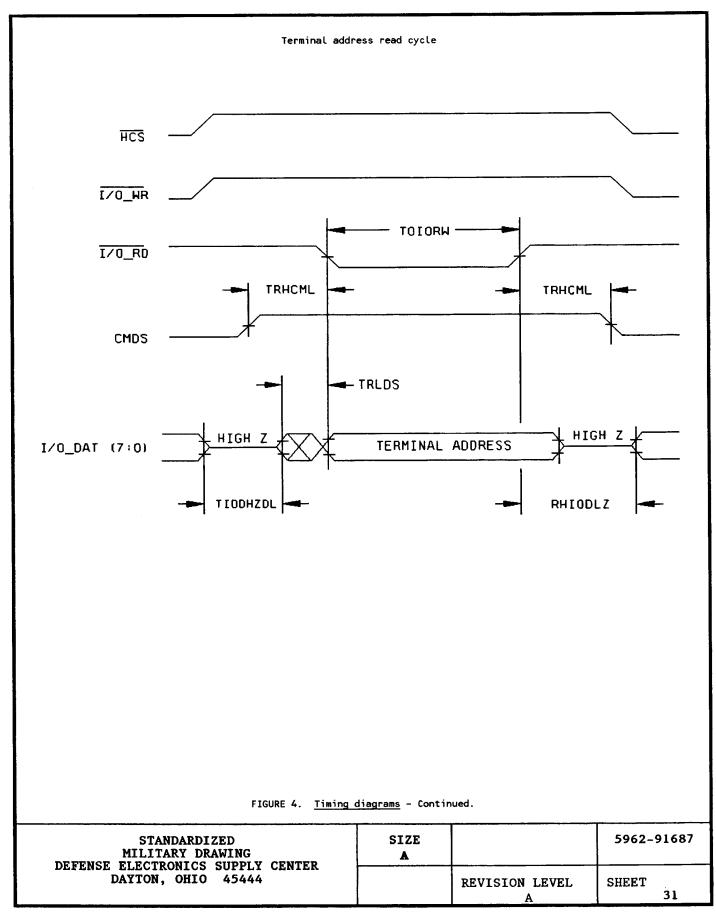

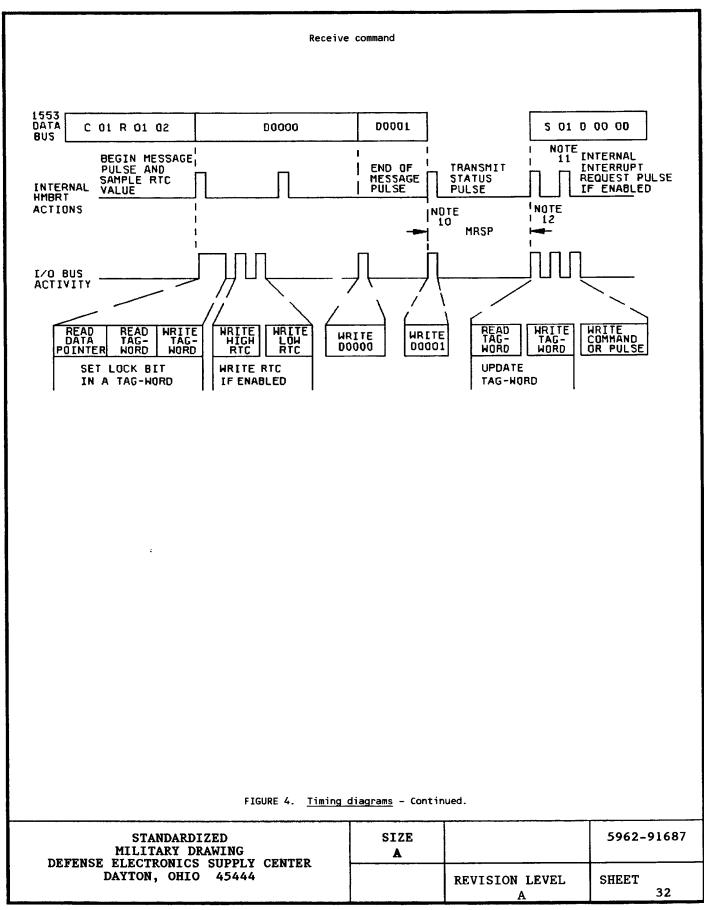

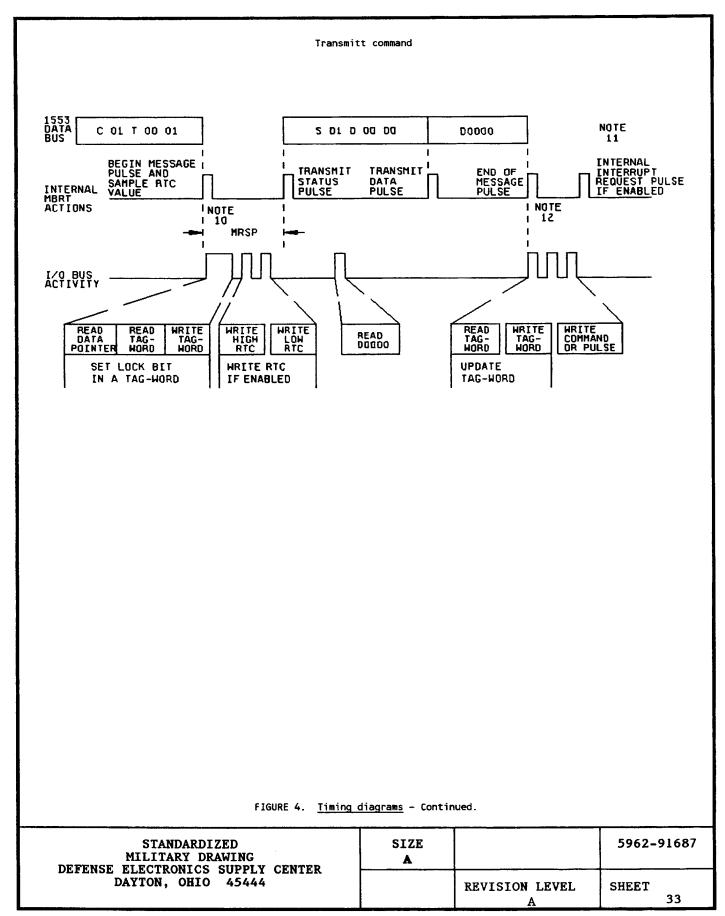

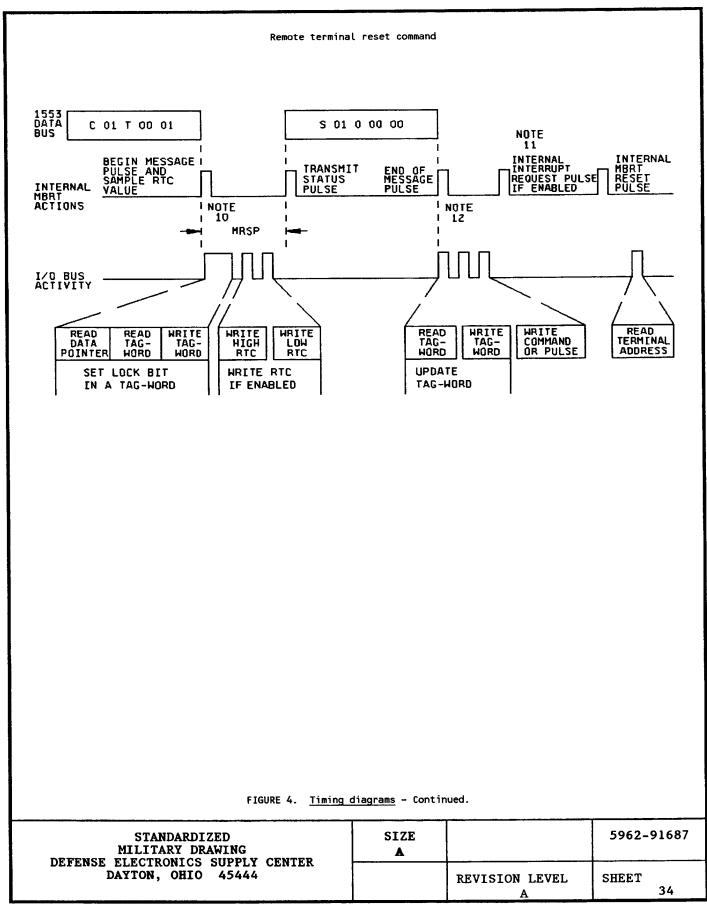

- 3.2.4 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 4.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full specified operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-H-38534. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in QML-38534.

- 3.6 Manufacturer eligibility. In addition to the general requirements of MIL-H-38534, the manufacturer of the part described herein shall maintain the electrical test data (variables format) from the initial quality conformance inspection group A lot sample, produced on the certified line, for each device type listed herein. The data should also include a summary of all parameters manually tested, and for those which, if any, are guaranteed. This data shall be maintained under document revision level control by the manufacturer and be made available to the preparing activity (DESC-EC) upon request.

- 3.7 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to supply to this drawing. The certificate of compliance submitted to DESC-EC shall affirm that the manufacturer's product meets the requirements of MIL-H-38534 and the requirements herein.

- 3.8 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-H-38534 shall be provided with each lot of microcircuits delivered to this drawing.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with MIL-H-38534.

- 4.2 Screening. Screening shall be in accordance with MIL-H-38534. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DESC-EC or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2)  $T_{\Delta}$  as specified in accordance with table I of method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>4 |

| Test                                    | Symbol            | Conditions $\frac{1}{2}$ / -55°C $\leq T_C \leq +125$ °C | Group A subgroups | Device<br>type | Li       | mits | Unit        |  |

|-----------------------------------------|-------------------|----------------------------------------------------------|-------------------|----------------|----------|------|-------------|--|

|                                         |                   | unless otherwise specified                               |                   |                | Min      | Max  |             |  |

| Input voltage<br>high                   | V <sub>IH</sub>   | V <sub>CC</sub> = 5.5 V<br>I <sub>IH</sub> = ≤  10 μA    | 1, 2, 3           | All            | 2        |      | V           |  |

| Input voltage<br>low                    | VIL               | I <sub>IL</sub> ≤  10 μA                                 | 1, 2, 3           | All            |          | 0.8  | V           |  |

| Low level output <u>3</u> /<br>current  | I <sub>OL1</sub>  | V <sub>CC</sub> = 5.5 V, V <sub>OL</sub> ≤ 0.4 V         | 1, 2, 3           | ALL            |          | 8    | .mĄ         |  |

| Low level output <u>4</u> /             | I <sub>OL2</sub>  | _                                                        |                   |                |          | 4    | <br> <br> - |  |

| Low level output <u>5</u> /<br>current  | I <sub>OL</sub> 3 |                                                          |                   |                |          | 4    | _           |  |

| Low level output <u>6</u> /<br>current  | I <sub>OL4</sub>  | _                                                        |                   |                |          | 6    | <br> <br> - |  |

| Low level output <u>7</u> /<br>current  | I <sub>OL5</sub>  |                                                          |                   |                |          | 12   | <u> </u>    |  |

| High level output <u>3</u> /<br>current | I <sub>OH1</sub>  | v <sub>CC</sub> = 5.5 v, v <sub>OH</sub> ≤ 2.7 v         | 1, 2, 3           | ALL            | 8        |      | mA_         |  |

| High level output <u>4</u> /<br>current | I <sub>OH2</sub>  | _                                                        |                   |                | 4        |      | -           |  |

| High level output <u>5</u> /<br>current | <sup>I</sup> он3  | _                                                        |                   |                | 4        |      | -           |  |

| High level output <u>6</u> /<br>current | <sup>1</sup> он4  |                                                          |                   | 1              | 6        |      | -           |  |

| Supply current                          | <sup>1</sup> cc   | Standby (idle)                                           | 1, 2, 3           | ALL            |          | 90   | _  mA       |  |

|                                         |                   | 25% duty cycle, 1 MHz                                    | _                 |                | <u> </u> | 250  | -           |  |

|                                         |                   | 50% duty cycle, 1 MHz                                    | _                 |                |          | 380  | -           |  |

|                                         |                   | 100% duty cycle, 1 MHz                                   |                   |                |          | 675  |             |  |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-91687 |

|------------------------------------------------------------------------------------|-----------|---------------------|------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>5 |

| Test                                     | Symbol          | Conditions $\frac{1}{2}$ /<br>-55°C $\leq T_C \leq +125$ °C | Group A   | Device<br>type | Li   | mits       | ts Uni          |  |

|------------------------------------------|-----------------|-------------------------------------------------------------|-----------|----------------|------|------------|-----------------|--|

|                                          |                 | unless otherwise specified                                  |           |                | Min  | Max        |                 |  |

| Input capacitance                        | c <sub>IN</sub> | See 4.3.1c                                                  | 4         | All            |      | 10         | pF              |  |

| Receiver differential<br>input impedance | z <sub>IN</sub> | DC to 1.0 MHz                                               | 4, 5, 6   | ALL            | 10   |            | kΩ              |  |

| Receiver input<br>threshold voltage      | v <sub>TH</sub> | Direct coupled                                              | 4, 5, 6   | ALL            | 0.6  | 1.2        | V <sub>PP</sub> |  |

| Receiver differential<br>input voltage   | VIN             | DC to 1.0 MHz                                               | 4, 5, 6   | ALL            |      | 20         | V <sub>PP</sub> |  |

| Receiver common-mode<br>rejection ratio  | CMRR            | DC to 2.0 MHz                                               | 4, 5, 6   | ALL            | 40   |            | dB              |  |

| Transmitter<br>differential              | v <sub>o</sub>  | 35Ω load                                                    | 4, 5, 6   | ALL            | 7.1  | 9          | V <sub>PP</sub> |  |

| output voltage                           |                 | 140Ω Load                                                   |           |                | 28.3 | 36         |                 |  |

| Waveform distortion                      | v <sub>wD</sub> | 35Ω Load                                                    | 4, 5, 6   | 03,04,         | -0.1 | 0.1        | VPEAK           |  |

| Output offset<br>voltage                 | v <sub>os</sub> | Direct coupled, measured across the bus.                    | 4, 5, 6   | 01,02          | -90  | +90        | mV              |  |

| Output: rise time                        | tr              | <br>  See figure 4                                          | 9, 10, 11 | 01,02          | 100  | 300        | ns              |  |

| fall time                                | t <sub>f</sub>  |                                                             |           |                | 100  | 300        |                 |  |

| Access setup time                        | TADS            | Host read, write and                                        | 9, 10, 11 | ALL            | 0    |            | _ ns            |  |

| Access hold time                         | TADH            | read-modify write, see<br>figure 4. Setup receive           |           |                | 200  | ļ <u>.</u> | _               |  |

| Address strobe low to                    | TASLC           | message as on figure 4 (receive command).                   |           |                | 0    |            |                 |  |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-91687 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET 6    |

| Test                                     | Symbol                 | Conditions $\frac{1}{2}$ /<br>$-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$<br>unless otherwise specified | Group A subgroups | Device<br>type | <br> | imits    | Unit  |

|------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|-------------------|----------------|------|----------|-------|

|                                          |                        | unless otherwise specified                                                                               |                   |                | Min  | Max      |       |

| Data acknowledge low<br>to write high    | TACKWH                 | Host read, write and read-modify write, see                                                              | 9, 10, 11         | ALL            | 0    |          | ns    |

| *HWRL, *HWRH high<br>to *HCS high        | TWASH                  | figure 4. Setup receive message as on figure 4 (receive command).                                        |                   |                | 0    |          | _     |

| End of cycle to data<br>acknowledge high | ТАСКН                  |                                                                                                          |                   |                | 0    | 30       |       |

| End of cycle to data                     | TACKL1                 | no contention                                                                                            |                   |                | 0.3  | 0.5      | _  µs |

| acknowledge low                          | TACKL2                 | with contention                                                                                          |                   |                | 0.3  | 1.2      | _     |

|                                          | TACKL3                 | worst case, one time<br>  at start of each message                                                       |                   |                | 0.3  | 2.8      |       |

| Data setup time                          | TDS                    | 1                                                                                                        |                   |                | 0    | ļ        | ns    |

| Data hold time                           | TDH                    |                                                                                                          |                   |                | 0    | <u> </u> | _[    |

| Data acknowledge low<br>to read high     | TACKRH                 |                                                                                                          |                   |                | 0    |          |       |

| *HRD low to data<br>low Z                | TRDLZ                  |                                                                                                          |                   |                | 0    | 20       | _     |

| *HRD high to data<br>high Z              | TRDHDHZ                |                                                                                                          |                   |                | 0    | 30       | _     |

| *HRD high to write<br>low                | TRDHWL                 |                                                                                                          |                   |                | 30   |          |       |

| *IRQ to *INTPI<br>output high            | TIRQPOH                | Interrupt acknowledge cyclo<br>see figure 4. Setup receiv                                                |                   | All            |      | 20       | ns    |

| *INPI low to *INTPO<br>low               | TPILPOL                | message as on figure 4.                                                                                  |                   |                |      | 40       | _     |

| Priority propagation time                | TPR                    |                                                                                                          |                   |                | 400  | 500      |       |

| Propagation time                         | TPRE                   | -                                                                                                        |                   |                | 0    |          |       |

| *INTACK low to *IRQ<br>high              | TINAIRQH               |                                                                                                          |                   |                | 0    | 200      | _     |

| *INTACK high to next<br>*IRQ low         | TINAIRQL               |                                                                                                          |                   |                | 0    | 200      |       |

| See footnotes at end o                   | of table.              |                                                                                                          |                   |                |      |          |       |

|                                          |                        |                                                                                                          |                   |                |      |          |       |

| MIL                                      | STANDARDI<br>LITARY DR |                                                                                                          | SIZE<br>A         |                |      | 5        |       |

| Test                                     | Symbol   | Conditions <u>1</u> / <u>2</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified | Group A<br>subgroups | Device<br>type | Limits |     | Unit          |

|------------------------------------------|----------|---------------------------------------------------------------------------------------------------|----------------------|----------------|--------|-----|---------------|

|                                          |          | untess otherwise specified                                                                        |                      |                | Min    | Max |               |

| *INTACK high to<br>*INTPO low            | TINAPOL  | Interrupt acknowledge cycle, see figure 4. Setup receive message on figure 4.                     | 9, 10, 11            | ALL            | 30     | 40  | <br>  ns<br>- |

| *HRD low to *DTACK<br>low                | TRINAH   |                                                                                                   |                      |                | 0      |     |               |

| *HRD low to *DTACK<br>low                | ITACK    |                                                                                                   |                      |                | 300    | 400 | -             |

| *DTACK low to *HRD<br>high               | TACKRH   |                                                                                                   |                      |                | 0      |     |               |

| *HRD low to data in low Z                | TRDLZ    |                                                                                                   |                      |                | 0      | 20  |               |

| *HRD low to data in<br>high Z            | TRSHDHZ  |                                                                                                   |                      |                | o<br>  | 30  |               |

| End of cycle to<br>*DTACK high           | ТАСКН    |                                                                                                   |                      |                | o<br>  | 30  |               |

| Transmitter output<br>rise and fall time | tr, tf   |                                                                                                   |                      |                | 100    | 300 |               |

| Vadid address to<br>I/O write low        | TVAWL    | <br>  I/O write and command<br>  write, see figure 4.                                             | 9, 10, 11            | ALL            | 50     |     | ns<br>        |

| Address valid to<br>I/O write high       | TWHVA    | Setup receive message as on figure 4.                                                             |                      |                | 50     |     |               |

| I/O *WR pulse width                      | TIOWW    | _                                                                                                 |                      |                | 90     | 110 |               |

| Data setup time                          | TDS      | _                                                                                                 |                      |                | 25     | 50  |               |

| Data hold time                           | <br> TDH |                                                                                                   |                      |                | 40     | 80  |               |

| Command write pulse width                | TCMWW    |                                                                                                   | [<br> <br>           |                | 290    | 310 |               |

| Command strobe to I/O write low          | TCMHWL   | -<br>-<br>-                                                                                       |                      |                | 40     |     |               |

| Write high to CMDS                       | TWHCML   |                                                                                                   |                      |                | 100    |     |               |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-91687 |

|------------------------------------------------------------------------------------|-----------|---------------------|------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>8 |

| Test                                  | Symbol              | Conditions $\frac{1}{2}$ / $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$ unless otherwise specified | Group A subgroups | Device<br>type | Li             | mits     | Unit<br>- |

|---------------------------------------|---------------------|----------------------------------------------------------------------------------------------------|-------------------|----------------|----------------|----------|-----------|

|                                       |                     | unless otherwise specified                                                                         |                   |                | Min            | Max      |           |

| Valid address to<br>read low          | TVARL               | I/O read and terminal address read, see                                                            | 9, 10, 11         | ALL            | 50             |          | ns<br>-   |

| Adress valid after<br>read high       | TRHVA               | figure 4. Setup receive<br>message as on figure 4.                                                 |                   |                | 50             |          | -         |

| I/O *RD pulse width                   | TOIORW              |                                                                                                    | [<br>]            |                | 190            | 210      | _         |

| I/O *RD high to data<br>high Z        | TRHDHZ              |                                                                                                    |                   |                | 0              | 200      | _         |

| I/O *RD high to CMDS<br>low           | TRHCML              |                                                                                                    |                   |                | 100            |          | _         |

| I/O data bus high Z<br>to data on bus | TIODHZRL            |                                                                                                    |                   |                | 100            |          | _         |

| I/O data bus high Z<br>to data on bus | TIODHZDL            |                                                                                                    |                   |                | 100            |          | _         |

| I/O *RD low to data<br>stable         | TRLDS               |                                                                                                    |                   |                |                | 80       | _         |

| I/O *RD high to data<br>bus in low Z  | RHIODLZ             |                                                                                                    |                   |                | 50             |          |           |

| Output impedence                      | R <sub>OUT</sub>    | When transmitting                                                                                  | 4, 5, 6           | 04             |                | 10       | Ω         |

| Rise time                             | t <sub>r</sub>      | 10% to 90%                                                                                         | 9, 10,11          | 04             | 220            | 300      | ns        |

| Fall time                             | <br> t <sub>f</sub> | 90% to 10%                                                                                         | 9, 10,11          | 04             | ]<br>  220<br> | 300      | ns        |

| Output harmonic content (referenced   |                     | at 1.5 MHz                                                                                         | 4, 5, 6           | 04             | -3             |          | _  dB     |

| to the average<br>peak value at       |                     | at 2.5 MHz                                                                                         | -                 |                | -13.5          | <u> </u> | -         |

| 1.0 MHz)                              |                     | at 4.0 MHz                                                                                         |                   |                | -25.5          |          | 1         |

<sup>1/</sup> Device types 01 and 02, V<sub>CC</sub> = +4.75 V dc to +5.50 V dc unless otherwise specified.

Device types 03, 04, 05, and 06, V<sub>CC</sub> = +4.50 V dc to +5.50 V dc unless otherwise specified.

2/ All group A subgroup testing of the same type returned as the performed concurrently.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>9 |

<sup>3/</sup> Measured at pin functions: H\_DATO through H\_DAT15.

<sup>4/</sup> Measured at pin functions: I/O\_DATO through I/O\_DAT7, I/O\_ADR1, I/O\_ADR2. 5/ Measured at pin functions: DSC\_INTPO\_L.

<sup>6/</sup> Measured at pin functions: PLSCMD, I/O\_RD, I/O\_WR, CMDS, MDCDRST. 7/ Measured at pin functions: IRQ\_L, DTACK\_L.

FIGURE 1. Case outline(s).

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>10 |

# Case outline Z (Device types 03 and 04)

| Inches | mm   | Inches | mm    |

|--------|------|--------|-------|

| .002   | 0.05 | .080   | 2.03  |

| .005   | 0.13 | .100   | 2.54  |

| .010   | 0.25 | .120   | 3.05  |

| .012   | 0.30 | .800   | 20.32 |

| .018   | 0.46 | 1.000  | 25.40 |

| .050   | 1.27 | 1.100  | 27.94 |

### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- Unless otherwise specified, tolerance is ±.005 (0.13 mm) for three place decimals and ±.01 (0.3 mm) for two place decimals.

FIGURE 1. <u>Case outline(s)</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>13 |

| Device<br>types    | 03 an              | d 04 | Device<br>types    | 03 an              | d 04 |

|--------------------|--------------------|------|--------------------|--------------------|------|

| Case<br>outline    | U                  |      | Case<br>outline    | U                  |      |

| Terminal<br>number | Terminal<br>symbol | Туре | Terminal<br>number | Terminal<br>symbol | Туре |

| 1                  | 1/0_DAT1           | 1/0  | 21                 | CMDS               | 0    |

| 2                  | 1/0_DAT2           | 1/0  | 22                 | TXINH_B            | 0    |

| 3                  | I/O_DAT3           | 1/0  | 23                 | BUS_B              | 0    |

| 4                  | 1/0_DAT4           | 1/0  | 24                 | BUS_B              | 0    |

| 5                  | I/O_DAT5           | 1/0  | 25                 | NC                 |      |

| 6                  | 1/0_DAT6           | 1/0  | 26                 | I/O_RD             | 0    |

| 7                  | I/O_DAT7           | 1/0  | 27                 | I/O_WR             | o    |

| 8                  | HCS                | I    | 28                 | MDCDRST            | 0    |

| 9                  | SSF_TF             | I    | 29                 | PLSCMD             | 0    |

| 10                 | RST                | I    | 30                 | ĪRQ                | 0    |

| 11                 | CLK10              | ī    | 31                 | DTACK              | 0    |

| 12                 | I/O_ADR1           | 0    | 32                 | H_DAT12            | 1/0  |

| 13                 | I/O_ADR2           | o    | 33                 | H_ADR2             | I    |

| 14                 | INTPO_DSC          | o    | 34                 | H_ADR3             | I    |

| 15                 | INTPI              | I    | 35                 | H_ADR4             | I    |

| 16                 | INTACK             | I    | 36                 | H_ADR5             | I    |

| 17                 | TXINH_A            | I    | 37                 | H_ADR6             | I    |

| 18                 | BUS_A              | I    | 38                 | H_ADR7             | I    |

| 19                 | BUS_A              | I    | 39                 | +5 V               | I    |

| 20                 | NC NC              |      |                    | +5 V               | I    |

FIGURE 2. <u>Terminal connections</u>.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>14 |

| Device<br>types    | 03 ar              | nd 04 | Device<br>types      | 03 ar              | nd 04 |

|--------------------|--------------------|-------|----------------------|--------------------|-------|

| Case<br>outline    | L                  | J     | Case<br>outline      | l                  | j     |

| Terminal<br>number | Terminal<br>symbol | Туре  | Terminal<br>  number | Terminal<br>symbol | Туре  |

| 41                 | GND                |       | 55                   | H_DAT6             | 1/0   |

| 42                 | GND                |       | 56                   | H_DAT7             | 1/0   |

| 43                 | GND                |       | 57                   | H_DAT8             | 1/0   |

| 44                 | H_ADR8             | 1     | 58                   | H_DAT9             | 1/0   |

| 45                 | H_ADR9             | I     | 59                   | H_DAT10            | 1/0   |

| 46                 | H_ADR10            | 1     | 60                   | H_DAT11            | 1/0   |

| 47                 | H_ADR11            | I     | 61                   | H_ADR1             | 1/0   |

| 48                 | H_ADR12            | I     | 62                   | HRD                | I     |

| 49                 | H_DATO             | 1/0   | 63                   | HWRL               | I     |

| 50                 | H_DAT1             | 1/0   | 64                   | HWRH               | I     |

| 51                 | H_DAT2             | 1/0   | 65                   | H_DAT13            | 1/0   |

| 52                 | H_DAT3             | 1/0   | 66                   | H_DAT14            | 1/0   |

| 53                 | H_DAT4             | 1/0   | 67                   | H_DAT15            | 1/0   |

| 54                 | H_DAT5             | 1/0   | 68                   | I/O_DATO           | 1/0   |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-91687  |

|------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>15 |

| Device<br>types    | 01, 02, 05      | , and 06 | Device<br>types    | 01, 02, 05,        | and 06 |

|--------------------|-----------------|----------|--------------------|--------------------|--------|

| Case<br>outlines   | X an            | d Y      | Case<br>outlines   | X and Y            |        |

| Terminal<br>number | Terminal symbol | Туре     | Terminal<br>number | Terminal<br>symbol | Туре   |

| 1                  | TXINH_A         | 1        | 21                 | H_DAT6             | 1/0    |

| 2                  | +5 V            | I        | 22                 | H_DAT7             | 1/0    |

| 3                  | H_ADR1          | I        | 23                 | H_DAT8             | 1/0    |

| 4                  | H_ADR2          | I        | 24                 | H_DAT9             | 1/0    |

| 5                  | H_ADR3          | I        | 25                 | H_DAT10            | 1/0    |

| 6                  | H_ADR4          | I        | 26                 | H_DAT11            | 1/0    |

| 7                  | H_ADR5          | I        | 27                 | H_DAT12            | 1/0    |

| 8                  | H_ADR6          | I        | 28                 | H_DAT13            | 1/0    |

| 9                  | H_ADR7          | I        | 29                 | H_DAT14            | 1/0    |

| 10                 | H_ADR8          | I        | 30                 | H_DAT15            | 1/0    |

| 11                 | H_ADR9          | I        | 31                 | HWRH               | I      |

| 12                 | H_ADR10         | I        | 32                 | +5 V               | I      |

| 13                 | H_ADR11         | I        | 33                 | тхімн_в            | I      |

| 14                 | H_ADR12         | I        | 34                 | BUS_B              | 1/0    |

| 15                 | H_DATO          | 1/0      | 35                 | BUS_B              | 1/0    |

| 16                 | H_DAT1          | 1/0      | 36                 | GND                |        |

| 17                 | H_DAT2          | 1/0      | 37                 | I/O_DATO           | 1/0    |

| 18                 | H_DAT3          | 1/0      | 38                 | I/O_DAT1           | 1/0    |

| 19                 | H_DAT4          | 1/0      | 39                 | I/O_DAT2           | 1/0    |

| 20                 | H DAT5          | 1/0      | 40                 | I/O DAT3           | 1/0    |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>16 |

| Device<br>types    | 01, 02, 05         | 5, and 06 | Device<br>types    | 01, 02, 0          | 5, and 06 |

|--------------------|--------------------|-----------|--------------------|--------------------|-----------|

| Case<br>outlines   | X ar               | nd Y      | Case<br>  outlines | Ха                 | nd Y      |

| Terminal<br>number | Terminal<br>symbol | Type      | Terminal<br>number | Terminal<br>symbol | Туре      |

| 41                 | I/O_DAT4           | 1/0       | 54                 | INTPI              | I         |

| 42                 | I/O_DAT5           | 1/0       | 55                 | INTACK             | I         |

| 43                 | I/O_DAT6           | 1/0       | 56                 | CMDS               | 0         |

| 44                 | I/O_DAT7           | 1/0       | 57                 | PLSCMD             | 0         |

| 45                 | HCS                | 1         | 58                 | HWRL               | I         |

| 46                 | See note           | I         | 59                 | HRD                | I         |

| 47                 | RST                | 1         | 60                 | I/O_RD             | 0         |

| 48                 | CLK10              | 1         | 61                 | I/O_WR             | О         |

| 49                 | I/O_ADR1           | 0         | 62                 | IRQ                | 0         |

| 50                 | I/O_ADR2           | o         | 63                 | DTACK              | 0         |

| 51                 | +5 V               | I         | 64                 | GND                |           |

| 52                 | INTPO_DSC          | 0         | 65                 | BUS_A              | 1/0       |

| 53                 | MDCDRST            | 0         | 66                 | BUS_A              | 1/0       |

Note: Terminal 46, the terminal symbol is +5 V RAM supply for device types 01 and 05, SSF\_TF for device types 02 and 06.

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-91687  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>17 |

| Device<br>types    | 03 an              | d 04 | Device<br>types    | 03 and 04          |        |

|--------------------|--------------------|------|--------------------|--------------------|--------|

| Case<br>outline    | Z                  |      | Case<br>outline    | Z                  |        |

| Terminal<br>number | Terminal<br>symbol | Туре | Terminal<br>number | Terminal<br>symbol | Туре   |

| L10                | I/O_DAT1           | 1/0  | L3                 | CMDS               | o      |

| н10                | 1/0_DAT2           | 1/0  | К4                 | в_ниіхт            | o      |

| J10                | 1/0_DAT3           | 1/0  | к1                 | GND                |        |

| K10                | I/O_DAT4           | 1/0  | н1                 | BUS_B              | o      |

| К9                 | 1/0_DAT5           | 1/0  | <br>   J1          | GND                | 0      |

| L9                 | I/O_DAT6           | I/O  | L4                 | I/O_RD             | 1/0    |

| L8                 | I/O_DAT7           | 1/0  | н2                 | I/O_WR             | 1/0    |

| G11                | HCS                | I    | K2                 | MDCDRST            | 0      |

| н11                | SSF_TF             | I    |                    | PLSCMD             | o      |

| G10                | RST                | I    | <br>    F1         | ĪRQ                | 0      |

| J11                | CLK10              | I    | <br>    E1         | DTACK              | 0      |

| к8                 | I/O_ADR1           | 1/0  | G1                 | H_DAT12            | 1/0    |

| L7                 | I/O_ADR2           | 1/0  | E2                 | H_ADR2             | I      |

| к7                 | INTPO_DSC          | 0    | D1                 | H_ADR3             | I      |

| L6                 | INTPI              | I    | c3                 | NC                 |        |

| К6                 | INTACK             | 1    | <br>   D2          | H_ADR4             | I      |

| J2                 | BUS_B              | I    | [] c1              | H_ADR5             | I      |

| кз                 | NC                 |      | B1                 | H_ADR6             | I      |

| L2                 | NC                 |      | A2                 | H_ADR7             | I      |

| G2                 | TXINH_A            | I    | L5                 | +5 V               | l<br>I |

|                    |                    |      | <br>   K5          | +5 V               | I      |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>18 |

| Device<br>types    | 03 and 04          |          | Device<br>types   | 03 ar              | nd 04    |

|--------------------|--------------------|----------|-------------------|--------------------|----------|

| Case<br>outline    | 7                  | <u> </u> | Case<br>  outline | 7                  | <u> </u> |

| Terminal<br>number | Terminal<br>symbol | Туре     | Terminal          | Terminal<br>symbol | Туре     |

| B2                 | GND                |          | A10               | H_DAT6             | 1/0      |

| в3                 | BUS_A              | I        | В8                | H_DAT7             | 1/0      |

| c2                 | BUS_A              | 1        | В9                | H_DAT8             | 1/0      |

| A3                 | H_ADR8             | I        | B10               | H_DAT9             | 1/0      |

| B4                 | H_ADR9             | 1        | B11               | H_DAT10            | 1/0      |

| A4                 | H_ADR10            | I        | [] c11            | H_DAT11            | 1/0      |

| B5                 | H_ADR11            | 1        | c10               | H_ADR1             | 1/0      |

| A5                 | H_ADR12            | I        | D11               | HRD                | I        |

| В6                 | H_DATO             | 1/0      | E11               | HWRL               | I        |

| <b>A</b> 6         | H_DAT1             | 1/0      | F11               | HWRH               | I        |

| A7                 | H_DAT2             | 1/0      | D10               | H_DAT13            | 1/0      |

| В7                 | H_DAT3             | 1/0      | E10               | H_DAT14            | 1/0      |

| A8                 | H_DAT4             | 1/0      | F10               | H_DAT15            | 1/0      |

| A9                 | H_DAT5             | 1/0      | К11               | I/O_DATO           | 1/0      |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>19 |

#### NOTES:

(Notes 1 through 9 describe the HMBRT signal responses to messages on the address, data, and control lines.)

- The address is latched by the HMBRT on the high-to-low transition of the HCS line. TADS, TADH, and TASLC are referenced to the high-to-low transition of HCS.

- 2. TACK is a function of the contending access performed by the HMBRT (see table I).

- 3. The low-to-high transition of HRD or I/O\_RD terminates the read cycle.

- 4. The DTACK line is three stated after delay "TACKH". It is the rise time, a function of the internal 5 kohm pull-up resistor and external load.

- 5. While INTACK is low, INTPO will be affected by changes in IRQ.

- 6. In order to support edge triggered interrupt requests, IRQ is returned high "TINAIRQH" nanoseconds after ITACK goes low. If the HMBT is not empty, IRQ will go low "TINAIRQL" nanoseconds after INTACK returns high.

- 7. After INTACK goes low, the HMBRT waits "TPR" nanoseconds to allow for the propagation of INTPO and INTPI through the daisy chain.

- The minimum propagation time "TPR" through the daisy chain can be extended by delaying the HRD signal by any amount "TPRE".

- 9. If HRD falling edge occurs less than "TPR" nanoseconds after INTACK, INTACK starts "TPR" nanoseconds after ITACK, otherwise ITACK starts after the falling edge of HRD.

- 10. Status response is delayed by MBRT for MRSP = 6.5 microseconds.

- 11. <u>Int</u>ernal interrupt request pulse will enter the FIFO immediately if associated level is not masked and IRQ signal will be activated if IRE bit is set in the control word.

- 12. The exact timing command write and  $\overline{\text{IRQ}}$  activation depends on a host bus activity.

### FIGURE 4. Timing diagrams - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>35 |

TABLE II. <u>Electrical test requirements</u>.

| MIL-H-38534 test requirements                                              | Subgroups (in accordance with MIL-H-38534, group A test table)    |

|----------------------------------------------------------------------------|-------------------------------------------------------------------|

| Interim electrical parameters                                              | 1,2,3,4,5,6,9,10,11                                               |

| Final electrical test parameters                                           | 1*,2,3,4,5,6,9,10,11                                              |

| Group A test requirements                                                  | 1,2,3,4,5,6,9,10,11                                               |

| Group C end-point electrical parameters                                    | 1,2,3,4,5,6,9,10,11                                               |

| MIL-STD-883, group E end-point<br>electrical parameters for RHA<br>devices | Subgroups ** (in accordance with method 5005, group A test table) |

- \* PDA applies to subgroup 1.

- \*\* When applicable to this standardized military drawing, the subgroups shall be defined.

- 4.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with MIL-H-38534 and as specified herein.

- 4.3.1 Group A inspection. Group A inspection shall be in accordance with MIL-H-38534 and as follows:

- a. Tests shall be as specified in table II herein.

- b. Subgroups 7 and 8 shall be omitted.

- c. Input capacitance shall be measured only for the initial test and after process or design changes which may affect input capacitance.

- 4.3.2 Group B inspection. Group B inspection shall be in accordance with MIL-H-38534.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-91687  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>36 |

- 4.3.3 Group C inspection. Group C inspection shall be in accordance with MIL-H-38534 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test, method 1005 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DESC-EC or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- (2)  $T_{\Delta}$  as specified in accordance with table I of method 1005 of MIL-STD-883.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- 4.3.4 Group D inspection. Group D inspection shall be in accordance with MIL-H-38534.

- 4.3.5 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes H and K shall be M, D, R, and H. RHA quality conformance inspection sample tests shall be performed at the RHA level specified in the acquisition document.

- a. RHA tests for device classes H and K for levels M, D, R, and H shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- b. End-point electrical parameters shall be as specified in table II herein.

- c. Prior to total dose irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table II herein.

- d. For device classes H and K, the devices shall be subjected to radiation hardness assured tests as specified in MIL-H-38534 for RHA level being tested, and meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A$  = +25°C ±5 percent, after exposure.

- e. Prior to and during total dose irradiation testing, the devices shall be biased to establish a worst case condition as specified in the radiation exposure circuit.

- f. For device classes H and K, subgroups 1 and 2 in table V, method 5005 of MIL-STD-883 shall be tested as appropriate for device construction.

- g. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-H-38534.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>37 |

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.5 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444, or telephone (513) 296-5373.

- 6.6 One part one part number system. The one part one part number system described below has been developed to allow for transitions between identical generic devices covered by the three major microcircuit requirements documents (MIL-H-38534, MIL-I-38535, and 1.2.1 of MIL-STD-883) without the necessity for the generation of unique PIN's. The three military requirements documents represent different class levels, and previously when a device manufacturer upgraded military product from one class level to another, the benefits of the upgraded product were unavailable to the Original Equipment Manufacturer (OEM), that was contractually locked into the original unique PIN. By establishing a one part number system covering all three documents, the OEM can acquire to the highest class level available for a given generic device to meet system needs without modifying the original contract parts selection criteria.

| Military documentation format                              | Example PIN under new system | Manufacturing source listing | Document<br><u>listing</u> |

|------------------------------------------------------------|------------------------------|------------------------------|----------------------------|

| New MIL-H-38534 Standardized Military<br>Drawings          | 5962-XXXXXZZ(H or K)YY       | QML-38534                    | MIL-BUL-103                |

| New MIL-I-38535 Standardized Military<br>Drawings          | 5962-XXXXXZZ(Q or V)YY       | QML-38535                    | MIL-BUL-103                |

| New 1.2.1 of MIL-STD-883 Standardized<br>Military Drawings | 5962-XXXXXZZ(M)YY            | MIL-BUL-103                  | MIL-BUL-103                |

- 6.7 <u>Sources of supply for device classes H and K</u>. Sources of supply for device classes H and K are listed in QML-38534. The vendors listed in QML-38534 have submitted a certificate of compliance (see 3.7 herein) to DESC-EC and have agreed to this drawing.

- 6.8 Pin functions. Microcircuit conforming to this drawing shall have pin functions as specified in table III herein.

TABLE III. Pin functions.

| Terminal<br>symbol | 1/0 | Description                                               |

|--------------------|-----|-----------------------------------------------------------|

| A_HMIXT            | I   | Bus A inhibit. This signal inhibits the bus A transmitter |

| +5 <b>V</b>        | I   | +5 volt power supply connections (3 pins)                 |

| H_ADR1             | I   | Host address bus bit 1.                                   |

| H_ADR2             | 1   | Host address bus bit 2.                                   |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>38 |

TABLE III. Pin functions - Continued.

| Terminal<br>symbol | 1/0 | Description              |

|--------------------|-----|--------------------------|

| H_ADR3             | I   | Host address bus bit 3.  |

| H_ADR4             | I   | Host address bus bit 4.  |

| H_ADR5             | I   | Host address bus bit 5.  |

| H_ADR6             | I   | Host address bus bit 6.  |

| H_ADR7             | I   | Host address bus bit 7.  |

| H_ADR8             | I   | Host address bus bit 8.  |

| H_ADR9             | I   | Host address bus bit 9.  |

| H_ADR10            | I   | Host address bus bit 10. |

| H_ADR11            | I   | Host address bus bit 11. |

| H_ADR12            | I   | Host address bus bit 12. |

| H_DATO             | 1/0 | Host data bus bit O.     |

| H_DAT1             | 1/0 | Host data bus bit 1.     |

| H_DAT2             | 1/0 | Host data bus bit 2.     |

| H_DAT3             | 1/0 | Host data bus bit 3.     |

| H_DAT4             | 1/0 | Host data bus bit 4.     |

| H_DAT5             | 1/0 | Host data bus bit 5.     |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON OHIO 45444 | SIZE<br>A |                     | 5962-91687  |

|-----------------------------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                                                |           | REVISION LEVEL<br>A | SHEET<br>39 |

TABLE III. <u>Pin functions</u> - Continued.

| Terminal<br>symbol | 1/0 | Description                                               |

|--------------------|-----|-----------------------------------------------------------|

| H_DAT6             | 1/0 | Host data bus bit 6.                                      |

| H_DAT7             | 1/0 | Host data bus bit 7.                                      |

| H_DAT8             | 1/0 | Host data bus bit 8.                                      |

| H_DAT9             | 1/0 | Host data bus bit 9.                                      |

| H_DAT10            | 1/0 | Host data bus bit 10.                                     |

| H_DAT11            | 1/0 | Host data bus bit 11.                                     |

| H_DAT12            | 1/0 | Host data bus bit 12.                                     |

| H_DAT13            | 1/0 | Host data bus bit 13.                                     |

| H_DAT14            | 1/0 | Host data bus bit 14.                                     |

| H_DAT15            | 1/0 | Host data bus bit 15.                                     |

| HWRH               | I   | Host write higher byte (active low).                      |

| +5 V               | I   | +5 volt power supply connections (3 pins)                 |

| TXINH_B            | 1/0 | Bus B inhibit. This signal inhibits the bus B transmitter |

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-91687  |

|------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>40 |

TABLE III. <u>Pin functions</u> - Continued.