|                                                                                                                                        |                                                                                   |       |          |     |                  |                | -               | R    | EVISI | ONS  |          |      |       |        |          |                |      |      | -   |    |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|----------|-----|------------------|----------------|-----------------|------|-------|------|----------|------|-------|--------|----------|----------------|------|------|-----|----|

| LTR                                                                                                                                    | DESCRIPTION                                                                       |       |          |     |                  |                |                 |      |       |      |          | DA   | TE (Y | R-MO-D | (A)      |                | APPR | OVED |     |    |

| A                                                                                                                                      | Make change to 1.2.4. In accordance N.O.R. 5962-R086-96.                          |       |          |     |                  |                |                 | wit  | h     |      |          | 96-0 | 3-20  |        | 1        | M.A.           | FRYI | 2    |     |    |

| В                                                                                                                                      | Add device class N. Add case outline Y. Ma editorial changes throughout. Redrawn. |       |          |     |                  |                |                 | Ма   | ke.   | ,    | 96-0     | 8-16 |       | ]      | R. MO    | INNC           | 1    |      |     |    |

|                                                                                                                                        |                                                                                   |       |          |     |                  |                |                 |      |       |      |          | •    |       |        |          |                |      |      |     |    |

| REV                                                                                                                                    | T                                                                                 | !     | <u> </u> | ľ   | <u> </u>         |                |                 |      |       |      |          |      |       |        |          |                |      |      |     |    |

| SHEET                                                                                                                                  |                                                                                   |       |          |     |                  |                |                 |      |       |      |          |      |       |        |          |                |      |      |     |    |

| REV                                                                                                                                    | В                                                                                 | В     | В        | В   | В                | В              | В               | В    | В     | В    | В        | В    | В     |        |          |                |      |      |     |    |

| SHEET                                                                                                                                  | 15                                                                                | 16    | 17       | 18  | 19               | 20             | 21              | 22   | 23    | 24   | 25       | 26   | 27    |        |          |                |      |      |     |    |

| REV STATU                                                                                                                              |                                                                                   |       |          | RE  | V                |                | В               | В    | В     | В    | В        | В    | В     | В      | В        | В              | В    | В    | В   | В  |

| OF STILLING                                                                                                                            | ,                                                                                 |       |          | SH  | EET              | -              | 1               | 2    | 3     | 4    | 5        | 6    | 7     | 8      | 9        | 10             | 11   | 12   | 13  | 14 |

| PMIC N/A                                                                                                                               |                                                                                   |       |          |     | PAREI<br>CK OF   | D BY<br>FICER  |                 |      |       |      | !        | DEFE |       |        |          | NTER<br>110 4: |      | MBUS | 6   |    |

| STA<br>MICRO                                                                                                                           | OCIR                                                                              | CUI   | Т        |     | CKED<br>RAJESI   | BY<br>I PITH   | ADIA            |      |       |      |          |      |       |        |          |                |      |      |     |    |

| DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL  APPROVED BY MICHAEL FRYE  MICROCIRCUIT, LINEAR, 175 MHZ INTERFACE PALETTE, MONOLITH |                                                                                   |       |          |     | , 64-B<br>IC SIL | IT, VI<br>ICON | DEO<br>I        |      |       |      |          |      |       |        |          |                |      |      |     |    |

| DEPA<br>AND AGE<br>DEPARTME                                                                                                            |                                                                                   | OF TH |          | DRA | WING             |                | OVAL I<br>01-12 | DATE |       | SIZE | _        |      | E COI |        |          | 59             | 962  | -967 | 758 |    |

| AMS                                                                                                                                    | N/A                                                                               |       |          | REV | /ISION           | LEVE           | -               |      |       |      | <u> </u> | 6    | 726   | 8      | <u> </u> |                |      |      |     |    |

|                                                                                                                                        |                                                                                   |       |          |     | E                | 3              |                 |      |       | SHE  | EET      | 1    | *     | OF     | 2        | 27             |      |      |     |    |

9004708 0024100 958 📟

DESC FORM 193

JUL 94

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-È497-96

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents three product assurance class levels consisting of high reliability (device classes Q and M), space application (device class V) and nontraditional performance environment (device class N). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN. For device class N, the user is cautioned to assure that the device is appropriate for the application environment.

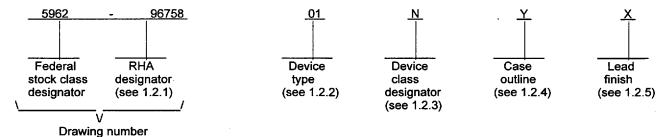

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device classes N, Q, and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function                         |

|-------------|----------------|------------------------------------------|

| 01          | TVP3026        | 175 MHz, 64-bit, video interface palette |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class | Device requirements documentation                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| М            | Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A |

| N            | Certification and qualification to MIL-PRF-38535 with a non traditional performance environment $\underline{1}$ /                                         |

| Q or V       | Certification and qualification to MIL-PRF-38535                                                                                                          |

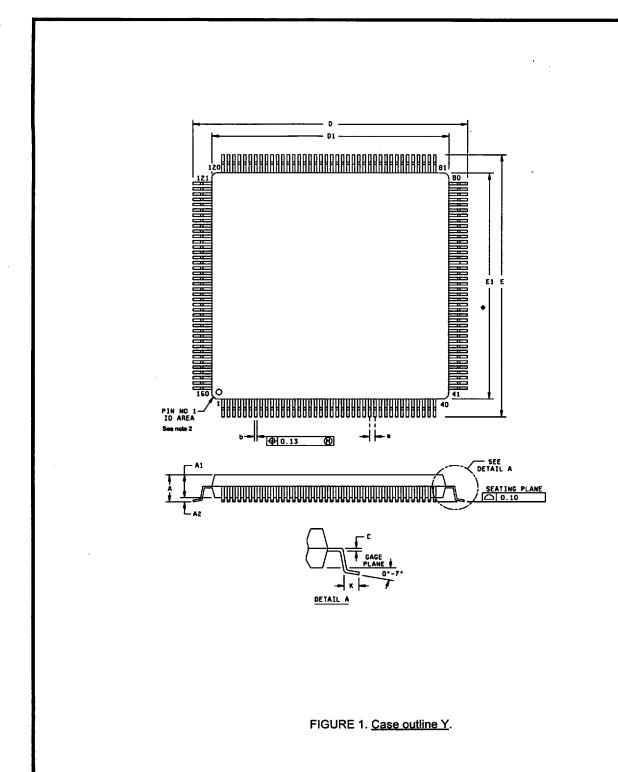

1.2.4 Case outline(s). The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                                         |

|----------------|------------------------|------------------|-------------------------------------------------------|

| X              | CQCC2-F164             | 164              | Quad ceramic flat pack with<br>non-conductive tie bar |

| Y              | See figure 1           | 160              | Plastic quad flat pack                                |

1/ Any device outside the traditional performance environment; e.g., an operating temperature range of -55°C to +125°C and which requires hermetic packaging.

| STANDARD<br>MICROCIRCUIT DRAWING                         | SIZE<br><b>A</b> |                     | 5962-96758 |

|----------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 2    |

DESC FORM 193A JUL 94

9004708 0024101 894

| 1.2.5 <u>Lead finish</u> . The lead finish is as specified in MIL-PRF-38535 for device class appendix A for device class M.                                                                                                                                                         | ses N, Q, and V or MIL-PRF-38535,                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.3 Absolute maximum ratings. 1/ 2/ 3/                                                                                                                                                                                                                                              |                                                    |

| Supply voltage range (V <sub>DD</sub> )                                                                                                                                                                                                                                             | +7.0 V dc                                          |

| DC input voltage range (V <sub>IN</sub> )                                                                                                                                                                                                                                           | -0.5 V dc to V <sub>DD</sub> + 0.5 V dc <u>4</u> / |

| Analog output short-circuit duration to any power supply or common ground                                                                                                                                                                                                           | Unlimited                                          |

| Storage temperature range (T <sub>STG</sub> )                                                                                                                                                                                                                                       |                                                    |

| Junction temperature (T <sub>J</sub> )                                                                                                                                                                                                                                              | +175°C                                             |

| Case temperature for 10 seconds (HFG package)                                                                                                                                                                                                                                       | +260°C                                             |

| Lead temperature (1.6 mm (1/16 inch) from case for 10 seconds)                                                                                                                                                                                                                      |                                                    |

| Thermal resistance, junction to case $(\Theta_{1C})$ :                                                                                                                                                                                                                              |                                                    |

| Case outline X                                                                                                                                                                                                                                                                      |                                                    |

| Case outline Y                                                                                                                                                                                                                                                                      | 10.3°C/W                                           |

| Thermal resistance, junction to ambient ( $\Theta_{JA}$ ):                                                                                                                                                                                                                          |                                                    |

| Case outline X                                                                                                                                                                                                                                                                      | 36° C/W                                            |

| Case outline Y                                                                                                                                                                                                                                                                      | 41.4°C/VV                                          |

| 1.4 Recommended operating conditions. 2/ 3/                                                                                                                                                                                                                                         |                                                    |

| Supply voltage range (AV <sub>DD</sub> , DV <sub>DD</sub> )                                                                                                                                                                                                                         | +4.75 V dc to +5.25 V dc                           |

| Reference voltage,(V <sub>REF</sub> )                                                                                                                                                                                                                                               | +1.1 V dc to +1.3 V dc                             |

| High level input voltage range (V <sub>IH</sub> )                                                                                                                                                                                                                                   | +2.4 V dc to VDD + 0.5 V dc                        |

| Maximum low level input voltage (V <sub>IL</sub> )                                                                                                                                                                                                                                  | +0.8 V                                             |

| Ambient operating free-air temperature (T <sub>A</sub> )                                                                                                                                                                                                                            | -55°C to +125°C                                    |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                                                                                             |                                                    |

| 2.1 <u>Government specification, standards, and handbooks</u> . The following specificat part of this drawing to the extent specified herein. Unless otherwise specified, the iss the issue of the Department of Defense Index of Specifications and Standards (DoDIS solicitation. | ues of these documents are those listed in         |

| SPECIFICATION                                                                                                                                                                                                                                                                       |                                                    |

| MILITARY                                                                                                                                                                                                                                                                            |                                                    |

| MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification                                                                                                                                                                                                           | for.                                               |

|                                                                                                                                                                                                                                                                                     |                                                    |

|                                                                                                                                                                                                                                                                                     |                                                    |

|                                                                                                                                                                                                                                                                                     |                                                    |

|                                                                                                                                                                                                                                                                                     |                                                    |

| 1/ Stresses above the absolute maximum rating may cause permanent damage to t                                                                                                                                                                                                       | he device. Extended operation at the               |

| maximum levels may degrade performance and affect reliability.                                                                                                                                                                                                                      | 151156. Enterided operation at the                 |

| <ul> <li>Unless otherwise noted, all voltages are referenced to GND.</li> <li>The limits for the parameters specified herein shall apply over the full specified V</li> </ul>                                                                                                       | nange and ambient temperature range                |

| 3/ The limits for the parameters specified herein shall apply over the full specified v of -55°C to +125°C. Unused inputs must be held high or low.                                                                                                                                 | DD range and ambient temperature range             |

| 4/ The input populity voltage rating may be exceeded provided that the input clamp                                                                                                                                                                                                  | current rating is observed                         |

4/ The input negative voltage rating may be exceeded provided that the input clamp current rating is observed.

| STANDARD<br>MICROCIRCUIT DRAWING                         | SIZE<br><b>A</b> |                     | 5962-96758 |

|----------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET<br>3 |

#### **STANDARDS**

### **MILITARY**

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines.

#### **HANDBOOKS**

#### **MILITARY**

MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's).

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements for device classes N, Q, and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes N, Q, and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.2.3 <u>Truth table(s)</u>. The truth table(s) shall be as specified on figure 3.

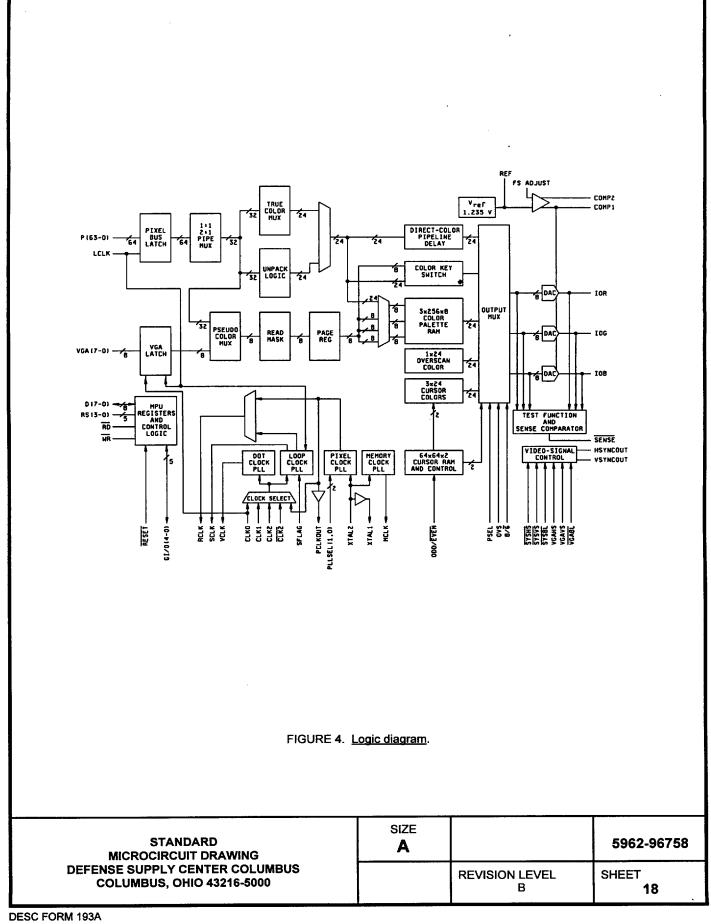

- 3.2.4 Logic diagram(s). The logic diagram(s) shall be as specified on figure 4.

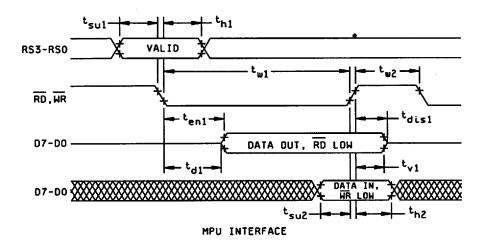

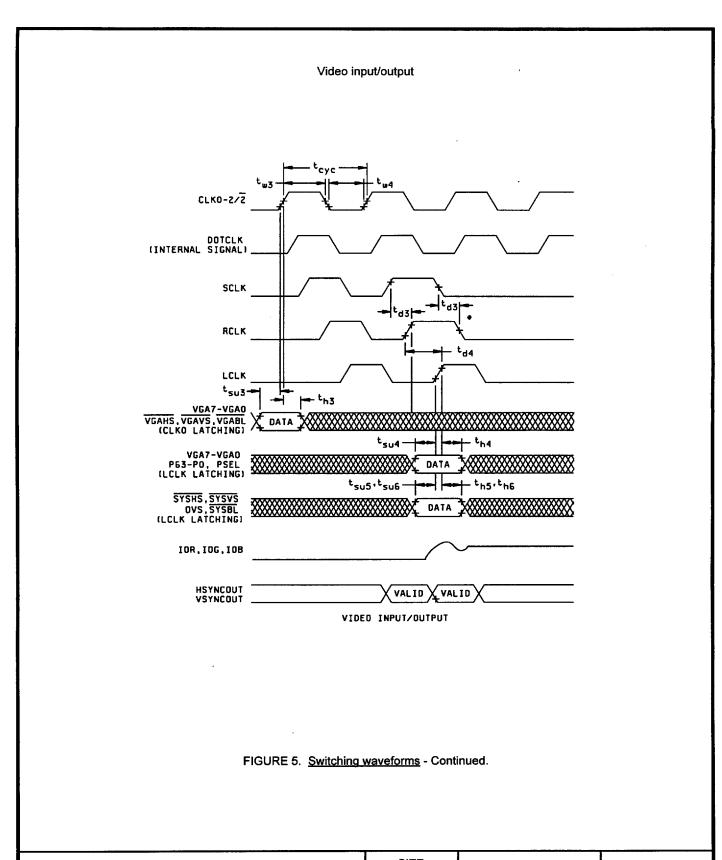

- 3.2.5 Switching waveform(s). The switching waveform(s) shall be as specified on figure 5.

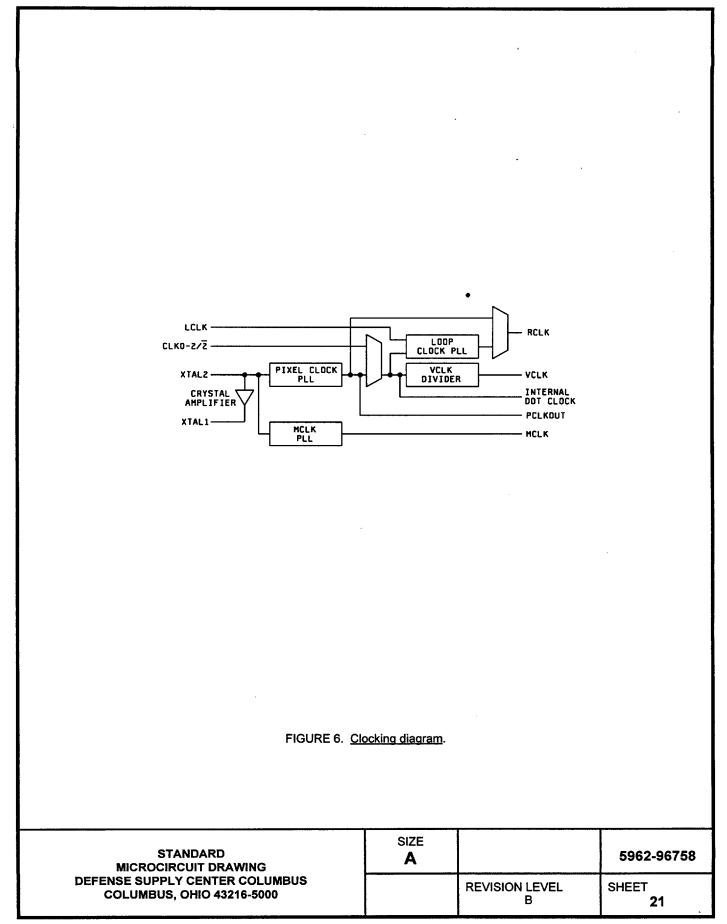

- 3.2.6 Clock diagram. The clock diagram shall be as specified on figure 6.

- 3.3 Electrical performance characteristics and postirradiation parameter limits. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full ambient operating temperature range.

- 3.4 Electrical test requirements. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-96758 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 4    |

- 3.5 Marking. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes N, Q, and V shall be in accordance with MIL-PRF-38535. For class N devices only, the date code format may be modified as a traceable date code in lieu of the inspection lot date code for case outline Y.

- 3.5.1 Certification/compliance mark. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes N, Q, and V shall be a "QML" or "Q" as required in MIL-PRF-38535.

- 3.6 Certificate of compliance. For device classes N, Q, and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes N, Q, and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 Certificate of conformance. A certificate of conformance as required for device classes N. Q. and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change for device class M. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 Verification and review for device class M. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 Microcircuit group assignment for device class M. Device class M devices covered by this drawing shall be in microcircuit group number 110 (see MIL-PRF-38535, appendix A).

### 4. QUALITY ASSURANCE PROVISIONS

4.1 Sampling and inspection. For device classes N, Q, and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. For device class M, sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

SIZE **STANDARD** 5962-96758 Α MICROCIRCUIT DRAWING **DEFENSE SUPPLY CENTER COLUMBUS REVISION LEVEL** SHEET **COLUMBUS, OHIO 43216-5000**

5

| Test and <u>1</u> /<br>MIL-STD-883       | Symbol          | To<br>-55                                              | est conditions<br>°C ≤ T <sub>Δ</sub> ≤ +1.                            | s <u>2</u> /<br>25°C       | v <sub>cc</sub>        | Group A subgroups | Lir  | Limits                   |            |

|------------------------------------------|-----------------|--------------------------------------------------------|------------------------------------------------------------------------|----------------------------|------------------------|-------------------|------|--------------------------|------------|

| test method                              |                 | +4.75<br>unles                                         | °C ≤ T <sub>A</sub> ≤ +1<br>5 V ≤ V <sub>DD</sub> ≤ +<br>s otherwise s | -5.25 V<br>pecified        | <u>3</u> / M           |                   | Min  | Max                      |            |

| High level output<br>voltage<br>3006     | V <sub>OH</sub> | For all inputs<br>test, I <sub>OH</sub> = -8           | affecting outp<br>00 μΑ                                                | ut under                   | 4.75 V<br>to<br>5.25 V | 1,2,3             | 2.4  |                          | V          |

| Low level output<br>voltage<br>3007      | V <sub>OL</sub> | affecting PCLKOUT, MCLK, I <sub>OL</sub> output 3.2 mA |                                                                        | NSE,                       | 4.75 V<br>to<br>5.25 V | 1,2,3             |      | 0.4                      | ٧          |

|                                          |                 | under test                                             | HSYNCOL                                                                | UT,VSYNCOUT<br>nA          |                        |                   |      | 0.4                      |            |

|                                          |                 |                                                        | SCLK, IOI                                                              | = 18 mA                    |                        |                   |      | 0.5                      |            |

| Input current high                       | I <sub>IH</sub> | For input                                              | TTL inputs                                                             | s, V <sub>IN</sub> = 2.4 V | 4.75 V                 | 1,2,3             |      | 10                       | μA         |

| 3010                                     |                 | under test                                             | ECL input                                                              | s, V <sub>IN</sub> = 4.0 V | to<br>5.25 V           |                   |      | 10                       |            |

| Input current low                        | I <sub>IL</sub> | For input                                              | TTL inputs                                                             | s, V <sub>IN</sub> = 0.8 V | 4.75 V                 | 1,2,3             |      | -10                      | μA         |

| 3009                                     |                 | under test                                             | ECL input                                                              | s, V <sub>IN</sub> = 0.4 V | to<br>5.25 V           |                   |      | -10                      |            |

| Supply current                           | 1 <sub>DD</sub> | Psuedo                                                 |                                                                        |                            | 4.75 V                 | 1,2,3             |      | 1.0                      | Α          |

|                                          |                 | True color                                             |                                                                        |                            | to<br>5.25 V           |                   |      | 1.0                      |            |

|                                          |                 | Direct                                                 |                                                                        |                            |                        |                   |      | 1.0                      |            |

| High impedance-state output current 3021 | loz             |                                                        |                                                                        |                            | 4.75 V<br>to<br>5.25 V | 1,2,3             |      | 25                       | μA         |

| Differential input<br>voltage            | V <sub>ID</sub> | ECL inputs                                             |                                                                        |                            | 4.75 V<br>to<br>5.25 V | 1,2,3             | 0.6  | 6.0                      | ٧          |

| Common-mode input voltage                | V <sub>IC</sub> | ECL inputs                                             |                                                                        |                            | 4.75 V<br>to<br>5.25 V | 1,2,3             | 2.85 | V <sub>DD</sub><br>- 0.5 | \<br> <br> |

| End-point linearity                      | EL              | 8/6 high                                               |                                                                        |                            | 4.75 V                 | 1,2,3             |      | 1                        | LS         |

| error (each DAC)                         |                 | 8/6 low                                                | · · · · · · · · · · · · · · · · · · ·                                  |                            | to<br>5.25 V           |                   |      | 0.25                     |            |

| Differential linearity                   | E <sub>D</sub>  | 8/6 high                                               |                                                                        |                            | 4.75 V                 | 1,2,3             |      | 1                        | LS         |

| error (each DAC)                         |                 | 8/6 low                                                |                                                                        |                            | to<br>5.25 V           |                   |      | 0.25                     |            |

| Gray scale error                         | GSE             |                                                        |                                                                        |                            | 4.75 V<br>to<br>5.25 V | 1,2,3             |      | 5                        | %          |

| See footnotes at end of t                | able.           |                                                        |                                                                        |                            |                        |                   |      |                          |            |

|                                          | STANDAR         |                                                        |                                                                        | SIZE<br><b>A</b>           |                        |                   | 5    | 5962-96                  | 758        |

| DEFENSE SUF                              |                 |                                                        | JS                                                                     |                            | REVISION               | ON LEVEL<br>B     | SH   | EET 6                    |            |

|                                                                       | T                    | ABLE I. <u>Electrical performan</u>                                                                 | ce characteristic | <u>s</u> - Continu           | ed.        |             |         |      |

|-----------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|-------------------|------------------------------|------------|-------------|---------|------|

| Test and 1/<br>MIL-STD-883<br>test method                             | Symbol               | Test condition<br>-55° C ≤ T <sub>A</sub> ≤ +1<br>+4.75 V ≤ V <sub>DD</sub> ≤<br>unless otherwise s | V <sub>DD</sub>   | Group A subgroups <u>3</u> / | Lim<br>Min | nits<br>Max | Unit    |      |

| Output current 4/                                                     | lout                 | White level relative to blan                                                                        |                   | 4.75 V                       | 1,2,3      | 17.69       | 20.4    | mA   |

|                                                                       |                      | White level relative to black<br>(7.5 IRE only)                                                     | ķ                 | to<br>5.25 V                 |            | 16.74       | 18.5    | mA   |

|                                                                       |                      | Black level relative to blant<br>(7.5 IRE only)                                                     | (                 |                              |            | 0.95        | 1.9     | mA   |

|                                                                       |                      | Blank level on IOR, IOB                                                                             |                   |                              |            | -50         | 50      | μΑ   |

|                                                                       |                      | Blank level on IOG (with S                                                                          | YNC enabled)      |                              | -          | 6.29        | 8.96    | mA   |

|                                                                       |                      | Sync level on IOG (with S)                                                                          | 'NC enabled)      |                              |            | -50         | 50      | μΑ   |

| DAC-to-DAC matching                                                   | DDM                  |                                                                                                     |                   | 4.75 V<br>• to<br>5.25 V     | 1,2,3      |             | 5       | %    |

| Output compliance voltage                                             | Voc                  |                                                                                                     |                   | 4.75 V<br>to<br>5.25 V       | 1,2,3      | 0.4         | 1.2     | V    |

| Voltage reference output voltage                                      | V <sub>REFO</sub>    |                                                                                                     |                   | 4.75 V<br>to<br>5.25 V       | 1,2,3      | 1.1         | 3.0     | ٧    |

| Input capacitance                                                     | C <sub>IN</sub>      | See 4.4.1c, TTL inputs<br>f = 1 MHz, V <sub>IN</sub> = 2.4 V                                        | -                 | 4.75 V<br>to                 | 4          |             | 4.0     | pF   |

|                                                                       | i                    | See 4.4.1c, ECL inputs<br>f = 1 MHz, V <sub>IN</sub> = 4 V                                          |                   | 5.25 V                       |            |             | 4.0     |      |

| Output capacitance                                                    | COUT                 | See 4.4.1c, f = 1 MHz, I <sub>OUT</sub> = 0 mA                                                      |                   | 4.75 V<br>to<br>5.25 V       | 4          |             | 13.0    | рF   |

| Functional test                                                       |                      | See 4.4.1b                                                                                          |                   | 4.75 V<br>to<br>5.25 V       | 7,8        |             |         |      |

| DOTCLK frequency                                                      | fDC                  | <u>5</u> /                                                                                          |                   | 4.75 V<br>to<br>5.25 V       | 9,10,11    |             | 175     | MH   |

| Pixel clock PLL                                                       | f <sub>PC</sub>      | Internal frequency 5/                                                                               |                   | 4.75 V                       | 9,10,11    |             | 175     | MH:  |

| frequency                                                             |                      | PCLKOUT frequency 5/                                                                                |                   | to<br>5.25 V                 |            |             | 110     |      |

| MCLK PLL frequency                                                    | f <sub>M</sub>       | <u>5</u> /                                                                                          |                   | 4.75 V<br>to<br>5.25 V       | 9,10,11    |             | 100     | MH   |

| VCO frequency, pixel<br>clock PLL, MCLK<br>PLL, and loop clock<br>PLL | fvco                 | <u>5</u> /                                                                                          |                   | 4.75 V<br>to<br>5.25 V       | 9,10,11    | 110         | 220     | MH   |

| See footnotes at end of t                                             | able.                |                                                                                                     |                   |                              |            |             |         |      |

|                                                                       | STANDAR<br>CIRCUIT D |                                                                                                     | SIZE<br><b>A</b>  |                              |            | 5           | 5962-9  | 6758 |

| DEFENSE SUP                                                           | PLY CEN              | TER COLUMBUS<br>43216-5000                                                                          |                   | REVISION LEVEL<br>B          |            |             | SHEET 7 |      |

| Test and 1/                                                                  | Symbol           | Test conditions 2/                                                                                   | V <sub>DD</sub>         | Group A                 | Lin | nits | Unit            |

|------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----|------|-----------------|

| MIL-STD-883<br>test method                                                   |                  | -55°C ≤ T <sub>A</sub> ≤ +125°C<br>+4.75 V ≤ V <sub>DD</sub> ≤ +5.25 V<br>unless otherwise specified |                         | subgroups<br><u>3</u> / | Min | Max  |                 |

| CLK0 frequency for VGA mode 2                                                | <sup>f</sup> VGA | <u>5</u> /                                                                                           | 4.75 V<br>to<br>5.25 V  | 9,10,11                 |     | 85   | MHz             |

| Clock cycle time                                                             | t <sub>cyc</sub> | TTL <u>5</u> /                                                                                       | 4.75 V                  | 9,10,11                 | 7.1 |      | ns              |

|                                                                              |                  | ECL <u>5</u> /                                                                                       | to<br>5.25 V            |                         | 5.7 |      |                 |

| Delay time, RCLK<br>to LCLK                                                  | t <sub>d4</sub>  | 5/6/                                                                                                 | 4.75 V<br>to<br>5.25 V  | 9,10,11                 |     | 0.5  | RCLK<br>periods |

| Hold time, RS(3 <u>-0</u> ) valid before RD or WRI                           | t <sub>su1</sub> | 5/                                                                                                   | 4.75 V<br>to<br>5.25 V  | 9,10,11                 | 10  |      | ns              |

| Hold time, RS( <u>3-</u> 0)<br>valid after RD or<br>WRI                      | t <sub>h1</sub>  | 5/                                                                                                   | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 10  |      | ns              |

| Setup time, D(7 <u>-0</u> )<br>valid before WRî                              | <sup>t</sup> su2 | 5/                                                                                                   | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 35  |      | ns              |

| Hold time, D(7 <u>-0</u> )<br>valid after WR↑                                | <sup>t</sup> h2  | <u>5</u> /                                                                                           | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 0   |      | ns              |

| Setup time, VGA(7-0)<br>and VGAHS, VGAVS,<br>and VGABL valid<br>before CLK01 | t <sub>su3</sub> | 5/                                                                                                   | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 5   |      | ns              |

| Hold time, VGA(7-0)<br>and VGAHS, VGAVS,<br>and VGABL valid<br>After CLK01   | t <sub>h</sub> 3 | <u>5</u> /                                                                                           | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 5   |      | ns              |

| Setup time, P(63-0),<br>VGA(7-0), and PSEL<br>valid before LCLK†             | t <sub>su4</sub> | 5/                                                                                                   | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 5   |      | ns              |

| Hold time, P(63-0),<br>VGA(7-0), and PSEL<br>valid after LCLK1               | t <sub>h4</sub>  | 5/                                                                                                   | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 2   |      | ns              |

| Setup time, SYSHS,<br>SYSVS, and OVS<br>valid before<br>LCLKI                | t <sub>su5</sub> | <u>5</u> /                                                                                           | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 5   |      | ns              |

| Hold time, SYSHS,<br>SYSVS, and OVS<br>valid after LCLK1                     | t <sub>h5</sub>  | 5/                                                                                                   | 4.75 V<br>and<br>5.25 V | 9,10,11                 | 2   |      | ns              |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-96758 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 8          |

|                                                                                        | T#                | ABLE I. Electrical performan                                                                                                              | ce characteristics | - Continue              | ed.                          |            |             |      |

|----------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|------------------------------|------------|-------------|------|

| Test and 1/<br>MIL-STD-883<br>test method                                              | Symbol            | Test conditions $2$ / $-55^{\circ}$ C ≤ T <sub>A</sub> ≤ +125 $^{\circ}$ C +4.75 V ≤ V <sub>DD</sub> ≤ +5.25 V unless otherwise specified |                    | V <sub>DD</sub>         | Group A subgroups <u>3</u> / | Lin<br>Min | nits<br>Max | Unit |

| Setup time, SYSBC valid before LCLK1                                                   | <sup>t</sup> su6  | 5/                                                                                                                                        |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      | 5          |             | ns   |

| Hold time, SYSBC valid after LCLK1                                                     | t <sub>h6</sub>   | 5/                                                                                                                                        |                    | 4.75 V<br>and<br>5.25 V | <sup>.</sup> 9,10,11         | 2          |             | ns   |

| Pulse duration, RD or WR low                                                           | <sup>t</sup> w1   | 5/                                                                                                                                        |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      | 50         |             | ns   |

| Pulse duration, RD or WR high                                                          | t <sub>w2</sub>   | 5/                                                                                                                                        | 5/                 |                         | 9,10,11                      | 30         |             | ns   |

| Pulse duration, clock                                                                  | t <sub>w3</sub>   | TTL <u>5</u> /                                                                                                                            |                    | 4.75 ∨                  | 9,10,11                      | 3          |             | ns   |

| high                                                                                   |                   | ECL <u>5</u> /                                                                                                                            |                    | and<br>5.25 V           |                              | 2.5        |             |      |

| Pulse duration, clock                                                                  | t <sub>w4</sub>   | TTL <u>5</u> /                                                                                                                            |                    | 4.75 V                  | 9,10,11                      | 3          |             | ns   |

| low                                                                                    |                   | ECL <u>5</u> /                                                                                                                            |                    | and<br>5.25 V           |                              | 2.5        |             |      |

| SCLK/RCLK 7/<br>frequency                                                              | f <sub>SR</sub>   |                                                                                                                                           |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      |            | 85          | MHz  |

| VCLK frequency 7/                                                                      | fvc               |                                                                                                                                           |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      |            | 85          | МHz  |

| Enable time, RD low to D(7-0) valid                                                    | <sup>t</sup> en1  | See figure 5                                                                                                                              |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      |            | 40          | ns   |

| Disable time, RD<br>high to D(7-0)<br>disabled                                         | <sup>t</sup> dis1 | See figure 5                                                                                                                              |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      |            | 17          | ns   |

| Valid time, D(7-0)<br>valid after RD<br>high                                           | t <sub>v1</sub>   | See figure 5                                                                                                                              |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      | 5          |             | ns   |

| Delay time, RD low<br>to D(7-0) starting<br>to turn on                                 | t <sub>d1</sub>   | See figure 5                                                                                                                              |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      | 5          |             | ns   |

| Delay time, SCLK<br>high/low to RCLK<br>high/low                                       | t <sub>d3</sub>   | See figure 5 <u>8</u> / <u>9</u> / <u>10</u> /                                                                                            |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      | 1          | 6           | ns   |

| Analog output skew                                                                     | AOS               |                                                                                                                                           |                    | 4.75 V<br>and<br>5.25 V | 9,10,11                      | 0          | 2           | ns   |

| See footnotes at end of table.                                                         |                   |                                                                                                                                           |                    |                         |                              |            |             |      |

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                   |                                                                                                                                           | SIZE<br><b>A</b>   |                         |                              | 5          | 962-9       | 6758 |

|                                                                                        |                   |                                                                                                                                           |                    | REVISIO                 | N LEVEL<br>B                 | SH         | EET<br>9    |      |

## TABLE I. Electrical performance characteristics - Continued.

- 1/ For tests not listed in the referenced MIL-STD-883 (e.g. I<sub>DD</sub>), utilize the general test procedure of MIL-STD-883 under the conditions listed herein.

- 2/ Each input/output, as applicable, shall be tested at the specified temperature, for the specified limits, to the tests in table I herein. Output terminals not designated shall be high level logic, low level logic, or open, except for the I<sub>DD</sub> test, where the output terminals shall be open. When performing these tests, the current meter shall be placed in the circuit such that all current flows through the meter. For input terminals not designated, V<sub>IN</sub> = GND or V<sub>IN</sub> ≥ 3.0 V.

- 3/ For device class N only, all subgroup 3 (-55°C) test limits are guaranteed but not tested.

- 4/ Test conditions for RS343-A video signals (unless otherwise specified): recommended using external voltage reference V<sub>REF</sub> = 1.235 V, R<sub>SET</sub> = 523 Ω. When using the internal voltage reference, R<sub>SET</sub> may need to be adjusted in order to meet these limits.

- 5/ Unless otherwise specified, TTL input signals are 0 V to 3 V with less than 3 ns rise/fall time between the 10% and 90% levels. ECL input signals are V<sub>DD</sub>-1.8 V to V<sub>DD</sub>-0.8 V with less than 2 ns rise/fall time between the 20% and 80% levels. For input and output signals, timing reference points are at the 10% and 90% signal levels. Analog output loads are less than 10 pF. D(0-7) output loads are less than 50 pF. Unless otherwise specified, all other output loads are less than 50 pF. See figures 5 and 6.

- 6/ This parameter only applies when SCLK is used as the VRAM shift clock. When SCLK is not used, the delay may be as much as is required by system logic (assuming the loop clock PLL is used to compensate for the system delay).

- Z/ SCLK can drive an output capacitive load up to 60 pF. The worst-case transition time between the 10% and 90% levels is less than 4 ns (typical 3 ns). RCLK and VCLK can drive output capacitive loads up to 15 pF, with worst-case transition times between 10% and 90% levels less than 4 ns (typical 3 ns). See figure 6.

- 8/ The SCLK delay time to RCLK depends on the load that the signals drive. This parameter is measured with an VCLK = RCLK load of 15 pF and SCLK load of 60 pF.

- 9/ In SCLK mode, RCLK is delayed from SCLK in such a way that when RCLK is connected to LCLK.

- 10/ This parameter applies when SCLK is used.

- 4.2 <u>Screening</u>. For device classes N, Q, and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- Interim and final electrical test parameters shall be as specified in table II herein.

- Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-96758  |

|----------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                        |                  | REVISION LEVEL<br>B | SHEET<br>10 |

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-96758 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 11         |

| Symbol | Dimer  | Notes     |   |

|--------|--------|-----------|---|

|        | Millim | neters    |   |

|        | Min    | Max       |   |

| Α      |        | 4.07      | · |

| A1     | 3.17   | 3.67      |   |

| A2     | 0.25   |           |   |

| b      | 0.30   |           |   |

| С      | 0.16   |           |   |

| D      | 30.95  | 31.45     |   |

| D1     | 27.90  | 28.10     | • |

| E      | 30.95  | 31.45     |   |

| E1     | 27.90  | 28.10     |   |

| е      | 0.65   |           |   |

| k      | 0.65   | 0.65 0.95 |   |

| N      | 10     | 3         |   |

| Notes  | 1      |           |   |

## NOTES:

- 1. Controlling dimension: millimeter.

- 2. Index area: A notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as a pin one identification mark.

- 3. N is the maximum number of terminal positions.

FIGURE 1. Case outline Y - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-96758      |

|-------------------------------------------------------------|------------------|---------------------|-----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET <b>12</b> |

| Device                                                                                                                                                                                                                                                                                                      | 01                                                                                                                                                                                          |                                                                                                                                                                                  |                                              |                                                                                                                                                                                                                                                                            |                                                                              |                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| type  Case outline                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                             | X                                                                                                                                                                                |                                              |                                                                                                                                                                                                                                                                            |                                                                              |                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |  |  |

| Terminal<br>number                                                                                                                                                                                                                                                                                          | Terminal<br>symbol                                                                                                                                                                          | Terminal<br>number                                                                                                                                                               | Terminal<br>symbol                           | Terminal<br>number                                                                                                                                                                                                                                                         | Terminal<br>symbol                                                           | Terminal number                                                                                                                                                                                                                                                                             | Terminal<br>symbol                                                                                                                                        |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40 | PLLSEL0 DV <sub>DD</sub> P33 P32 P31 P30 P29 P28 P27 P26 P25 P24 P23 P22 P21 P20 GND DV <sub>DD</sub> P18 NC P17 P16 P15 P14 P13 P12 P11 P10 P9 P8 P7 P6 P5 P4 P3 P2 P1 P0 VD <sub>DD</sub> | 42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>55<br>55<br>55<br>55<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>77<br>77<br>78<br>79<br>80<br>81<br>82 | GN33 WRD DDD D DD DDD DDD DDD DDD DDD DDD DD | 83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>99<br>100<br>101<br>102<br>103<br>104<br>105<br>106<br>107<br>108<br>109<br>110<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>120<br>121<br>122<br>123 | GND DD AVGA3 4 5 6 7 SEL SYSAHS VGABG CLK1 2 P63 P59 P58 P57 DD CXTAL1 XTAL2 | 124<br>125<br>126<br>127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136<br>137<br>138<br>139<br>140<br>141<br>142<br>143<br>144<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154<br>155<br>156<br>157<br>158<br>159<br>160<br>161<br>162<br>163<br>164 | MCLK ODD/EVEN LCLK RCLK VCLK SCLK P56 P55 P54 P53 P52 P51 P50 P48 GND P47 P46 P45 NC P44 PLLV PCLKO NC P43 P42 P41 P40 P39 P38 P37 P36 P35 P34 GND PLSEL1 |  |  |

FIGURE 2. <u>Terminal connection</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-96758 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 13   |

| Device type                                                                                                       |                                                                                                                                          |                                                                                                                                                                                  |                                                  | 01                                                                                                                                                                                                                                         |                                           |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Case outline                                                                                                      |                                                                                                                                          | Y                                                                                                                                                                                |                                                  |                                                                                                                                                                                                                                            |                                           |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                   |

| Terminal<br>number                                                                                                | Terminal<br>symbol                                                                                                                       | Terminal<br>number                                                                                                                                                               | Terminal<br>symbol                               | Terminal<br>number                                                                                                                                                                                                                         | Terminal<br>symbol                        | Terminal<br>number                                                                                                                                                                                                                                              | Terminal<br>symbol                                                                                                                                                                                                                                                                |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 | PLLSEL0 DV DD P33 P32 P31 P30 P29 P28 P27 P26 P25 P24 P23 P20 GND P19 P18 P17 P16 P13 P12 P11 P10 P9 P8 P7 P6 P5 P4 P3 P2 P1 P0 VDDD GND | 42<br>43<br>44<br>45<br>47<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>71<br>72<br>73<br>74<br>75<br>77<br>78<br>81<br>82 | RS3 WR RD DO | 83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95<br>99<br>100<br>101<br>102<br>103<br>104<br>105<br>107<br>108<br>109<br>110<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>121<br>122<br>123 | GND DD D | 124<br>125<br>126<br>127<br>128<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136<br>137<br>138<br>139<br>140<br>141<br>142<br>143<br>144<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154<br>155<br>156<br>157<br>158<br>159<br>160 | RCLK<br>VCLK<br>SCLK<br>P56<br>P55<br>P54<br>P53<br>P52<br>P51<br>P50<br>P49<br>P48<br>GND<br>DVDD<br>P47<br>P46<br>P45<br>P44<br>PLLGND<br>PCLKOUT<br>NC<br>PLLVDD<br>NC<br>PLLVDD<br>NC<br>P43<br>P42<br>P41<br>P40<br>P39<br>P38<br>P37<br>P36<br>P35<br>P34<br>GND<br>P1LSEL1 |

FIGURE 2. <u>Terminal connection</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-96758 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 14   |

# Direct register map

| RS<br>3 | RS<br>2 | RS<br>1 | RS<br>0 | Register addressed by MPU                           | R/W | Default (Hex) |

|---------|---------|---------|---------|-----------------------------------------------------|-----|---------------|

| 0       | 0       | 0       | 0       | Palette/cursor RAM write address/<br>index register | R/W | XX            |