# **Motor Drivers for Printers**

# Three-phase Brushless Motor Driver for Polygonal Mirrors [For LBP, PPC]

**BD67929EFV** No.10016EAT05

# Description

BD67929EFV is a 3-phase brushless motor driver for polygon mirror motors of direct PWM drive type built-in PLL ensuring. As for its basic function, it is a 3-phase 120 $^{\circ}$  energization direct PWM drive type with power supply rated voltage of 36V and rated output current 2.3A. It is useful for high speed drive. It has the P-MOS and D-MOS on the output block, and the output ON Resistance is very low 1.35  $\Omega$  (Typ.). It is very useful for low power consumption. And this IC is high reliability due to built-in each protection functions (thermal protection, over current protection, restricted protection circuit).

### Features

- 1) 3-Phase MOS120° energization, direct PWM drive type

- 2) High output current: 2.5A

- 3) Low ON resistance DMOS output

- 4) PLL control circuit

- 5) Phase lock detection circuit

- 6) Current limiting circuit

- 7) 5V regulator output

- 8) Power-saving function (SS)

- 9) Short brake function (SB)

- 10) Built-in logic input pull-up resistor

- 11) Restricted protection circuit

- 12) CLK un-input protection circuit

- 13) CLK input baffler chattering circuit

- 14) Over current protection circuit (OCP)

- 15) Thermal shutdown circuit (TSD)

- 16) Over voltage lock out circuit (OVLO)

- 17) Under voltage lock out circuit (UVLO)

- 18) Electrostatic discharge: 8kV (HBM standard)

# Applications

Laser beam printer, PPC, etc.

# ● Absolute maximum ratings (Ta=25°C)

| Parameter                              | Symbol                          | Ratings                                  | Unit |

|----------------------------------------|---------------------------------|------------------------------------------|------|

| Supply voltage                         | Vcc                             | -0.2~+36.0                               | V    |

| Applied voltage of LD, FG terminal     | V <sub>LD</sub> , <sub>FG</sub> | -0.2~+6.5                                | V    |

| Applied voltage of HB terminal         | V <sub>HB</sub>                 | -0.2~+6.5                                | V    |

| Input voltage of Hall signal           | V <sub>HALL</sub>               | -0.2~+6.5                                | V    |

| Input voltage of CLK                   | V <sub>CLK</sub>                | -0.2~+6.5                                | V    |

| Input voltage of control pin (SS, SBE) | V <sub>IN</sub>                 | -0.2~+6.5                                | V    |

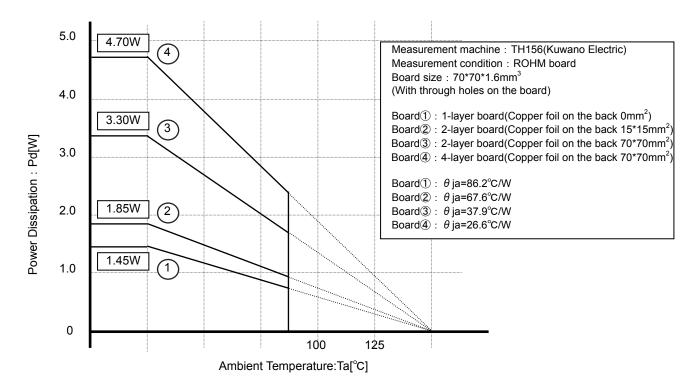

| Power dissipation                      | Pd                              | 1.45 <sup>*1</sup><br>4.70 <sup>*2</sup> | W    |

| Output current                         | l <sub>out</sub>                | 2500 <sup>*3</sup>                       | mA   |

| Operating temperature range            | T <sub>opr</sub>                | -25~+85                                  | °C   |

| Storage temperature range              | T <sub>str</sub>                | -55~+150                                 | °C   |

| Junction temperature                   | T <sub>jmax</sub>               | 150                                      | °C   |

<sup>70</sup>mm×70mm×1.6mm glass epoxy board. Derating in done at 11.6mW/°C for operating above Ta=25°C Mounting on 4-layer board. Derating in done at 37.6mW/°C for operating above Ta=25°C.

# ●Operating conditions (Ta=-25~85°C)

| Parameter                          | Symbol                          |      | Unit |      |       |  |

|------------------------------------|---------------------------------|------|------|------|-------|--|

| Farameter                          | Symbol                          | Min. | Тур. | Max. | Offic |  |

| Supply voltage                     | V <sub>CC</sub>                 | 19   | 24   | 28   | V     |  |

| Output current of 5V regulator     | I <sub>REG</sub>                | -20  | -    | 0    | mA    |  |

| Input current of HB terminal       | I <sub>HB</sub>                 | 0    | -    | 20   | mA    |  |

| Applied voltage of LD, FG terminal | $V_{LD}$ , FG                   | 0    | -    | 5.5  | V     |  |

| Output current of LD, FG terminal  | I <sub>LD</sub> , <sub>FG</sub> | 0    | -    | 15   | mA    |  |

Do not, however exceed Pd, ASO and Tlmax=150°C.

# ● Electrical characteristics (Unless otherwise specified, Ta=25°C, Vcc=24V)

| ctrical characteristics (Unless otherwise specified, |                                      | Ia=25°C, VCC=24V) |            |      |            |                                                      |

|------------------------------------------------------|--------------------------------------|-------------------|------------|------|------------|------------------------------------------------------|

| Parameter                                            | Parameter Symbol Limits  Nin Typ May |                   | Max        | Unit | Conditions |                                                      |

| \A/I <sub>2</sub> = I =                              |                                      | Min.              | Тур.       | Max. |            |                                                      |

| Whole                                                |                                      |                   | 4.0        | 0.0  | 0          | 00 1 Outrot in ON                                    |

| Circuit current 1                                    | I <sub>CC1</sub>                     | -                 | 4.0<br>1.0 | 9.0  | mA<br>mA   | SS=L, Output is ON                                   |

|                                                      | Circuit current 2 I <sub>CC2</sub>   |                   |            |      |            | SS=H, Output is OFF                                  |

| VREG output                                          | 1                                    |                   |            | T    |            |                                                      |

| Output voltage                                       | $V_{REG}$                            | 4.65              | 5.00       | 5.35 | V          |                                                      |

| Driver block (U, V, W)                               | 1                                    | ı                 |            | ı    | ı          | 1 404 1:1                                            |

| Output ON resistance                                 | R <sub>ON</sub>                      | -                 | 1.35       | 1.76 | Ω          | I <sub>OUT</sub> =1.0A on high and low side in total |

| Forward voltage of Diode on low side                 | $V_{D1}$                             | 0.70              | 1.10       | 1.55 | V          | I <sub>OUT</sub> =-1.0A                              |

| Forward voltage of Diode on high side                | $V_{D2}$                             | 0.70              | 1.10       | 1.55 | V          | I <sub>OUT</sub> =1.0A                               |

| Output leak current                                  | I <sub>LEAK</sub>                    | -                 | -          | 10   | μΑ         |                                                      |

| Hall comparator (HUP, HUN, HVP, HVN                  | , HWP, HW                            | /N)               |            |      |            |                                                      |

| In-phase input voltage range                         | VICM                                 | 1.5               | -          | 3.5  | V          | High and low side in total                           |

| Hysteresis voltage                                   | $\Delta V_{IN}$                      | 15                | 24         | 42   | mV         |                                                      |

| LD, FG output                                        | •                                    |                   |            |      |            |                                                      |

| Low output voltage                                   | $V_{OD}$                             | -                 | 0.15       | 0.50 | V          | I <sub>LD,FG</sub> =10mA                             |

| PD output                                            | 1                                    |                   | 1          |      |            | -                                                    |

| High output voltage                                  | $V_{PDH}$                            | 4.5               | 4.9        | -    | V          | I <sub>PD</sub> =-100μA                              |

| Low output voltage                                   | $V_{PDL}$                            | -                 | 0.2        | 0.3  | V          | I <sub>PD</sub> =100μA                               |

| Integral Amplifier                                   | 1                                    |                   |            |      |            |                                                      |

| High output voltage of EO                            | $V_{ERH}$                            | 3.5               | 4.1        | -    | V          | I <sub>EO</sub> =-500μA                              |

| Low output voltage of EO                             | V <sub>ERL</sub>                     | -                 | 0.9        | 1.5  | V          | I <sub>EO</sub> =500μA                               |

| Input current of EI                                  | I <sub>Ei</sub>                      | -2.0              | -0.1       | -    | μΑ         | V <sub>Ei</sub> =0V                                  |

| Current limiting circuit                             |                                      |                   |            |      |            |                                                      |

| Gain at start up                                     | GH                                   | 1.2               | 1.5        | 1.8  | times      |                                                      |

| Gain at steady state                                 | GL                                   | 0.4               | 0.5        | 0.6  | times      |                                                      |

| Limit voltage                                        | $V_{RNF}$                            | 0.45              | 0.50       | 0.55 | V          |                                                      |

| CLK input                                            | I.                                   |                   |            |      |            |                                                      |

| External input frequency                             | F <sub>CLK</sub>                     | _                 | -          | 10   | kHz        |                                                      |

| High level input voltage                             | V <sub>CLKH</sub>                    | 3.0               | -          | -    | V          |                                                      |

| Low level input voltage                              | V <sub>CLKL</sub>                    | -                 | -          | 1.5  | V          |                                                      |

| Low level input current                              | I <sub>CLKL</sub>                    | -75               | -50        | -25  | μΑ         | V <sub>CLK</sub> =0V                                 |

| Control input(SS, SB)                                | I.                                   |                   |            |      |            |                                                      |

| High level input voltage                             | V <sub>INH</sub>                     | 3.0               | -          | -    | V          |                                                      |

| Low level input voltage                              | V <sub>INL</sub>                     | -                 | -          | 1.5  | V          |                                                      |

| Low level input current                              | I <sub>INL</sub>                     | -75               | -50        | -25  | μA         | V <sub>IN</sub> =0V                                  |

| Oscillator                                           | 1                                    | 1                 | 1          | 1    | 1          | I                                                    |

| Oscillating frequency                                | Fosc                                 | 130               | 200        | 270  | kHz        | C <sub>OSC</sub> =220pF                              |

| High triangular waveform voltage                     | Vosch                                | 1.6               | 2.0        | 2.4  | V          |                                                      |

| Low triangular waveform voltage                      | Voscl                                | 1.2               | 1.5        | 1.8  | V          |                                                      |

| PROCLK                                               | 1                                    | 1                 | I.         | 1    | 1          | I                                                    |

| CLK cycle for protection circuit                     | T <sub>PCLK</sub>                    | 13                | 20         | 27   | msec       | C <sub>PCLK</sub> =0.1µF                             |

| Hall bias                                            | 1                                    | 1                 | 1          | 1    | 1          | 1                                                    |

| Hall bias voltage                                    | $V_{HB}$                             | 0.65              | 0.80       | 0.95 | V          | I <sub>HB</sub> =10mA                                |

|                                                      |                                      | 1                 | 1          | 1    | 1          | 1                                                    |

# ●Pin function

| Pin No | Pin name | Function                                                     | Pin No | Pin name | Function                                                                 |

|--------|----------|--------------------------------------------------------------|--------|----------|--------------------------------------------------------------------------|

| 1      | GND      | Ground                                                       | 15     | HUP      | Hall signal input terminal                                               |

| 2      | VCC      | Power supply terminal                                        | 16     | VREG     | 5V regulator output terminal                                             |

| 3      | FG       | FG output terminal                                           | 17     | PD       | Phase comparison output terminal                                         |

| 4      | CS       | Current detection comparator input terminal                  | 18     | TEST     | Testing terminal                                                         |

| 5      | RNF      | Connection terminal of resistor for output current detection | 19     | EI       | Error amplifier input terminal                                           |

| 6      | W        | Output terminal                                              | 20     | EO       | Error amplifier output terminal                                          |

| 7      | V        | Output terminal                                              | 21     | PROCLK   | Connection terminal of a capacitor to set the clock cycle for protection |

| 8      | U        | Output terminal                                              | 22     | CLK      | Speed control clock input terminal                                       |

| 9      | НВ       | Bias terminal for Hall element                               | 23     | SS       | Start/stop signal input terminal                                         |

| 10     | HWN      | Hall signal input terminal                                   | 24     | LD       | Phase locked detection output terminal                                   |

| 11     | HWP      | Hall signal input terminal                                   | 25     | OSC      | Connection terminal of capacitor to set PWM oscillating frequency        |

| 12     | HVN      | Hall signal input terminal                                   | 26     | BRMODE   | Switch terminal of deceleration mode in servo                            |

| 13     | HVP      | Hall signal input terminal                                   | 27     | CNF      | Connection terminal of capacitor for current sense amp                   |

| 14     | HUN      | Hall signal input terminal                                   | 28     | SB       | Short brake signal input terminal                                        |

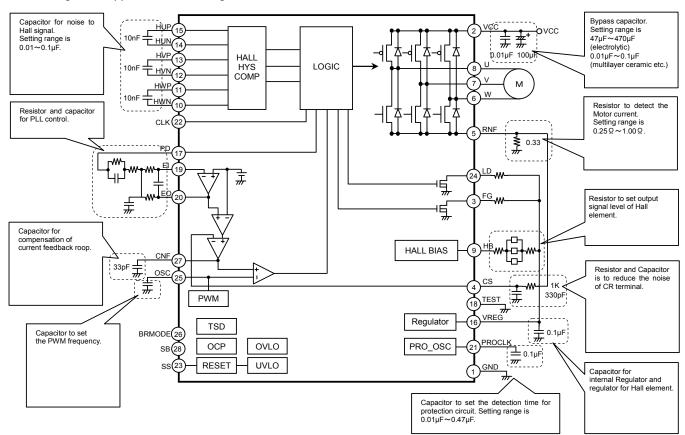

# Block diagram & Application circuit diagram

Block diagram & Application circuit diagram

### Terminal function

# OHWP, HVP, HUP, HWN, HVN, HUN/Hall signal input terminal

These terminals are the input terminals of the output signals from Hall elements. This has the comparator with hysteresis. The width of hysteresis voltage is  $\pm 12 \text{mV}(\text{Typ.})$ . The output of this comparator will be high if the voltage of HxP terminal is greater than the voltage of HxN terminal by 12mV, and the level will be low if the voltage of HxP terminal is less than the voltage of HxN terminal by 12mV. For the countermeasures against noise interface with Hall inputs, the connection of a capacitor with a capacitance of approximately  $0.01 - 0.1 \mu\text{F}$  between HxP terminal and HxN terminal.

### OPD/Phase comparison output terminal

This terminal outputs the signal that is the comparison of FG signal and CLK signal.

# OEI/Error amplifier input terminal

This terminal is the input terminal of the error amplifier.

### OEO/Error amplifier output terminal

This terminal is the output terminal of the error amplifier. It is connected to the input terminal of motor torque command signal inside the IC.

# OCLK/Speed control clock input terminal

This terminal is the CLK signal input terminal to control the speed. This terminal has the  $100k\Omega$  resistor which is pulled-up to the internal regulator. This block detect the falling edge. In case that there is the noise on the CLK signal, it makes the miscount of the CLK signal. Be sure to design the pattern without the influence of the noise.

# OSS/Start/Stop signal input terminal

This terminal makes the motor start or stop.

This terminal has the  $100k\Omega$  resistor which is pulled-up to the internal regulator.

| SS |       |

|----|-------|

| LO | start |

| HI | stop  |

When SS=HI, IC becomes stop condition. Stop condition is Free Run or Short Brake that decided by SB terminal. Moreover, it makes the HB terminal off, and shut down the current to the Hall element. It is very useful to low power consumption.

# OLD/Phase locked detection output terminal

When the rotation count of the motor is within 10% of the target rotation count, the LD terminal becomes LO. This terminal is open drain type output, please connect to the external regulator (0~5.5V recommended) through the resistor. The capability of this terminal is 15mA maximum, please set the voltage of the external regulator and the value of resistor to be within 15mA.

# OOSC/Connection terminal of capacitor to set PWM oscillating frequency

This terminal is the connection terminal of capacitor to make the triangle waveform that set the PWM frequency.  $f_{PWM} = 44 \mu / C \text{ [Hz]}$

ex.) when C=220pF, f=200 [kHz]

# OCNF/Connection terminal of capacitor of Current Sense Amp.

This terminal is the connection terminal of capacitor to compensate the phase of CS Amplifier.

# OSB/Short brake signal input terminal

This terminal is the input signal terminal that set output condition when the voltage of SS is HI. This terminal has the  $100k\Omega$  resistor which is pulled-up to the internal regulator. When the voltage of SB terminal turns to LO, all low side MOS FET turns to ON, and it should be short brake condition. It is very useful to reduce the speed quickly.

| SB | stop mode        |  |  |  |

|----|------------------|--|--|--|

| LO | Short brake mode |  |  |  |

| HI | Free run mode    |  |  |  |

# OBRMODE/PLL brake setting terminal

This IC has the two kinds of deceleration method. The method is configurable by which terminal to connect with BRMODE, VREG or GND terminal. This terminal has the  $100k\Omega$  resistor which is pulled-up to the internal regulator.

| BRMODE | deceleration method |  |  |

|--------|---------------------|--|--|

| GND    | short brake         |  |  |

| VREG   | free run            |  |  |

# OVREG/5V regulator output terminal

This terminal is the connection terminal of capacitor to stabilize the 5V output of internal regulator. It should be connected with the capacitor  $(0.01\mu\text{F}-1\mu\text{F})$  to the ground. This terminal is used as the regulator to the Hall element too. The road current should be within 20mA.

# OPROCLK/Connection terminal of a capacitor to set the clock cycle for protection

This terminal is the connection terminal of capacitor to set the time of detection.

The period of PROCLK=C × 200k[s]

ex.) when C=0.1µF, The period of PROCLK=20m[s]

# OHB/Bias terminal for Hall element

This terminal is the open collector type, and low side switch. By connecting the GND side of Hall element to the HB, the bias current of the Hall element will be turned off with the SS set to high or open. It is very useful for the low power consumption because the bias current for Hall element will be  $0\mu$ A.

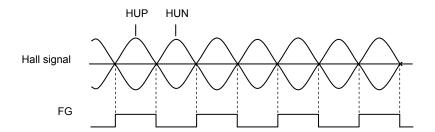

# OFG/FG output terminal

This terminal outputs the signal which indicate the rotation count, which is synthesize from Hall signal of U-phase. This terminal is open drain type output, it should be pulled-up to the external regulator (0-5.5V) through the resistor. The capability of FG terminal is 15mA maximum, please set the voltage of external regulator and the value of resistor to be within 15mA.

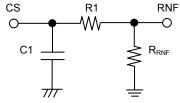

# OCS/Current detection comparator input terminal

In this IC, CS terminal, which is the input terminal of current limit comparator, is independently arranged in order to decrease the lowering of current-detecting accuracy caused by the wire impedance inside the IC of RNF terminal.

Therefore, please be sure to connect RNF terminal and CS terminal together when using in the case of PWM constant current control. In addition, because the wires from CS terminal is connected near the current-detecting resistor in the case of interconnection, the lowering of current-detecting accuracy, which is caused by the impedance of board pattern between RNF terminal and the current-detecting resistor, can be decreased. Moreover, please design the pattern in such a way that there is no noise plunging. In addition, please be careful because if terminal of RNF is shorted to GND, large current flows without normal PWM constant current control and, then there is danger that OCP or TSD will operate.

To reduce the PWM noise influence, please out the filter between RNF terminal and CS terminal.

The cut-off frequency is below  $f = 1 / (2 \pi \times R1 \times C1)$

ex.) when C1=330pF, R1=1kHz f=483[kHz]

# OU, V, W/Output terminal

Motor's drive current is flowing in it, so please wires in such a way that the wire is thick & short has low impedance. It is also effective to add a Shot-key diode if output has positive or negative great fluctuation when large current is used etc., for example, if counter electromotive voltage etc. is great. Moreover, in the output terminal, there is built-in clamp component for preventing of electrostatic destruction. If steep pulse or voltage of surge more that maximum absolute rating is applied, this clamp component operates, as a result there is the danger of even destruction, so please be sure that the maximum absolute rating must not be exceeded.

# **OGND/Ground terminal**

In order to reduce the noise caused by switching current and to stabilize the internal reference voltage of IC, please wire in such a way that the wiring impedance from this terminal is made as low as possible to achieve the lowest electrical potential no matter what operating state it may be.

# OVCC/Power supply terminal

Motor's drive current is flowing in it, so please wire in such a way that the wire is thick & short and has low impedance. Voltage VCC may have great fluctuation, so please arrange the bypass capacitor of about  $47\mu\text{F}\sim470\mu\text{F}$  as close to the terminal as possible and adjust in such a way that the voltage VCC is stable. Please increase the capacity if needed especially when a large current is used or those motors that have great back electromotive force are used. In addition, for the purpose of reducing of power supply's impedance in wide frequency bandwidth, parallel connection of multi-layered ceramic capacitor of  $0.01\mu\text{F}\sim0.1\mu\text{F}$  etc. is recommended. Extreme care must be used to make sure that the voltage VCC does not exceed the rating even for a moment. Still more, in the power supply terminal, there is built-in clamp component for preventing of electrostatic destruction. If steep pulse or voltage of surge more that maximum absolute rating is applied, this clamp component operates, as a result there is the danger of destruction, so please be sure that the maximum absolute rating must not be exceeded. It is effective to mount a Zener diode of about the maximum absolute rating. Moreover, the diode for preventing of electrostatic destruction if reverse voltage is applied between  $V_{CC}$  terminal and GND terminal, so please be careful.

### ORNF/Connection terminal of resistor for detecting of output current

Please connect the resistor of  $0.25\,\Omega\sim1.00\,\Omega$  for current detection between this terminal and GND. In view of the power consumption of the current-detecting resistor, please determine the resistor in such a way that W=I<sub>OUT</sub><sup>2</sup> • R[W] does not exceed the power dissipation of the resistor. In addition, please wire in such a way that it has a low impedance and does not have a impedance in common with other GND patterns because motor's drive current flows in the pattern through RNF terminal~current-detecting resistor~GND. Please do not exceed the rating because there is the possibility of circuits' malfunction etc. if RNF voltage has exceeded the maximum rating (0.7V). Moreover, please be careful because if RNF terminal is shorted to GND, large current flows without normal PWM constant current control, then there is the danger that OCP or TSD will operate. If RNF terminal is open, then there is the possibility of such malfunction as output current does not flow either, so please do not let it open.

# OIC back side metal/Metal for heat-radiation

For HTSSOP-B28 package, the heat-radiating metal is mounted on IC's back side, and on the metal the heat-radiating treatment is performed when in use, which becomes the precondition to use, so please secure sufficiently the heat-radiating area by surely connecting by solder with the GND plane on the board and getting as wide GND pattern as possible. Please be careful because the allowable loss as shown in page 21 cannot be secured if not connected by solder. Moreover, the back side metal is shorted with IC chip's back side and becomes the GND potential, so there is the danger of malfunction and destruction if shorted with potentials other than GND, therefore please absolutely do not design patterns other than GND through the IC's back side.

# OTEST terminal/Terminal for testing

This is the terminal used at the time of shipping test. Please connect to GND. Please be careful because there is a possibility of malfunction if GND unconnected.

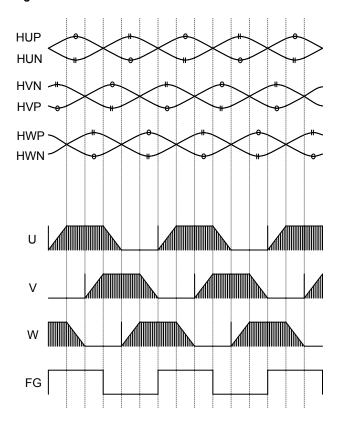

# ●Servo and PLL

This IC synchronizes the phase of the reference CLK signal and the internal three-phase synthesized FG in motor RPM control. In the control system, the rising of the FG signal and the falling of CLK signal are monitored and the phase comparison of the two signals is made. The output signal after the phase comparison is smoothed by the active filter with the above INT amplifier used to determine the torque of the motor. The motor rotates at the torque determined here and the FG signal is generated. The motor rotates at the number of revolutions according the CLK, and the IC goes into servo mode.

# ●Input and output condition table

|             | Hall input |     |     | Output |   |   | FG logic |

|-------------|------------|-----|-----|--------|---|---|----------|

| Pin No.     | 15         | 13  | 11  | 8      | 7 | 6 | 3        |

| Pin Name    | HUP        | HVP | HWP | U      | V | W | FG       |

| Condition 1 | L          | Н   | Н   | L      | Н | М | L        |

| Condition 2 | L          | L   | Н   | L      | М | Н | L        |

| Condition 3 | Н          | L   | Н   | М      | L | Н | Н        |

| Condition 4 | Н          | L   | L   | Н      | L | М | Н        |

| Condition 5 | Н          | Н   | L   | Н      | М | L | Н        |

| Condition 6 | L          | Н   | L   | М      | Н | L | L        |

HUN(35pin)= HVN(33pin)= HWN(31pin)= M

# Timing Chart

BD67929EFV Technical Note

### Protection Circuits

### OThermal Shutdown (TSD)

This IC has a built-in thermal shutdown circuit for thermal protection. When the IC's chip temperature rises above 175°C (Typ.), the motor output becomes OPEN. Also, when the temperature returns to under 150°C(Typ.), it automatically returns to normal operation. However, even when TSD is in operation, if heat is continued to be added externally, heat overdrive can lead to destruction.

# OOver Current Protection (OCP)

This IC has a built-in over current protection circuit as a provision against destruction when the motor outputs are shorted each other or VCC-motor output pr motor output-GND is shorted. This circuit latches the motor output to OPEN condition when the regulated threshold current flows for 4µs (Typ.). It returns with power reactivation or a reset of the SS terminal. The over current protection circuit's only aim is to prevent the destruction of the IC from irregular situations such as motor output shorts, and is not meant to be used as protection or security for the set. Therefore, sets should not be designed to take into account this circuit's functions. After OCP operating, if irregular situations continues and the return by power reactivation or a reset of the PS terminal is carried out repeatedly, then OCP operates repeatedly and the IC may generate heat or otherwise deteriorate. When the L value of the wiring is great due to the wiring being long, after the over current has flowed and the output terminal voltage jumps up and the absolute maximum values may be exceeded and as a result, there is a possibility of destruction. Also, when current which is over the output current rating and under the OCP detection current flows, the IC can heat up to over Tjmax=150°C and can deteriorate, so current which exceeds the output rating should not be applied.

# OUnder Voltage Lock Out (UVLO)

This IC has a built-in under voltage lock out function to prevent false operation such as IC output during power supply under voltage. When the applied voltage to the  $V_{CC}$  terminal does under 15V (Typ.), the motor output is set to OPEN. This switching voltage has a 1V (Typ.) hysteresis to prevent false operation by noise etc. Please be aware that this circuit does not operate during SS=HI mode.

# OOver Voltage Lock Out (OVLO)

This IC has a built-in over voltage lock out function to protect the IC output and the motor during power supply over voltage. When the applied voltage to the VCC terminal goes over 33V (Typ.), the motor output is set to OPEN. This switching voltage has a 1V (Typ.) hysteresis and a 4µs (Typ.) mask time to prevent false operation by noise etc. Although this over voltage locked out circuit is built-in, there is a possibility of destruction if the absolute maximum value for power supply voltage is exceeded, therefore the absolute maximum value should not be exceeded. Please be aware that this circuit does not operate during SS=HI mode.

# ORestricted protection circuit

This IC has a built-in restricted protection circuit for the provision against restriction of the motor. This circuit sets PD to H for decreasing the torque when FG signal does not change over for certain time. It returns by re-charging the power supply or resetting by SS terminal. The length of the time for detecting the motor lock will be able to set by the value of the capacitor which is connected to PROCLK terminal.

When motor is locked by some reason, Pd is changed to H and the motor torque is decreased. The time that is until detecting the lock is set by the value of capacitor which is connected to PROCLK terminal.

The period of PROCLK =  $C \times 200k[s]$

The detecting time to lock = the period of PROCLK × 96 count

=  $C \times 200k[s] \times 96$  count

ex.) When C=0.1µF, T= 1.92 [s]. The declination of 1 count may occur by the timing of the count.

# ONon input CLK protection circuit

This IC has a built-in non input CLK protection circuit for the provision against breaking of CLK. This circuit sets the motor output open when CLK signal does not change over for certain time. It returns by re-changing the power supply or resetting by SS terminal. The length of the time for detecting the state of non input CLK will be able to set by the value of the capacitor which is connected to PROCLK terminal.

The period of PROCLK =  $C \times 200k[s]$

The detecting time to lock T = The period of PROCLK  $\times$  3count

=  $C \times 200k[s] \times 3count$

ex.) When C=0.1µF, T= 80 [ms]. The declination of 1 count may occur by the timing of the count.

### Power Consumption

Please confirm that the IC's chip temperature Tj is not over 150°C, while considering the IC's power consumption (W), package power (Pd) and ambient temperature (Ta). When Tj is exceeded 150°C, the functions as a semiconductor do not operate and problems such as parasitism and leaks occur. Constant use under these circumstances leads to deterioration and eventually destruction of the IC. Tjmax=150°C must be strictly obeyed under all circumstances.

### OThermal Calculation

The IC's consumed power can be estimated roughly with the power supply voltage (VCC), circuit current (ICC), output ON resistance ( $R_{ONH}$ ,  $R_{ONL}$ ) and motor output current value ( $I_{OUT}$ ).

Consumed power of the Vcc [W] =  $V_{CC}$  [V] ×  $I_{CC}$  [A] ······①

Consumed power of the output DMOS [W] =  $(R_{ONH} + R_{ONL}) \times I_{OUT}^2 \times on_{duty} + \{R_{ONL} \times I_{OUT}^2 + D_{IVL} \times I_{OUT}\} (1-on_{duty}) \cdots ②$

ton varies depending on the L and R values of the motor coil and the current set value.

Please confirm by actual measurement, or make an approximate calculation.

t<sub>chop</sub> is the period of chopping which is set by the external capacitor of OSC terminal. See page 5 for detail.

High side Pch DMOS ON Resistance  $R_{ONH} [\Omega]$  (typ.)= 0.70  $[\Omega]$  Low side Nch DMOS ON Resistance  $R_{ONL} [\Omega]$  (typ.)= 0.65  $[\Omega]$

Consumed power of total IC W\_total[W] = ① + ②

Junction temperature Tj = Ta[ $^{\circ}$ C] +  $\theta$  ja[ $^{\circ}$ C/W]·W total [W]

However, the thermal resistance value  $\theta_{ja}$  [°C/W] differs greatly depending on circuit board conditions. Refer to the derating curve on P.10. Also, we are taking measurements of thermal resistance value  $\theta_{ja}$  of boards actually in use. Please feel free to contact our salesman. The calculated values above are only theoretical. For actual thermal design, please perform sufficient thermal evaluation for the application board used, and create the thermal design with enough margin to not exceed Tjmax=150°C. Although unnecessary with normal use, if the IC is to be used under especially strict heat conditions, please consider externally attaching a Schottky diode between the motor output terminal and GND to abate heat from the IC.

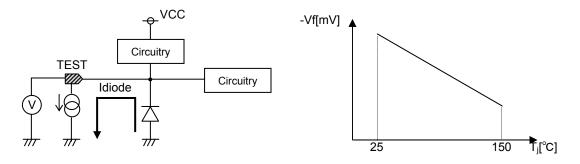

# **OTemperature Monitoring**

There is a way to directly measure the approximate chip temperature by using the TEST terminal. However, temperature monitor using this TEST terminal is only for evaluation and experimenting, and must not be used in actual usage conditions. TEST terminal has a protection diode for prevention from electrostatic discharge. The temperature may be monitored using this protection diode.

- (1) Measure the terminal voltage when a current of Idiode=50μA flows from the TEST terminal to the GND, without supplying VCC to the IC. This measurement is of the Vf voltage inside the diode.

- (2) Measure the temperature characteristics of this terminal voltage. (Vf has a linear negative temperature may be calibrated from the TEST terminal voltage.

- (3) Supply VCC, confirm the TEST terminal voltage while running the motor, and the chip temperature can be approximated from the results of (2).

Model diagram for measuring chip temperature

# ●Power Dissipation

# OHTSSOP-B28 Package

HTSSOP-B28 has exposed metal on the back, and it is possible to dissipate heat from a through hole in the back. Also, the back of board as well as the surfaces has large areas of copper foil heat dissipation patterns, greatly increasing power dissipation. The back metal is shorted with the back side of the IC chip, being a GND potential, therefore there is a possibility for malfunction if it is shorted with any potential other than GND, which should be avoided. Also, it is recommended that the back metal is soldered onto the GND to short. Please note that it has been assumed that this product will be used in the condition of this back metal performed heat dissipation treatment for increasing heat dissipation efficiency.

HTSSOP-B28 Derating Curve

### Notes for use

# (1) Absolute maximum ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down the devices, thus making impossible to identify breaking mode, such as a short circuit or an open circuit. If any over rated values will expect to exceed the absolute maximum ratings, consider adding circuit protection devices, such as fuses.

(2) Connecting the power supply connector backward

Connecting of the power supply in reverse polarity can damage IC. Take precautions when connecting the power supply lines. An external direction diode can be added.

# (3) Power Supply Lines

Design PCB layout pattern to provide low impedance GND and supply lines. To obtain a low noise ground and supply line, separate the ground section and supply lines of the digital and analog blocks. Furthermore, for all power supply terminals to ICs, connect a capacitor between the power supply and the GND terminal. When applying electrolytic capacitors in the circuit, not have sufficient current absorption capacity, regenerative current will cause the voltage on the power supply line to rise, which combined with the product and its peripheral circuitry may exceed the absolute maximum ratings. It is recommended to implement a physical safety measure such as the insertion of a voltage clamp diode between the power supply and GND pins.

# (4) GND Potential

The potential of GND pin must be minimum potential in all operating conditions.

(5) Metal on the back side (Define the side where product markings are printed as front)

The metal on the backside is shorted with the backside of IC chip therefore it should be connected to GND. Be aware that there is a possibility of malfunction or destruction if it is shorted with any potential other than GND.

### (6) Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions. This IC is equipped with FIN heat dissipation terminals, but dissipation efficiency can be improved by applying heat dissipation treatment in this area. It is important to consider actual usage conditions and to take as large a dissipation pattern as possible.

### (7) Inter-pin shorts and mounting errors

When attaching to a printed circuit board, pay close attention to the direction of the IC and displacement. Improper attachment may lead to destruction of the IC.

# (8) Operation in a strong electric field

Use caution when using the IC in the presence of a strong electromagnetic field as doing so may cause the IC to malfunction.

# (9) ASO

When using the IC, set the output transistor so that it does not exceed absolute maximum ratings or ASO.

# (10) Thermal shutdown circuit

The IC has a built-in thermal shutdown circuit (TSD circuit). If the chip temperature becomes  $T_{max}=150^{\circ}C$ , and higher, coil output to the motor will be open. The TSD circuit is designed only to shut the IC off to prevent runaway thermal operation. It is not designed to protect or indemnify peripheral equipment. Do not use the TSD function to protect peripheral equipment.

| TSD on temperature [°C] (Typ.) | Hysteresis Temperature [°C] (Typ.) |

|--------------------------------|------------------------------------|

| 175                            | 25                                 |

### (11) Inspection of the application board

During inspection pf the application board, if a capacitor is connected to a pin with low impedance there is a possibility that it could cause stress to the IC, therefore an electrical discharge should be performed after each process. Also, as a measure again electrostatic discharge, it should be earthed during the assembly process and special care should be taken during transport or storage. Furthermore, when connecting to the jig during the inspection process, the power supply should first be turned off and then removed before the inspection.

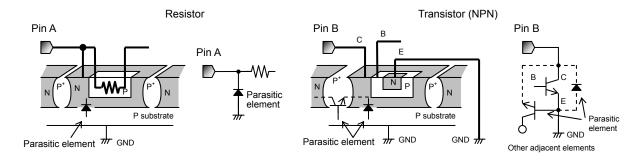

# (12) Input terminal of IC

This IC is a monolithic IC, and between each element there is a P+ isolation foe element partition and a P substrate. This P layer and each element's N layer make up the P-N junction, and various parasitic elements are made up.

For example, when the resistance and transistor are connected to the terminal as shown in figure,

- OWhen GND>(Terminal A) at the resistance and GND>(Terminal B) at the transistor (NPN),

- the P-N junction operates as a parasitic diode.

- OAlso, when GND>(Terminal B) at the transistor (NPN)

The parasitic NPN transistor operates with the N layers of other elements close to the aforementioned parasitic diode.

Because of the IC's structure, the creation of parasitic elements is inevitable from the electrical potential relationship. The operation of parasitic elements causes interference in circuit operation, and can lead to malfunction and destruction. Therefore, be careful not to use it in a way which causes the parasitic elements to operate, such as by applying voltage that is lower than the GND (P substrate) to the input terminal.

Pattern Diagram of Parasitic Element

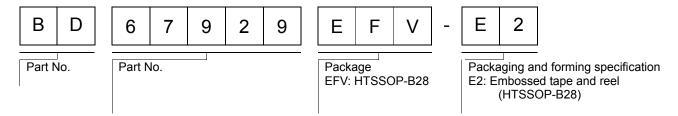

# Ordering part number

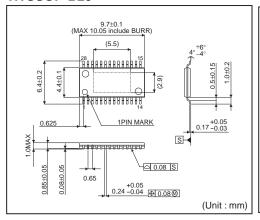

# HTSSOP-B28

# Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/