## Introduction

The CY7C964 is a flexible collection of byte (8-bit) wide transceivers, latches, counters, multiplexers, and comparators that provide bus interface designs with a low-cost alternative to PLDs, ASICs, or discrete logic devices. It is based on a standard cell design that incorporates patented line drivers for reduced ground bounce and high noise immunity. The CY7C964 is a companion part to Cypress's VIC068A and VIC64 VMEbus interface controller devices. It is completely compatible with all operating modes of either device, such as dual-address path, block transfer boundary crossing conditions, block transfer initialization cycle, local DMA control, and D64 VMEbus block transfers, (the latter when used in conjunction with the VIC64). Signal-naming conventions correspond directly to the VIC068A/VIC64 buffer control signals, and the CY7C964 can be directly connected to these corresponding signals.

The CY7C964 can also be used as a generic-interface building block. Some examples include low-cost slave VMEbus controllers, VSB interfaces, or other interface applications. CY7C964s are cascadable allowing easy interfacing to buses of any width. By combining multiple logic functions into one discrete part, the CY7C964 saves board space and reduces power consumption, which is becoming increasingly important to designers. The CY7C964 has two operating modes, Byte Width and Word Width. The Byte Width configuration of the device has 8 local address, 8 local data signals, 8 VMEbus address and 8 VMEbus data signals. The Word Width mode changes the local and VMEbus data signals into 16-bit extended address or data paths.

## **Features**

- Directly connects to VIC068A or VIC64 for seamless VME bus interface

- Has internal counters for block transfer and local DMA address control

- Has internal multiplexers for D64 64-bit VMEbus block transfers

- Has internal comparators for address decoding

- Supports VIC068A/VIC64 dual-address-path option

- Has cascadable operation

- Directly drives VMEbus address and data bus signals

- Directly drives local address and data bus signals

- Reduces components for a compact board design

- Has low power requirements

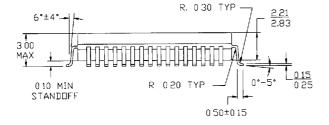

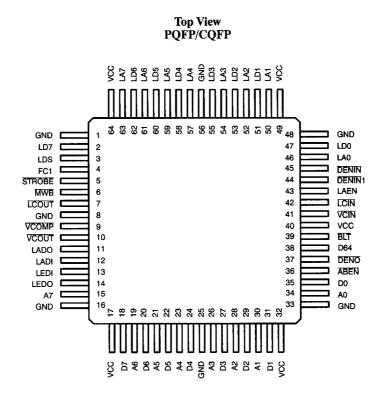

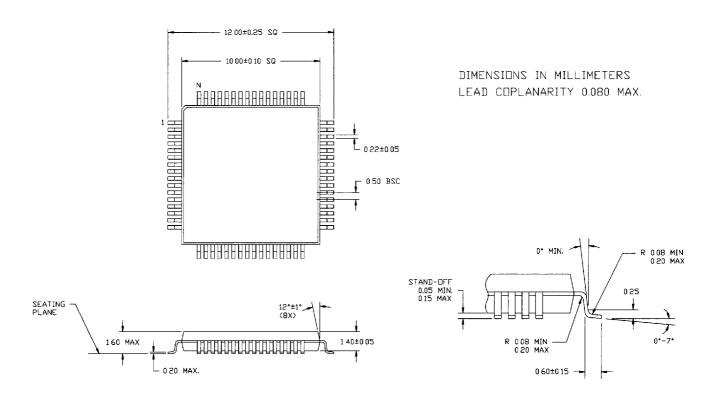

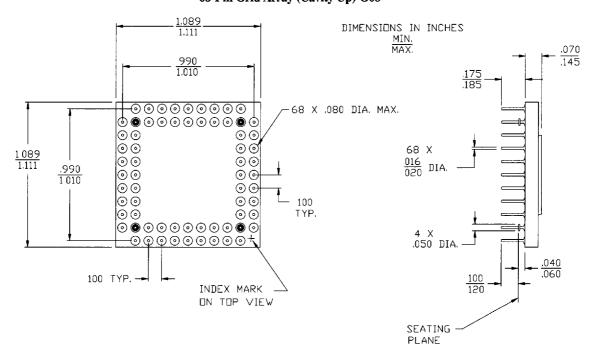

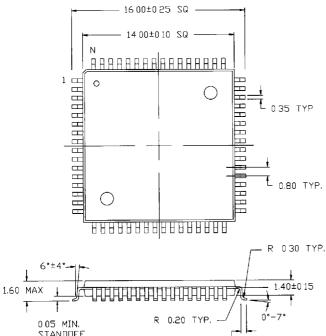

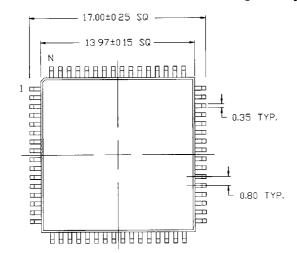

- Is available in a 64-pin QFP or 68-pin PGA

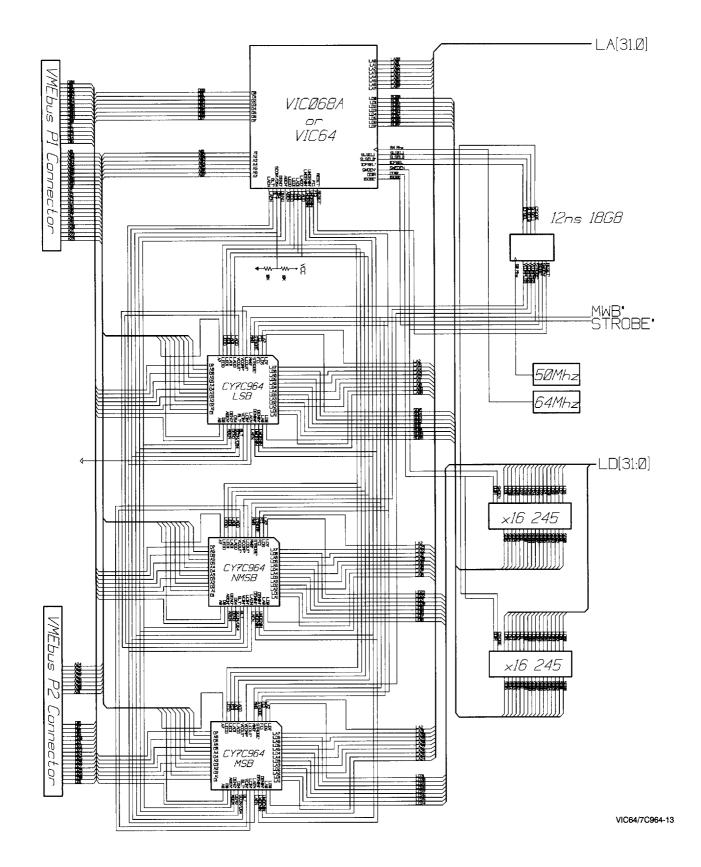

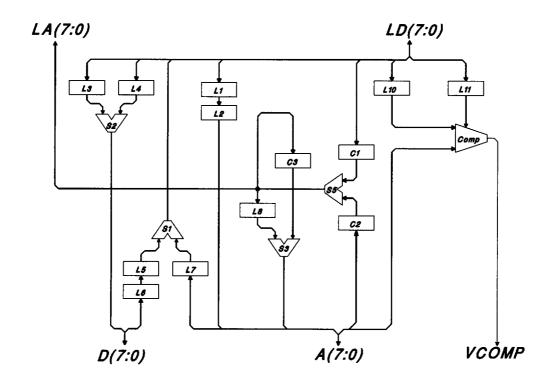

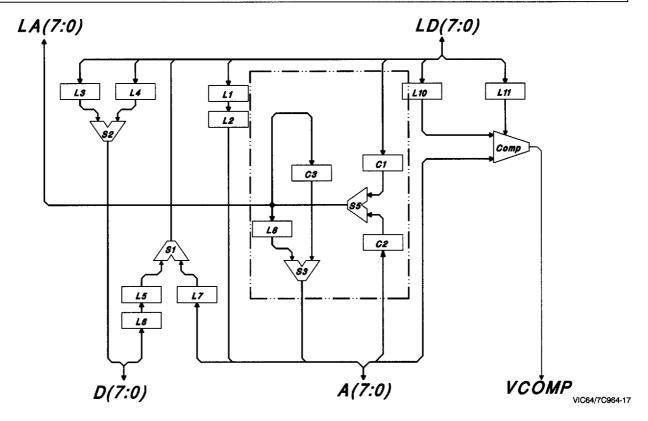

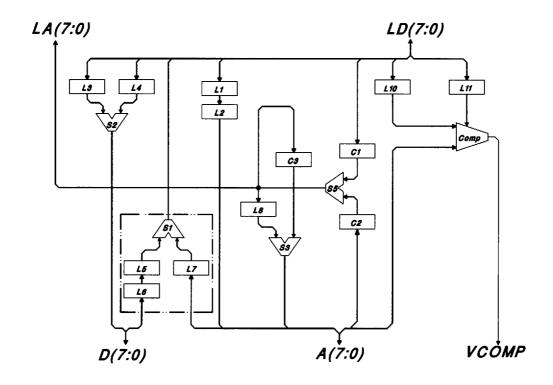

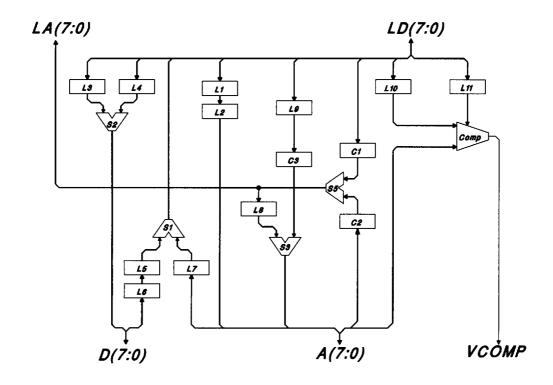

Figure 10. Full Function D64 VMEbus Interface

# Interfacing to the VIC64 and VIC068A

Previously, interfacing the VIC068A to the VMEbus required a significant amount of LSI and MSI devices. With the advent of 64-bit VMEbus block transfers and the VIC64, the external discrete device count for a full functional interface has expanded. The CY7C964 has been developed to combat this problem by incorporating the functions of much of this external logic into a single package. Using the CY7C964 shortens system design, debug, and manufacturing cycle times. Design engineers are relieved from the burden of performing critical or worst-case timing analysis on the VMEbus and VIC buffer control signals. Local control signals other than those directly interfaceable to the VIC64 or VIC068A have been kept to a minimum.

Figure 10 shows a full function D64 VMEbus interface implemented using the CY7C964, VIC64, and all VMEbus interface local support logic. This interface features:

- Block transfer support for D16, D32, and D64 VMEbus transfers

- Dual-path address operation (allowing single-cycle transfers during master block transfer interleave periods)

- Slave block transfers during master block transfer interleave periods

- Fully programmable slave VMEbus address decoding

- Write posting

- The VIC mail box interrupt message support

The interface can be broken into six functional sections for the purpose of discussion. These sections are:

- VMEbus signal group

- VIC buffer control signal group

- CY7C964 local signal group

- CY7C964 address comparator and local signal group

- Local data swap buffer logic

- VIC local control signal group

The focus of this section is the CY7C964. Each of the interface functional blocks are examined from this perspective. The CY7C964s will be referred to as the LSB, NMSB, and MSB device depending on the segment of the VMEbus that they control. The LSB controls VMEbus address and data signals [15:8], NMSB [23:16], and MSB [31:24]. This interface uses the CY7C964s in the Byte Width mode as address and data controllers. All of the information contained within this section is pertinent to this mode of operation. Refer to the Operation section of this document for information on the Word Width (16-bit address control) mode of the device. For additional information on the signals described within this section, consult the VMEbus Specification (IEEE 1014) and/or Cypress Semiconductor's VIC068A/VAC068A User's Guide.

**Table 4. VMEbus Signals**

| Signal | Description                       | Interface Comments                              |

|--------|-----------------------------------|-------------------------------------------------|

| D[7:0] | VMEbus compatible data signals    | Directly connect to VMEbus P1 and P2 connectors |

| A[7:0] | VMEbus compatible address signals | Directly connect to VMEbus P1 and P2 connectors |

## VMEbus Signal Group

This group includes the VMEbus address and data signals. Each CY7C964 provides support for 8 bits of VMEbus address and data. Three CY7C964s are necessary for 32-bit interface applications when used

with the VIC068A or VIC64. The A[7:0] and D[7:0] transceivers on the CY7C964 furnish a high drive strength, allowing direct connection to the respective address and data signals on the VMEbus backplane. With the VIC068A or VIC64 generating the control information, the CY7C964s meet VMEbus worst-case timing and drive-strength requirements for all forms of data transfers.

## **VIC Buffer Control Signal Group**

This group includes all of the VIC buffer control signals. A major design time savings is realized using the CY7C964s as all of these signals directly connect to the VIC or are hard-wired to a steady state value. The buffer control interface is simple and straight forward with the minor exception that the connection of UW-DENIN\* and LWDENIN\* control signals from the VIC are swapped to the DENIN\* and DENIN1\* on the LSB CY7C964. See *Table 5* for further information on the connection of these signals.

**Table 5. Buffer Control Signals**

| Signal  | Description                     | Interface Comments                                                                                             |

|---------|---------------------------------|----------------------------------------------------------------------------------------------------------------|

| LADO    | Latch address out               | Directly connect to VIC LADO on all CY7C964s.                                                                  |

| LADI    | Latch address in                | Directly connect to VIC LADI on all CY7C964s.                                                                  |

| LEDO    | Latch enable data out           | Directly connect to VIC LEDO on all CY7C964s.                                                                  |

| LEDI    | Latch enable data in            | Directly connect to VIC LEDI on all CY7C964s.                                                                  |

| ABEN*   | VMEbus address bus enable       | Directly connect to VIC ABEN* on all CY7C964s.                                                                 |

| DENO*   | Data enable output              | Directly connect to VIC DENO* on all CY7C964s.                                                                 |

| D64     | D64 block transfer mode enable  | Directly connect to VIC64 SCON/D64 pin on all CY7C964s. Tie this input LOW on all CY7C964s when using VIC068A. |

| BLT*    | Block transfer enable           | Directly connect to VIC BLT* on all CY7C964s.                                                                  |

| LAEN    | Local address enable            | Directly connect to VIC LAEN on all CY7C964s.                                                                  |

| DENIN*  | Primary data enable in signal   | Directly connect to VIC UWDENIN* on NMSB and MSB CY7C964s, directly connect to VIC LWDE-NIN* on LSB CY7C964.   |

| DENIN1* | Companion data enable in signal | Directly connect to VIC LWDENIN* on NMSB and MSB CY7C964s, directly connect to VIC UWDENIN* on LSB CY7C964.    |

## CY7C964 Local Signal Group

The CY7C964 local signal group consists of the VMEbus and local block-transfer counter count-enable daisy-chains. These signals enable the local and VMEbus higher-order address counters; two local address counters (a master block transfer and a slave block transfer) and a single VMEbus address counter. The local address counters share the LCIN\*/LCOUT\* count-enable daisy-chain. These signals are multiplexed within the CY7C964 and enable counting for the proper counter depending on the current state of the interface. The VCIN\*/VCOUT\* daisy-chain is dedicated to the VMEbus address counter on the device. When the VCIN\* or LCIN\* inputs are held Low, counting is enabled for the appropriate counters within the device. The VCIN\* and LCIN\* signals do not advance the counters, they just enable counting. The counters increment when these signals are active and the proper increment count control logic sequence

occurs. The VIC advances the address counters at the proper time during VMEbus and local DMA block transfer operations. For further information on the counter advance control sequence, refer to the CY7C964 Operation section of this document.

Table 6. CY7C964 Local Signals

| Signal | Description                         | Interface Comments                                                                                                                                                    |

|--------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCIN*  | Local address counter count enable  | On LSB CY7C964 tie this input LOW. On the NMSB device directly connect to the LCOUT* of the LSB device. For the MSB CY7C964 connect to the LCOUT* of the NMSB device. |

| LCOUT* | Local address counter carry out     | On LSB CY7C964 connect this output to the LCIN* input. On the NMSB CY7C964 connect this output to the MSB LCIN* input. For the MSB device do not connect this output. |

| VCIN*  | VMEbus address counter count enable | On LSB CY7C964 tie this input LOW. On the NMSB device directly connect to the VCOUT* of the LSB device. For the MSB CY7C964 connect to the VCOUT* of the NMSB device. |

| VCOUT* | VMEbus address counter carry out    | On LSB CY7C964 connect this output to the VCIN* input. On the NMSB CY7C964 connect this output to the MSB VCIN* input. For the MSB device do not connect this output. |

## CY7C964 Address Comparison and Local Signal Group

The implementation of this group of CY7C964 signals is application specific. The MWB\* signal and FC1 signal have been included in this section because they are locally generated signals required by the VIC. These two signals differ slightly on the VIC; MWB\* is an input only, while FC1 is a bidirectional signal that can be driven by the VIC. On the CY7C964 the MWB\* and FC1 signals are inputs. These signals should be directly connected to the respective local signals on VIC.

Table 7. CY7C964 Address Comparison and Local Signals

| Signal  | Description                      | Interface Comments                                                                                                             |

|---------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| FC1     | Function code 1 signal           | Directly connect on all CY7C964s to the same local signal that drives the FC1 signal on the VIC.                               |

| MWB*    | Module wants VMEbus              | Directly connect on all CY7C964s to the same local signal that drives the MWB* signal on the VIC.                              |

| LDS     | Load register select signal      | Should be directly connected to LA2 for systems with 32-bit local bus. Refer to text below for further information.            |

| STROBE* | Latch register control signal    | Chip select—like signal for CY7C964 internal comparator mask and comparison registers. See text below for further information. |

| VCOMP*  | VMEbus address comparator output | Needs a small amount of external glue logic to validate and combine signals in a parallel high-performance fashion.            |

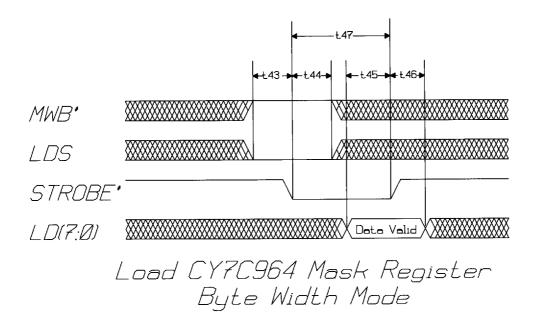

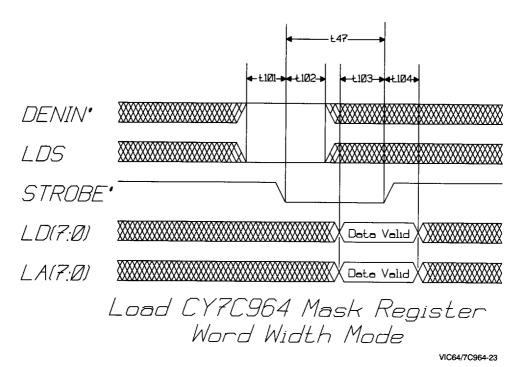

Figure 11. Mask Register Load Timing in Byte Width Mode

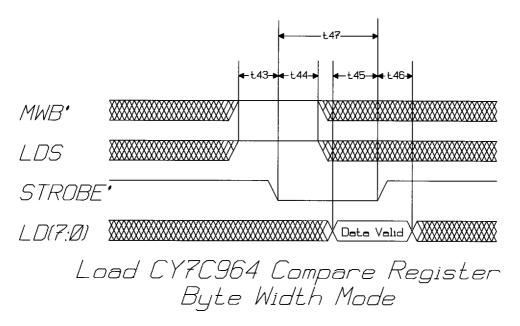

Figure 12. Compare Register Load Timing in Byte Width Mode

The CY7C964s contain a high-performance programmable VMEbus address equality comparator. The comparator is controlled by two internal, write-only registers, a mask, and a compare register. The mask register enables and disables bits of the comparator, and the compare register stores the data pattern that inputs are compared against. VCOMP\* is the active-Low comparator match output signal. VCOMP\* is driven Low by the CY7C964 when the bit pattern on pins A[7:0] match enabled bits of the compare register. Setting mask register bits to 0 enables the corresponding bits of the compare register. Loading bits of the mask register with 1's places bits of the compare register in don't care or match anything state. Loading the mask register with all 0's forces the compare register to match all bits of the pattern on A[7:0]. Setting the mask register to all 1's effectively disables the on-board comparator. VCOMP\* will always be Low.

These registers are loaded by supplying the proper data on LD[7:0] and the register address on MWB\* and LDS signals. The STROBE\* input is used to qualify the address and latch the data into the proper internal register. Figure 11 and Figure 12 show the waveforms needed to load the compare and mask registers.

This load cycle operates as follows:

- 1. The state of LDS and MWB\* are latched on the falling edge of STROBE\*.

- 2. The data is loaded into the selected register on the rising edge of the STROBE\* signal.

- 3. MWB\* must be held inactive (High): the state of LDS selects the register to load.

- 4. If LDS is High at the falling edge of STROBE\*, the compare register will be loaded; if LDS is Low the data is written to the mask register.

This load cycle can be generated by decoding a separate address region or chip select signal for the CY7C964 comparator registers. In applications with a 32-bit local data bus, it is desirable to load all three CY7C964s in parallel by having the host processor perform a 32-bit write cycle to the address region that will activate STROBE\*. The select signal for the address region is connected to the STROBE\* input on all three CY7C964s. The 8 bits of data on the lowest-order section of the data bus does not matter to the VIC, as long as the VIC CS signal remains inactive during this write cycle. Boards that use this style of interface should connect LDS to LA2, thereby decoding the mask register at the base address of the address region and the compare register at the base address +4. LDS also controls the operation of the D64 block transfer data multiplexer/demultiplexer. If it is not connected to LA2, this logic will not operate properly.

```

C18G8;

{ VMEbus address decode CY7C964 support logic PLD Cypress Semiconductor 12ns

18G8 PLD }

CONFIGURE;

{ 32 MHz Clock }

CLK 32 (node=1),

{ LSB CY7C964 VCOMP* output signal }

LSB VCOMP*(node=2),

{ NMSB CY7C964 VCOMP* output signal }

NMSB VCOMP*(node=3),

{ MSB CY7C964 VCOMP* output signal }

MSB VCOMP*(node=4),

{ CY7C964 STROBE* register load signal }

STROBE* (node=5),

{ System resent signal }

SYSTEM RESET (node=6),

{ Node Declaration }

{ Signal used to ENABLE to the SLESELO, SLSEL1, and ICFSEL to the VIC }

ENABLE (node=12, noreg, iop),

{ Delay ICFSEL signal used to filter ICFSEL output to VIC }

DICFSEL (node=13),

{ Delay SLSEL1 signals used to filter SLSEL1 output to VIC }

DSLSEL1 (node=14),

{ Delay SLSELO signals used to filter SLSELO output to VIC }

DSLSEL0 (node=15),

{ Filtered SLSEL1 output to VIC }

SLSEL1 (node=17),

{ Filtered SLSELO output to VIC }

SLSEL0 (node=18),

{ Filtered ICFSEL output to VIC }

ICFSEL (node=19) ,

EOUATIONS;

{ Enable term built to disable VIC slave select signal generation until the

first register access has occurred to the CY7C964 }

/ENABLE=SYSTEM RESET * /STROBE*

+SYSTEM RESET * /ENABLE;

{ Generate \overline{\text{DICFSEL}} when \overline{\text{ENABLE}} has been activated and \overline{\text{LSB VCOMP*}} is active}

/DICFSEL=/LSB VCOMP* * /ENABLE * SYSTEM RESET;

\{ Filter ICFSEL output by ANDing the DI\overline{\text{CFSEL}} and the LSB VCOMP* signal this

method forces the output to remain stable for two clock cycles. }

/ICFSEL=/DICFSEL * LSB VCOMP* * /ENABLE * SYSTEM RESET;

{Generate DSLSELO when ENABLE has been activated and NMSB VCOMP* is active }

/DSLSEL0=/NMSB_VCOMP* * /ENABLE * SYSTEM_RESET;

{ Filter SLSELO output by ANDing the DSLSELO and the NMSB VCOMP* signal this

method forces the output to remain stable for two clock cycles }

/SLSEL0=/DSLSEL0 * /NMSB_VCOMP* * /ENABLE * SYSTEM RESET;

{ Generate DSLSEL1 when ENABLE has been activated and both MSB VCOMP* and

NMSB VCOMP* are active }

/DSLSEL1=/MSB_VCOMP* * /NMSB VCOMP* * /ENABLE * SYSTEM RESET;

{ Filter SLSEL1 output by ANDing the DSLSEL1 and the MSB VCOMP* and NMSB VCOMP*

signals allows greater than 8 bits of VMEbus address decoding }

/SLSEL1=/MSB VCOMP* * /NMSB VCOMP* * /DSLSEL1 * /ENABLE * SYSTEM_RESET;

```

Figure 13. PLD Toolkit<sup>TM</sup> Design File

The mask and compare registers can be set to select any contiguous address region on the VMEbus. These registers do not preload and can power up in any state. It is advisable to initialize these registers as soon as possible in the system boot sequence. Note that the act of writing the compare register clears the mask register.

The CY7C964 comparator output signal VCOMP\* supplies the result from the equality compare logic. VCOMP\* drives Low when the input matches the loaded conditions. The CY7C964 VCOMP\* signals are not directly compatible with the VIC SLSEL0\* and SLSEL1\* slave select signals. The short (10 ns) address set up time to AS\* active for VMEbus slave boards, does not meet the worst case compare out delay of the CY7C964 VCOMP\* signal. Combining this with the potential output glitching that can occur with an asynchronous comparator can cause problems for the VIC. It is recommended that the VCOMP\* signal be externally filtered prior to being used with the VIC SLSEL0\* or SLSEL1\* signal. Most applications will require some external comparison logic to combine VCOMP\* signals from the NMSB and MSB device, furnishing finer grained VMEbus decoding: this logic can also be used to filter the CY7C964 VCOMP\* signals.

The interface in *Figure 10* uses a 12-ns 18G8 to perform these functions and disable the VMEbus slave select signals to the VIC until the first CY7C964 comparator register access has been performed. Using the PLD allows the interface to decode VMEbus addresses in three different regions:

- VMEbus A32 (for local access VIC SLSEL0)

- VMEbus A24 (for local access VIC SLSEL1)

- VMEbus A16 (for VIC mailbox interrupt and message VIC ICFSEL)

Figure 13 shows the PLD Toolkit design file for this device. The two VIC slave select signals, SLSEL0\* and SLSEL1\*, can be used to conveniently decode two VMEbus address regions. SLSEL0\* will select if the NMSB CY7C964 becomes True. SLSEL1\* requires both NMSB and MSB comparators to evaluate True.

A 32-MHz clock and the D registers within the 18G8 are used to build a simple digital filter which removes any glitches that may occur on the CY7C964 VCOMP\* signals.

As mentioned previously, the comparators within the CY7C964s are always active, and power up in an unknown state. The PLD includes an Enable signal that disables the SLSEL0\*, SLSEL1\* and ICFSEL\* signals to the VIC until the first access is made to one of the comparator control registers. Adding the Enable function to this PLD guarantees that the VIC slave select signals can not become active until one of the comparator control registers has been initialized.

## **Local Data Swap Buffer Logic**

Local Data Swap Buffer logic is a requirement for all 32-bit local bus designs that perform 8- or 16-bit transfers. The swap buffer moves data to and from the lower section of the VMEbus, D[15:0], to the upper segments of the local bus, D[31:16]. VMEbus requires that all 8- and 16-bit data transfers be performed on the D[15:0] section of the bus. The CY7C964s work properly with the VIC-controlled swap buffer. If an isolation buffer is implemented, care should be taken to ensure that the local data bus is driven to the least-significant CY7C964 during address/mask register programming cycles. One way to ensure this is to assert the  $\overline{\text{CS}}$  and  $\overline{\text{PAS}}$  signals to the VIC068/VIC64, thus causing VIC to assert the  $\overline{\text{ISOBE}}$  signal to the isolation buffer.

## **VIC Local Control Signal Group**

All VIC local interface signals that have not been discussed are not impacted when using the CY7C964s. For further information on the local VIC interface refer to the VIC068A/VAC068A User's Guide.

# **Signal Descriptions**

## **VMEbus Signals**

A[7:0]

Input: Yes

Output: Yes, three-state

Drive  $(I_{OL})$ : 48 mA

These are VMEbus-compatible address signal transceivers that can be directly connected to the VMEbus. A0 is the least significant address bit. In flow-through modes of operation, these signals correspond one for one with local interface signals LA[7:0].

In VMEbus interface applications including those using the VIC068A or VIC64, these signals should be connected to the VMEbus address bus sequentially.

D[7:0]

Input: Yes

Output: Yes, three-state

Drive  $(I_{OL})$ : 48 mA

These are VME bus compatible data signal transceivers that can be directly connected to the VME bus. D0 is the least data signals. In flow-through modes of operation, these signals correspond one for one with local interface signals LD[7:0].

In VMEbus interface applications, including those using the VIC068A or VIC64, these signals should be connected to the VMEbus address bus sequentially.

#### **Local Signals**

LA[7:0]

Input: Yes

Output: Yes, three-state

Drive  $(I_{OL})$ : 8 mA

These are medium drive-strength local address transceivers that allow direct connection to memory, microprocessors and/or peripheral controllers. LA0 is the least-significant local address signal. In flow-through operating modes these signals correspond one for one with the VMEbus signals A[7:0].

When implementing conventional VMEbus interfaces or using the CY7C964 with the VIC068A or VIC64, these signals should be connected to the local bus sequentially.

LD[7:0]

Input: Yes

Output: Yes, three-state

Drive  $(I_{OL})$ : 8 mA

These are medium drive-strength local address transaceivers that allow direct connection to memory, microprocessors, and/or peripheral controllers. LD0 is the least-significant local address signal. In flow-through operating modes these signals correspond one for one with the VMEbus signals D[7:0].

In VMEbus interface applications, including those using the VIC068A or VIC64, these signals should be connected to the local data bus sequentially.

#### ABEN\*

Input: Yes Output: No

Drive: None

This is the VMEbus Address Bus ENable control signal. This signal controls the state of the VMEbus address transceivers A[7:0]. When asserted (driven Low) the transceivers are configured as outputs and are enabled.

When using the CY7C964 with the VIC068A or VIC64 to implement VMEbus interfaces, this input should be connected to the ABEN\* output of the VIC.

## BLT\*

Input: Yes

Output: No

Drive:

None

This signal controls the VIC-compatible block transfer operations that require local Direct Memory Access (DMA). If this input is driven Low, the CY7C964 will operate in the appropriate VIC-compatible block transfer mode (dependent on the states of the other buffer control logic).

When using the CY7C964 with the VIC068A or VIC64, this signal can be directly connected to the VIC BLT\* pin. A rising edge on BLT\* increments the local address counters if LCIN\* is Low. Refer to the LCIN\* signal description and the CY7C964 Operation section of this document for further information on the local address counter function.

## D64

Input: Output:

Drive:

No None

Yes

This signal is used to indicate to the CY7C964 that a VMEbus D64 block transfer is in progress. When High, the CY7C964 is instructed to use the high-performance two-state pipeline and multiplex or demultiplex 64-bit data to and from the VMEbus address bus.

When used in conjunction with the VIC64, this pin can be directly connected to the SCON\*/D64 signal. For applications that only support 32-bit block transfers, as is the case with the VIC068A, this input should be tied Low.

## **DENIN\***

Input:

Output:

Drive:

No None

Yes

The Data ENable IN signal is used to control the three-state data transceivers LD[7:0]. If a logic Low level is presented to this input, LD[7:0] transceivers will be enabled. In conventional VMEbus designs, this signal would need to be driven during master read or slave write operations.

When used in conjunction with the VIC068A or VIC64, this input is typically connected to UWDENIN\* for CY7C964's controlling bus data lines D16 through D31, and to LWDENIN\* for the CY7C964's controlling bus data lines D8 through D15.

## DENIN1\*

Input: Yes

Output: No

Drive: None

The Data ENable IN 1 signal is used in conjunction with DENIN\* to latch data from the VMEbus and provide a second enable control of the LD[7:0] transceivers for D64 transactions.

When used in conjunction with VIC64, this input is typically connected to LWDENIN\* for CY7C964's controlling data bus signals D16 through D31 and to UWDENIN\* for the CY7C964 controlling data bus signals D8 through D15.

#### DENO\*

Input: Yes

Output: No

Drive: None

The Data ENable Out signal is used to control the three-state transceivers D[7:0]. If a logic-Low level is presented to this input, the D[7:0] transceivers will be enabled. In conventional VMEbus design, the D[7:0] signals will be directly connected to the VMEbus. Used in this manner, this input must be asserted during master writes and slave read operations.

When used in conjunction with the VIC068A or VIC64, this signal should be connected to the DENO\* output on the VIC.

#### FC1

Input: Yes

Output: No

Drive: None

The Function Code 1 input is used by the CY7C964 during block transfer operations to determine the source for the local address signals LA[7:0]. If the input is driven High the internal Local DMA counter is selected as the source for LA[7:0]. If this input is Low, the Slave Block Transfer counter is the source for LA[7:0].

When used with the VIC068A or VIC64, this signal can be directly connect to the FC1 bidirectional pin on VIC. VIC will drive this pin to the proper level for slave or block transfer operations when it is master of the local system bus.

#### LCOUT\*

Input: No

Output: Yes

Drive: 8 mA

The Local Carry Out signal is used by the CY7C964 for cascading the local address counter chains. This signal will drive Low when the local address counter has reached the maximum count (255). The signal

generates a synchronous count enable for the next-most-significant CY7C964 in the cascade chain. This signal alone does not cause the local address counter to increment.

When cascading the CY7C964s, this signal should be connected to the LCIN\* input pin of the next most significant device. Refer to the description of the LCIN\* pin for further information on the operation of the local address counters.

## LDS

Input: Yes

Output: No

Drive: None

The Local Data Select input has two main functions: (1) as a control input for the data to address bus multiplexer during D64 VMEbus block transfers, (2) as a select bit for configuring the CY7C964 address comparison and mask registers. Refer to the operation section of this document for further information about how data is steered to and from the VMEbus address bus during block transfers. Typically this input will be connected to LA2. It must be connected to LA2 for proper operation when using the VIC068A or VIC64.

When configuring the CY7C964 internal address mask and address compare registers, this pin in conjunction with MWB\* selects which registers to load. During a comparator register load cycle, LDS High will select the Address Compare register; otherwise the Address Mask register will be selected. Refer to the section called Interfacing to the VIC64 and VIC068A for further information on loading the address comparator control registers.

## **LADI**

Input: Yes

Output: No

Drive: None

The Latch ADdress In signal controls a transparent VMEbus to local address latch within the CY7C964. When this input is High, the device will latch the data present on A[7:0]. This function is useful when building VMEbus interfaces for latching the VMEbus address during a slave access. If LADI is Low, the internal address latch will be in a flow-through mode. LADI\* is also used to increment the slave block transfer local address counter. LADI is used in conjunction with LAEN to control the operation of the address VMEbus to local address section of the CY7C964. For more information, refer to the description of LAEN.

When using the CY7C964 to implement VMEbus interfaces, this signal is used to maintain the local address during slave read and write cycles. For VMEbus designs that use the VIC068A or VIC64, this input should be connected to the LADI output of the VIC.

#### **LAEN**

Input: Yes

Output: No

Drive: None

The Local Address ENable signal controls the three-state enable for signals LA[7:0]. When this signal is High, LA[7:0] drive the address local bus. Driving the signal Low places LA[7:0] in the high-impedance/input state.

When using the CY7C964 to implement VMEbus interfaces, this signal is driven High to maintain the local address VMEbus during slave cycles. For VMEbus interfaces using the VIC068A or VIC64, this pin should be connected to the LAEN output on the VIC.

#### **LEDI**

Input: Yes

Output: No

Drive: None

The Latch Enable Data In signal controls a transparent VMEbus-to-local-data-bus latch within the CY7C964. When this input is High, the device will latch the data present on D[7:0]. This function is useful when building VMEbus interfaces for latching the VMEbus data during a master or slave access. If LEDI is Low, the internal address latch will be in a flow-through mode.

LEDI is used in conjunction with DENIN\* and DENIN1\* to control the operation of the address VME-bus-to-local data section of the CY7C964. For additional information, refer to the description of DENIN\* and DENIN1\*.

When implementing VMEbus interfaces with the CY7C964, LEDI can be used to maintain the local data during VMEbus master read and slave write cycles. For VMEbus designs that use the VIC068A or VIC64, this input should be connected to the LEDI output of the VIC.

#### **LEDO**

Input: Yes

Output: No

Drive: None

The Latch Enable Data Out signal controls a transparent local-data-to-VMEbus-data latch within the CY7C964. When this input is High, the device will latch the data present on LD[7:0]. This function is useful when building VMEbus interfaces for latching the VMEbus data during a master or slave access. If LEDO is Low the internal address latch will be in a flow-through mode.

LEDO is used in conjunction with DENO\* to control the operation of the local-to-VMEbus data section of the CY7C964. For further information, refer to the description of DENO\*.

When implementing VMEbus interfaces with the CY7C964, LEDO can be used to maintain the VMEbus data during VMEbus master write or slave read cycles. For VMEbus designs that use the VIC068A or VIC64, this input should be connected to the LEDO output of the VIC.

#### LADO

Input: Yes

Output: No

Drive: None

The Latch Address Out signal controls a transparent local-to-VMEbus address latch within the CY7C964. When this input is High, the device will latch the data present on LA[7:0]. This function is useful when building VMEbus interfaces for latching the local address during a master transfers. If LADO is Low the internal address latch will be in a flow-through mode.

LADO is used in conjunction with ABEN\* to control the operation of the local-to-VMEbus address section of the CY7C964. For further information, refer to the description of ABEN\*.

When using the CY7C964 to implement a VMEbus interface, this signal can be used to maintain the local address during slave read and write cycles. For VMEbus designs that use the VIC068A or VIC64, this input should be connected to the LADO output of the VIC.

#### LCIN\*

Input: Yes

Output: No

Drive: None

Local Carry IN is a synchronous count enable for both the local master block transfer and slave block transfer local address counters. LCIN\* is multiplexed within the CY7C964 and can be routed to either local block transfer address counter. When connected to the master block transfer local address counter, if LCIN\* is driven Low, a falling edge on the BLT\* signal will increment the address count. When this input is connected to the slave block transfer counter and driven Low, a rising edge of LADI will increment the address count.

When cascading CY7C964s, this signal should be connected to the LCOUT\* signal of the next-least-significant device.

## MWB\*

Input: Yes

Output: No

Drive: None

The Module Wants Bus is a decoding/control signal for the CY7C964 that allows the device to discern the cycle type. When MWB\* is active (Low), the CY7C964 assumes that a block transfer initiation cycle of a single-cycle VMEbus transfer is pending. Subsequent assertion of BLT\* allows the CY7C964 to enter block transfer mode.

MWB\* is also used to decode accesses to the CY7C964 address Mask and Compare registers. To load these registers MWB\* must be inactive (High).

Refer to the Interfacing to the VIC64 and VIC068A section for further information on the use of MWB\* to load the Address Mask and Compare registers.

## STROBE\*

Input: Yes

Output: No

Drive: None

The STROBE\* signal controls the loading of the internal Address Mask and Compare registers. This signal operates in the same manner as an active-Low chip select for these registers. When STROBE\* is Low and MWB\* is High, data present on LD[7:0] will be loaded into either the Address Mask or Compare registers.

Refer to the CY7C964 Operation section for further information on the use of MWB\* to load the Address Mask and Compare registers.

## VCOMP\*

Input: No

Output: Yes

Drive: 8 mA

The VMEbus COMPare signal indicates whether the address presented on A[7:0] matches the significant bit of the internal Address Compare register. If the two values are determined to match, VCOMP\* will drive Low. (Note: The Address Mask register can mask compare bits, causing these bits match anything.)

Refer to the section called 3 Interfacing to the VIC64 or VIC068A for further information on the use of MWB\* to load the Address Mask and Compare registers.

This signal is the output of an asynchronous comparator and is therefore susceptible to glitching during address transitions on A[7:0]. When used in conjunction with the VIC64 or VIC068A for conventional VMEbus implementations, these signals should be de-glitched externally. External logic is required to cascade VCOMP\* comparison outputs.

## VCIN\*

Input: Yes

Output: No

Drive: None

The VMEbus Carry IN is a synchronous count enable for the local address counters. When VCIN\* is Low and the device is not operating in the Dual-Address-Path mode, a rising edge on the LADO signal will increment the VMEbus address counter.

When cascading CY7C964s, this signal should be connected to the VCOUT\* signal of the next-least-significant device.

For more information on the Dual-Address-Path mode, refer to the CY7C964 Operations sections.

#### **VCOUT\***

Input: No

Output: Yes

Drive: 8 mA

The VMEbus Carry Out signal is used by the CY7C964 for cascading the VMEbus address counter chains. This signal will drive Low when the VMEbus address counter has reach the maximum count (255). The signal generates a synchronous count enable for the next-most-significant CY7C964 in the cascade chain. This signal alone does not cause the VMEbus address counter to increment.

When cascading CY7C964s, this signal should be connected to the VCIN\* input pin of the next-most-significant device. Refer to the description of the VCIN\* pin for further information on the operation of the VMEbus address counters.

Figure 14. CY7C964 Block Diagram

## **CY7C964 Byte Width Mode Operation**

## Overview

The CY7C964 is a general-purpose bus interface device that provides seamless support for the VIC64/VIC068A family VMEbus interface controllers. The part is also suitable for many other general-purpose bus interface applications. *Figure 14* is the block diagram of the device, showing the array of latches, multiplexers, and counters.

This section of the document dissects the high-level block diagram into lower-level functional blocks. General operational and timing information is presented on a block-by-block basis. This information is provided for designers who wish to implement non-VIC-controlled interfaces. The tables show the control signal logic sequence needed to operate or communicate with each of the functions. Timing parameters are included, which reference the switching characteristics listed later in this document.

The CY7C964 operation is controlled by the combination of external control signals and internal state logic. Three internal asynchronous state bits control the operating mode of the device. These bits are referred

to as BLT\_STATE, BLT\_INIT, and DUAL\_PATH. The BLT\_STATE bit is set during VIC block transfer operations. The VIC block transfer initiation cycle generates a rising edge on the BLT\_INIT signal. The DUAL\_PATH signal is the output of a transparent latch within the device that latches the state of LADO. These internal state bits must be in the proper state to use and communicate with the internal logic of the device. The functional tables include references to these signals when their state is required for the operation. The designer must perform the appropriate cycle to the device to set or clear these latches as needed prior to the desired functional cycle. The internal latch signals and all other control signals that are not called out within the tables for a specific operation can be considered don't cares.

**Table 8. Examples of References to Control Signals Within Functional Tables**

```

Note 1: BLT_STATE=(/BLT* * /MWB*) + (BLT_STATE * (/BLT* + /MWB* + LAEN))

Note 2: BLT_INIT=(/BLT*_STATE * /BLT* * /MWB*) + (BLT_INIT * /BLT* * /MWB*)

Note 3: DUAL_PATH=(LADO * BLT_INIT) + (DUAL_PATH * /BLT_INIT)

```

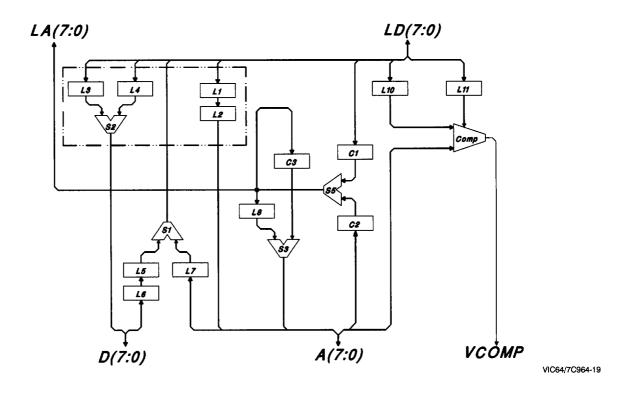

Figure 15. CY7C964 Block Diagram: Address Counters and Address Multiplexers

## **Master Block Transfer Local Address Counter (C1)**

The Master Block Transfer Local Address Counter supplies the local address to LA[7:0] during master block transfer operations. This 8-bit synchronous counter is cascadable using the LCIN\*/LCOUT\* daisy-chain. The counter powers up in an uninitialized state and must be initialized for predictable operation. The counter loads from LD[7:0] when both MWB\* and BLT\* control signals are active (Low). To enable

the counter onto LA[7:0], an internal asynchronous latch (BLT\_STATE) must be set and Local Address Multiplexer S5 must select counter C1. A falling edge on MWB\* or BLT\* increments C1. FC1 controls S5. If it is High, as shown in Table 10., C1 is selected. The internal latch and S5 multiplexer must also be in the proper state to increment the counter. For further information on the S5 Local Address Multiplexer, see the next section.

Table 9. Master Block Transfer Local Address Counter Operation

| Logic | Functional Description              | Operational Description            | Required Condition                         | Parameter  |

|-------|-------------------------------------|------------------------------------|--------------------------------------------|------------|

| C1    | Load counter                        | LD[7:0] valid to falling edge of   | BLT*=0, LAEN=0                             | Set-up t48 |

|       |                                     | MWB*                               |                                            | Hold t49   |

|       |                                     | LD[7:0] valid to falling edge of   | MWB*=0, LAEN=0                             | Set-up t50 |

|       |                                     | BLT*                               |                                            | Hold t51   |

|       | Increment counter                   | MWB* falling edge to LA[7:0] valid | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Prop t54   |

|       |                                     | BLT* falling edge to LA[7:0] valid | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Prop t54   |

|       |                                     | LCIN* valid to MWB* falling edge   | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Set-up t52 |

|       |                                     |                                    |                                            | Hold t53   |

|       |                                     | LCIN* valid to BLT* falling edge   | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Set-up t52 |

|       |                                     |                                    |                                            | Hold t133  |

|       | Counter carry out at terminal count | MWB* falling edge to LCOUT* valid  | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Prop t55   |

|       |                                     | BLT* falling edge to LCOUT* valid  | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Prop t55   |

|       |                                     | LCIN* valid to LCOUT* valid        | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | Prop t56   |

|       | Minimum pulse widths                | BLT*                               | LAEN=1, FC1=1,<br>BLT_STATE=1 <sup>1</sup> | t57        |

|       |                                     | MWB*                               |                                            | t57        |

# **Local Address Multiplexer (S5)**

The Local Address Multiplexer S5 routes the outputs of counters C1 or C2 to signals LA [7:0]. The local address counter carry chain LCIN\*/LCOUT\* is also controlled by this multiplexer. If FC1 is High counter C1 drives LA[7:0] and LCIN\*/LCOUT\* are visible/driven by C1, respectively. When FC1 is Low, C2 drives LA [7:0] and is attached to the LCIN\*/LCOUT\* daisy-chain.

Table 10. Local Address Multiplexer Operation

| Logic | <b>Functional Description</b> | Operational Description            | Required Condition | Parameter |

|-------|-------------------------------|------------------------------------|--------------------|-----------|

| S5    | Select C1 counter             | FC1 rising edge to LA [7:0] valid  |                    | Prop t85  |

|       | Select C2 counter             | FC1 falling edge to LA [7:0] valid |                    | Prop t86  |

|       | Select C1 carry chain         | FC1 rising edge to LCOUT* valid    |                    | Prop t88  |

|       | Select C2 carry chain         | FC1 falling edge to LCOUT* valid   |                    | Prop t87  |

## Slave Block Transfer Local Address Counter/Latch (C2)

The Slave Block Transfer Local address counter provides two functions: a counter for slave block transfer operations and a transparent address latch for VMEbus slave operations. When the latch control signal LADI is held Low the counter is in a transparent mode: Logic levels present will flow through the device to the inputs of the local address multiplexer S5. FC1 controls the S5 multiplexer and must be Low to select counter C2 as the source for LA[7:0]. Driving either LADI or D64 High exclusively latches the data present on A[7:0]. The counter increments if LCIN\* is Low, D64 is High, and a rising edge occurs on LADI. The contents of the counter/latch are enabled onto the local data bus when LADI and FC1 are Low and D64 is High. Counter C2 is not initialized at power-up; for predictable operation the counter should be loaded prior to use.

Table 11. Slave Block Transfer Local Address Counter/Latch Operation

| Logic | <b>Functional Description</b>            | Operational Description          | Required Condition | Parameter  |

|-------|------------------------------------------|----------------------------------|--------------------|------------|

| C2    | Load counter                             | A[7:0] valid to D64 rising edge  | LADI=0             | Set-up t58 |

|       |                                          |                                  |                    | Hold t59   |

|       |                                          | A[7:0] valid to LADI rising edge | D64=0              | Set-up t60 |

|       |                                          |                                  |                    | Hold t61   |

|       | Increment counter                        | LADI rising edge to LA[7:0]      | D64=1, FC1=0       | Prop t64   |

|       |                                          | LCIN* active to LADI rising edge | D64=1              | Set-up t62 |

|       |                                          |                                  |                    | Hold t63   |

|       | Counter carry out at ter-<br>minal count | LADI rising edge to LCOUT*       | D64=1, FC1=0       | Prop t65   |

|       | Minimum pulse width                      | LADI                             |                    | t66        |

## **Master Block Transfer VMEbus Address Counter (C3)**

The VMEbus Master Block Transfer Address stores and increments the VMEbus address during master block transfer operations. The counter loads from LA[7:0] on the rising edge of MWB\* provided that the internal asynchronous latch BLT\_STATE is set. The contents of the counter are enabled onto the A[7:0] pins if the internal asynchronous latch bits BLT\_STATE and multiplexer S3 are in the appropriate state. Depending on the state of DUAL\_PATH, either the rising or the falling edge of LADO increments C3. Counter C3 uses the VCIN\*/VCOUT\* counter daisy-chain. This counter is uninitialized at power-up and should be initialized prior to use for predictable operation.

Table 12. Master Block Transfer VMEbus Address Counter Operation

| Logic | Functional Description | Operational Description                 | Required Condition                                                     | Parameter   |

|-------|------------------------|-----------------------------------------|------------------------------------------------------------------------|-------------|

| C3    | Load counter           | LA[7:0] valid to rising edge of         | BLT_STATE=11                                                           | Set-up t67  |

|       |                        | MWB*                                    | BLT_INIT=1                                                             | Hold t68    |

|       | Increment counter      | LADO falling edge to A[7:0]             | BLT_STATE=1 <sup>1</sup> ,<br>DUAL_PATH=1 <sup>3</sup> ,<br>BLT_INIT=0 | Prop t69    |

|       |                        | LADO rising edge to A[7:0]              | BLT_STATE=1 <sup>1</sup> ,<br>DUAL_PATH=0,<br>BLT_INIT=0               | Prop t70    |

|       |                        | VCIN* valid to LADO rising/falling edge |                                                                        | Set-up t134 |

|       |                        |                                         |                                                                        | Hold t135   |

|       | Counter carry out      | LADO falling edge to VCOUT* valid       | BLT_STATE=1 <sup>1</sup> ,<br>DUAL_PATH=1 <sup>3</sup> ,<br>BLT_INIT=0 | Prop t71    |

|       |                        | LADO rising edge to VCOUT* valid        | BLT_STATE=1 <sup>1</sup> ,<br>DUAL_PATH=0,<br>BLT_INIT=0               | Prop t72    |

|       | Minimum pulse width    | LADO (High)                             |                                                                        | t73         |

|       |                        | LADO (Low)                              |                                                                        | t73         |

## VMEbus Address Latch (L8) and Multiplexer (S3)

The VMEbus Address Latch and Multiplexer selects the source for the VMEbus address signals A[7:0]. The information supplied to A[7:0] originates at one of three sources: the D64 block transfer data pipeline latch L2, the VMEbus master block transfer counter C3, or the VMEbus address latch L8. Table 13 shows how to latch information into the VMEbus address latch L8 and control the selection of the source for signals A[7:0]. Latch L8 is uninitialized at power-up and for predictable operation should be loaded prior to use.

Table 13. VMEbus Address Latch and Multiplexer Operation

| Logic | Functional Description | Operational Description            | Required Condition       | Parameter  |

|-------|------------------------|------------------------------------|--------------------------|------------|

| S3    | Select L8              | D64 falling edge to A[7:0] valid   | BLT_STATE=1 <sup>1</sup> | Prop t83   |

|       |                        | ABEN* falling edge to A[7:0] valid | BLT_STATE=1 <sup>1</sup> | Prop t84   |

|       |                        | D64 falling edge to A[7:0] valid   | BLT_STATE=0              | Prop t81   |

| L8    | Load L8                | LA[7:0] valid to LADO rising       |                          | Set-up t40 |

|       |                        | edge                               |                          | Hold t41   |

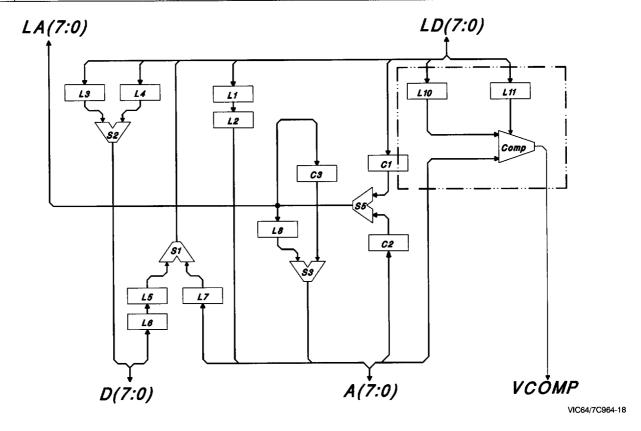

Figure 16. CY7C964 Block Diagram: VMEbus Address Comparator

## VMEbus Address Comparator

The VMEbus Address Comparator is made up of three logic elements: an address mask register, address compare register, and a high-performance, 8-bit, equality comparator. The compare and mask registers control the compare logic. The mask register contains an 8-bit value that enables or disables bits of the comparator. The compare register contains an 8-bit pattern. The enabled bits of the compare register are matched against the value on A[7:0]. If a match is detected (all active bits equal), the VCOMP\* output pin is driven Low. Neither the compare register nor the mask register are preset at power-up and must be initialized for predictable operation. The act of writing the compare register clears the mask register. This prevents any inadvertant address compares during the configuration process. See the Interfacing to the VIC64 and VIC068A section for further information on the VMEbus address comparator.

**Table 14. VMEbus Address Comparator Operation**

| Logic | Functional Description  | Operational Description                    | Required Condition | Parameter  |

|-------|-------------------------|--------------------------------------------|--------------------|------------|

| L10   | Select compare register | LDS, MWB* valid to<br>STROBE* falling edge | LDS=1, MWB*=1      | Set-up t43 |

|       |                         |                                            |                    | Hold t44   |

|       | Load compare register   | LD[7:0] valid to STROBE* rising edge       |                    | Set-up t46 |

|       |                         | Tioning dage                               |                    | Hold t47   |

| L11   | Select mask register    | LDS, MWB* valid to<br>STROBE* falling edge | LDS=0, MWB*=1      | Set-up t43 |

|       |                         |                                            |                    | Hold t44   |

|       | Load compare register   | LD[7:0] valid to STROBE*                   |                    | Set-up t46 |

|       |                         | rising edge                                |                    | Hold t47   |

|       | Compare out             | A[7:0] valid to VCOMP* valid               |                    | Prop t23   |

|       |                         | A[7:0] valid to VCOMP* invalid             |                    | Prop t24   |

|       | Minimum pulse width     | STROBE* minimum pulse width                |                    | t47        |

## VMEbus D64 Block Transfer Data Pipeline and Multiplexer

Latches L1 and L2 form a two-stage high-performance data pipeline for D64 block transfer operations. These latches load from the local signals LD[7:0], but drive VMEbus address signals A[7:0]. Latches L3 and L4 load from the local data signals LD[7:0] and in combination with multiplexer S2 drive D[7:0]. On the first cycle of a D64 block transfer data on LD[7:0] is written to latch L1. During the second local data fetch of a D64 block transfer operation (D64 = 1), data from LD[7:0] is written to latch L3 and the data within latch L1 moves to L2. Two fetches must be performed to form the 64-bit block transfer data word. During non-D64 modes of operation (D64=0) data from LD[7:0] is written to latch L4. This is the normal data path from LD[7:0] to D[7:0] for all non-D64 operation. Because all the latches are implemented on transparent latches, L2 may be loaded from LD[7:0] when L1 is transparent (LEDO=0). None of the latches are initialized at power-up. Therefore for predictable operation these latches should be written prior to their use.

Figure 17. CY7C964 Block Diagram: D64 Block Transfer Data Pipeline and Multiplexer

Table 15. VMEbus D64 Block Transfer Data Pipeline and Multiplexer Operation

| Logic | Functional Description                 | Operational Description           | Required Condition | Parameter   |

|-------|----------------------------------------|-----------------------------------|--------------------|-------------|

| L1    | Load register                          | LD[7:0] valid to LEDO rising edge |                    | Set-up t25  |

|       |                                        |                                   |                    | Hold t26    |

| L2    | Load register                          | LD[7:0] valid to DENO*            | LEDO=0             | Set-up t28  |

|       |                                        | falling edge                      |                    | Hold t29    |

|       | Drive A[7:0]                           | D64 rising edge to A[7:0] valid   | BLT_STATE=1        | Prop t82    |

| L3    | Load register                          | LD[7:0] valid to DENO*            |                    | Set-up t25  |

|       |                                        | rising edge                       |                    | Hold t26    |

| L4    | Load register                          | LD[7:0] valid to LEDO*            |                    | Set-up t131 |

|       |                                        | rising edge                       |                    | Hold t132   |

| S2    | Multiplexer selects L3<br>drive D[7:0] | D64 rising edge to D[7:0] valid   |                    | Prop t78    |

|       | Multiplexer selects L4<br>drive D[7:0] | D64 falling edge to D[7:0] valid  |                    | Prop t79    |

|       | Minimum pulse width                    | DENO*                             |                    | t30         |

|       |                                        | LEDO                              |                    | t27         |

Figure 18. CY7C964 Block Diagram: D64 Block Transfer Data Demultiplexer

## VMEbus D64 Block Transfer Data Demultiplexer

The VMEbus D64 block transfer data demultiplexer moves data from D[7:0]/A[7:0] to LD[7:0]. The demultiplexer consists of three latches-L5, L6, and L7-and an output multiplexer, S1. During D64 block transfer operations (D64=1), data is written to latches L6 and L7 simultaneously on the rising edge of LEDI. Multiplexer S1 then selects either latch L6 or L7, depending on the state of LDS as a source for LD[7:0]. In most applications, LDS should be connected to LA2, showing that L7 contains even 32-bit words (addresses 0, 8,  $10_{16...}$ ) and L6 contains odd 32-bit words (addresses 4, C,  $14_{16...}$ ). Latch L6 is also used for non-D64 operating modes. None of these latches are initialized at power-up and for predictable operation should be initialized prior to use.

Table 16. VMEbus D64 Block Transfer Data Demultiplexer Operation

| Logic | Functional Description  | Operational Description          | Required Condition | Parameters |

|-------|-------------------------|----------------------------------|--------------------|------------|

| L5    | Load register           | D[7:0] valid to DENIN*           | DENIN1*=0,         | Set-up t31 |

|       |                         | falling edge LEDI=0              | Hold t32           |            |

|       | D[7:0] valid to DENIN1* | N1* DENIN*=0, LEDI=0             | Set-up t34         |            |

|       |                         | falling edge                     |                    | Hold t35   |

| L6    | Load register           | D[7:0] valid to LEDI rising edge | LEDO=0             | Set-up t37 |

|       |                         |                                  |                    | Hold t38   |

| L7    | Load register           | A[7:0] valid to LEDI rising edge | LEDO=0             | Set-up t37 |

|       |                         |                                  |                    | Hold t38   |

Table 17. VMEbus D64 Block Transfer Data Demultiplexer Operation (Continued)

| Logic | Functional Description | Operational Description           | Required Condition | Parameter |

|-------|------------------------|-----------------------------------|--------------------|-----------|

| S1    | Select L5              | LDS rising edge to LD[7:0] valid  | D64=1              | Prop t74  |

|       |                        | D64 rising edge to LD[7:0] valid  | LDS=1              | Prop t76  |

|       | Select L7              | LDS falling edge to LD[7:0] valid | D64=1              | Prop t75  |

|       | Select L6              | D64 falling edge to LD[7:0] valid |                    | Prop t77  |

|       | Minimum pulse width    | DENIN*                            |                    | t33       |

|       |                        | DENIN1*                           |                    | t36       |

|       |                        | LEDI                              |                    | t39       |

# CY7C964 Byte Width Mode Alternate BLT Initiation Operation

Another method of loading the VMEbus block transfer address counters exists within the CY7C964. This method has been placed within its own section of the document because it is not completely compatible with the VIC block transfer initiation cycle.

The CY7C964 determines the source for loading the VMEbus master block transfer counter C3 by monitoring the arrival sequence of the MWB\* and BLT\* signals. For typical block transfers initiation cycles the assertion of MWB\* occurs prior to the assertion of the BLT\*. The VMEbus master block transfer counter C3 loads from the local address pins, LA[7:0], as described within a previous section of this document.

Reversing the arrival order of these two signals changes the operation of the device. This is done at system design time by swapping the BLT\* and MWB\* inputs to the CY7C964. For proper operation, these signals must continue to operate in the same manner as they do on the VIC, even though they are no longer connected to the associated input pins on the CY7C964 which have the same name. Swapping these signals on the device changes the way that the VMEbus master block transfer counter C3 is loaded. In this mode it loads from the local data bus via latch L9. All other functions within the device operate in the same manner as described within the previous section.

Loading C3 is accomplished with a local cycle similar to the cycles needed to load the mask and compare registers. This cycle operates as follows: LDS is driven high, (most likely this signal is connected to LA2), the MWB\* input pin of the CY7C964 is driven Low, (this pin is actually connected to the open collector BLT\* output of the VIC), and STROBE\* is asserted. The local data bus should be driven to the appropriate value for the address to load into the C3 counters. STROBE\* is deasserted and the data is latched into L9 within the CY7C964. The local address decode signal used to assert MWB\* on the CY7C964, (BLT\* on the VIC), must be a three-state or an open-collector output. This signal must not be driven high or the VIC will be unable to perform block transfers.

A normal master block transfer initiation cycle is then performed, with one minor exception. The lower 8 bits of address LA[7:0] which are controlled by the VIC, must contain the desired lower address. This is needed because the VIC operates in the typical block transfer initiation mode. The upper address LA[31:8] will be ignored by the CY7C964s during the initiation cycle.

Figure 19. CY7C964 Byte Width Mode Alternate BLT Operation Block Diagram

This mode of operation allows the VMEbus master block transfer address counters to be loaded independent of the VMEbus address. This has advantages in some designs, but C3 cannot be used to source single cycle transfer addresses. This limitation should be considered while performing the design analysis to use this mode.

**Table 17. Byte Width Mode Alternate BLT Initiation Operation**

| Logic | Functional Description | Operational Description         | Required Condition | Parameters |

|-------|------------------------|---------------------------------|--------------------|------------|

| L9    | Select register        | LDS, MWB* valid to STROBE*      | LDS=1, MWB*=0      | Set-up t43 |

|       |                        | falling edge                    |                    | Hold t44   |

|       | Load register          | LD[7:0] valid to STROBE* rising |                    | Set-up t45 |

|       |                        | edge                            |                    | Hold t46   |

|       | Minimum pulse width    | STROBE*                         |                    | t46        |

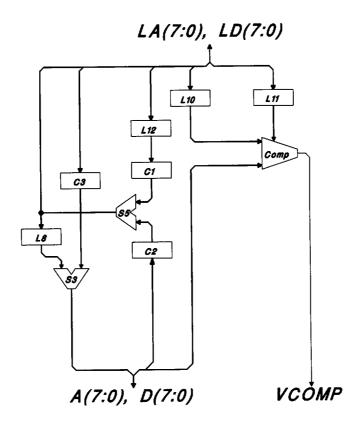

# **CY7C964 Word Width Mode Operation**

The second operating personality of the CY7C964 is a 16-bit wide address or data-only controller. The device is more suited to be an address controller for conventional VMEbus interfaces because the block transfer counters C1, C2, and C3 and the comparator operate in the same manner as described in the previous section, but they expand to 16 bits wide. Data-related functions such as the data multiplexer and data demultiplexer are not available in this mode of operation.

Figure 20. CY7C964 Block Diagram for Word Width Mode of Operation

The address and data signals A[7:0], D[7:0], LA[7:0], and LD[7:0] are combined to form two 16-bit buses. A high drive-strength, 16-bit bus-A[7:0], D[7:0]-and a medium drive-strength bus-LA[7:0], LD[7:0], D[7:0], and LD[7:0]-are the least-significant bytes of these buses.

The word width mode of operation has a rich set of features for use as a 16-bit VMEbus address controller. Because of this, the local bus-LA[7:0], LD[7:0] and A[7:0], D[7:0]-are being referred to as the local and VMEbus address buses within this section of the document.

In word width mode, one additional latch, L12, is located between the local address bus and local master block transfer counter C1. This latch allows the local master block transfer counter to be loaded from the local address bus prior to loading the VMEbus master block transfer counter C3. This is necessary since both VMEbus master block transfer counter C3 and the local master block transfer counter C1 are loaded from the same local address bus. When the VMEbus master block counter C3 loads during the block transfer initiation cycle, the contents of latch L12 are moved to counter C1. To write L12, LDS and DENIN\* must both be Low. In the same manner as the byte width mode, C3 is normally loaded directly from LA[7:0], LD[7:0]. If the arrival order of MWB\* and BLT\* is reversed, the device operates in a similar manner to the byte width mode, using L9 to hold the information destined for C3. This operation is described on page 61 of this book.

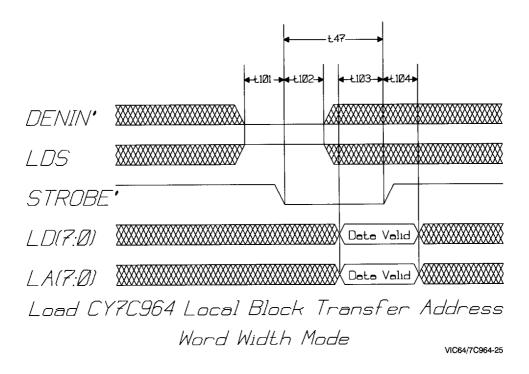

To place the device in word width mode of operation, input signals LEDO and LEDI should be tied High. The address compare and mask registers load in a similar manner to the byte width mode, except DENIN\* replaces MWB\* as a control input for register decoding. Mask and compare register load waveforms are shown in *Figure 21* and *Figure 22*.

Figure 21. Mask Register Load Timing in Word Width Mode

DENIN'

LDS

STROBE'

LD(7:D)

Deta Valid

Load CY7C964 Compare Register

Word Width Mode

Figure 22. Compare Register Load Timing in Word Width Mode

64

Figure 23. Local Block Transfer Address in Word Width Mode

The block transfer initiation cycle shanges slightly in the word width mode. The typical block transfer initiation cycle loads the local DMA address into the local DMA counter C1 from the data bus. This is not possible in the word width mode because the part is strictly an address controller and does not have a data bus.

Two cycles are required to initiate a block transfer in word width mode. The first cycle is used to set up the local DMA counter C1. This cycle is similar to the mask and compare register cycles. *Figure 23* shows the timing waveform for this cycle. The VMEbus block transfer address counter C3 is loaded using the usual VIC block transfer initiation cycle with the local address bus containing the large VMEbus address. It is important to note that the local DMA address must be loaded first, because the typical VIC block transfer cycle will begin the block transfer using the contents of the local DMA block transfer C3.

Table 18. Word Width Mode Operation

| Logic | <b>Functional Description</b> | Operational Description         | Required Condition | Parameters |

|-------|-------------------------------|---------------------------------|--------------------|------------|

| L12   | Select register               | LDS, DENIN* valid to STROBE*    | LDS=1,             | Set-up t43 |

|       |                               | falling edge                    | DENIN*=0           | Hold t44   |

|       | Load register                 | LD[7:0] valid to STROBE* rising |                    | Set-up t45 |

|       |                               | edge                            |                    | Hold t46   |

|       | Minimum pulse width           | STROBE*                         |                    | t46        |

# **DC Performance Specifications**

# VMEbus Signals (A[7:0], D[7:0])

| Parameter       | Description                       | Test Condition                                                                                                                             | Military/Industrial/Commercial | Unit |

|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|

| V <sub>IH</sub> | Minimum high-level input voltage  |                                                                                                                                            | 2.0                            | V    |

| V <sub>IL</sub> | Maximum high-level input voltage  |                                                                                                                                            | 0.8                            | V    |

| V <sub>OH</sub> | Minimum high-level output voltage | $V_{CC}$ =minimum<br>$I_{OH}$ = -3 mA                                                                                                      | 2.4                            | V    |

| $V_{OL}$        | Minimum low-level output voltage  | $V_{CC}$ =minimum<br>$I_{OL}$ = 48 mA                                                                                                      | 0.6                            | V    |

| $I_{L}$         | Maximum input leakage current     | V <sub>CC</sub> =maximum<br>V <sub>IN</sub> =0.6 - 2.4                                                                                     | ±5                             | uA   |

| $V_{IK}$        | Input clamp voltage               | $\begin{array}{c} V_{CC}\text{=}\min I_{IN}\text{=}\\ \text{-}18\text{ mA}\\ V_{CC}\text{=}\min I_{IN}\text{=}\\ 18\text{ mA} \end{array}$ | -1.2<br>V <sub>CC</sub> +1.2   | V    |

| $I_{OZ}$        | Maximum output leakage current    | $V_{CC}$ =maximum<br>$GND \le V_{OUT}$<br>$\le V_{CC}$<br>all outputs dis-<br>abled                                                        | ±10                            | uA   |

## **Non-VMEbus Signals**

| Parameter       | Description                       | Test Condition                                                                        | Military/Industrial/Commercial | Unit |

|-----------------|-----------------------------------|---------------------------------------------------------------------------------------|--------------------------------|------|

| V <sub>IH</sub> | Minimum high-level input voltage  |                                                                                       | 2.0                            | V    |

| $V_{IL}$        | Maximum high-level input voltage  |                                                                                       | 0.8                            | V    |

| V <sub>OH</sub> | Minimum high-level output voltage | $V_{CC}$ =minimum<br>$I_{OH}$ = -8 mA                                                 | 2.4                            | V    |

| V <sub>OL</sub> | Maximum input leakage current     | $V_{CC}$ =maximum<br>$I_{OL}$ = 8 mA                                                  | 0.6                            | V    |

| $I_L$           | Maximum input leakage current     | V <sub>CC</sub> =maximum<br>V <sub>IN</sub> =0 -V <sub>CC</sub>                       | ±5                             | uA   |

| $V_{IK}$        | Input clamp voltage               | $V_{CC} = \min \\ I_{IN} = -18 \text{ mA} \\ V_{CC} = \min \\ I_{IN} = 18 \text{ mA}$ | -1.2<br>V <sub>CC</sub> +1.2   | V    |

## **Non-VMEbus Signals**

| Parameter       | Description                                      | Test Condition                                                                            | Military/Industrial/Commercial | Unit |

|-----------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|------|

| I <sub>OZ</sub> | Maximum output leakage current                   | $V_{CC}$ =maximum GND $\leq$ V <sub>OUT</sub> $\leq$ V <sub>CC</sub> all outputs disabled | ±5                             | uA   |

| I <sub>CC</sub> | V <sub>CC</sub> maximum operating supply current | V <sub>CC</sub> =maximum<br>all outputs<br>disabled                                       | 25                             | mA   |

# **AC Performance Specifications**

# **Byte Width Mode**

| Parameter | Description                                                  | Min.<br>All<br>Grades <sup>[1]</sup> | Max.<br>(Com'l) | Max.<br>(Ind) | Max.<br>(Mil) | Unit | Comment      |

|-----------|--------------------------------------------------------------|--------------------------------------|-----------------|---------------|---------------|------|--------------|

| t1        | LA[7:0] to A[7:0] propagation delay <sup>[2]</sup>           |                                      | 15              | 16            | 18            | ns   |              |

| t2        | LD[7:0] to D[7:0] propagation delay                          |                                      | 16              | 17            | 19            | ns   |              |

| t3        | A[7:0] to LA[7:0] propagation delay                          |                                      | 17              | 18            | 20            | ns   |              |

| t4        | D[7:0] to LD[7:0] propagation delay <sup>[2]</sup>           |                                      | 19              | 20            | 22            | ns   |              |

| t5        | LD[7:0] to A[7:0] propagation delay <sup>[2]</sup>           |                                      | 19              | 20            | 22            | ns   | D64 = 1      |

| t6        | A[7:0] to LD[7:0] propagation delay <sup>[2]</sup>           |                                      | 19              | 20            | 22            | ns   | D64 = 1      |

| t7        | ABEN* active to A[7:0] output enable delay <sup>[2]</sup>    |                                      | 11              | 11            | 12            | ns   |              |

| t8        | DENO* active to D[7:0] output enable delay <sup>[2]</sup>    |                                      | 14              | 15            | 16            | ns   |              |

| t9        | ABEN* active to D[7:0] output enable delay                   |                                      | 14              | 15            | 17            | ns   | D64 = 1      |

| t10       | D64 active to D[7:0] output enable delay <sup>[2]</sup>      |                                      | 13              | 14            | 15            | ns   | $ABEN^* = 0$ |

| t11       | LAEN active to LA[7:0] output enable delay <sup>[2]</sup>    |                                      | 10              | 11            | 12            | ns   |              |

| t12       | DENIN* active to LD[7:0] output enable delay                 |                                      | 15              | 16            | 18            | ns   |              |

| t13       | DENIN1* active to LD[7:0] output enable delay <sup>[2]</sup> |                                      | 18              | 19            | 21            | ns   | D64 = 1      |

| t14       | D64 active to LD[7:0] output enable delay <sup>[2]</sup>     |                                      | 18              | 19            | 21            | ns   | DENIN1*= 0   |

| Parameter | Description                                                               | Min.<br>All<br>Grades | Max.<br>Com'l | Max.<br>Ind | Max.<br>Mil | Unit | Comment              |

|-----------|---------------------------------------------------------------------------|-----------------------|---------------|-------------|-------------|------|----------------------|

| t15       | ABEN* inactive to A[7:0] High-Z outputdisable delay <sup>[2]</sup>        |                       | 8             | 10          | 12          | ns   |                      |

| t16       | DENO* inactive to D[7:0] High-Z output disable delay <sup>[2]</sup>       |                       | 12            | 14          | 15          | ns   |                      |

| t17       | ABEN* inactive to D[7:0] High-Z output disable delay <sup>[2]</sup>       |                       | 12            | 14          | 15          | ns   | D64 = 1              |

| t18       | D64 inactive to D[7:0] High-Z output disable delay <sup>[2]</sup>         |                       | 14            | 15          | 16          | ns   | $ABEN^* = 0$         |

| t19       | LAEN Inactive to LA[7:0] High-Z output disable delay <sup>[2]</sup>       |                       | 13            | 14          | 15          | ns   |                      |

| t20       | DENIN* inactive to LD[7:0]<br>High-Z output disable delay <sup>[2]</sup>  |                       | 14            | 16          | 18          | ns   |                      |

| t21       | DENIN1* Inactive to LD[7:0]<br>High-Z output disable delay <sup>[2]</sup> |                       | 14            | 16          | 18          | ns   | D64 = 1              |

| t22       | D64 inactive to LD[7:0] High-Z output disable delay <sup>[2]</sup>        |                       | 19            | 21          | 24          | ns   | DENIN1*= 0           |

| t23       | A[7:0] to VCOMP* High-to-Low propagation delay                            |                       | 18            | 19          | 21          | ns   |                      |