# FEATURES

- Add/drop up to 28 E1, DS1, or VT/TU payloads from two add and two drop STM-1/VC4, STS-3 buses

- · Add bus and drop bus timing modes

- Cross mapping applications (DS1 mapped to/from VT2/TU-12s)

- Selectable HDB3/B8ZS/AMI positive/negative rail, NRZ, or VT/TU interfaces per channel

- H4 multiframe option in place of Telecom Bus V1 pulse

- Digital desynchronizer

- Drop buses are monitored for parity, loss of clock, and upstream AIS

- Performance counters for pointer movements, BIP-2 errors, REI and coding violations

- Single-bit or three-bit RDI operation per channel

- Tandem connection capability per ETSI standards

- J2 trail trace comparison option

- Processor access to H1/H2, H4 overhead bytes, and V1/V2 and V4 bytes

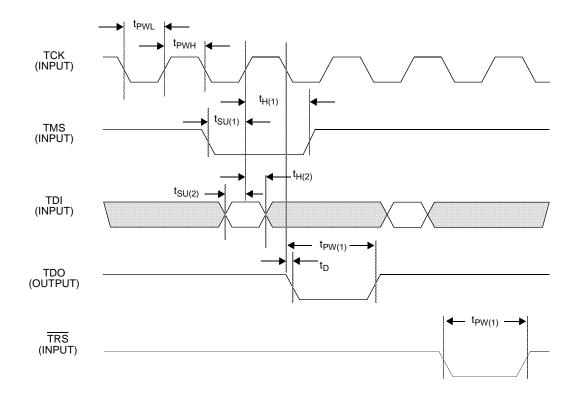

- Selectable positive, negative or positive/negative alarm transition interrupt options

- Line and facility loopbacks, generation of BIP-2 and REI errors, PRBS generator and analyzer per channel

- · Polling registers and global summary alarm status

- One second measurements: counters and alarms

- · Software device driver is provided

- IEEE 1149.1 standard boundary scan

- +3.3 V and 1.8 V power supplies, 5 V tolerant I/O leads

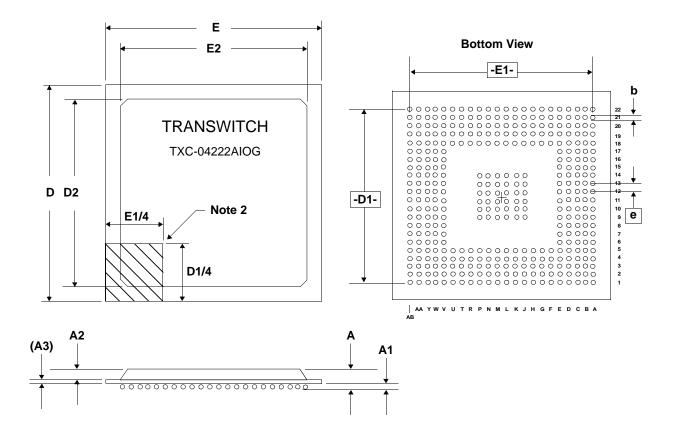

- 376-lead plastic ball grid array (PBGA) package (23 mm x 23 mm)

# DESCRIPTION

The TEMx28<sup>®</sup> device is designed for add/drop multiplexer, terminal multiplexer, and dual and single unidirectional ring applications. Up to 28 E1, DS1, or VT/TU payloads are mapped to and from VT1.5/TU-11s and VT2/TU-12s carried in an STM-1 VC-4 or STS-3 format. The device interfaces to a multiple-segment, byte-parallel SDH/SONET-formatted bus at the 19.44 Mbyte/s byte rate. The E1 and DS1 signals can be HDB3 or B8ZS/AMI rail signals, or NRZ signals. The VT/TU interface can be provided with or without the overhead bytes for virtual concatenation applications. The TEMx28 performs pointer tracking and overhead byte processing, including single-bit or three-bit RDI operation, and optional tandem connection capability. All overhead bytes, including the V1/V2/V4 bytes, are provided for microprocessor access.

The TEMx28 can generate receive and transmit line AIS, transmit unequipped and supervisory unequipped channels, and transmit VT/TU AIS, in addition to standards-compliant overhead byte monitoring. It also provides test features and a microprocessor interface.

# APPLICATIONS

- 3 STS-3/STM-1 to 1.544 Mbit/s and 2.048 Mbit/s add/drop mux/demux

- · Unidirectional or bidirectional ring applications

- STS-3/STM-1 termination terminal mode multiplexer

- STS-3/STM-1 test equipment

**DATA SHEET**

# **TABLE OF CONTENTS**

| Section                                                | Page |

|--------------------------------------------------------|------|

| List of Figures                                        | 3    |

| Overview                                               |      |

| Features                                               | 5    |

| Block Diagram                                          | 9    |

| Block Diagram Description                              | 10   |

| Application Example                                    | 16   |

| Interoperability                                       | 16   |

| Lead Diagram                                           | 17   |

| Lead Descriptions                                      | 18   |

| Absolute Maximum Ratings and Environmental Limitations | 28   |

| Thermal Characteristics                                |      |

| Power Requirements                                     | 28   |

| Input, Output and Input/Output Parameters              | 29   |

| Timing Characteristics                                 |      |

| Operation                                              |      |

| Bus Interface Modes                                    | 51   |

| Bus Mode Selection                                     |      |

| SDH/SONET Add/Drop Multiplexing Format Selections      |      |

| Drop and Add TU/VT Selection                           |      |

| Bus Timing                                             |      |

| Performance Counters                                   |      |

| Alarm Structure                                        |      |

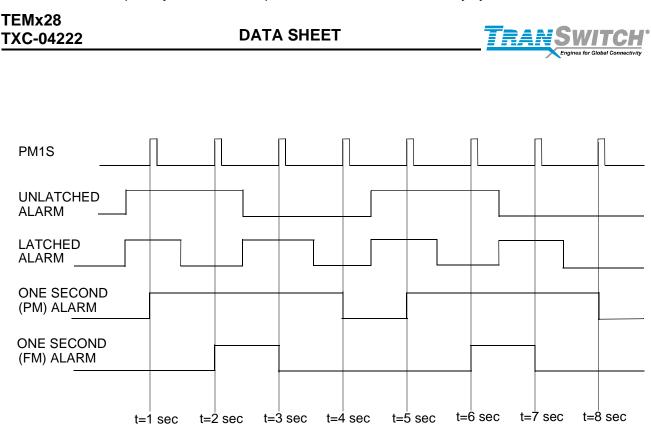

| One Second (Shadow) Registers                          | 55   |

| Interrupt Structure                                    |      |

| Drop Bus Interface                                     |      |

| Drop Bus Parity Selection                              | 60   |

| Drop Bus Multiframe Alignment                          |      |

| SDH/SONET AIS Detection                                | 62   |

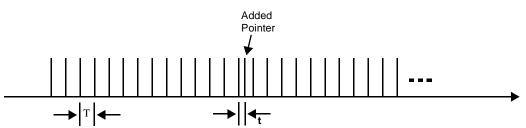

| TU/VT Pointer Tracking                                 | 63   |

| Overhead Byte Processing                               | 66   |

| Overhead Communications Bit Access                     | 72   |

| Overhead Byte Insertion                                | 77   |

| Test Functions                                         | 86   |

| PRBS Pattern Generator and Analyzer                    | 86   |

| Resets                                                 | 87   |

| Data Throughput Delay                                  |      |

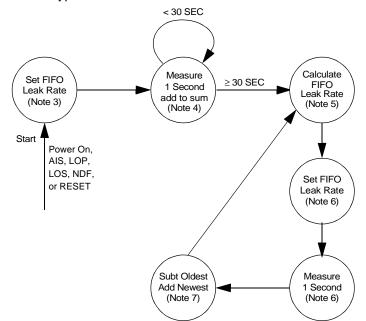

| Pointer Leak Rate Calculations                         | 89   |

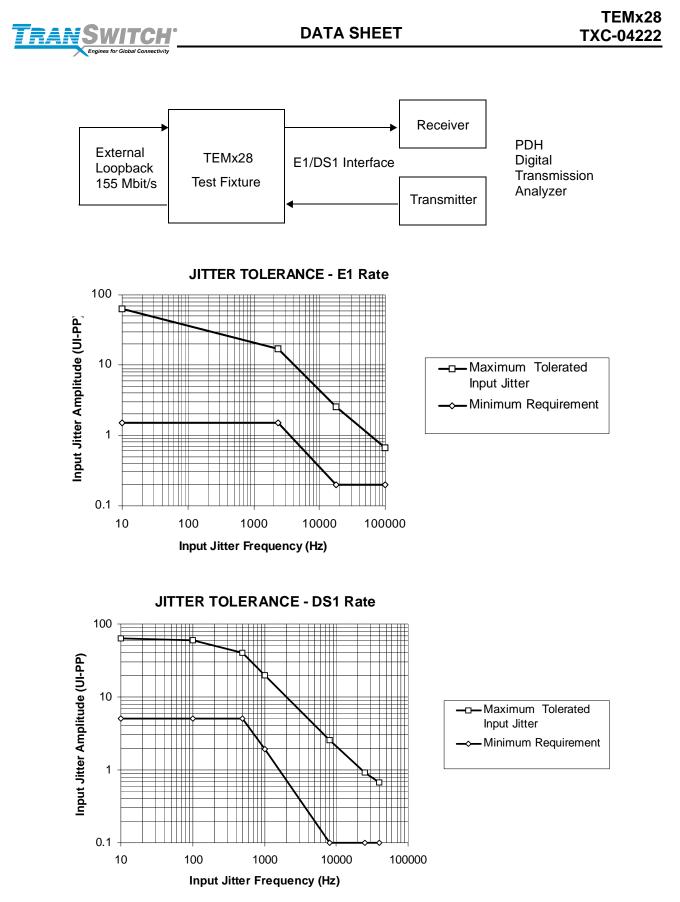

| Jitter Measurements                                    | 90   |

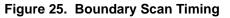

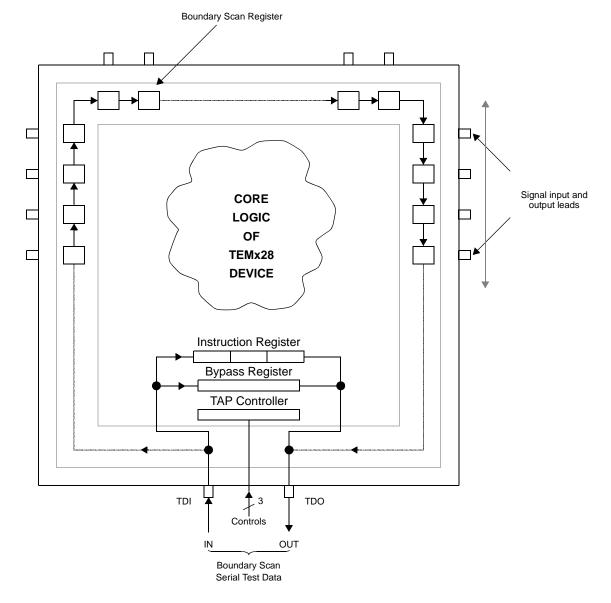

| Boundary Scan                                          | 99   |

| Multiplex Format and Mapping Information               | 112  |

| Memory Map                                             |      |

| Memory Map Descriptions                                | 136  |

| Package Information                                    | 239  |

| Ordering Information                                   |      |

| Related Products                                       |      |

| Reference Documents                                    | 241  |

| Standards Documentation Sources                        |      |

| List of Data Sheet Changes                             | 244  |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# LIST OF FIGURES

| Figu | ure P                                                                             | age  |

|------|-----------------------------------------------------------------------------------|------|

| 1    | TEMx28 TXC-04222 Block Diagram                                                    | 9    |

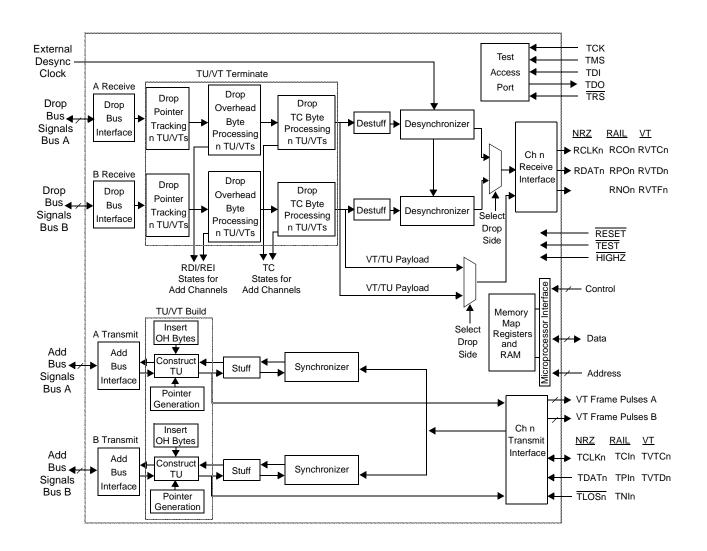

| 2    | 1544 kbit/s Asynchronous Mapping                                                  | . 13 |

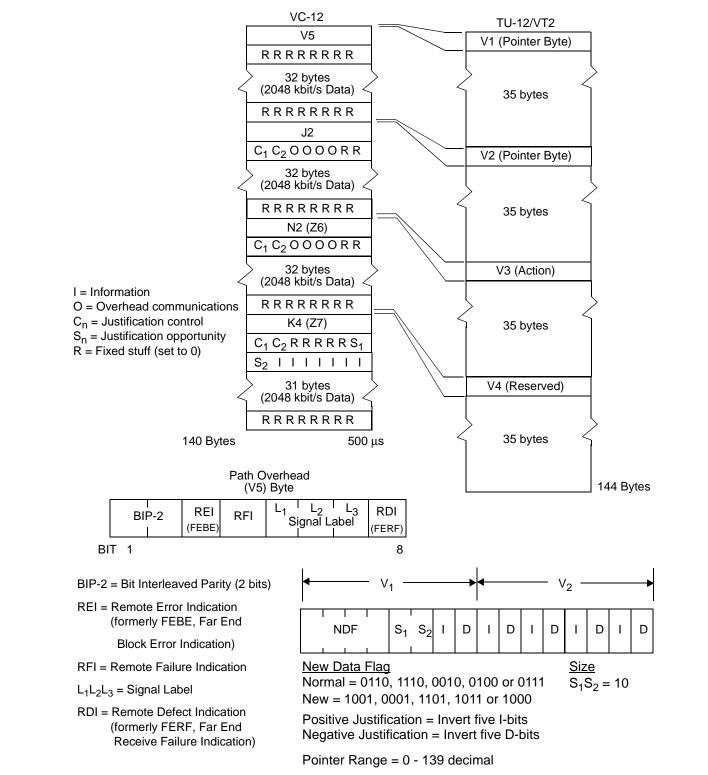

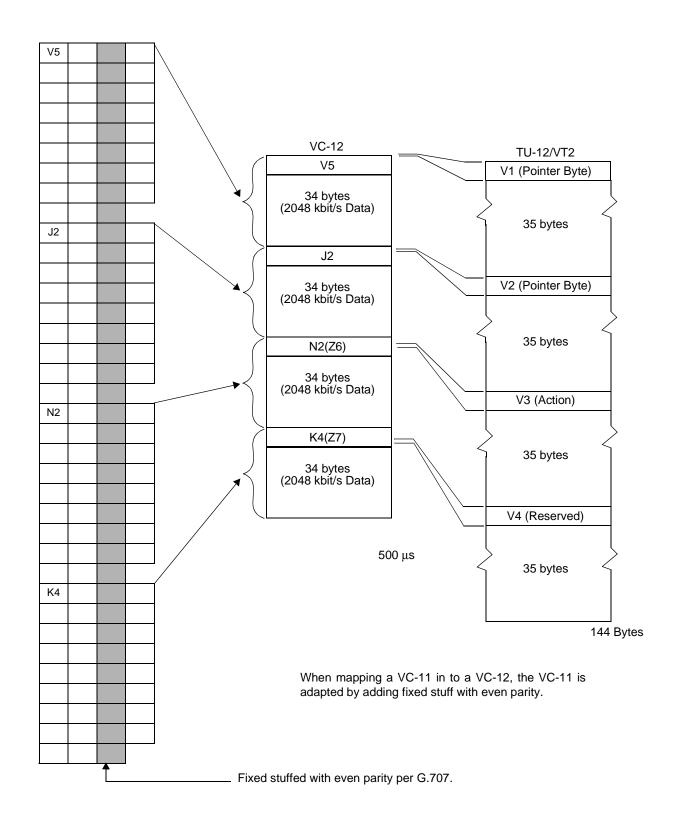

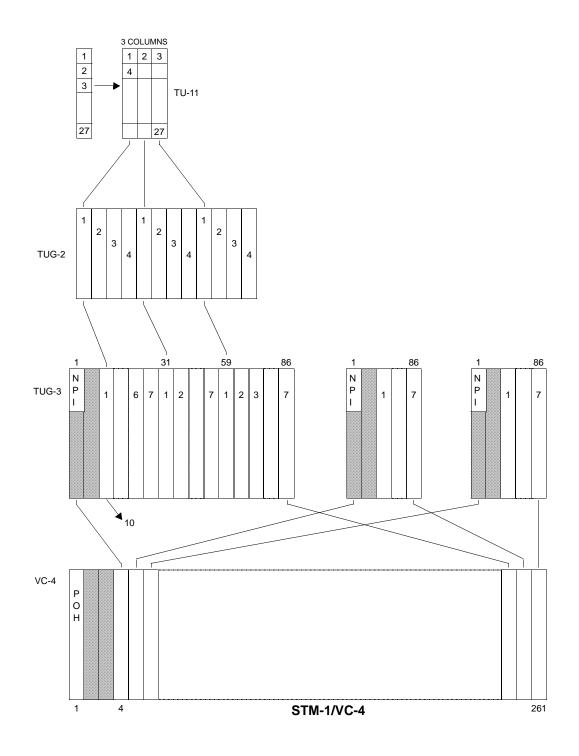

| 3    | 2048 kbit/s Asynchronous Mapping                                                  | . 14 |

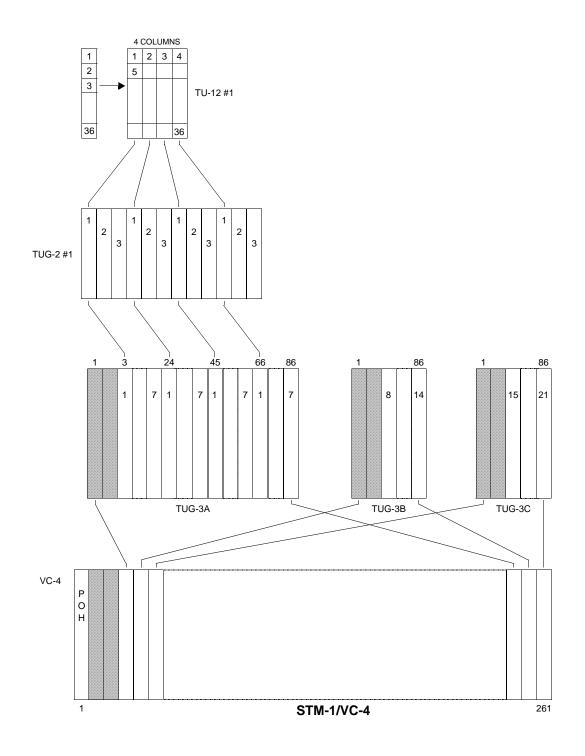

| 4    | VC-11 to VC-12 Cross Mapping                                                      | . 15 |

| 5    | Application Using the TEMx28 TXC-04222                                            | . 16 |

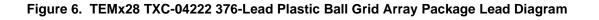

| 6    | TEMx28 TXC-04222 376-Lead Plastic Ball Grid Array Package Lead Diagram            | . 17 |

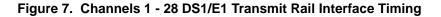

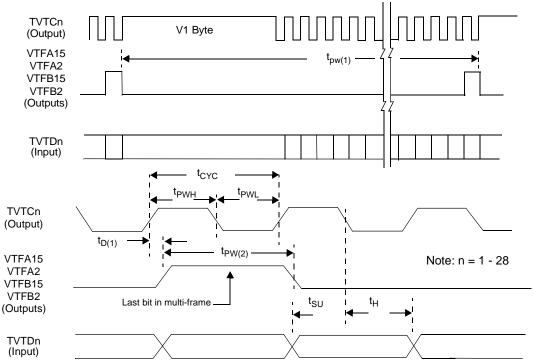

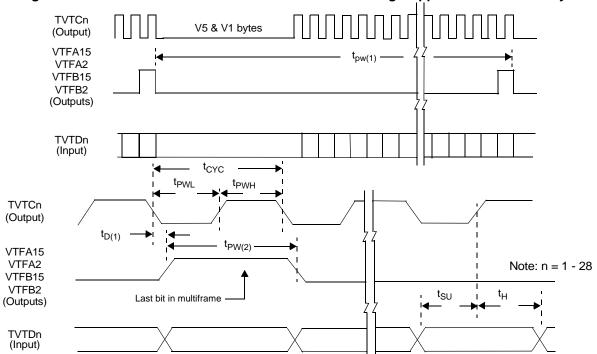

| 7    | Channels 1 - 28 DS1/E1 Transmit Rail Interface Timing                             | . 32 |

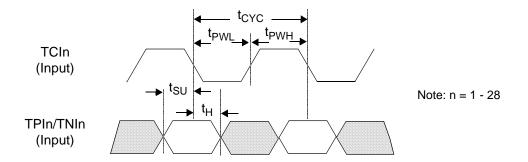

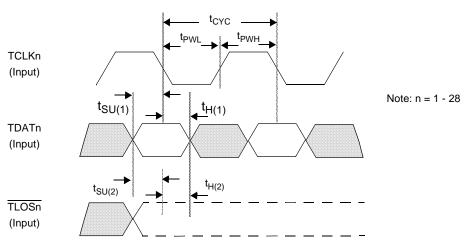

| 8    | Channels 1 - 28 DS1/E1 Transmit NRZ Interface Timing                              | . 33 |

| 9    | Channels 1 - 28 Transmit VT/TU Interface Timing -Gapped Pointer Bytes             | . 34 |

| 10   | Channels 1 - 28 Transmit VT/TU Interface Timing-Gapped Pointer & POH Byte         | . 35 |

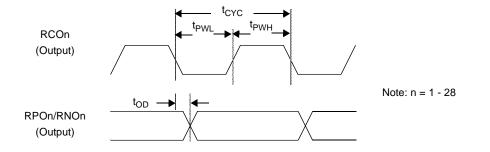

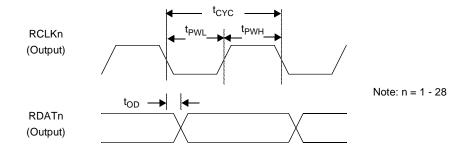

| 11   | Channels 1 - 28 DS1/E1 Receive Rail Timing                                        | . 36 |

| 12   | Channels 1 - 28 DS1/E1 Receive NRZ Timing                                         | . 37 |

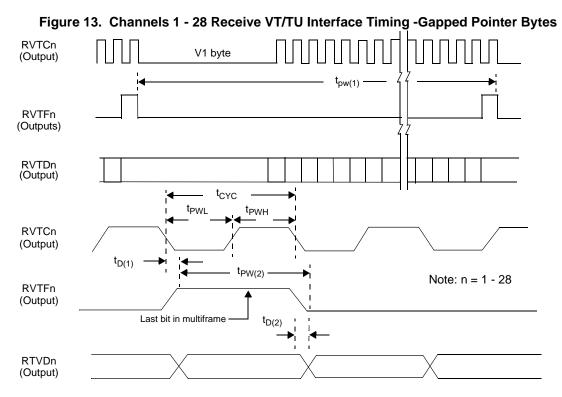

| 13   | Channels 1 - 28 Receive VT/TU Interface Timing -Gapped Pointer Bytes              | . 38 |

| 14   | Channels 1 - 28 Receive VT/TU Interface Timing-Gapped Pointer & POH Byte          | . 39 |

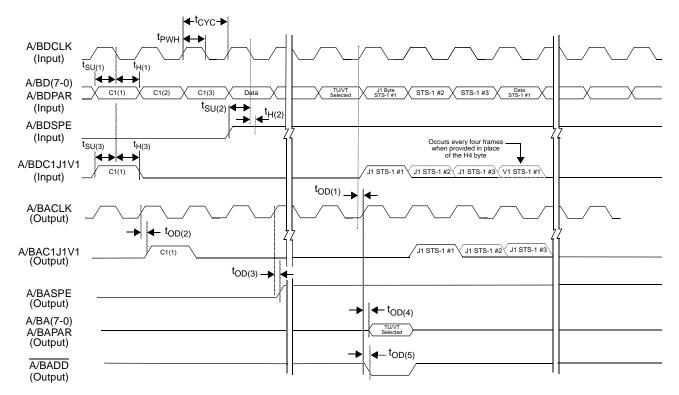

| 15   | STS-3 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus (lead ABTE low)  | . 40 |

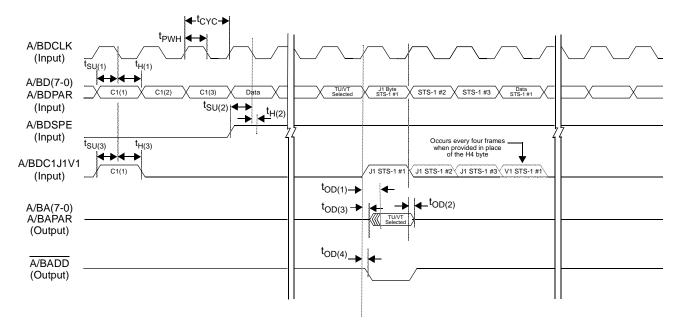

| 16   | STS-3 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus (lead ABTE high) | . 41 |

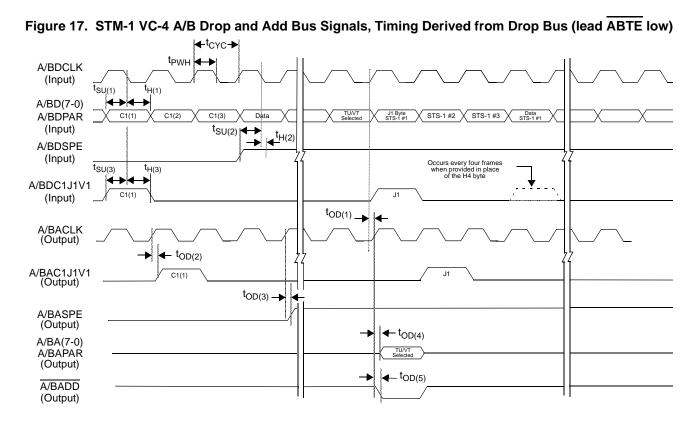

| 17   | STM-1 VC-4 A/B Drop and Add Bus Signals,                                          |      |

|      | Timing Derived from Drop Bus (lead ABTE low)                                      | . 42 |

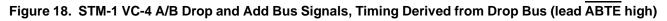

| 18   | STM-1 VC-4 A/B Drop and Add Bus Signals,                                          |      |

|      | Timing Derived from Drop Bus (lead ABTE high)                                     |      |

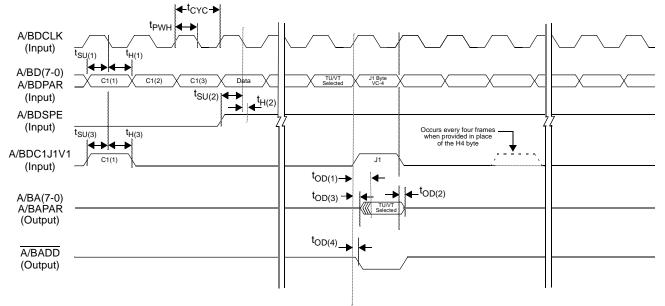

| 19   | STS-3 A/B Add Bus Signals, Timing Derived from Add Bus                            |      |

| 20   | STM-1 VC-4 A/B Add Bus Signals, Timing Derived from Add Bus                       |      |

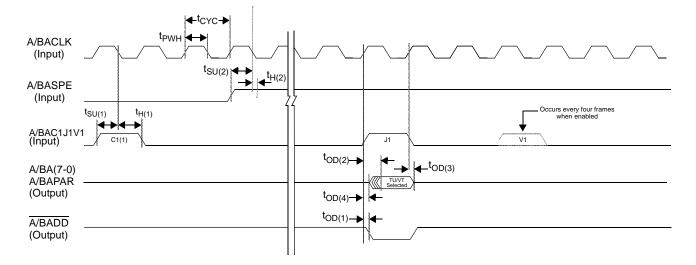

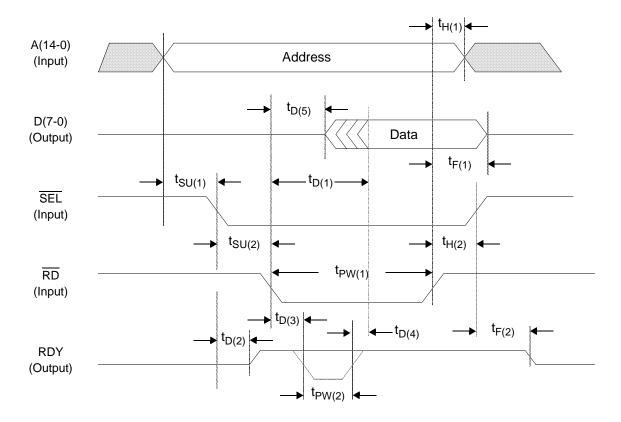

| 21   | Microprocessor Read Cycle Timing - Intel                                          |      |

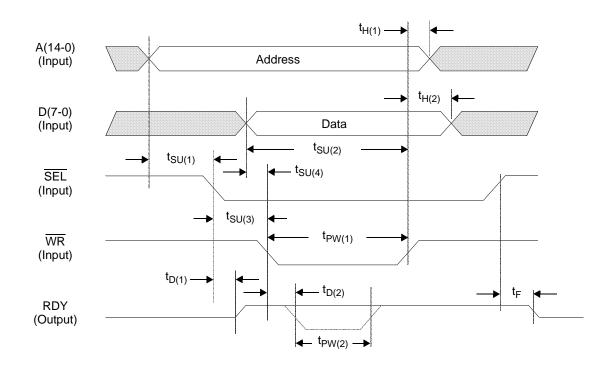

| 22   | Microprocessor Write Cycle Timing - Intel                                         |      |

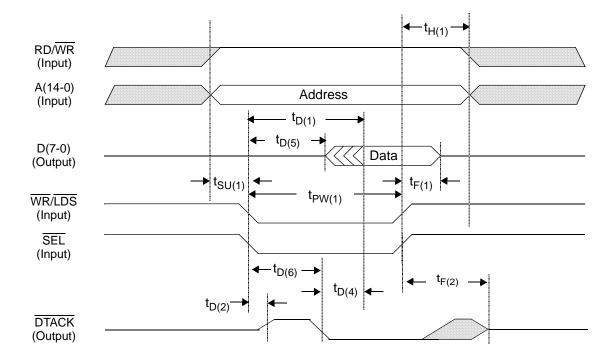

| 23   | Microprocessor Read Cycle Timing - Motorola                                       |      |

| 24   | Microprocessor Write Cycle Timing - Motorola                                      |      |

| 25   | Boundary Scan Timing                                                              |      |

| 26   | Alarm Latching Configurations                                                     |      |

| 27   | One Second (Shadow) Register Operation                                            |      |

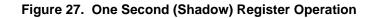

| 28   | Channel Polling Alarms                                                            |      |

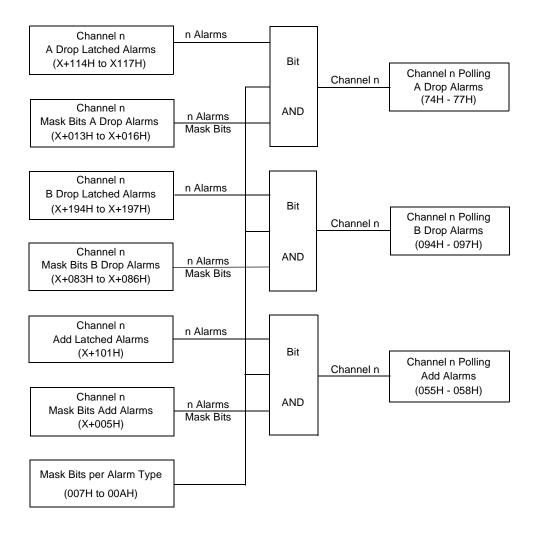

| 29   | Global Indication Alarms                                                          |      |

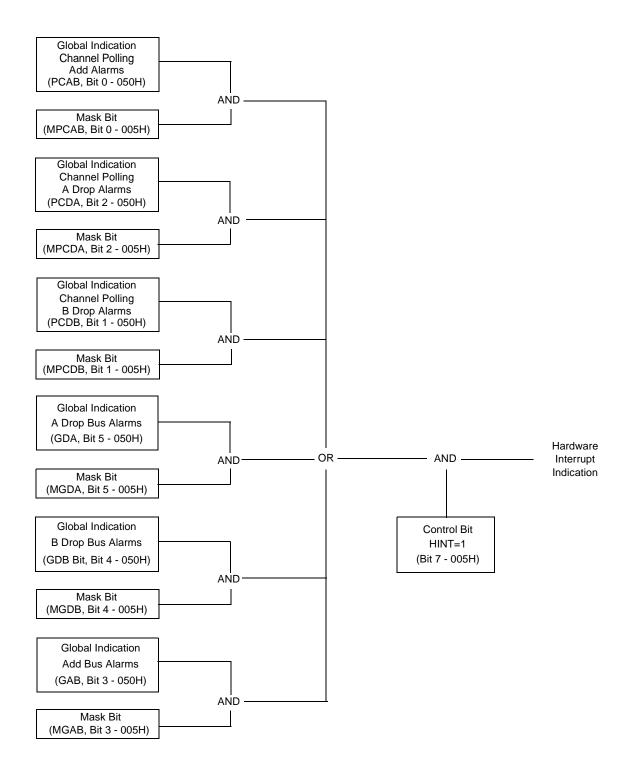

| 30   | Hardware Interrupt Indication                                                     |      |

| 31   | H4 Byte Floating VT Mode Bit Allocation                                           |      |

| 32   | VT/TU Pointer Tracking State Machine                                              |      |

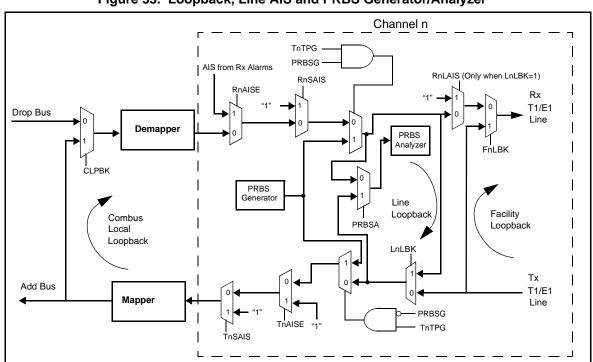

| 33   | Loopback, Line AIS and PRBS Generator/Analyzer                                    |      |

| 34   | E1 (2048 kbit/s) Jitter Tolerance                                                 |      |

| 35   | DS1 (1544 kbit/s) Jitter Tolerance                                                | . 90 |

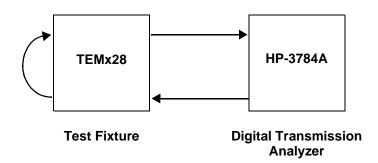

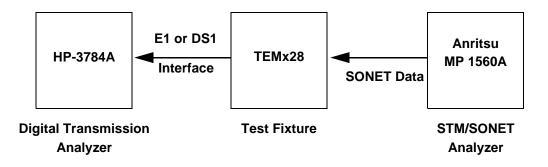

| 36   | Jitter Tolerance Measurements                                                     |      |

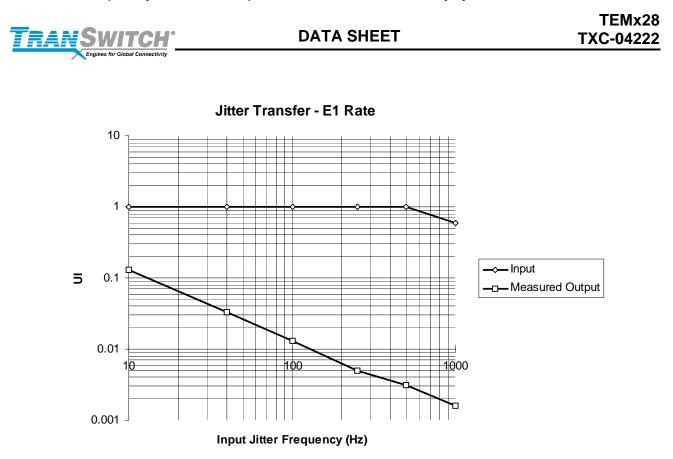

| 37   | E1 Jitter Transfer Measurements                                                   |      |

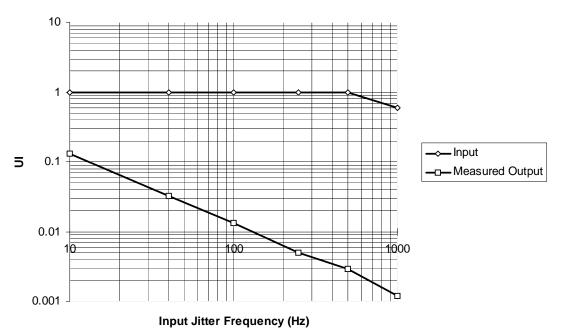

| 38   | DS1 Jitter Transfer Measurements                                                  |      |

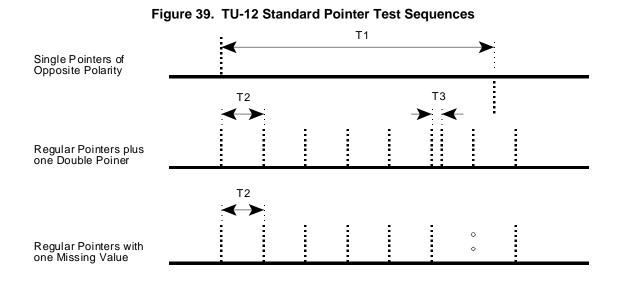

| 39   | TU-12 Standard Pointer Test Sequences                                             |      |

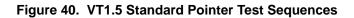

| 40   | VT1.5 Standard Pointer Test Sequences                                             |      |

| 41   | Boundary Scan Schematic                                                           |      |

| 42   | TEMx28 TXC-04222 376-Lead Plastic Ball Grid Array Package                         | 239  |

**DATA SHEET**

## **OVERVIEW**

The TEMx28 device is designed for add/drop multiplexer, terminal multiplexer, and dual and single unidirectional ring applications. Up to 28 E1, DS1, or VT/TU payloads are mapped to and from VT1.5/TU-11s and VT2/TU-12s carried in an STM-1 VC-4 or STS-3 format. The device interfaces to a multiple-segment, byte-parallel SDH/SONET-formatted bus at the 19.44 Mbyte/s byte rate. The E1 and DS1 signals can be HDB3 or B8ZS/AMI positive/negative rail (dual unipolar) signals, or NRZ signals. The VT/TU interface can be provided with or without the overhead bytes for virtual concatenation applications. The TEMx28 performs pointer tracking and overhead byte processing, including single-bit or three-bit RDI operation, and optional tandem connection capability. All overhead bytes, including the V1/V2/V4 bytes, are provided for microprocessor access.

The TEMx28 can generate receive and transmit line AIS, transmit unequipped and supervisory unequipped channels, and transmit VT/TU AIS, in addition to standards-compliant overhead byte monitoring.

For testing, the device provides IEEE 1149.1 boundary scan, a PRBS generator and analyzer, and both line and facility loopbacks. The TEMx28 supports split bus access for either Intel or Motorola microprocessors. Its performance counters can be configured to be either saturating or roll over. Interrupts can be generated by alarms that latch on positive, negative, or both positive and negative status transitions, and they can be disabled via mask bits. A software polling register and summary alarm bit status are also provided. One second measurements are performed for alarms and counters.

# FEATURES

The following is a detailed list of features supported by the TEMx28:

- Bus Modes of operation (Each Channel)

- Drop Mode Only

- Drop from A or B

- Add Mode only

- Add to A or B

- Add to A and B

- Single Unidirectional Ring

- Drop from A, Add to A

- Drop from B, Add to B

- Multiplexer

- Drop from A, Add to B

- Drop from B, Add to A

- Dual Protection Ring

- Drop from A, Add to A and B

- Drop from B, Add to B and A

- Bus Timing

- Drop Bus Timing

- Add Bus Timing Derived from the same named Drop Bus

- Add Bus Timing

- Add Bus Timing is independent of the Drop Bus

- Lead Selectable

- SONET/SDH COMBUS Interface

- Drop Bus Timing Enabled

- Drop Bus: C1J1V1, SPE, Byte Wide Data, Clock, Parity

- Add Bus: Byte Wide Data, Parity, Add Indicator

- Option: Clock, C1J1V1, and SPE are Outputs

- Add Bus Timing Enabled

- Drop Bus: C1J1V1, SPE, Byte Wide Data, Clock, Parity

- Add Bus: Clock, C1J1V1, SPE are inputs; Byte Wide Data, Parity, Add Indicator are Outputs.

- Mappings

- Maximum of up to 28 Channels

- DS1/E1 Line Asynchronous Formats, or VC-11/VC-12s

- Independent VT1.5/TU-11 or VT2/TU12 Selection per Channel for both Drop and Add Buses

- Cross Mapping: DS1 mapped into VT1.5/TU-12

- SONET/SDH Operating Formats

- STS-3 STS-1 (19.44 Mbyte/s)

- STM-1 VC-4/TUG-3/TUG-2 (19.44 Mbyte/s)

- STM-1 AU-3s (19.44 Mbyte/s)

**DATA SHEET**

- Drop Buses

- Input Parity Check with Alarm Indication

- Odd, or Even

- Data Only, or Bus Signals

- Input Loss Of Clock Detection

- Stuck High or Low

- Add Buses

- Output Parity Generation

- Odd, or Even

- Data Only, or Bus Signals

- Add to Bus Indicator

- High Z Output Bus Signals Control

- Individual Channel High Z VT/TU Time Slots

- SONET/SDH Features

- In-band upstream AIS Detection

- H1/H2 Pointer Bytes

- E1 Bytes using Majority Voting

- H4 Byte Multiframe Detectors or V1 pulse (C1J1V1) reference input

- Determines Location of V1/V2 Pointer Bytes

- Pointer Tracking

- ETSI/ITU/ANSI State Machine

- Wrong Size Bits Detection

- Positive/Negative Justification 8-bit Counters

- Microprocessor Access to

- V1/V2 Pointer Bytes (Each Channel)

- H4 POH Bytes (Both Buses, VC-4 or Three STS-1s)

- E1 (used for Upstream AIS Indication) Bytes (Both Buses, VC-4 or Three STS-1s)

- H1/H2 Pointer Bytes (Both Buses, VC-4 or Three STS-1s)

- VT/TU Overhead Byte Processing

- J2 Byte

- 64 Byte Read Segment with Optional CR/LF Alignment

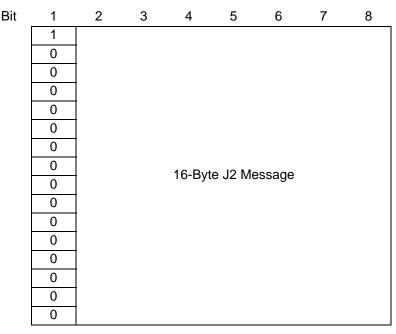

- 16 Byte Read Segment with Optional Trail Trace Message Comparison

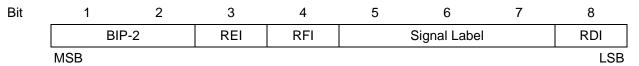

- V5/K4 Byte

- Three Bit or Single Bit RDI (Programmable for Each Channel)

- Detection/Recovery Selection: 5 or 10 event Option

- REI Error Counter

- RFI Detector

- BIP-2 Bit/Block Error Counter Option

- Signal Label Mismatch, Unequipped, and VC AIS detection

- Detection/Recovery: 5 events

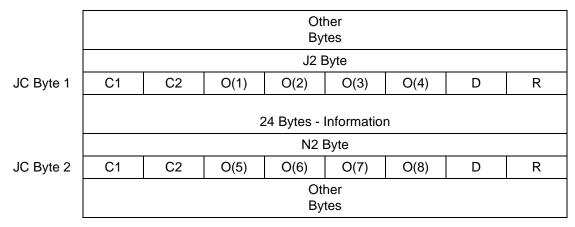

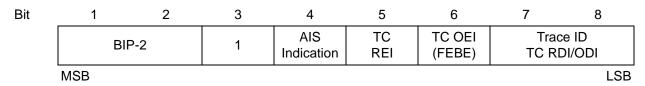

- N2 Byte

- Tandem Connection Option

- Trail Trace Message Comparison against Microprocessor Written Message

- Overhead Byte Access

- Both A and B Buses

- Desynchronizer

- Meets ANSI/ETSI/ITU Requirements

- Pointer Test Sequences

- Jitter/MTIE

- External Clock (Common to Both Rates)

- Leak Rate Control

- Microprocessor Control 10 Bits

- Line AIS (DS1/E1) Generation

- Mask Bits for Individual Alarms

- Global Mask Bit for all Alarms

- Microprocessor Control

- VT/TU Overhead Byte Insertion (per Channel)

- J2 Byte

- 64 or 16 byte Microprocessor Written Message

- J2 Forced to 0 Option

- V5/K4 Byte

- REI Insertion (from Drop Side VT/TU)

- RFI Value from Microprocessor

- BIP-2 Calculation and Insertion

- RDI Insertion

- Single or Three Bit

- RDI Generated for a Minimum of 20 Multiframes

- Mask bits for Alarms

- Global Mask Bit for all Alarms

- Microprocessor Control

- K4 Byte

- Input Bits 1 and 2 from External VT/TU interface

- N2 Byte

- Tandem Connection Option

- 16 byte Message Insertion

- Mask Alarm Bits or Microprocessor for TC ODI and RDI Generation

- Internal Multiframe Generation

- TC AIS Generation

- •TC Unequipped Generation

- Overhead Single Byte Insertion

- All Bytes

- Test purpose

- Unequipped Generation (per Channel)

- Supervisory Unequipped Generation Option

- Transmit AIS Generation

**DATA SHEET**

- TU/VT AIS

- Microprocessor Control

- DS1 or E1 AIS

- Alarms with mask Bits

- Microprocessor Control

- O-bit Access

- Drop and Add both A and B Buses

- Line Interface

- NRZ

- External Loss Of Signal or Coding Violation Input

- Rail

- CODEC

- AMI/B8ZS/HDB3

- Coding Violation Counter

- Loss Of Signal Detector

- VT/TU Interface

- Add Bus Timing Mode Only

- Fixed C1J1 Locations in Add Direction

- Two Modes: With or Without (Gapped Clock) Overhead Bytes

- Transmit Direction: Fixed Framing References and Clock Outputs, Data in

- Bits 1 and 2 in K4 byte clocked in with data for symmetrical clock

- Microprocessor Interface

- Intel or Motorola Split Bus

- LDS lead Option (683XX Processors)

- READY/DTACK Leads

- Interrupt Structure

- Positive, Negative, Positive/Negative Alarm Transitions

- Polling Registers with Mask Bits

- Alarm Summary Bits with Mask Bits

- One Second Measurements

- Counters

- Roll Over or Saturating

- One Second Measurements

- Test features

- Boundary Scan

- DS-1/E1 loopbacks

- Facility

- Line

- COMBUS loopback

- High Z all Leads (except Boundary Scan Output)

- PRBS Generator and Analyzer

- 2<sup>15</sup>-1 as defined in O.151 and T1M1.3/92-006R3 or QRSS (2<sup>20</sup>-1) as defined in ANSI T1.403-1195)

- Drop or Add Direction Placement

- Single Bit Error Generation for Transmit REI and BIP-2

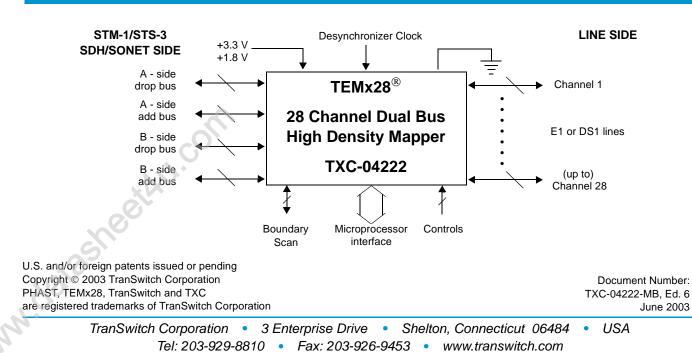

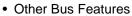

# **BLOCK DIAGRAM**

A block diagram of the TEMx28 device is shown in Figure 1. Further information on device operation and the interfaces to external circuits is provided in the following paragraphs.

Figure 1. TEMx28 TXC-04222 Block Diagram

**DATA SHEET**

# **BLOCK DIAGRAM DESCRIPTION**

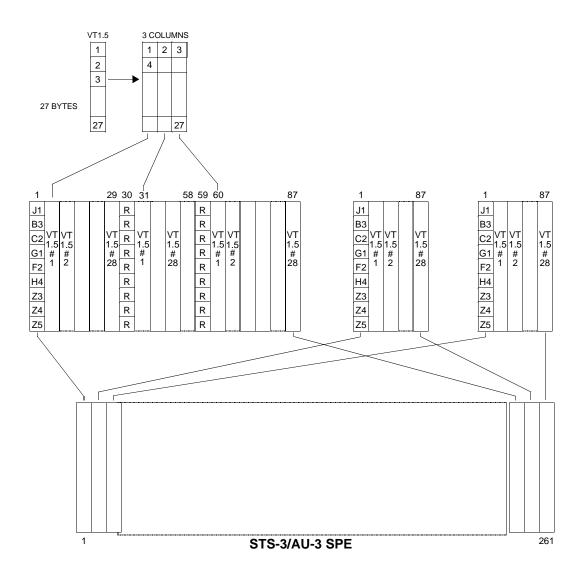

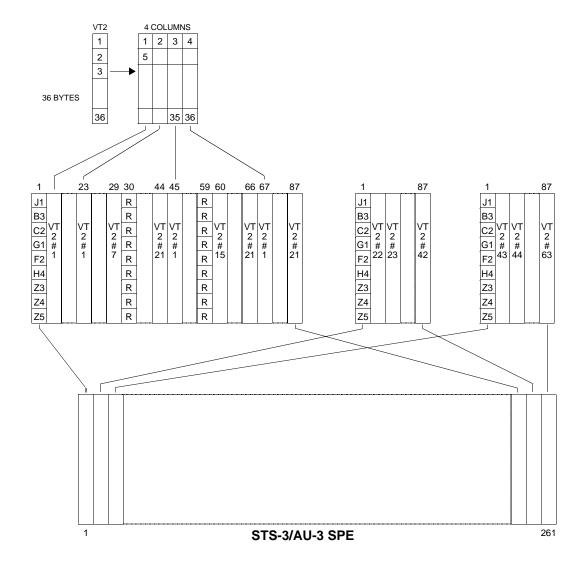

As illustrated in Figure 1, the TEMx28 interfaces to four buses, designated as A Drop, B Drop, A Add, and B Add. The four buses run at the STM-1/STS-3 rate of 19.44 Mbyte/s. For North American applications, asynchronous DS1 signals are carried in a floating Virtual Tributary 1.5 (VT1.5) format, while E1 signals are carried in a floating Virtual Tributary 2 (VT2) format. A maximum of 28 VT1.5 and 21 VT2 signals are carried in a Synchronous Transport Signal - 1 (STS-1) format. Three STS-1s are in turn carried in a STS-3 signal. For ITU-T applications, asynchronous E1 signals are carried in floating mode Tributary Unit - 12 (TU-12) format and DS1 signals are carried in floating mode Tributary Unit - 11 (TU-11) format. The TU-12s and TU-11s are carried in an STM-1 Virtual Container - 4 (VC-4) structure using Tributary Unit Group - 3 (TUG-3), or in the STM-1 Virtual Container - 3 (VC-3) structure using Tributary Unit Group - 2 (TUG-2) mapping schemes. Up to 28 DS1 or E1 signals, or a combination of DS1 and E1 signals, can be dropped from one bus (A Drop or B Drop) to the DS1 or E1 lines. A maximum of 28 asynchronous DS1 or E1 signals are converted into TU-11/TU-12 or VT1.5/VT2 format and are added to either of the add buses, or both, depending upon the mode of operation.

The TEMx28 can provide, on a per channel basis, the Virtual Container - 11 (VC-11), or the E1 Virtual Container - 12 (VC-12) formats in place of the DS1 or E1 signals for Virtual Concatenation applications. The VC format contains the payload and overhead bytes associated with the TU-11 and TU-12 formats.

The TEMx28 also supports the cross mapping feature specified in ITU Recommendation G707. This feature enables a DS1 asynchronous line signal to be carried in a TU-12/VT2 payload. This feature is supported in the TEMx28 on a per channel basis.

When the TEMx28 is configured for drop bus timing, the add buses are, by definition, byte- and multiframe-synchronous with their like-named drop buses, but are delayed by one or two byte times because of internal processing. For example, if a byte in the STM-1 Virtual Container - 4 (VC-4) structure using Tributary Unit Group - 3 (TUG-3), TU-12/VT2 is to be added to the A Add bus, the time of its placement on the bus is derived from the A Drop bus timing, and from software instructions specifying which TU/VT number is being added. Note that the TU/VT A drop bus selection can be different from the A add bus selection. An option is provided which enables the dropped timing signals to be sent as outputs on the add bus. When the device is configured for add bus timing, the add bus, parity, and add indicator signals are derived from the input add bus clock, C1J1V1 and SPE signals.

In the drop (receive) direction, the A Receive Drop Bus Interface block is identical to the B Receive block. The TU/VT Terminate block, Destuff block and Desychronizer block are repeated 56 times, 28 for each side (A and B sides). The Channel n Receive Interface blocks are repeated 28 times, one for each channel. The interface between a drop bus and the receive block consists of 12 input leads: a 19.44 MHz byte clock, byte-wide data, a C1J1 indicator which may be also carrying a V1 indication making the signal a C1J1V1 indicator, an SPE indicator, and an odd/even parity bit. The Drop C1J1V1 signal is used in conjunction with the Drop SPE signal to determine the location of the various bytes in the SONET/SDH format. A single J1 pulse identifies the starting location of the J1 byte in the VC-4 format, when the SPE signal is high. Three J1 pulses are provided for the STS-3 format, each identifying the starting location of the J1 byte in each of the three STS-1 signals.

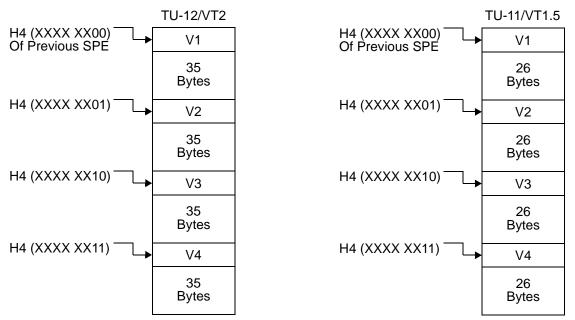

The TEMx28 can function with either a V1 pulse in the C1J1V1 signal, or it can use an internal H4 detector, for determining the location of the V1 byte. The V1 pulse location is used to determine the location of the pointer bytes V1 and V2. For STM-1 VC-4 operation, if the C1J1V1 signal is used, a one add or drop bus clock cycle wide pulse must occur every four frames and three drop bus clock cycles after the J1 pulse while the SPE is high. The J1 pulse identifies the J1 byte location (defined as the starting location for the VC-4) in the POH bytes. In the next column (first clock cycle) all the rows are assigned as fixed stuff. Similarly, in the next column (second clock cycle) all the rows are assigned as fixed stuff. The next column (third clock cycle) defines the start of TUG-3 A. This column is where the V1 pulse occurs every four frames. However, the actual V1 byte location is six clock cycles after the V1 pulse. For STS-3 operation, three V1 pulses must be present every four frames. Each of the three V1 pulses must be present three clock cycles after the corresponding J1 pulse, when the SPE signal is high.

Each drop bus (A and B) is monitored for parity errors, loss of clock, H4 multiframe alignment if selected, and an upstream SDH/SONET AIS indication. The TEMx28 can monitor either the TOH E1 order wire bytes or the H1/H2 bytes for an upstream AIS indication.

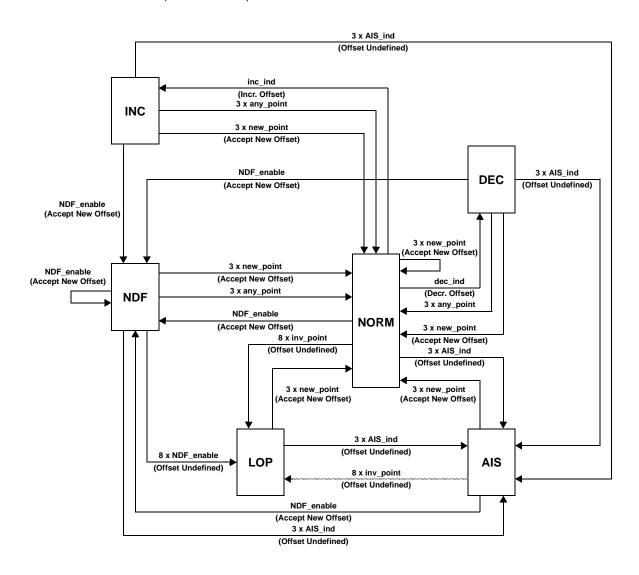

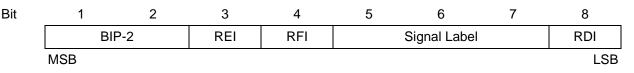

Each TU/VT Terminate block (A and B side) performs pointer processing using the V1 and V2 bytes. The pointer bytes are monitored for loss of pointer, Alarm Indication Signal (AIS), and a New Data Flag (NDF). The pointer tracking process is based on ETSI/ITU-T standards, which also meets ANSI requirements. Pointer increments and decrements are also counted, and the size bits are monitored for the correct value. This block also processes and monitors the various alarms found in the four overhead bytes. These operations including signal label mismatch detection, unequipped status detection, BIP-2 parity error detection and error counter, REI error counting, and single-bit or three-bit Remote Defect Indications (RDI). The TEMx28 performs a 16-byte J2 trail trace comparison on the channels selected. For 64-byte messages, the bytes are stored in a memory map segment for a microprocessor read cycle. The device also provides the TU tandem connection feature and performs the 16-byte message comparison for the N2 (formerly known as Z6) byte message.

All VT/TU overhead bytes, eight overhead communications channel bits (O-bits), the V1/V2 pointer bytes, and the V4 byte for each channel are available for a microprocessor read cycle. Also, the E1 order wire bytes, the H1/H2 pointer bytes, and the H4 bytes from the upstream circuitry are also available for a microprocessor read cycle.

A control bit for each port selects the TU/VT from either the A Drop or B Drop bus. The TU/VT is destuffed in the Destuff block using majority logic rules for the three sets of three justification control bits to determine if the two S-bits are data bits or frequency justification bits.

The Desynchronizer block removes the effects on the DS1 or E1 output of systemic jitter that might occur because of signal mappings and pointer movements in the network. The Desynchronizer block is comprised of a pointer leak buffer and a loop buffer. The pointer leak buffer spaces bursts of pointer movements more gradually over time and can accept up to five consecutive pointer movements. The loop buffer consists of a digital loop filter, which is designed to track the frequency of the received signal and to remove both transmission and stuffing jitter.

The Channel n Receive Interface block of each channel provides either NRZ data, positive and negative rail signal, or a VT/TU interface. Receive data (towards the line), for each of the channels, can be clocked out on either rising or falling edges of the clock. In addition, a control bit is provided for forcing the data and clock signals to a high impedance state (tristate), or to the zero state.

In the add (transmit) direction, the TEMx28 accepts a clock and either NRZ data or positive and negative rail signals. Data, for each of the channels, can be clocked in on either the falling or rising edge of the clock. In the NRZ mode, an external loss of clock indication or external coding violations can be provided. For the rail signal, coding violations are counted, and there is a loss of signal detector. A DS1/E1 AIS detector is also provided.

Each channel can also be configured for VT/TU interface for Virtual Concatenation data applications. When this interface is selected, a clock signal is provided for strobing in data for either the A or B bus. Four framing pulses are also provided which define the starting location of the VT1.5/TU-11 and VT2/TU-12. An option is provided for including the four overhead bytes. However, except for bits 1 and 2 in the K4 bytes, the other bits are ignored. Bits 1 and 2 in the K4 byte carry an extended signal label and information pertaining to the payload position within the Virtual Concatenation channel. The Virtual Concatenation channel will be assigned to n VT/TUs based on the data bandwidth required for the application.

**DATA SHEET**

For a NRZ or positive/negative rail transmit interface, the line signal is written into two FIFOs, one for add A side and the other for the B side, in one of the two Stuff/Synchronizer block pairs. Threshold modulation is used for the frequency justification process. Timing information from the A and B drop buses or from the A and B add buses is used to read the FIFO and perform the TU/VT justification process. The Synchronizer block permits tracking of an incoming signal having an average frequency offset as high as 120 ppm, and up to 1.5 UI of peak-to-peak jitter. Since the TEMx28 supports two different network architectures (DS1 and E1), two sets of blocks are provided for each channel. The TU/VT A and B add bus selection can be different. The VT/TU add bus selection can be different from the drop VT/TU selection. A control bit, and transmit line alarms, can also generate DS1/E1 AIS.

The TU/VT Build blocks format the TU/VT into an STS-3 or STM-1 structure for the asynchronous DS1 or E1 signals. The pointer value carried in the V1 and V2 bytes is transmitted with a fixed value of 78 for the VT1.5/TU-11 and 105 for the VT2/TU-12. Transmit access is provided for the eight overhead communications channel bits (O-bits) via the microprocessor. The microprocessor also writes the signal label, and the value of the J2 message, either as a 16-byte or a 64-byte message. The TEMx28 provides the TU tandem connection feature for the TU-11 or TU-12, including the transmission of the 16-byte message and the various alarms associated with the tandem connection feature. The device provides either single-bit or three-bit RDI using the V5 and K4 bytes. Local alarms, or the microprocessor, can generate the remote payload, server, or connectivity defect indications. The Remote Error Indication (REI) is inserted from the BIP-2 errors detected on the receive side, and BIP-2 parity is generated for the V5 byte. Control bits are provided for generating unequipped status, generating TU/VT AIS, and inserting REI and BIP-2 errors in the V5 byte. Control bits are also provided that enable the microprocessor to insert overhead byte test values, including the V1/V2 pointer bytes and the V4 byte.

The A Transmit block is identical to the B Transmit block. The interface between an add bus and a Transmit block consists of three input leads and ten output leads, when the add bus timing mode is selected. The input leads are a byte clock, a C1J1V1 indicator, and an SPE indicator. The output leads are byte-wide data, and a parity indicator, and an add-to-bus indicator signal. The Add C1J1V1 signal is used in conjunction with the Add SPE signal to determine the location of the various bytes in the SONET/SDH format.

When drop bus timing is selected, the output leads are byte-wide data, a parity indicator, and an add-to-bus indicator. The add bus clock, SPE and C1J1V1 signals, which are derived from the drop bus, can disabled or provided. The selection is performed by a lead.

The Microprocessor Input/Output Interface block consists of an Intel- or Motorola-compatible split address/data bus interface that provides access to assigned TEMx28 memory map addresses. Interrupt capability, interrupt mask bits, alarm summary bits, and software polling bits are also provided. The alarms that cause the interrupt can be set on positive, negative, or both positive and negative transitions.

Control bits are provided which enable a facility or a line loopback. In addition, a PRBS analyzer and generator are provided. A 2<sup>15</sup>-1 or 2<sup>20</sup>-1 PRBS pattern is supported. The analyzer and generator can be used in the drop or add line direction for additional testing flexibility.

The Test Access Port (TAP) block provides a five-lead Boundary Scan capability that conforms to the IEEE 1149.1 standard. This standard provides external boundary scan functions to read and write the external Input/Output leads from the TAP for board and component test.

The TEMx28 software driver has the same architecture of the other TranSwitch device drivers such as the ML3M software, and is meant to be easily integrated with them. The application software calls the driver functions to configure, control and manage the TEMx28 device. The device driver insulates the application from the internal details of the device register usage and provides a higher level of abstraction. Particularly powerful are the default configurations provided within the driver that allow one single command to bring the device to operational mode.

## TEMx28 TXC-04222

#### Figure 2. 1544 kbit/s Asynchronous Mapping

DATA SHEET

Engines for Global C

## TEMx28 TXC-04222

**DATA SHEET**

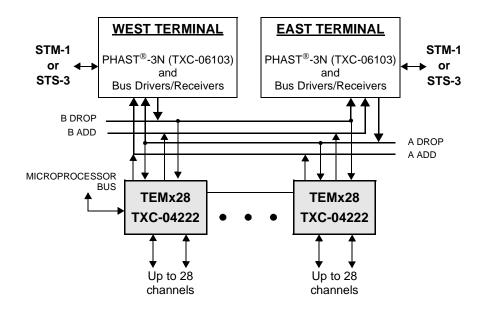

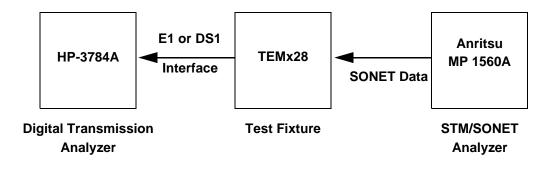

## APPLICATION EXAMPLE

The application diagram in Figure 5 below shows a fully configured bidirectional add/drop fiber multiplexer. Using the four-bus capability of the TEMx28, channels may be dropped from either direction with full time slot reuse in both directions. Using only the B Drop and the A Add buses provides add/drop service back to the network source only, and eliminates the block marked "East Terminal" for a terminal configuration.

Figure 5. Application Using the TEMx28 TXC-04222

### INTEROPERABILITY

The TEMx28 works directly with the following TranSwitch devices:

- QT1F-Plus (TXC-03103)

- T1Fx8 (TXC-03108)

- E1Fx8 (TXC-03109)

- QE1F-Plus (TXC-03114)

- PHAST<sup>®</sup>-3N (TXC-06103)

- T3BwP (TXC-06826)

| 17 o | of 246 | - |

|------|--------|---|

|      |        |   |

-

| Customers |           |

|-----------|-----------|

|           | TEMx28    |

|           | TXC-04222 |

# LEAD DIAGRAM

| AB | GND        |            | NC          |             |            | A14        | A10         | A8         | A4         | A0         |            |            |             |            | RCO2        |             | RCO3       |            | RPO4        |            | RNO5       |            |

|----|------------|------------|-------------|-------------|------------|------------|-------------|------------|------------|------------|------------|------------|-------------|------------|-------------|-------------|------------|------------|-------------|------------|------------|------------|

| AA | TESTI      | TMS        | тск         | NC          |            | D2         | A13         | A9         | A5         | A2         |            |            | RCO1        |            | RNO2        | RPO3        | TCI3       | TPI4       | RPO5        |            | RPO6       | TCI6       |

|    | TESTI      | TESTO      |             |             |            | D6         | D1          | A12        | A7         | A3         | SEL        | мото       | RNO1        | RPO2       |             | ТРІЗ        | RNO4       | RC05       | TCI5        | GND        | RC06       | RN07       |

| Y  |            |            | TESTI       |             | TDO        |            | D5          |            | ()<br>A11  | ()<br>A6   | ()<br>A1   | C<br>RP01  |             | U<br>TCI2  | ()<br>RNO3  | CO4         |            | U<br>TPI5  |             | RNO6       |            | C)<br>RPO8 |

| w  | $\bigcirc$ |            |             | TESTO       | $\bigcirc$ |            |             |            | O<br>VDD2  |            |            | O<br>VDD1  | $\bigcirc$  | $\bigcirc$ |             |             |            |            |             |            |            | RCO8       |

| v  | ABTE       |            |             |             |            | VDD2       |             |            | $\bigcirc$ | $\bigcirc$ |            |            | VDD2        | VDD2       |             |             | VDD2       | GND        |             | RPO7       | $\bigcirc$ |            |

| U  | VTFB15     | PM1S       | TEST        | TESTO       | VDD2       |            |             |            |            |            |            |            |             |            |             |             |            | VDD2       | RCO7        |            |            |            |

| т  | AAPAR      | VTFA15     |             | HIGHZ       | VDD1       |            |             |            |            |            |            |            |             |            |             |             |            | VDD1       |             | TPI8       | RPO9       | TPI9       |

| •  | AACIJI     |            |             | VTFA2       |            |            |             |            |            |            |            |            |             |            |             |             |            | VDD1       |             | RC09       | TCI9       |            |

| R  | ()<br>AA3  | ()<br>AA2  | ()<br>AA0   | AACLK       |            |            |             |            |            | CND        | GND        | CND        | GND         | GND        |             |             |            |            |             |            |            |            |

| Р  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  |             | $\bigcirc$ |            |             |            |            | GND        |            | GND        |             |            |             |             |            | $\bigcirc$ | $\bigcirc$  |            |            |            |

| N  | AA7        | AA5        | AA4         | AA1         | VDD2       |            |             |            | GND        | GND        | GND        | GND        | GND         | GND        |             |             |            | VDD2       | RCO10       | TCI10      |            | RCO11      |

|    | BACLK      |            |             | AA6         | VDD1       |            |             |            | GND        | GND        | GND        | GND        | GND         | GND        |             |             |            | VDD1       | RPO11       | RNO11      |            | TCI11      |

| м  | BASPE      | BACIJ      | 1 BA0       | BA2         | VDD1       |            |             |            | GND        | GND        | GND        | GND        | GND         | GND        |             |             |            | VDD1       | TPI12       | RC012      | RPO12      | U<br>TNI11 |

| L  | BA1        | BA3        | BA5         | BA6         | VDD2       |            |             |            | GND        | GND        | GND        | GND        | GND         | GND        |             |             |            |            |             |            | C<br>TCI12 |            |

| κ  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | Õ           | $\bigcirc$ |            |             |            |            |            |            |            |             |            |             |             |            | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| J  | BA4        |            | BA7         | AD0         | VDD2       |            |             |            | GND        | GND        | GND        | GND        | GND         | GND        |             |             |            | VDD2       | RCO14       |            | RCO13      | RPO13      |

| н  |            |            | AD1         | AD4         | VDD1       |            |             |            |            |            | •          |            |             | •          |             |             |            | VDD1       | TNI14       | RNO14      | 4 TNI13    | TCI13      |

|    | ADC1J1     | AD2        | AD5         | BDCLK       |            |            |             |            |            |            |            |            |             |            |             |             |            | VDD1       | TCI15       | RPO1       | 5 TPI14    | RPO14      |

| G  | ()<br>AD3  | AD6        | BDSPE       | ()<br>BD0   | VDD2       |            |             |            |            |            |            |            |             |            |             |             |            |            | ()<br>RNO16 |            | CO15       | CI14       |

| F  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$  | $\bigcirc$ |            |             |            |            |            |            |            |             |            |             |             |            | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

| Е  | AD7        | BDC1J1     |             | BD5         | GND        |            |             |            | $\bigcirc$ | $\bigcirc$ |            | VDD1       |             |            |             | VDD1        |            | GND        |             |            | RPO16      | RNO15      |

| D  | BDPAR      | BD2        | BD7         | GND         | TCI28      | TNI27      | RCO27       | RNO26      | TCI25      | TNI24      | RPO24      | TPI22      | TCI21       |            | RCO20       | RN019       | TCI18      | RPO18      | GND         | RNO17      | TCI16      | TPI15      |

|    | BD1        | BD3        | TNI28       | NC          | RPO28      | RNO27      | TPI26       | TNI25      | RPO25      | TPI24      | TCI23      | TNI22      | RCO22       | TPI21      | TCI20       | RPO20       | RCO19      | TPI18      | TCI17       | GND        | RCO17      | RCO16      |

| С  | BD6        |            |             | RCO28       | U<br>TPI27 |            | RPO26       | RNO25      | U<br>TCI24 | RC024      | U<br>TPI23 | C<br>RPQ23 | RNO22       |            | RCO21       | U<br>TPI20  |            | RPO19      |             |            | U<br>TPI17 |            |

| в  |            | TPI28      | C)<br>TCI27 | ()<br>RPO27 |            | CO26       | ()<br>TPI25 | CO25       |            |            |            | CO23       | ()<br>TCI22 |            | ()<br>RNO21 | ()<br>RPO21 |            |            | ()<br>TPI19 | U<br>TNI18 | CO18       |            |

| Α  | ۲          | 0          | Õ           | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | Õ           | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | 0          | $\bigcirc$  | 0          | $\bigcirc$  | $\bigcirc$  | $\bigcirc$ | Õ          | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ |            |

|    | 1          | 2          | 3           | 4           | 5          | 6          | 7           | 8          | 9          | 10         | 11         | 12         | 13          | 14         | 15          | 16          | 17         | 18         | 19          | 20         | 21         | 22         |

**DATA SHEET**

**DATA SHEET**

## LEAD DESCRIPTIONS

#### POWER SUPPLY, GROUND AND NO CONNECTS

| Symbol | Lead No.                                                                                                                                                    | I/O/P *     | Name/Function                                                                                                                                                                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD1   | E7, E8, E11, E12, E15,<br>E16, G5, G18, H5, H18,<br>L5, L18, M5, M18, R5,<br>R18, T5, T18, V7, V8,<br>V11, V12, V15, V16                                    | Р           | <b>VDD1:</b> +1.8 volt supply voltage, ±5%.                                                                                                                                                                                                             |

| VDD2   | E6, E9, E10, E13, E14,<br>E17, F5, F18, J5, J18,<br>K5, K18, N5, N18, P5,<br>P18, U5, U18, V6, V9,<br>V10, V13, V14, V17                                    | Р           | <b>VDD2:</b> +3.3 volt supply voltage, $\pm$ 5%. This supply voltage should be powered up prior to the 1.8 V (VDD1) supply voltage or at the same time. This supply voltage must not go below VDD1 by more than 0.5 V at any time including power down. |

| GND    | A1, A22, B2, C20, D4,<br>D19, E5, E18, J9 - J14,<br>K9 - K14,<br>L9 - L14,<br>M9 -M14,<br>N9 - N14,<br>P9 - P14,<br>V5, V18, W4, W19, Y3,<br>Y20, AB1, AB22 | Ρ           | Ground: 0 volt reference.                                                                                                                                                                                                                               |

| NC     | C4, W6, AA4, AB3                                                                                                                                            | T. Triatate | <b>No Connect:</b> NC leads are not to be connected, not even to another NC lead, but must be left floating. Connection of these leads may impair performance or cause damage to the device.                                                            |

\*Note: I = Input; O = Output; P = Power; T=Tristate

#### A DROP AND A ADD BUS I/O

| Symbol  | Lead No.                                | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------------------------------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCLK   | J2                                      | Ι     | TTL3V  | A Drop Bus Clock: This clock operates at 19.44 MHz for<br>STM-1/STS-3 operation. A Drop bus byte-wide data (AD7-AD0), the<br>parity bit (ADPAR), SPE indication (ADSPE), and the C1J1V1 indica-<br>tion (ADC1J1V1) are clocked in on falling edges of this clock. This<br>clock may also be used for add bus timing and deriving the<br>like-named add bus byte-wide data, add and TU/VT indications, and<br>parity bits. |

| ADPAR   | H1                                      | Ι     | TTL3V  | <b>A Drop Bus Parity Bit:</b> A parity bit input signal representing the odd or even parity calculation for each data byte, SPE, and C1J1V1 signal from the drop bus, or the data byte only.                                                                                                                                                                                                                              |

| AD(7-0) | E1, F2,<br>G3, H4,<br>F1, G2,<br>H3, J4 | Ι     | TTL3V  | <b>A Drop Bus Data Byte:</b> Byte-wide data that corresponds to the STM-1/STS-3 signal on the drop bus. The first bit received (dropped) corresponds to bit 7 which is lead E1.                                                                                                                                                                                                                                           |

\*See Input, Output and Input/Output Parameters section below for Type definitions.

| Symbol     | Lead No.                                | I/O/P  | Type *                  | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------------------------------------|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADSPE      | H2                                      | I      | TTL3V                   | <b>A Drop Bus SPE Indicator:</b> A signal that is active high for each byte of the STM-1 VC-4 and STS-3/STS-1 SPEs, and low for overhead byte times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ADC1J1(V1) | G1                                      | Ι      | TTL3V                   | A Drop Bus C1J1V1 Indications: An active high timing signal that carries STM-1/STS-3 frame and SPE information. This signal works in conjunction with the ADSPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1 and STS-3 signals, when ADSPE signal is low. The J1 pulse identifies the starting location of the J1 byte in the STM-1 VC-4 signal when ADSPE is high. Three J1 pulses identify the starting location for each of the three STS-1 signals in the STS-3 signal. A single V1 pulse identifies the location for the V1/V2 bytes in the TUG-3 within the VC-4. Three V1 pulses identify the location of the V1/V2 bytes within each of the three STS-1s. The V1 pulses may be absent. In which case the mapper will detect the starting location of the multiframe within the H4 byte. |

| AACLK      | P4                                      | I/O(T) |                         | <b>A Add Bus Clock:</b> When the add bus timing mode is selected (lead ABUST is low), this input must be provided for add bus timing. This clock operates at 19.44 MHz for STM-1/STS-3 operation. The add bus SPE indication (AASPE), and the C1J1V1 indication (AAC1J1V1) are clocked in on falling edges of this clock. Add bus byte-wide data (AA7-AA0), add indicator (AADD), and the parity bit (AAPAR) are clocked out on rising edges of the clock during the time slots that correspond to the selected TU/VT. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, this clock, which is derived from the like-named drop bus is an output. When lead ABTE is high in the drop bus timing mode, this lead is disabled.                                                                            |

| AAPAR      | T1                                      | O(T)   | CMOS3V<br>8mA           | <b>A Add Bus Parity Bit:</b> An odd or even parity output signal that is calculated over the byte-wide add data. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, parity may be also calculated for the C1J1V1 and SPE signals. This lead is only active when there is data being added to the add bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AA(7-0)    | N1, M4,<br>N2, N3,<br>P1, P2,<br>N4, P3 | O(T)   | CMOS3V<br>8mA           | <b>A Add Bus Data Byte:</b> Byte-wide data that corresponds to the selected TU/VT. The first bit transmitted (added) corresponds to bit 7 which is lead N1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AASPE      | R2                                      | I/O(T) | TTL3V/<br>CMOS3V<br>8mA | <b>A</b> Add Bus SPE Indicator: When the add bus timing mode is selected, this signal must be provided for add bus timing. This signal must be high during each byte of the STM-1/STS-3 payload, and low during Transport Overhead byte times. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, this signal, which is derived from the like-named drop bus is an output. When lead ABTE is high in the drop bus timing mode, this lead is disabled.                                                                                                                                                                                                                                                                                                                                                   |

**DATA SHEET**

| Symbol     | Lead No. | I/O/P  | Type *                  | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AAC1J1(V1) | R1       | I/O(T) | TTL3V/<br>CMOS3V<br>8mA | <b>A Add Bus C1J1V1 Indications:</b> An active high timing signal that carries STM-1/STS-3 frame and SPE information. This signal works in conjunction with the AASPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1 and STS-3 signals, when AASPE signal is low. The J1 pulse identifies the starting location of the J1 byte in the STM-1 VC-4 signal when ADSPE is high. Three J1 pulses identify the starting location for each of the three STS-1 signals in the STS-3 signal. A single V1 pulse identifies the starting location for the V1/V2 bytes in the TUG-3 within the VC-4. Three V1 pulses identify the starting location of the V1/V2 bytes within each of the three STS-1s. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, this signal, which is derived from the like-named drop bus is an output. When lead ABTE is high in the A drop bus timing mode, this lead is disabled. |

| AADD       | R3       | 0      | CMOS3V<br>8mA           | <b>A Add Bus Add Data Present Indicator:</b> This normally active low signal is present when output data to the A Add bus is valid. It identifies the location of all of the TU/VT time slots being selected. When control bit ADDI (bit 0, register 03AH) is 1, the indicator is active high instead of active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **B DROP AND B ADD BUS I/O**

| Symbol  | Lead No.                                | I/O/P | Туре  | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDCLK   | G4                                      | Ι     | TTL3V | <b>B Drop Bus Clock:</b> This clock operates at 19.44 MHz for STM-1/STS-3 operation. A Drop bus byte-wide data (BD7-BD0), the parity bit (BDPAR), SPE indication (BDSPE), and the C1J1V1 indication (BADC1J1V1) are clocked in on falling edges of this clock. This clock may also be used for add bus timing and deriving the like-named add bus byte-wide data, add and TU/VT indications, and parity bits. |

| BDPAR   | D1                                      | Ι     | TTL3V | <b>B Drop Bus Parity Bit:</b> A parity bit input signal representing the odd or even parity calculation for each data byte, SPE, and C1J1V1 signal from the drop bus, or the data byte only.                                                                                                                                                                                                                  |

| BD(7-0) | D3, B1,<br>E4, E3,<br>C2, D2,<br>C1, F4 | Ι     | TTL3V | <b>B Drop Bus Data Byte:</b> Byte-wide data that corresponds to the STM-1/STS-3 signal on the drop bus. The first bit received (dropped) corresponds to bit 7 which is lead D3.                                                                                                                                                                                                                               |

| BDSPE   | F3                                      | I     | TTL3V | <b>B Drop Bus SPE Indicator:</b> A signal that is active high for each byte of the STM-1 VC-4 and STS-3/STS-1 SPEs, and low for overhead byte times.                                                                                                                                                                                                                                                          |

| Symbol     | Lead No.                             | I/O/P  | Туре                    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDC1J1(V1) | E2                                   | Ι      | TTL3V                   | <b>B</b> Drop Bus C1J1V1 Indications: An active high timing signal that carries STM-1/STS-3 frame and SPE information. This signal works in conjunction with the BDSPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1 and STS-3 signals, when BDSPE signal is low. The J1 pulse identifies the starting location of the J1 byte in the STM-1 VC-4 signal when BDSPE is high. Three J1 pulses identify the starting location for each of the three STS-1 signals in the STS-3 signal. A single V1 pulse identifies the location for the V1/V2 bytes in the TUG-3 within the VC-4. Three V1 pulses identify the location of the V1/V2 bytes within each of the three STS-1s. The V1 pulses may be absent. In which case the mapper will detect the starting location of the multiframe within the H4 byte. |

| BACLK      | M1                                   | I/O(T) | TTL3V/<br>CMOS3V<br>8mA | <b>B</b> Add Bus Clock: When the add bus timing mode is selected (lead ABUST is low), this input must be provided for add bus timing. This clock operates at 19.44 MHz for STM-1/STS-3 operation. The add bus SPE indication (BASPE), and the C1J1V1 indication (BAC1J1V1) are clocked in on falling edges of this clock. Add bus byte-wide data (BA7-BA0), add indicator (BADD), and the parity bit (BAPAR) are clocked out on rising edges of the clock during the time slots that correspond to the selected TU/VT. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, this clock, which is derived from the like-named drop bus is an output. When lead ABTE is high in the drop bus timing mode, this lead is disabled and forced to the high impedance state.                                            |

| BAPAR      | M2                                   | O(T)   | CMOS3V<br>8mA           | <b>B Add Bus Parity Bit:</b> An odd or even parity output signal that is calculated over the byte-wide add data. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, parity may be also calculated for the C1J1V1 and SPE signals. This lead is only active when there is data being added to the add bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BA(7-0)    | J3, K4, K3,<br>J1, K2, L4,<br>K1, L3 | O(T)   | CMOS3V<br>8mA           | <b>B Add Bus Data Byte:</b> Byte-wide data that corresponds to the selected TU/VT. The first bit transmitted (added) corresponds to bit 7 which is lead J3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BASPE      | L1                                   | I/O(T) |                         | <b>B Add Bus SPE Indicator:</b> When the add bus timing mode is selected, this signal must be provided for add bus timing. This signal must be high during each byte of the STM-1/STS-3 payload, and low during Transport Overhead byte times. When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, this signal, which is derived from the like-named drop bus is an output. When lead ABTE is high in the drop bus timing mode, this lead is disabled and forced to the high impedance state.                                                                                                                                                                                                                                                                                                                   |

**DATA SHEET**

| Symbol     | Lead No. | I/O/P  | Туре                    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAC1J1(V1) | L2       | I/O(T) | TTL3V/<br>CMOS3V<br>8mA | <b>B</b> Add Bus C1J1V1 Indications: An active high timing signal that carries STM-1/STS-3 frame and SPE information. This signal works in conjunction with the AASPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1 and STS-3 signals, when AASPE signal is low. The J1 pulse identifies the starting location of the J1 byte in the STM-1 VC-4 signal when ADSPE is high. Three J1 pulses identify the starting location for each of the three STS-1 signals in the STS-3 signal. A single V1 pulse identifies the starting location for the V1/V2 bytes in the TUG-3 within the VC-4. Three V1 pulses identify the starting location of the V1/V2 bytes within each of the three STS-1 <u>s</u> . When drop bus timing is selected (lead ABUST is high), and lead ABTE is low, this signal, which is derived from the like-named drop bus is an output. When lead ABTE is high in the B drop bus timing mode, this lead is disabled and forced to the high impedance state. |

| BADD       | М3       | 0      | CMOS3V<br>8mA           | <b>B Add Bus Add Data Present Indicator:</b> This normally active low signal is present when output data to the A Add bus is valid. It identifies the location of all of the TU/VT time slots being selected. When control bit ADDI (bit 0, register 03AH) is 1, the indicator is active high instead of active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# CHANNEL n LINE INTERFACE (n = 1, up to 28)

| Symbol                             | Lead No.                                                                                                                                                              | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCOn<br>RCLKn<br>RVTCn<br>(n=1-28) | AA13, AB15,<br>AB17, W16,<br>Y18, Y21, U19,<br>V22, R20, N19,<br>N22, L20, J21,<br>J19, F21, C22,<br>C21, A21, C17,<br>D15, B15, C13,<br>A12, B10, A8,<br>A6, D7, B4  | O(T)  | CMOS3V<br>4mA | <b>Receive Channel n Rail, NRZ, TU/VT Output Clock:</b> A DS1,<br>E1, or VT/TU clock output. Data (Rail or NRZ) is clocked out on<br>positive transitions of this clock when control bit RnCLKI (bit 3,<br>register X+000H) is a 1. When control bit RnCLKI is a 0, data is<br>clocked out on negative transitions of this clock. RCOn is the<br>E1/T1 rail clock (control bits RnLINT1/0 (bits 7/6, register<br>X+006H) are 10). RCLKn is the NRZ clock (control bits<br>RnLINT1/0 are 01). RVTCn is the TU/VT NRZ clock (control<br>bits RnLINT1/0 are 11). This lead is disabled when control bits<br>RnLINT1/0 are 00. When disabled, this lead can be forced to<br>ether a high impedance state (control bit RnOUTL (bit 5, regis-<br>ter 006H) is a 0), or to zeros (control bit RnOUTL is a 1). Lead<br>AA13 is RCO1/RCLK1/RVTC1 (Channel 1).<br><b>Note:</b> See Description for control bit RnOUTL for detailed operation. |

| RPOn<br>RDATn<br>RVTDn<br>(n=1-28) | W12, Y14,<br>AA16, AB19,<br>AA19, AA21,<br>V20, W22, T21,<br>P20, M19, L21,<br>J22, G22, G20,<br>E21, E19, D18,<br>B18, C16, A16,<br>A14, B12, D11,<br>C9, B7, A4, C5 | O(T)  | CMOS3V<br>4mA | <b>Receive Channel n Data Positive Rail, NRZ, TU/VT:</b> When control bits RnLINT1/0 are set to 10, positive rail E1/T1 data (RPOn) is provided on this lead. When control bit RnLINT1/0 is set to 01, NRZ E1/T1 data (RDATn) is provided on this lead. When control bits RnLINT1/0 are set to 11, VT/TU NRZ data (RVTDn) is provided on this lead. This lead is disabled when control bits RnLINT1/0 are 00. When disabled, this lead can be forced to ether a high impedance state (control bit RnOUTL is a 0), or to zeros (control bit RnOUTL is a 1). Lead W12 is RPO1/RDAT1/RVTD1 (Channel 1).                                                                                                                                                                                                                                                                                                                                |

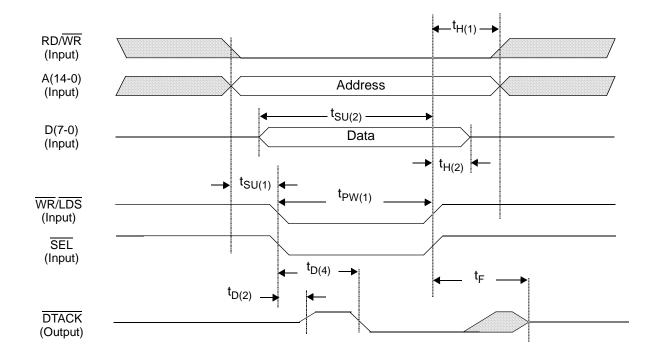

| Symbol                             | Lead No.                                                                                                                                                             | I/O/P  | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |