# BU8309AS BU8309AK

# Pulse and tone dialer for telephone set

The BU8309AS and BU8309AK are large scale integrated circuits for telephone sets. The LSI has both a pulse dialer and tone, and a 32-digit redial buffer. It also has an internal serial input interface that allows control of the LSI using an external CPU.

#### **Features**

- since the chip includes both a pulse and tone, it is possible to mix dial pulse and tone

- internal 4 × 4 encoder (4 × 4 matrix, 4-bit parallel output) together with serial interface allow external control from a CPU

- in the event of a power failure when CPU control may be lost, dial signals can still be sent from a keypad because line current is used to power the LSI

- built-in 32-digit redialing memory in pulse mode. In tone mode, a digit in the memory is used to store the mode, so the maximum number of digits is 31

- power supply voltage (V<sub>DD</sub>) is independent of the DTMF output level

- LSI complies with standard specifications in Japan, U.S. A., Canada, U.K., Korea, Taiwan, and Australia

# **Applications**

telephone and cordless telephone sets

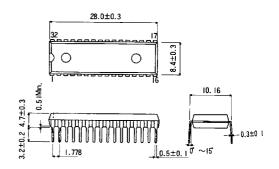

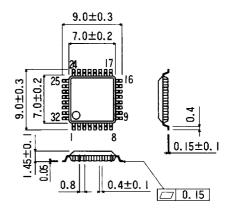

#### Dimensions (Units: mm)

#### **BU8309AS (SDIP32)**

#### BU8309AK (QFP32)

# BU8309AS, BU8309AK Telephone systems: Pulse and tone dialer

# Absolute maximum ratings ( $T_a = 25^{\circ}C$ )

| Parameter            |                     | Symbol            | Limits                                       | Unit  | Conditions                                                                                            |

|----------------------|---------------------|-------------------|----------------------------------------------|-------|-------------------------------------------------------------------------------------------------------|

| Power supply voltage |                     | $V_{DD}$          | 7.0                                          | ٧     |                                                                                                       |

| Input voltage        |                     | V <sub>IN</sub>   | $V_{SS} - 0.3 \sim V_{DD} + 0.3$             | ٧     | Applies to ROW1 ~ ROW4, COL1 ~ COL4, HS, MODEIN, OSCIN, 67%/60%, LH/SH, KEY/CPU, SD, SCK, and DL pins |

| Output               | 1 V <sub>out1</sub> |                   | V <sub>SS</sub> - 0.3 ~ V <sub>DD</sub> +0.3 | V     | Applies to OSCOUT, KEYTONE, and DTMF pins                                                             |

| voltage              | 2                   | V <sub>out2</sub> | V <sub>SS</sub> -0.3 ~ 7.0                   | ٧     | Applies to MODEOUT, MFMUTE, DPMUTE, DP, MON, KEYDOWN, and PD0 ~ PD3 pins                              |

| Power BU8309AS       |                     |                   | 900                                          | mW    | Reduce power by 9 mW/°C for each degree above 25°C.                                                   |

| dissipation BU8309AK |                     | P <sub>d</sub>    | 400                                          | 11144 | Reduce power by 4 mW/°C for each degree above 25°C.                                                   |

| Operating te         | emperature          | T <sub>opr</sub>  | <b>−10</b> ~ <b>+60</b>                      | °C    |                                                                                                       |

| Storage tem          | perature            | T <sub>stg</sub>  | <b>−55 ~ +125</b>                            | °C    |                                                                                                       |

# Recommended operating conditions (T<sub>a</sub> = 25°C )

| Parameter                   | Symbol           | Min | Typical  | Max | Unit | Conditions                                                                                                                                                                              |

|-----------------------------|------------------|-----|----------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage        | V <sub>DD</sub>  | 2.0 | 3.0      | 5.5 | ٧    |                                                                                                                                                                                         |

| Oscillation frequency       | fosc             |     | 3.579545 |     | MHz  | Recommended parts (Mfg. part numbers listed below are 3-pin surface-mount devices with internal capacitors): Murata CSTC3.58MGU300GA Fujitsu FAR-C4CA-03580-K02 Kyocera KBR-3.58MWS-BU4 |

| Key input time              | t <sub>KD</sub>  | 40  |          |     | ms   | Minimum time to process a key input (down) operation is 40 ms.                                                                                                                          |

| Key release time            | t <sub>KU</sub>  | 5   |          |     | ms   | Minimum time to process a key release (up) operation is 5 ms.                                                                                                                           |

| MODEIN pull-up resistance   | R <sub>MIU</sub> | 0   |          | 10  | kΩ   |                                                                                                                                                                                         |

| MODEIN pull-down resistance | R <sub>MID</sub> | 0   |          | 10  | kΩ   |                                                                                                                                                                                         |

Note: For test circuit, see Figure 2

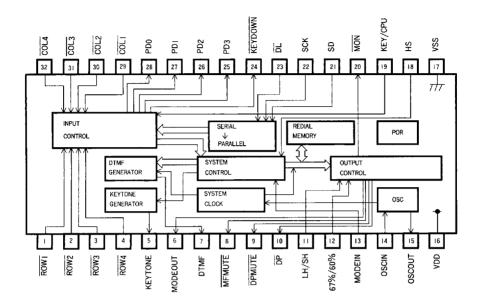

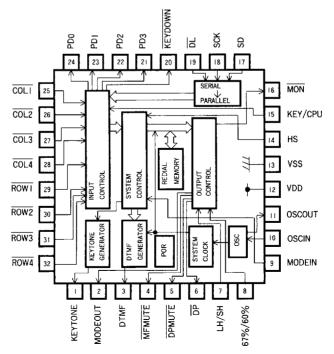

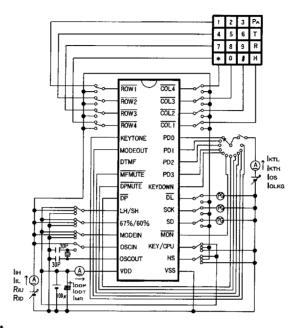

# **Block diagram**

### BU8309AS (SDIP32)

# BU8309AK (QFP32)

Table 1 Pin description

| Pin no<br>SDIP32 |                    | Symbol                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|--------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 ~ 4<br>29 ~ 32 | 29 ~ 32<br>25 ~ 28 | Key input: ROW1 ~ ROW4 and COL1 ~ COL4                           | These pins can either be connected to a 3 × 4 (2 of 7) or a 4 × 4 keypad. A valid key entry sequence can be either:  Connecting a ROW input to a COL input.  Taking a ROW input and a COL input LOW simultaneously.  In pulse mode, if more than one key is pressed at the same time, the entry is ignored.  In tone mode, you can generate a single tone by pressing two or more keys in the same row or the same column. If multiple keys not in the same row or the same column are pressed, the entry is ignored.                   |

| 18               | 14                 | HS<br>(Hook switch<br>input)                                     | When this pin is HIGH, the IC perceives the phone as on hook, when the pin is LOW, the phone is off hook. The IC is set to the off-hook state during a dial signal transmission and to the on-hook state during memory hold. In the on-hook state, only redial buffer memory erase is enabled. The oscillator circuit does not operate during redial buffer memory erase. Current does flow in the pull-up resistors (SCK, $\overline{\text{DL}}$ ). There is current flow in the shift register, the only current in the on-hook state |

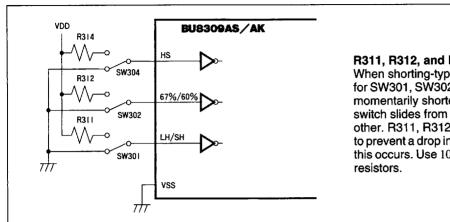

| 12               | 8                  | 67%/60%<br>(Dial pulse break<br>ratio switching)                 | Switches the dial pulse break. When this pin is HIGH, the IC uses the 67% ratio; when the pin is LOW, the IC uses the 60% ratio.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6                | 2                  | MODEOUT<br>(Mode status<br>output)                               | This pin is forced to the high impedance state when the output mode is set for pulse, and to LOW when the output mode is set for tone generation. This pin also goes to the high impedance state when the IC is in the on-hook state. The state on the MODEIN pin can also be output at MODEOUT by going off-hook and pressing the $P_{\rm A}$ key. (In this case, no pause is generated.) MODEOUT goes LOW if MODEIN is LOW, and HIGH if MODEIN is HIGH or is in the high impedance state (Z).                                         |

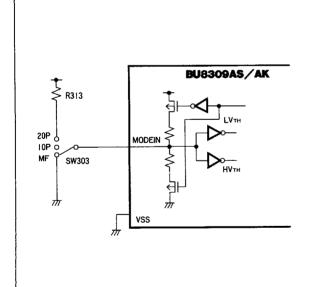

| 13               | 9                  | MODEIN<br>(Mode select)                                          | This pin has three states. LOW is used to select tone mode. Z (high impedance) is used to select the $10$ pps pulse mode and HIGH is used to select the $20$ pps pulse mode. When the T key is pressed, tone mode is selected regardless of the state of this pin. If the HIGH and LOW levels are applied to this pin through a resistor, the resistance should be $10~\mathrm{k}\Omega$ or less.                                                                                                                                       |

| 14<br>15         | 10<br>11           | OSCIN,<br>OSCOUT<br>(Internal<br>oscillator input<br>and output) | Connect a piezoelectric or ceramic resonator between OSCIN and OSCOUT. For ceramic resonators, please refer to notes in the table "Recommended operating conditions" on page 100.                                                                                                                                                                                                                                                                                                                                                       |

# Table 1 Pin description

| Pin no<br>SDIP32 | Pin no<br>QFP32 | Symbol                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|-----------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

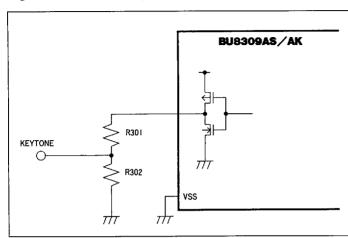

| 5                | 1               | KEYTONE                   | This has a CMOS output. When the IC is in the off-hook state, this pin outputs a key-press confirmation tone (square wave) for all valid key presses in pulse mode and for valid $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , and $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , and $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , and $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ , $P_A$ , and $P_A$ , $P_A$ |

| 11               | 7               | LH/SH                     | When set to LOW, the hooking time is set to 85 ms; when set to HIGH, 708 ms is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

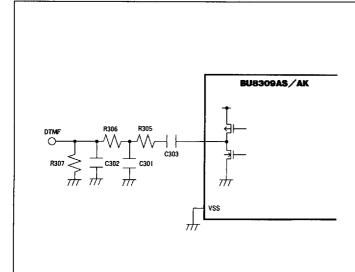

| 7                | 3               | DTMF                      | In tone mode, this pin outputs the DTMF signal for the key that was pressed. It is a CMOS output that is LOW when no DTMF tone is being transmitted. If the KEY/CPU pin is HIGH, holding a key down sends out a continuous DTMF signal. If the KEY/CPU pin is LOW, holding the DL pin LOW causes a continuous DTMF signal to be sent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  |                 |                           | A dc bias (a dc level between the minimum and maximum peaks of the DTMF signal) is output on the DTMF pin during the tone pre-pause time ( $t_{PPM}$ ), the tone mute overlap time ( $t_{MOM}$ ), and the tone inter-digital pause time ( $t_{IDPM}$ ) between consecutive key inputs. This bias keeps popping sounds from being generated by the amplifier and capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

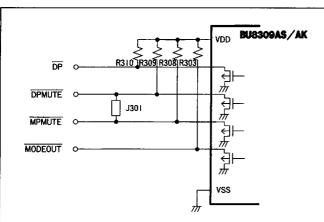

| 8                | 4               | MFMUTE                    | This pin is LOW when a DTMF signal is being output or an on-hook sequence is in progress. It goes to the high impedance state (Z) during pulse mode, or if no DTMF signal is being output, or the unit is on-hook.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9                | 5               | DPMUTE                    | This pin is LOW when a DTMF signal is being output or an on-hook sequence is in progress. It goes to the high impedance state (Z) during pulse mode, or if no DTMF signal is being output or the unit is on-hook.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10               | 6               | DP                        | In pulse mode, this pin outputs dial pulses (contact make and break sequences) corresponding to the pressed keys (Z = make; LOW = break). This is an N-channel, open drain (tri-state) output that goes to the high impedance state when not sending dial pulses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19               | 15              | KEY/CPU                   | This pin determines whether the input from the keypad or the CPU (serial data input) is used. The CPU input is used when this pin is LOW, the keypad input is used when this pin is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

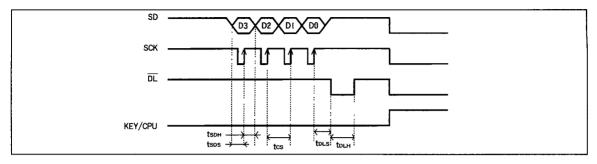

| 21               | 17              | SD<br>Serial data input   | When the KEY/CPU pin is LOW, serial data can be entered on this pin. This data is entered through the internal resistance of the IC. When the KEY/CPU pin is HIGH, the SD pin is pulled LOW by the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22               | 18              | SCK<br>Serial clock input | When the KEY/CPU pin is LOW, a serial clock can be connected to this pin. Data is clocked in on the rising edge of the clock pulse. When KEY/CPU pin is HIGH, this pin is pulled LOW by the IC. When $\overline{\text{DL}}$ is LOW, serial data shifting by SCK within the IC is inhibited.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# BU8309AS, BU8309AK Telephone systems: Pulse and tone dialer

# Table 1 Pin description

| Pin no<br>SDIP32 |         | Symbol                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|---------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23               | 19      | DL<br>(Data latch input) | When the KEY/CPU pin is LOW, data latch input is enabled on this pin. Serial data bits (from the SD input) that have been clocked into the IC by SCK are latched by taking this pin LOW for the duration of the latch time ( $t_{DLH}$ ). This pin should be held LOW whenever data is being latched (sent to the dialer). When the KEY/CPU pin is HIGH, this pin is pulled LOW by the IC.                                                                                                                                                                 |

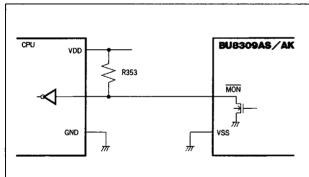

| 20               | 16      | MON                      | This pin is LOW while the dial signal (including pauses) is being transmitted. It is in the high impedance state (Z) if no dial signal is being sent, or if the HS pin is HIGH (on-hook). $\overline{\text{MON}}$ goes LOW at the end of the transmit start time, $t_{tso}$ (which follows the falling edge of $\overline{\text{DL}}$ ). It goes HIGH at the end of the dial signal transmission, at the end of the mute overlap time 1 ( $t_{TMO2}$ ), at the end of mute overlap time 2 ( $t_{TMO2}$ ), and at the tone mute overlap time ( $t_{MOM}$ ). |

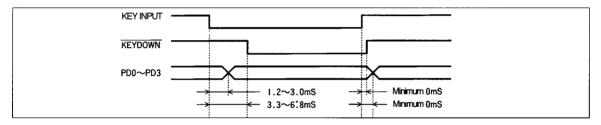

| 24               | 20      | KEYDOWN                  | When HS is LOW (off hook), this pin goes LOW when a single key is pressed, regardless of the state of the KEY/CPU pin. If HS is HIGH or no single key is being pressed, it is in the "Z" state                                                                                                                                                                                                                                                                                                                                                             |

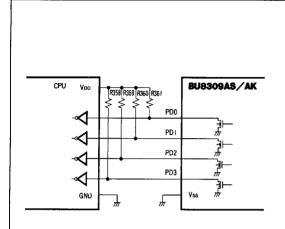

| 28 ~ 25          | 24 ~ 21 | PDO ~ PD3                | When the HS pin is LOW (off hook), these four pins output 4-bit (converted) parallel data corresponding to the keys that are pressed, regardless of the state of the KEY/CPU pin. Even non-valid key entries are sent (for instance, if more than one key is pressed simultaneously). KEYDOWN, however, remains in the Z state if multiple keys are pressed. Therefore, data should only be taken off these pins when KEYDOWN is LOW.  The Z state is defined as 1, and LOW is 0. The pins go to the Z state when no data is being output, or HS is HIGH.  |

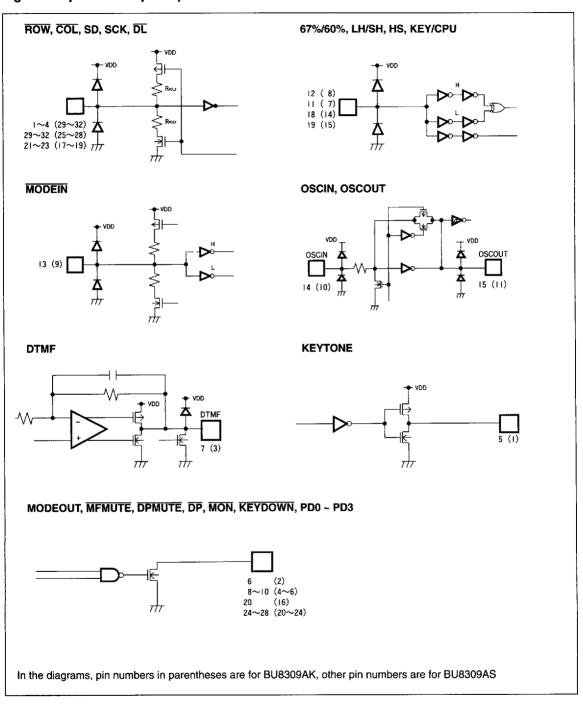

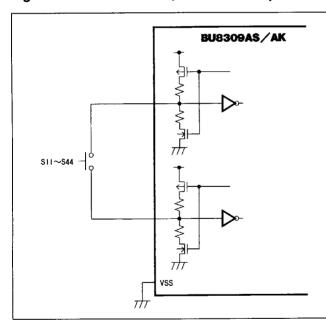

#### Figure 1 Input and output equivalent circuits

#### BU8309AS, BU8309AK Telephone systems: Pulse and tone dialer

#### Input and output pin specifications

#### Table 2 Logic inputs

| Pin name | HIGH                                          | Z                   | LOW                                           | Input type                         |  |

|----------|-----------------------------------------------|---------------------|-----------------------------------------------|------------------------------------|--|

| HS       | On hook                                       | Should not be used  | Off hook                                      | CMOS<br>(Schmidt trigger<br>input) |  |

| 67%/60%  | Pulse break ratio = 67%                       | Should not be used  | Pulse break ratio = 60%                       | CMOS                               |  |

| MODEIN   | Pulse mode = 20 pps                           | Pulse mode = 10 pps | Tone mode                                     | CMOS                               |  |

| LH/SH    | Hook time = 708 ms<br>Hook pause time = 1.0 s | Should not be used  | Hook time = 85 ms<br>Hook pause time = 406 ms | смоѕ                               |  |

| KEY/CPU  | Keypad input                                  | Should not be used  | CPU input                                     | CMOS<br>(Schmidt trigger<br>input) |  |

# Table 3 Serial data inputs

| Pin  | Pin function       | Input type                      |               |                |  |  |  |  |

|------|--------------------|---------------------------------|---------------|----------------|--|--|--|--|

| name | riii fulletion     |                                 | KEY/CPU = LOW | KEY/CPU = HIGH |  |  |  |  |

| SD   | Serial data input  | CMOS                            | Pull-up       | Pull-down      |  |  |  |  |

| SCK  | Serial clock input | CMOS<br>(Schmidt trigger input) | Pull-up       | Pull-down      |  |  |  |  |

| DL   | Data latch input   | CMOS                            | Pull-up       | Pull-down      |  |  |  |  |

# Table 4 Output pin circuit types

| Output  | Output type     | Output    | Output type     |

|---------|-----------------|-----------|-----------------|

| MODEOUT | NMOS open drain | DPMUTE    | NMOS open drain |

| KEYTONE | CMOS open drain | MON       | NMOS open drain |

| DTMF    | CMOS open drain | KEYDOWN   | NMOS open drain |

| MFMUTE  | NMOS open drain | PD0 ~ PD3 | NMOS open drain |

| DP      | NMOS open drain |           |                 |

MON, KEYDOWN, and PDO ~ PD3 output signals are normally output regardless of the state of the KEY/CPU pin. When the HS pin goes HIGH (off hook) the IC enters standby mode, with all of the above outputs in the high impedance (Z) state.

# DC electrical characteristics (unless otherwise noted, $T_a = 25~^{\circ}\text{C},~V_{DD} = 3.0~\text{V})$

| Parameter                       | Symbol            | Min                 | Typical | Max                 | Unit | Conditions                                                                                                                        |

|---------------------------------|-------------------|---------------------|---------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

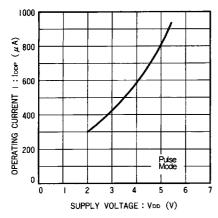

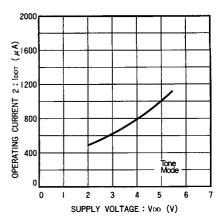

| Supply current, pulse mode      | I <sub>DDP</sub>  |                     | 0.45    | 0.60                | mA   | Output not loaded; pulse mode                                                                                                     |

| Supply current, tone mode       | I <sub>DDT</sub>  |                     | 0.60    | 1.00                | mA   | Output not loaded; tone mode                                                                                                      |

| Memory retention current        | <sub>MR</sub>     |                     | 0.01    | 2.0                 | μΑ   |                                                                                                                                   |

| Memory retention voltage        | V <sub>MR</sub>   | 1.0                 |         |                     | ٧    |                                                                                                                                   |

| Input voltage 1 HIGH            | V <sub>IIH</sub>  | 0.8 V <sub>DD</sub> |         | V <sub>DD</sub>     | ٧    | V <sub>DD</sub> = 2.0 ~ 5.5 V<br>Applies to ROW1 ~ ROW4, COL1 ~                                                                   |

| Input voltage 1 LOW             | V <sub>I1L</sub>  | V <sub>ss</sub>     |         | 0.2 V <sub>DD</sub> | ٧    | COL4, HS, OSCIN, SD, and DL pins                                                                                                  |

| Input voltage 2 HIGH            | V <sub>I2H</sub>  | 0.9 V <sub>DD</sub> |         | V <sub>DD</sub>     | ٧    | V <sub>DD</sub> = 2.0 ~ 5.5 V<br>Applies to MODEIN, 67%/60%, LH/SH,                                                               |

| Input voltage 2 LOW             | V <sub>I2L</sub>  | V <sub>SS</sub>     |         | 0.1 V <sub>DD</sub> | ٧    | KEY/CPU, and SCK pins                                                                                                             |

| Low level input current<br>HIGH | 1114              |                     |         | 1.0                 | μА   | V <sub>DD</sub> = 5.5 V<br>Applies to HS, 67%/60%, LH/SH, and                                                                     |

| Low level input current LOW     | I <sub>IL</sub>   |                     |         | -1.0                | μΑ   | KEY/CPU pins                                                                                                                      |

| Input pull-up resistance        | R <sub>IU</sub>   |                     | 300     |                     | kΩ   | Applies to ROW1 ~ ROW4, COL1 ~                                                                                                    |

| Input pull-down resistance      | R <sub>ID</sub>   |                     | 30      |                     | kΩ   | COL4, SD, SCK, and DL pins                                                                                                        |

| Keytone sink current            | I <sub>KTL</sub>  | 250                 |         |                     | μА   | $V_{DD} = 2.0 \text{ V}, V_{O} = 0.2 \text{ V}$                                                                                   |

| Keytone source current          | I <sub>KTH</sub>  | -250                |         |                     | μА   | $V_{DD} = 2.0 \text{ V}, V_{O} = 1.8 \text{ V}$                                                                                   |

| Output sink current             | los               | 250                 |         |                     | μΑ   | V <sub>DD</sub> = 2.0 V, V <sub>O</sub> = 0.2 V<br>Applies to MODEOUT, MFMUTE,<br>DPMUTE, DP, MON, KEYDOWN,<br>and PDO ~ PD3 pins |

| Output leakage current          | l <sub>OLKG</sub> |                     |         | 1.0                 | μΑ   | V <sub>DD</sub> - 5.5 V<br>Applies to MODEOUT, MFMUTE,<br>DPMUTE, DP, MON, KEYDOWN,<br>and PDO ~ PD3 pins                         |

Note: For the test circuit, see Figure 2

# AC electrical characteristics 1 (unless otherwise noted, $\rm T_a = 25~^{\circ}C,~V_{DD} = 3.0~V)$

| Parameter                     | Symbol             | Min | Typical | Max  | Unit             | Conditions                                                                                                                                                                                                                                                                                           |

|-------------------------------|--------------------|-----|---------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               |                    |     | 1,6102, |      |                  | $t_{OS} = t_1 - t_2$ , where $t_1$ is the elapsed time between the application                                                                                                                                                                                                                       |

| Oscillation start time        | t <sub>OS</sub>    |     | 0.1     | 2.0  | ms               | of a LOW on the COL1 pin, and the application of a LOW on the COL1 pin, and the appearance of a LOW level at the COL2 pin. t <sub>2</sub> is the elapsed time between the triggering of the internal division counter by the OSCOUT pin waveform, and the appearance of a LOW level at the COL2 pin. |

| Key denounce time             | t <sub>DB</sub>    |     | 30      |      | ms               |                                                                                                                                                                                                                                                                                                      |

| Output pulse rate 1           | PR1                |     | 9.9     |      | pps              | MODEIN = Z (Open)                                                                                                                                                                                                                                                                                    |

| Output pulse rate 2           | PR2                |     | 19.9    |      | pps              | MODEIN = HIGH                                                                                                                                                                                                                                                                                        |

| Pulse break ratio 1           | BR1                |     | 66.7    |      | %                | 67%/60% = HIGH                                                                                                                                                                                                                                                                                       |

| Pulse break ratio 2           | BR2                |     | 60      |      | %                | 67%/60% = LOW                                                                                                                                                                                                                                                                                        |

| Inter-digital pause 1<br>HIGH | t <sub>IDP1H</sub> |     | 838     |      | ms               | MODEIN = Z (10 pps)<br>67%/.60% = HIGH                                                                                                                                                                                                                                                               |

| Inter-digital pause 1<br>LOW  | t <sub>IDP1L</sub> |     | 845     |      | ms               | MODEIN = Z (10 pps)<br>67%/.60% = LOW                                                                                                                                                                                                                                                                |

| Inter-digital pause 2<br>HIGH | t <sub>IDP2H</sub> |     | 469     |      | ms               | MODEIN = Z (20 pps)<br>67%/.60% = HIGH                                                                                                                                                                                                                                                               |

| Inter-digital pause 2<br>LOW  | t <sub>IDP2L</sub> |     | 473     |      | ms               | MODEIN = Z (20 pps)<br>67%/.60% = LOW                                                                                                                                                                                                                                                                |

| Tone output time              | t <sub>MF</sub>    |     | 101     |      | ms               | Dial tone is output for as long as the key is held down (when KEY/CPU is HIGH), or DL is                                                                                                                                                                                                             |

| Tone inter-digital pause      | t <sub>IDPM</sub>  |     | 101     |      | ms               | being input (when KEY/CPU is LOW).<br>Minimum hold time for both tone output and an<br>inter-digital pause is 101 ms. When redialing,<br>tone output and interdigit pause are 101 ms.                                                                                                                |

| Tone output cycle variation   | ΙΔfΙ               |     |         | 0.15 | %                |                                                                                                                                                                                                                                                                                                      |

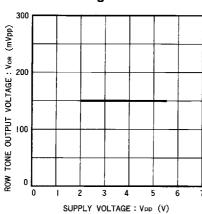

| Tone output voltage, row      | V <sub>OR</sub>    | 125 | 150     | 180  | mV <sub>PP</sub> |                                                                                                                                                                                                                                                                                                      |

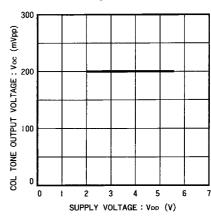

| Column tone output voltage    | v <sub>oc</sub>    | 166 | 200     | 240  | mV <sub>PP</sub> |                                                                                                                                                                                                                                                                                                      |

| High band pre-emphasis        | P <sub>EHB</sub>   | 1.8 | 2.5     | 3.3  | dB               |                                                                                                                                                                                                                                                                                                      |

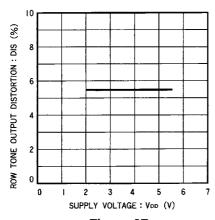

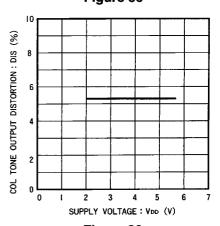

| Tone output distortion        | DIS                |     | 5.0     | 10.0 | %                | 400 Hz ~ 30 kHz, BPF                                                                                                                                                                                                                                                                                 |

Note: For the test circuit, see Figure 3

# AC electrical characteristics 2 (unless otherwise noted, $\rm T_a = 25~^{\circ}C,~V_{DD} = 3.0~V)$

| Parameter                 | Symbol             | Min | Typical | Max | Unit | Conditions                                                                                      |

|---------------------------|--------------------|-----|---------|-----|------|-------------------------------------------------------------------------------------------------|

| Pause time                | t <sub>PA</sub>    |     | 3.6     |     | s    |                                                                                                 |

| Hooking time              | t <sub>HK1</sub>   |     | 708     |     | ms   | LH/SH = HIGH                                                                                    |

| Hooking time              | t <sub>HK2</sub>   |     | 85      |     | ms   | LH/SH =LOW                                                                                      |

| Hooking pause time        | t <sub>HKPA1</sub> |     | 1.0     |     | s    | LH/SH = HIGH                                                                                    |

| Hooking pause time<br>2   | t <sub>HKPA2</sub> |     | 406     |     | ms   | LH/SH = LOW                                                                                     |

| Mute overlap time         | t <sub>MO</sub>    |     | 101     |     | ms   |                                                                                                 |

| On-hook time              | t <sub>OH</sub>    | 1   |         |     | ms   | When going on hook, the HS pin must be held HIGH for at least 1 ms.                             |

| Keytone frequency         | f <sub>KT</sub>    |     | 1193    |     | Hz   |                                                                                                 |

| Keytone output time       | t <sub>KT</sub>    |     | 34      |     | ms   |                                                                                                 |

| Pre-pause time, 1H        | t <sub>PP1H</sub>  |     | 334     |     | ms   | MODEIN = Z (10 pps)<br>67%/60% = HIGH                                                           |

| Pre-pause time, 1L        | t <sub>PP1L</sub>  |     | 340     |     | ms   | MODEIN = Z (10 pps)<br>67%/60% = LOW                                                            |

| Pre-pause time, 2H        | t <sub>PP2H</sub>  |     | 168     |     | ms   | MODEIN = HIGH(20 pps)<br>67%/60% = HIGH                                                         |

| Pre-pause time, 2L        | t <sub>PP2L</sub>  |     | 171     |     | ms   | MODEIN = HIGH (20 pps)<br>67%/60% = LOW                                                         |

| Tone pre-pause time       | t <sub>PPM</sub>   |     | 7       |     | ms   | MODEIN = LOW (Tone)                                                                             |

| SD setup time             | t <sub>SDS</sub>   | 100 |         |     | ns   | KEY/CPU = LOW These values apply for a CMOS                                                     |

| SD hold time              | t <sub>SDH</sub>   | 100 |         |     | ns   | interface. Note that these values become very large when an NMOS                                |

| Serial clock cycle period | t <sub>CS</sub>    | 500 |         |     | ns   | open drain interface is used. (See<br>"Precautions for use" following.)                         |

| DL setup time             | t <sub>DLS</sub>   | 500 |         |     | ns   | KEY/CPU = LOW                                                                                   |

| DL hold time              | t <sub>DLH</sub>   | 15  |         |     | ms   | KEY/CPU = LOW When using DL, to latch data into the IC, DL must be held LOW for at least 15 ms. |

| Transmit start time       | t <sub>SO</sub>    | 30  |         | 34  | ms   | Not including oscillator start time                                                             |

Note: For the test circuit, see Figure 3

#### **Test circuits** Figure 2 DC test circuit

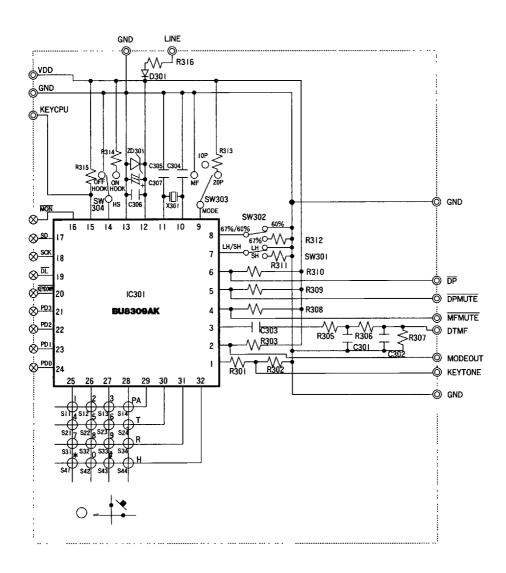

Figure 3 AC test circuit

7828999 0010019 3T5 **=**

# Operation

The following section describes the operation of the integrated circuit and its inputs.

Table 5 Keypad key functions

| Key            | Function                                                                                                                                                                                                                                        |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0~9            | Dial signals are sent when one of these keys is pressed.                                                                                                                                                                                        |

| * or #         | In tone mode, when these keys are pressed, DTMF signals are transmitted. In pulse mode, if the # key is the first key pressed after going off hook, the redial operation is executed. The * key switches the unit from pulse mode to tone mode. |

| P <sub>A</sub> | When this key is pressed, a 3.6-s pause is generated. Also serves as a "break pause" key when redialing.                                                                                                                                        |

| Т              | Used to switch from pulse to tone mode. Automatically inserts a 3.6-s pause. Also serves as a "break pause" key when redialing.                                                                                                                 |

| R              | Used in redial and dial inhibit operation. Also serves as a "break pause" key when redialing.                                                                                                                                                   |

| Н              | Pressed to simulate an on-hook operation.                                                                                                                                                                                                       |

Figure 4 Keypad arrangements

|      | COL1  | COL2   | COL3 |      | COL1 | COL2 | COL3 | COL4 |

|------|-------|--------|------|------|------|------|------|------|

| ROW1 | 1     | 2      | 3    | ROW1 | 1    | 2    | 3    | Pa   |

| ROW2 | 4     | 5      | 6    | ROW2 | 4    | 5    | 6    | Т    |

| ROW3 | 7     | 8      | 9    | ROW3 | 7    | 8    | 9    | R    |

| ROW4 | *     | 0      | #    | ROW4 | *    | 0    | #    | н    |

| 3×4  | (2 of | 7) key | pad  | I    | 4    | ×4 k | eypa | d    |

Table 6 DTMF frequencies

| Stand            | ard  | BU8309AS or BU8309AK | (excluding drift of resonator) |

|------------------|------|----------------------|--------------------------------|

| frequencies (Hz) |      | Frequency (Hz)       | Frequency variation (%)        |

|                  | 697  | 696.41               | -0.08                          |

|                  | 770  | 769.79               | -0.03                          |

| Low              | 852  | 852.27               | +0.03                          |

|                  | 941  | 941.99               | +0.10                          |

|                  | 1209 | 1209.31              | +0.03                          |

| High             | 1336 | 1335.65              | -0.03                          |

|                  | 1477 | 1479.15              | +0.15                          |

Table 7

| Pa | rallel d<br>Serial d | ata out<br>ata inp | put<br>ut | Corresponding k     | ey data or function        |

|----|----------------------|--------------------|-----------|---------------------|----------------------------|

| D3 | D2 D1 D0             |                    | D0        | Off hook (HS = LOW) | On hook (HS = HIGH)        |

| 0  | 0                    | 0                  | 0         | Н                   |                            |

| 0  | 0                    | 0                  | 1         | 1                   |                            |

| 0  | 0                    | 1                  | 0         | 2                   |                            |

| 0  | 0                    | 1                  | 1         | 3                   |                            |

| 0  | 1                    | 0                  | 0         | 4                   |                            |

| 0  | 1                    | 0                  | 1         | 5                   |                            |

| 0  | 1                    | 1                  | 0         | 6                   |                            |

| 0  | 1                    | 1                  | 1         | 7                   |                            |

| 1  | 0                    | 0                  | 0         | 8                   |                            |

| 1  | 0                    | 0                  | 1         | 9                   |                            |

| 1  | 0                    | 1                  | 0         | 0                   |                            |

| 1  | 0                    | 1                  | 1         | *                   | -                          |

| 1  | 1                    | 0                  | 0         | #                   |                            |

| 1  | 1                    | 0                  | 1         | T                   |                            |

| 1  | 1                    | 1                  | 0         | P <sub>A</sub>      |                            |

| 1  | 1                    | 1                  | 1         | R                   | Redial buffer memory erase |

## Key operation

In the following description, the IC behavior is described when certain key operations are carried out. In all cases, the  $(\uparrow)$  indicates that an off-hook signal is generated. A  $(\downarrow)$  symbol indicates that an on-hook signal is generated. Digit keys are represented by the symbol  $D_n$ , where n indicates the sequence number of the digit not the actual digit pressed. All special keys such as the  $P_A$  key are shown as, for instance,  $P_A$ .

**Normal dialing**  $(\uparrow)$  D<sub>1</sub>...D<sub>n</sub> When the IC is in the off-hook state, the dial data from the key input is written into the redial memory and the proper dial signals (tone or pulse, depending on the operating mode) are transmitted. There is no upper limit on the number of digits that can be dialed. Key inputs can be entered during dial output. The redial buffer is cleared if the R key is pressed twice at any time after the last dial signal is transmitted, but before the IC is returned to the on-hook state.

**Access pause** (↑)  $D_1P_A$ ,  $D_2...D_n$  When the  $P_A$  key is pressed with the IC in an off-hook state, a 3.6 pause is inserted into the transmission signal. Pause times can be stacked by simply re-pressing the  $P_A$  key. During a pause, dialing inputs are allowed as they are during dial signal transmission. If a pause is included in a redial, the pause can be removed during transmission by pressing the  $P_A$ , T, or R key. This operation will stop a single or a stacked pause.

**Redial** (↑) R (tone mode) or (↑) # (MODEIN = HIGH or Z) (pulse mode) Redial is only accepted if the redial key is pressed immediately after going off hook. Pressing R (tone mode) or # (pulse mode) after going off hook causes the last number dialed to be redialed. Key inputs are not accepted when a redial signal is being output. After the redial digits have been transmitted, any number of valid key inputs are accepted and transmitted.

The redial memory holds up to 32 digits. Redial is inhibited if more than 32 digits (pulse mode) or 31 digits (tone mode) are dialed. In tone mode, one digit of dial memory is used to store the current mode. Hence only 31 digits are available for redial in tone mode.

The following keys can form part of the redial string:

- Pulse mode: digits 0 through 9, P<sub>A</sub> and T

- Tone mode: digits 0 through 9, P<sub>A</sub>, \*, and #

The redial buffer is cleared if the R key is pressed twice at any time after the last dial signal is transmitted, but before the IC is returned to the on-hook state.

**Mode switching (Mixed mode dialing)** (↑)  $D_1...D_iT$  or \*,  $D_{i+1}...Dn$  (MODEIN = HIGH or Z). The IC can only be switched once from pulse mode to tone mode when in an off hook state. Setting the MODEIN pin to HIGH or Z (pulse mode) and pressing the T (or \*) key writes the data required to switch to tone mode into memory. When the IC is in pulse mode, and a T or \* key is pressed while the dial signal is being sent, a 3.6-s pause is inserted after all digits up to that key have been transmitted and all subsequent dial signals are transmitted as tones. In this case the \* signal is sent out as a DTMF signal. If a T or \* key is entered after the dial signal has been transmitted (after  $\overline{DPMUTE}$  goes from the LOW to the Z state) no pause is inserted.

Since the data for switching to tone mode is stored in the redial memory, mixed mode can also be used when redialing. When the IC redials, it always starts the redial in the mode that it was in when the numbers were initially dialed, no matter what the state of the MODEIN pin.

**Hooking** (↑) H. This sequence executes an on-hook sequence. A hook pause is automatically entered after the end of an on-hook sequence. If a dial signal is being transmitted when the H is pressed, the dial sequence is immediately interrupted and the on-hook sequence starts. Hook time is 708 ms.

When the H key is pressed, the following operations are performed in the IC:

- Input mode is reset, and the circuit goes to the pulse mode wait state (waiting for key inputs). If the MODEIN pin is LOW, the mode is changed to Tone.

- The write pointer is reset and the redial buffer is enabled.

**Note:** The hooking input is not written into memory. The operator can press any other keys after the H key is pressed. When the hooking operation is in progress, the only key input that is not accepted is the H key.

Table 8 Operating example:  $4 \times 4$  keypad

| Operation                                   | Key sequence                                   | Dial output                                                                    | Redial memory contents                         |

|---------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------|

| Normal dialing 1<br>MODEIN = HIGH           | (1) 1, 2, 3, 4                                 | Pulse 1, 2, 3, 4 at 20 pps                                                     | 1, 2, 3, 4                                     |

| Normal dialing 2<br> MODEIN = Z             | (1) 1, 2, 3, 4                                 | Pulse 1, 2, 3, 4 at 10 pps                                                     | 1, 2, 3, 4                                     |

| Normal dialing 3<br>MODEIN = LOW            | (1) 1, 2, 3, 4                                 | DTMF 1, 2, 3, 4                                                                | T, 1, 2, 3, 4                                  |

| Access pause                                | ( <sup>1</sup> ) 0, P <sub>A</sub> , 1, 2, 3   | 0, (pause 3.6 s), 1, 2, 3                                                      | 0, P <sub>A</sub> , 1, 2, 3                    |

|                                             | (↑) 0, P <sub>A</sub> , 1, 2, 3 (↓)<br>or      | 0, (pause 3.6 s), 1, 2, 3                                                      | 0, P <sub>A</sub> , 1, 2, 3                    |

| Break in progress pause                     | (↑)R●P <sub>A</sub>                            | 0, (pause ≤ 3.6 s), 1, 2, 3<br>(Press P <sub>A</sub> for break in<br>progress) | 0, P <sub>A</sub> , 1, 2, 3                    |

| Redial 1                                    | (↑) 1, 2, 3, 4 (↓)<br>(↑)R                     | 1, 2, 3, 4<br>1, 2, 3, 4                                                       | 1, 2, 3, 4<br>1, 2, 3, 4                       |

| Redial 2                                    | 1, 2, 332, 33<br>(↑) 1, 2, 3 2, 3, (↓)<br>(↑)R | 1, 2, 3, 2, 3<br>No output                                                     | Memory cleared<br>Memory cleared               |

| Inhibit redial 1                            | (↑) 1, 2, 3, 4 ○ R, R (↓)<br>(↑)R              | 1, 2, 3, 4<br>No output                                                        | Memory cleared<br>Memory cleared               |

| Inhibit redial 2                            | (↑) 1, 2, 3, 4 (↓)<br>(↑)RO R, R (↓)<br>(↑)R   | 1, 2, 3, 4<br>1, 2, 3, 4<br>No output                                          | 1, 2, 3, 4<br>Memory cleared<br>Memory cleared |

| Switch modes using T key MODEIN = HIGH or Z | (↑) 1, 2, T, 3, 4 (↓)                          | 1, 2, (pause 3.6 s), 3, 4<br>Pulse DTMF                                        | 1, 2, T, 3, 4                                  |

|                                             | (↑)R                                           | 1, 2, (pause 3.6 s), 3, 4<br>Pulse DTMF                                        | 1, 2, T, 3, 4                                  |

| Switch modes using * key MODEIN = HIGH or Z | (↑) 1, 2, *, #, *(↓)                           | 1, 2, (pause 3.6 s),#, *<br>Pulse DTMF                                         | 1, 2, T, #, *                                  |

| On-hook                                     | (1)H                                           | Hook sequence                                                                  |                                                |

Follow-on key pressed during pause

O Follow-on key pressed after previous input processed

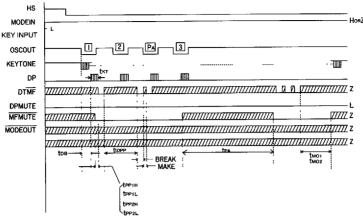

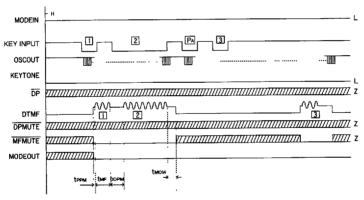

Figure 5 Pulse dial timing (KEY/CPU pin HIGH)

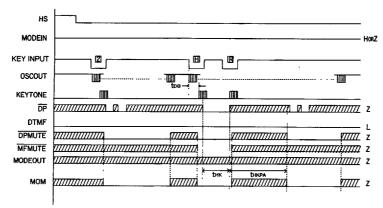

Figure 6 Tone dial timing (KEY/CPU pin HIGH)

Figure 7 Pulse and tone mixed dial timing (KEY/CPU pin HIGH)

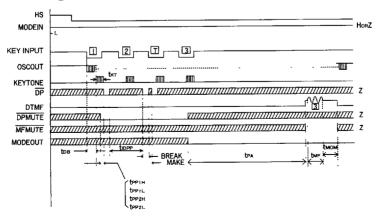

Figure 8 Hooking and redial timing (KEY/CPU pin HIGH)

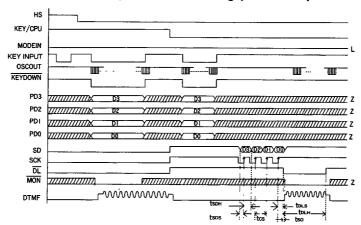

Figure 9 CPU interface timing

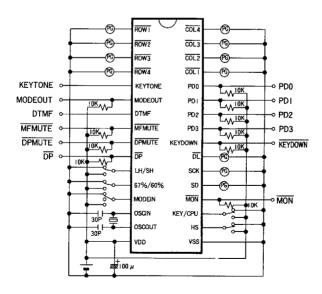

# Selecting external circuit components

The following section specifies the external components that are required to ensure that the IC functions as intended.

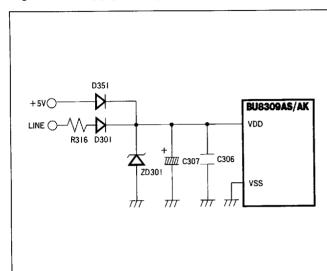

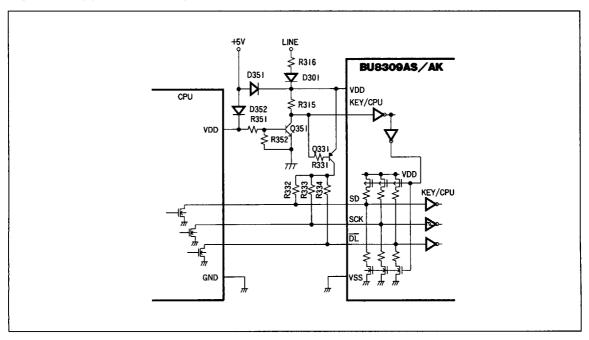

Figure 10 Supply voltage external circuit

C306, C307: V<sub>DD</sub> bypass capacitors.

**ZD301**: Prevents the supply voltage from rising above 5.5 V. (Use a 5.1-V zener.)

**D301, D351:** Reverse current blocking diodes. Connect the +5-V terminal of this circuit to the CPU 5-volt supply (Spec. 1SS133).

R316: This resistor applies supply voltage from the telephone circuit to the dialer. It also alters the ac impedance of the telephone. The LINE terminal of this circuit should be connected to the VL pin of the speech network IC. When selecting the value of R316, consider not only the voltage that needs to be applied to the dialer, but also the effect of the resistor on the ac impedance of the telephone.

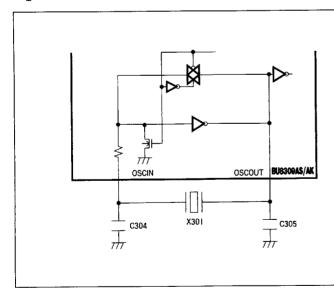

Figure 11 Oscillator circuit

**X301**: Use a 3.579545 MHz piezoelectric or ceramic resonator. For recommended ceramic resonators, see the table "Recommended operating conditions" on page 100.

C304, C305: These are loading capacitors required if a ceramic resonator is used. Use 33 pF CH-type capacitors. If a 3-pin resonator with built-in capacitors is used, C304 and C305 are not required.

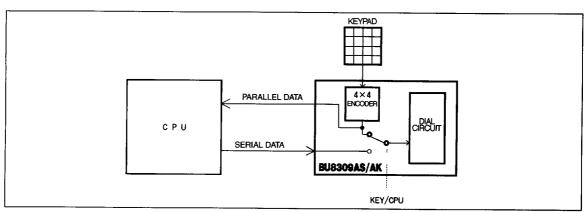

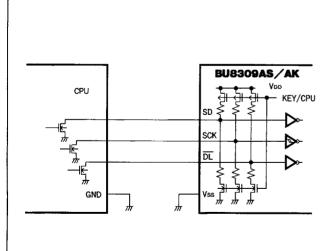

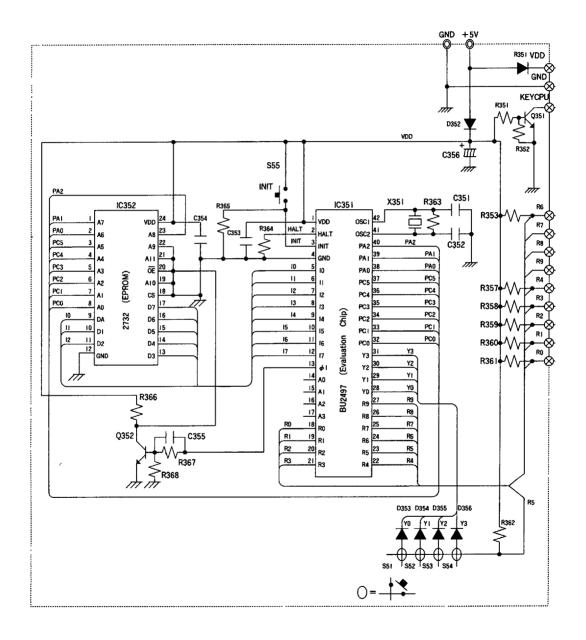

**CPU** interface

**Keypad input mode** When the KEY/CPU pin is HIGH, the IC is in the keypad input mode. Data entered from a keypad connected to the BU8309AS/AK is converted into 4-bit key codes by a  $4 \times 4$  key encoder, and the codes are transferred to the dial circuit. The key codes perform operations as defined by the dialer, and are also output to the CPU as parallel data.

CPU input mode When the KEY/CPU pin is LOW, the IC is in the CPU input mode. Data entered at a keypad connected to the BU8309AS/AK is converted into 4-bit key codes by a  $4\times4$  key encoder, and output to the CPU as parallel data. In this mode, the dial circuit is operated by serial data from the CPU. This allows data entered from the keypad to be processed against special function data as defined by the CPU (for instance, time stamps or secret code registration). The data sent to the dial circuit can also be defined as desired, and sent under CPU program control. Having a KEY/CPU pin to switch the CPU in and out of the dial signal path makes it easy to implement a variety of useful telephone functions, such as the capability to dial out during a power failure.

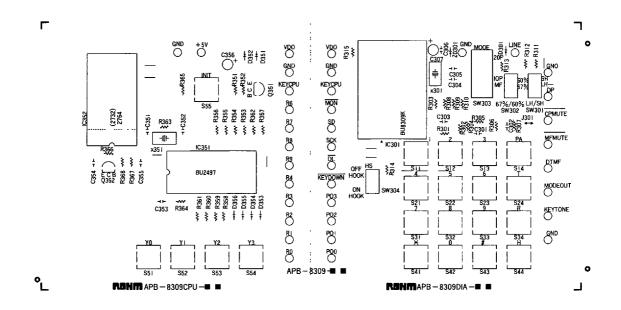

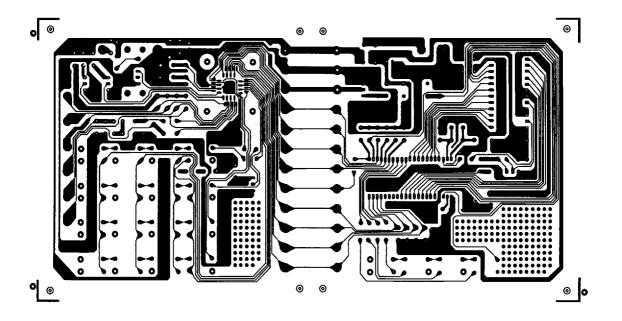

Figure 12 CPU interface

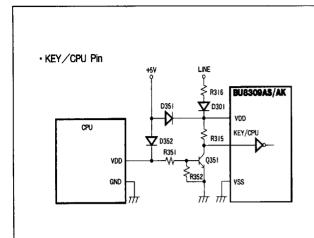

Figure 13 KEY/CPU pin external circuit

#### KEY/CPU pin input logic levels

Normal operation (5 V supplied): Q351 on; KEY/CPU pin LOW.

Power failure (no 5-V supply): Q351 off; KEY/CPU pin HIGH.

The circuit is configured so that when a power failure occurs, and the CPU is out of operation, the circuit will switch the IC from CPU-input to keypad-input mode.

**D352:** Diode to apply power from the +5-V supply to the CPU. The diode keeps the  $V_{DD}$  voltage applied to the CPU about the same as that applied to the BU8309AS/AK. (Specification 1SS133)

R315: KEY/CPU pin pull-up resistor.

R351, R352: Base resistors for Q351. The voltage at which Q351 will detect a drop in the 5-V supply is determined by the ratio of these resistors.

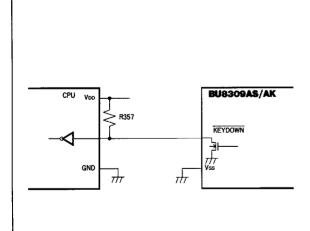

Figure 14 KEYDOWN pin external circuit

When the HS pin is LOW (off hook), the KEYDOWN pin outputs a LOW when any valid key input is entered at a keypad connected to the BU8309AS/AK. This is true regardless of the state of the KEY/CPU pin. The KEYDOWN pin is usually connected to an interrupt input port on the CPU.