# QLUM3332-PT280C Device Datasheet

## • • • • • Utopia Level 3 Master/Master Bridge

## 1.0 Utopia Level 3 (L3) Bridge Features

- Implements two Utopia L3 Masters providing a solution to bridge Utopia Slave devices

- Compliant with ATM-Forum af-phy-0136.000 (Utopia L3)

- Meets 90 MHz performance offering more than 2.5Gbps cell rate transfers

- Single chip solution for improved system integration

- Support cell level transfer mode

- Cell and clock rate decoupling with on chip FIFOs

- Up to 1.5 KByte of on chip FIFO per data direction

- Integrated management interface and built-in errored cell discard

- ATM Cell size programmable via external pins from 16 to 128 bytes

- Optional Utopia parity generation/checking enable/disable via external pin

- Built in JTAG port (IEEE1149 compliant)

- Simulation model available for system level verification (Contact Quicklogic for details)

- Solution also available as flexible Soft-IP core, delivered with a full device modelization and verification testbenches

## 2.0 Utopia Overview

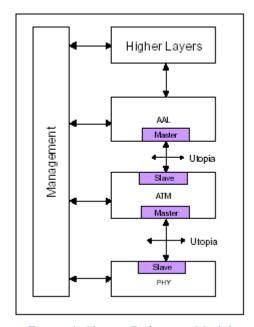

The Utopia (Universal Test & Operations PHY Interface for ATM) interface is defined by the ATM Forum to provide a standard interface between ATM devices and ATM PHY or SAR (segmentation and Re-assembly) devices.

Figure 1: Utopia Reference Model

The Utopia Standard defines a full duplex bus interface with a Master/Slave paradigm. The Slave interface responds to the requests from the Master. The Master performs PHY arbitration and initiates data transfers to and from the Slave device.

The ATM forum has standardized the Utopia Levels 1 (L1) to 3 (L3). Each level extends the maximum supported interface speed from OC3, 155Mbps (L1) over OC12, 622Mbps (L2) to 3.2Gbit/s (L3).

The following Table 1 gives an overview of the main differences in these three levels.

| Utopia Level | Interface Width | Max. Interface Speed | Maximum Throughput            |  |  |

|--------------|-----------------|----------------------|-------------------------------|--|--|

| 1            | 8-bit           | 25 MHz               | 200 Mbps (typ. OC3 155 Mbps)  |  |  |

| 2            | 8-bit, 16-bit   | 50 MHz               | 800 Mbps (typ. OC12 622 Mbps) |  |  |

| 3            | 8-bit, 32-bit   | 104 MHz              | 3.2 Gbps (typ. OC48 2.5 Gbps) |  |  |

Table 1: Utopia Level Differences

Utopia Level 1 implements an 8-bit interface running at up to 25MHz. Level 2 adds a 16 Bit interface and increases the speed to 50MHz. Level 3 extends the interface further by a 32 Bit word-size and speeds up to 104MHz providing rates up to 3.2 Gbit/s over the interface.

In addition to the differences in throughput, Utopia Level 2 uses a shared bus offering to physically share a single interface bus between one master and up to 31 slave devices (Multi-PHY or MPHY operation). This allows the implementation of aggregation units that multiplex several slave devices to a single Master device. The Level 2 and Level 3 are point-to-point only, whereas Level 1 has no notion of multiple slaves. Level 3 still has the notion of multiple slaves, but they must be implemented in a single physical device connected to the Utopia Interface.

## 3.0 Utopia Master/Master Bridge Application

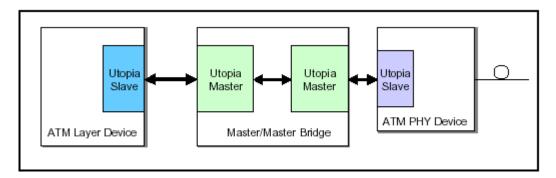

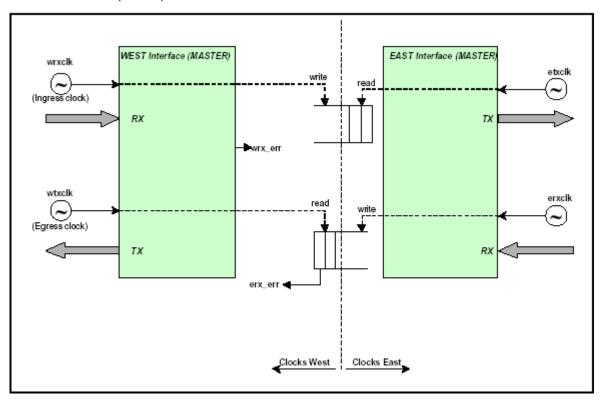

As it is not possible to connect two Slave devices together, the Master/Master Bridge provides the necessary interfaces to convey between two Slave devices as shown in Figure 2.

Figure 2: Utopia Master Bridge

The Bridge automatically transfers data as soon as it becomes available from one side to the other. Internal asynchronous FIFOs enable independent clock domains for each interface.

# 4.0 Application

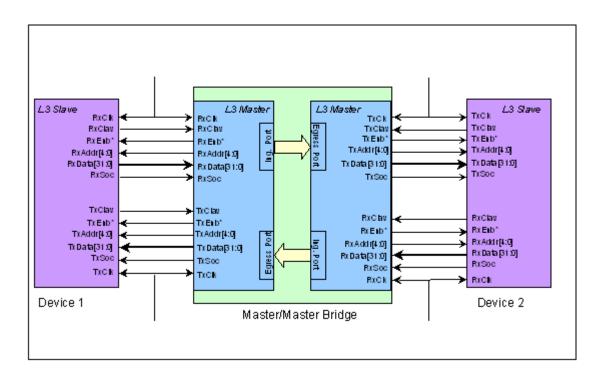

Figure 3: Master/Master Bridge connecting two Slave Devices

Data flows from the Bridge's RX Ports to the corresponding TX Ports on the other side of the bridge.

### 5.0 Core Pinout

Bridge Core implements all the required Utopia signals and provides all the Utopia optional signals (Indicated by an 'O' in the following tables).

In addition to the Utopia Interface signals, error indication signals are available for error monitoring or statistics. An error indication always shows that a cell has been discarded by the bridge. Possible errors are parity or cell-length errors on the receive interface of the corresponding Utopia Interfaces.

All Utopia interfaces work in the same transfer mode (cell level).

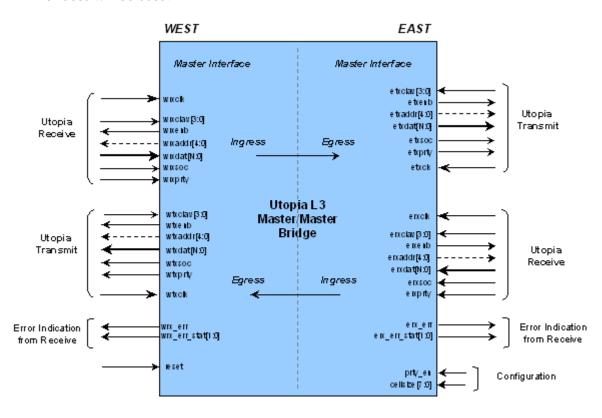

To identify the sides of the bridge, the notion "WEST" and "EAST" for the corresponding interfaces will be used.

Figure 4: Utopia Level 3 Master/Master Bridge Top Entity

## **5.1 Signal Descriptions**

Table 2: Global Signal

| Pin   | Mode | Description            |  |  |

|-------|------|------------------------|--|--|

| reset | In   | Active high chip reset |  |  |

Table 3: Device Management Interface

| Pin               | Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wrx_err           | Out  | Receive error indication on west receive interface. When driven high, indicates that an errored cell (Wrong parity or wrong length) was received from the device connected to the west interface and is discarded.                                                                                                                                                                                                                                |

| wrx_err_stat(1:0) | Out  | Receive error status information for west receive interface. When wrx_err is driven, indicates the error status of the discarded cell:  wrx_err_stat(0): When set to '1' indicates that a cell is discarded because of a parity error.  wrx_err_stat(1): When set to '1' indicates that a cell is discarded because it has a wrong length (Consecutive assertion of ut_tx_soc on the Utopia interface within less than a complete cell time).     |

| erx_err           | Out  | Receive error indication on east receive interface(s). When driven high, indicates that an errored cell (Wrong parity or wrong length) was received from the device connected to the east interface side.                                                                                                                                                                                                                                         |

| erx_err_stat(1:0) | Out  | Receive error status information for east receive interface. When erx_err is driven, indicates the error status of the discarded cell:  • erx_err_stat(0): When set to '1' indicates that a cell is discarded because of a parity error.  • erx_err_stat(1): When set to '1' indicates that a cell is discarded because it has a wrong length (Consecutive assertion of ut_tx_soc on the Utopia interface within less than a complete cell time). |

**NOTE:** wrx\_.. signals are sampled with west receive clock (wrxclk). erx\_.. signals are sampled with west transmit clock (wtxclk).

Table 4: West Utopia Master Transmit Interface

| Pin              | Mode | Description                                                                                                                                                                                                                                           |  |  |  |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| wtxclk           | ln   | 90MHz transmit byte clock. The Core samples all Utopia Transmit signals on txclk rising edge.                                                                                                                                                         |  |  |  |

| wtxdata[31:0]    | Out  | Transmit data bus.                                                                                                                                                                                                                                    |  |  |  |

| wtxprty          | Out  | Transmit data bus parity. Standard odd or non-standard even parity can be optionally checked by the connected Slave.  When the parity check is disabled during the Core configuration, or not used in the design, the pin txprty should be left open. |  |  |  |

| wtxsoc           | Out  | Transmit start of cell. Asserted by the Master to indicate that the current word is the first word of a cell.                                                                                                                                         |  |  |  |

| wtxenb           | Out  | Active low transmit data transfer enable.                                                                                                                                                                                                             |  |  |  |

| wtxclav[0]       | ln   | Cell buffer available. Asserted in octet level transfers to indicate to the Master that the FIFO is almost full (Active low) or, in cell level transfers, to indicate to the Master that the PHY port FIFO has space to accept one cell.              |  |  |  |

| wtxclav[3:1] (0) | ln   | Extra FIFO Full / Cell buffer available. In MPHY mode and when direct status indication is selected during the Core configuration, one txclav signal is implemented per PHY port. The maximum number of clav signals is limited to four.              |  |  |  |

| wtxaddr[4:0] Out |      | Utopia transmit address. When the Core operates in MPHY mode, address bus used during polling and slave port selection. Bit 4 is the MSB. txaddr(4:0) becomes optional (And should be left open) when the Core does not operate in MPHY mode.         |  |  |  |

**NOTE:** (O) indicates optional signals.

Table 5: West Utopia Master Receive Interface

| Pin                                                            | Mode | Description                                                                                                                                                                                                                                           |  |  |  |

|----------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| wrxclk                                                         | ln   | 90MHz receive byte clock. The Core samples all Utopia Receive signals on rxclk rising edge.                                                                                                                                                           |  |  |  |

| wrxdata[31:0]                                                  | In   | Receive data bus.                                                                                                                                                                                                                                     |  |  |  |

| wrxprty(0)                                                     | ln   | Receive data bus parity. Standard odd or non standard even parity can be optionally generated by the Utopia Slave Core.  When the parity generation is disabled during the Core configuration, the pin rxprty can be let unconnected.                 |  |  |  |

| Wrxsoc                                                         | In   | Receive start of cell. Asserted to indicate that the current word is the first word of a cell.                                                                                                                                                        |  |  |  |

| wrxenb                                                         | Out  | Active low transmit data transfer enable.                                                                                                                                                                                                             |  |  |  |

| wrxclav[0]                                                     | In   | Cell buffer available. Asserted in octet level transfers to indicate to the Master that the FIFO is almost empty (Active low) or, in cell level transfers, to indicate to the Master that the PHY port FIFO has space one cell available in the FIFO. |  |  |  |

| wrxclav[3:1] (0)                                               | ln   | Extra FIFO Full / Cell buffer available. In MPHY mode and when direct status indication is selected, one rxclav signal is implemented per PHY port. The maximum number of clav signals is limited to four.                                            |  |  |  |

| wryaddn(4:0) Out used during polling and slave port selection. |      | Utopia receive address. When the Core operates in MPHY mode, address bus used during polling and slave port selection. Bit 4 is the MSB. txaddr(4:0) becomes optional (And should be left open) when the Core does not operate in MPHY mode.          |  |  |  |

Table 6: East Utopia Master Transmit Interface

| Pin              | Mode | Description                                                                                                                                                                                                                                           |  |  |  |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| etxclk           | ln   | 90MHz transmit byte clock. The Core samples all Utopia Transmit signals on txclk rising edge.                                                                                                                                                         |  |  |  |

| etxdata[31:0]    | Out  | Transmit data bus.                                                                                                                                                                                                                                    |  |  |  |

| etxprty          | Our  | Transmit data bus parity. Standard odd or non-standard even parity can be optionally checked by the connected Slave.  When the parity check is disabled during the Core configuration, or not used in the design, the pin txprty should be left open. |  |  |  |

| etxsoc           | Out  | Transmit start of cell. Asserted by the Master to indicate that the current word is the first word of a cell.                                                                                                                                         |  |  |  |

| etxenb           | Out  | Active low transmit data transfer enable.                                                                                                                                                                                                             |  |  |  |

| etxclav[0]       | ln   | Cell buffer available. Asserted in octet level transfers to indicate to the Master that the FIFO is almost full (Active low) or, in cell level transfers, to indicate to the Master that the PHY port FIFO has space to accept one cell.              |  |  |  |

| etxclav[3:1] (0) | ln   | Extra FIFO Full / Cell buffer available. In MPHY mode and when direct status indication is selected during the Core configuration, one txclav signal is implemented per PHY port. The maximum number of clav signals is limited to four.              |  |  |  |

| etxaddr[4:0]     | Out  | Utopia transmit address. When the Core operates in MPHY mode, address bus used during polling and slave port selection. Bit 4 is the MSB. txaddr(4:0) becomes optional (And should be left open) when the Core does not operate in MPHY mode.         |  |  |  |

Table 7: East Utopia Master Receive Interface

| Pin             | Mode | Description                                                                                                                                                                                                                                           |  |  |  |

|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| erxclk          | ln   | 90MHz receive byte clock. The Core samples all Utopia Receive signals on rxclk rising edge.                                                                                                                                                           |  |  |  |

| erxdata[31:0]   | In   | Receive data bus.                                                                                                                                                                                                                                     |  |  |  |

| erxprty (0)     | ln   | Receive data bus parity. Standard odd or non standard even parity can be optionally generated by the Utopia Slave Core.  When the parity generation is disabled during the Core configuration, the pin rxprty can be let unconnected.                 |  |  |  |

| erxsoc          | In   | Receive start of cell. Asserted to indicate that the current word is the first word of a cell.                                                                                                                                                        |  |  |  |

| erxenb          | Out  | Active low transmit data transfer enable.                                                                                                                                                                                                             |  |  |  |

| erxclav[0]      | In   | Cell buffer available. Asserted in octet level transfers to indicate to the Master that the FIFO is almost empty (Active low) or, in cell level transfers, to indicate to the Master that the PHY port FIFO has space one cell available in the FIFO. |  |  |  |

| rxclav[3:1] (0) | In   | Extra FIFO Full / Cell buffer available. In MPHY mode and when direct status indication is selected, one rxclav signal is implemented per PHY port. The maximum number of clav signals is limited to four.                                            |  |  |  |

| erxaddr(4:0)    | Out  | Utopia receive address. When the Core operates in MPHY mode, address bus used during polling and slave port selection. Bit 4 is the MSB. taddr(4:0) becomes optional (And should be left open) when the Core does not operate in MPHY mode.           |  |  |  |

Table 8: Device Configuration Pins

| Pin           | Mode | Description                                                                                                                                                                                                              |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| prty_en       | In   | Enable parity checking on the Utopia interface.  If disabled (tied to 0), the wrx_err_stat(0) signal can be ignored and left open and the rx parity input should be tied to 0. Also the tx parity pins can be left open. |

| cellsize[7:0] | In   | Define cellsize: sets the size in bytes of a cell. Binary value to be set usually by board wiring. The size must be a multiple of 4.                                                                                     |

The configuration pins are not intended for change during operation. They are usually board wired to configure the device for operation.

## 6.0 Global Signal Descriptions

The externally provided Utopia Transmit and Receive clocks are connected to global resources to provide low skew and fast chip level distribution. In both data directions, the two corresponding Utopia Interfaces are decoupled by asynchronous FIFOs.

Therefore each interface runs completely independently each at its own tx and rx clocks which typically are 104 MHz.

The Error indications of the two receive interfaces are always sampled within the west clock domains. The errors of the east rx interface is available on the erx\_err signal, which is handled using the west clock domain (wtxclk). The west rx error is directly derived from the west rx block (wrxclk).

Figure 5: Master/Master Bridge Clock Distribution

## 7.0 Functional Description - Utopia Interface

The Utopia Bridge operates in single PHY mode. Therefore no address bus and only a single status pin (clav[0]) per direction is used on the interfaces.

### 7.1 Utopia Interface Single PHY Transmit Interface

The Transmit interface is controlled by the ATM layer.

The transmit interface has data flowing in the same direction as the ATM enable ut\_txenb. The ATM transmit block generates all output signals on the rising edge of the ut\_txclk.

Transmit data is transferred from the ATM layer to PHY layer via the following procedure. The Core indicates it can accept data using the ut\_txclav signal, then the ATM layer drives data onto ut\_txdat and asserts ut\_txenb.

When a cell transfer is initiated, the Master or the Slave cannot pause the transfer by any means.

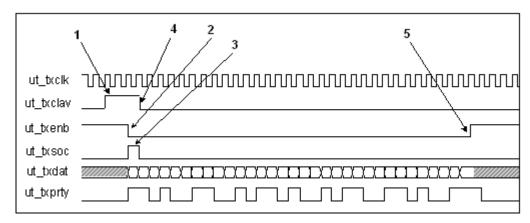

#### 7.1.1 Single Cell Transfer

10

The Slave asserts ut\_txclav 1 when it is capable of accepting the transfer of a whole cell. The Core asserts ut\_txenb (Low) to indicates that it drives valid data to the Slave 2. Together with the first word of a cell, the Core device asserts ut\_txsoc for one clock cycle 3.

To ensure that the ATM Layer (Core) does not cause transmit overrun, the Slave de-asserts ut\_txclav when ut\_txsoc is de-asserted by the Core 4.

To complete the cell transfer, the Core de-asserts the Utopia enable signal ut\_txenb 5.

Figure 6: Single Cell Transfer - Cell Level Transfer

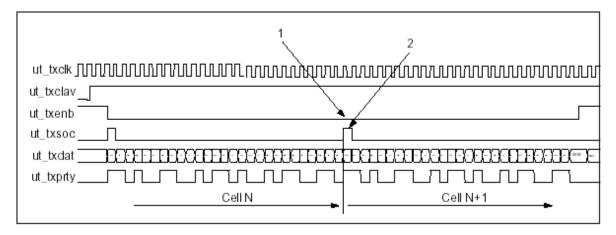

#### 7.1.2 Back to Back Cells Transfer

When, during a cell transfer, the Slave is able to receive a subsequent cell, the Master can keep ut\_txenb asserted between two cells 1 and asserts ut\_txsoc, to start a new cell transfer, immediately after the last word of the previous cell 2.

Figure 7: Back to Back Cell Transfer

### 7.2 Utopia Interface Single PHY Receive Interface

The Receive interface is controlled by the Master interface. The receive interface has data flowing in the opposite direction to the Master's enable ut\_rxenb.

Receive data is transferred from the Slave to the Master via the following procedure. The Slave indicates it has valid data, then the Master asserts ut\_rxenb to read this data from the Slave. The Master indicates valid data (thereby controlling the data flow) via the ut\_rxclav signal.

When a cell transfer is initiated, the transfer cannot be paused by the Master or the Slave.

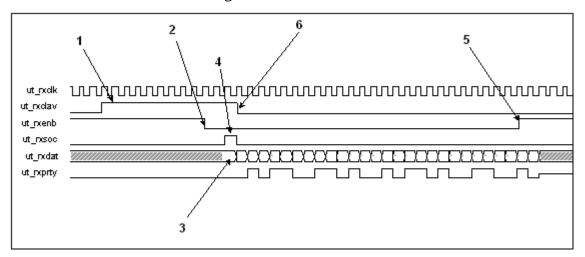

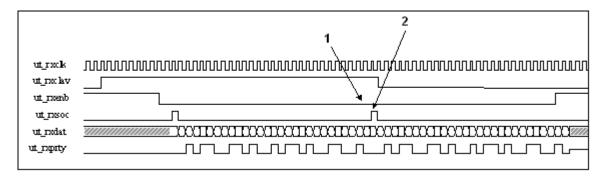

#### 7.2.1 Cell Level Transfer - Single Cell

The Slave asserts ut\_rxclav when it is ready to send a complete cell to the Master 1. The Master interface asserts ut\_rxenb to start the cell transfer 2. The Slave samples ut\_rxenb and start driving data on the following clock edge 3. The Slave asserts ut\_rxsoc together with the cell first word to indicate the start of a cell 4.

The Master drives ut\_txenb high two clock cycles before the expected end of the current cell if the Slave has no more cell to transfer 5. The Slave de-asserts ut\_rxclav to indicate that no new cell is available 6 together with the start of cell indication.

Figure 8: Single Cell Transfer

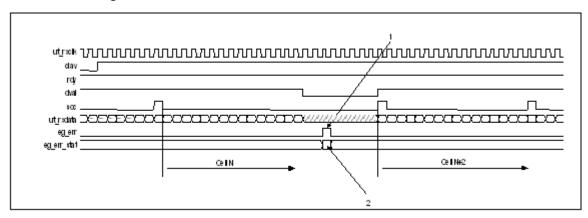

#### 7.2.2 Cell Level Transfer - Back to Back Cells

If the Master keeps ut\_rxenb asserted at the end of a cell transfer **1** and if the Slave has a new cell to send, the Slave keeps ut\_rxclav drives the new cell asserting ut\_rxsoc to indicate the start of a new cell **2**.

Figure 9: Back to Back Cells Transfer

## 8.0 Core Management and Error Handling

On Ingress, the Utopia Master Blocks are designed to handle and report Utopia errors such as Parity error or wrong cell length. Errored cells are discarded with an error status provided on pins for use by external management facilities.

The error handling only applies to the corresponding receive parts of the Core (i.e. Ingress Ports).

When an errored cell is received on the Utopia interface, the Core discards the complete cell and provides a cell discard indication (Signal eg\_err asserted)  $\mathbf{1}$  together with a cell discard status (Signal eg\_err\_stat(1:0))  $\mathbf{2}$ .

**NOTE:** eg\_err is routed to the corresponding wrx\_err and erx\_err respectively (see Figure 4).

Figure 10: Cell Discard Indication

PARITY\_ FERR Valid when wrx/erx\_err is asserted. If set to one indicates that a cell is discarded with a parity error decoded by the Core.

LENGTH\_ ER Valid when wrx/erx\_err is asserted. If set to one indicates that a cell is discarded with a cell length error detected on the Utopia interface.

Table 9: Error Status Word Bit Coding

The signals are sampled on the corresponding clocks from the west interface:

- erx\_... sampled with wtxclk (west transmit clock)

- wrx\_... sampled with wrxclk (west receive clock)

# 9.0 Complexity and Performance Summary

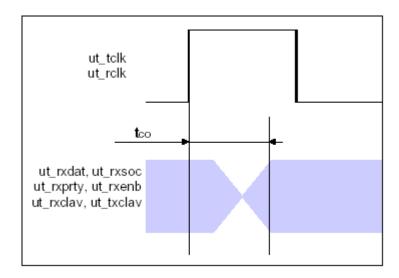

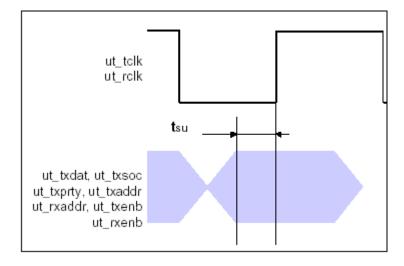

# 9.1 Timing Parameters Definition

Figure 11: Tco Timing Parameter Definition

Figure 12: Tsu Timing Parameter Definition

Table 10: 32-Bit Utopia Interface Timing Characteristics

| Parameter          | typ | Max (worst) | Unit |  |  |

|--------------------|-----|-------------|------|--|--|

| tco                | 7.0 | 6.5         | ns   |  |  |

| tsu                | 2.5 | 2.0         | ns   |  |  |

| wrxclk             |     | 90          | MHz  |  |  |

| wtxclk             |     | 90          | MHz  |  |  |

| erxclk             |     | 90          | MHz  |  |  |

| etxclk             |     | 90          | MHz  |  |  |

| minimum reset time | 50  |             | ns   |  |  |

**NOTE:** timing model "worst" case is used.

### 10.0 Device Pinout

# 10.1 Signals Overview

Table 11: Signals Overview Table

| Signals                                     | Description                                                                |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| wrxclk, wrxclav, wrxenb*,<br>wrxdat, wrxsoc | West Utopia Receive Interface.                                             |  |  |  |  |

| wtxclk, wtxclav, wtxenb*, wtxdata, wtxsoc   | West Utopia Transmit Interface.                                            |  |  |  |  |

| wrx_err, wrx_err_stat                       | West Interface error indication (sampled with wrxclk).                     |  |  |  |  |

|                                             |                                                                            |  |  |  |  |

| erxclk, erxclav, erxenb*, erxdata, erxsoc   | East Utopia Receive Interface.                                             |  |  |  |  |

| etxclk, etxclav, etxenb*, etxdata, etxsoc   | East Utopia Transmit Interface.                                            |  |  |  |  |

| erx_err, erx_err_stat                       | East Interface error indication (sampled with wtxclk).                     |  |  |  |  |

|                                             |                                                                            |  |  |  |  |

| prty_en, cellsize                           | Configuration Pins to be board wired. Cellsize[0-1] should be tied to GND. |  |  |  |  |

| reset                                       | Active high device reset                                                   |  |  |  |  |

|                                             |                                                                            |  |  |  |  |

| GND                                         | Ground                                                                     |  |  |  |  |

| VCC                                         | Device Power 2.5 V                                                         |  |  |  |  |

| clk(x)                                      | unused clock inputs should be tied to GND                                  |  |  |  |  |

| IOCTRL(x)                                   |                                                                            |  |  |  |  |

| VCCIO(x)                                    | IO Power 3.3 V                                                             |  |  |  |  |

| INREF(x)                                    | connect to GND                                                             |  |  |  |  |

| PLLRST(x)                                   | connect to GND or VCC                                                      |  |  |  |  |

| PLLOUT(x)                                   | connect to GND or VCC                                                      |  |  |  |  |

| VCCPLL(x)                                   |                                                                            |  |  |  |  |

| GNDPLL(x)                                   |                                                                            |  |  |  |  |

| TCK, TRSTB                                  | JTAG signals. connect to GND                                               |  |  |  |  |

| TMS, TDI                                    | JTAG signals. connect to VCC                                               |  |  |  |  |

| TDO                                         | JTAG signal. leave open                                                    |  |  |  |  |

| iov                                         |                                                                            |  |  |  |  |

| nc                                          | not connected. should be left open                                         |  |  |  |  |

<sup>\*:</sup> active low signal

16

**NOTE:** Unused Pins (data busses) in the following tables are to be handled like "nc".

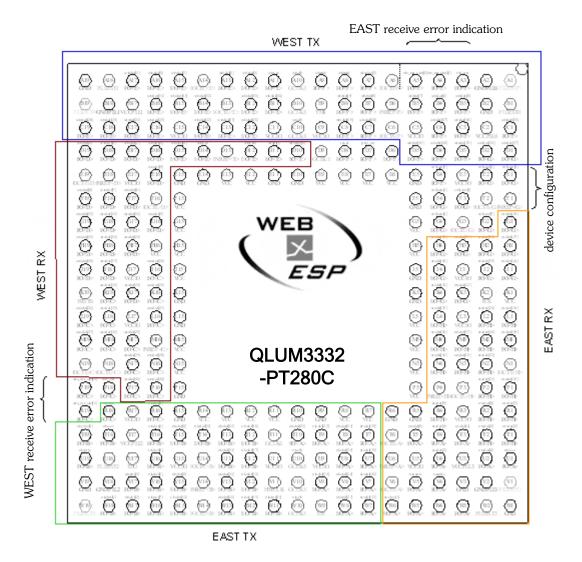

### 10.2 PT280 FPBGA Device Diagram

Figure 13: PT280 bottom view (0.8mm FPBGA)

18

### 10.3 PT280 FPBGA Pinout Table

Table 12: PT280 FPBGA Pinout Table

| PIN | Function        | PIN | Function         | PIN      | Function   | PIN | Function        | PIN | Function   |

|-----|-----------------|-----|------------------|----------|------------|-----|-----------------|-----|------------|

| A1  | pllout(3)       | D1  | wtxdat[27]       | G19      | wrxdat[12] | N16 | wrxdat[28]      | U6  | inref(a)   |

| A2  | gndpll(0)       | D2  | wtxdat[28]       | H1       | erxdat[27] | N17 | wrxdat[29]      | U7  | etxdat[29] |

| A3  | erx_err         | D3  | wtxdat[29]       | H2       | erxdat[28] | N18 | ioctrl(c)       | U8  | etxdat[25] |

| A4  | erx_err_stat[0] | D4  | wtxdat[30]       | H3       | erxdat[29] | N19 | ioctrl(c)       | U9  | vccio(a)   |

| A5  | erx_err_stat[1] | D5  | wtxdat[30]       | H4       | erxdat[30] | P1  | erxdat[10]      | U10 | erxclk     |

| A6  | ioctrl(f)       | D6  | nc (cellsize[0]) | H5       | vcc        | P2  | erxdat[11]      | U11 | vccio(b)   |

| A7  | wtxclav[0]      | D7  | prty_en          | H15      | vcc        | P3  | ioctrl(h)       | U12 | etxdat[17] |

| A8  | wtxprty         | D8  | reset            | H16      | vcc        | P4  | inref(h)        | U13 | etxdat[17] |

| A9  | wtxprty         | D9  | clk(8)           | H17      | wrxdat[13] | P5  | vcc             | U14 | ioctrl(b)  |

| A10 | wtxclk          | D10 | wrxclav[0]       | H18      | wrxdat[14] | P15 |                 | U15 | . ,        |

| A10 | Wtxsoc          | D10 |                  | H19      |            | P16 | gnd             | U16 | vccio(b)   |

| A11 |                 | D11 | wrxprty          |          | wrxdat[15] | P17 | wrxdat[30]      | U17 | etxdat[5]  |

|     | wtxdat[0]       |     | wrxenb           | J1<br>J2 | erxdat[24] | P17 | wrxdat[31]      |     | tdo        |

| A13 | wtxdat[1]       | D13 | inref(e)         |          | erxdat[25] |     | wrx_err         | U18 | pllrst(2)  |

| A14 | ioctrl(e)       | D14 | wrxsoc           | J3       | vccio(g)   | P19 | wrx_err_stat[0] | U19 | etxprty    |

| A15 | wtxdat[2]       | D15 | wrxdat[0]        | J4       | erxdat[26] | R1  | erxdat[7]       | V1  | pllout(2)  |

| A16 | wtxdat[3]       | D16 | wrxdat[1]        | J5       | gnd        | R2  | erxdat[8]       | V2  | gndpll(3)  |

| A17 | wtxdat[4]       | D17 | wrxdat[2]        | J15      | VCC        | R3  | vccio(h)        | V3  | gnd        |

| A18 | pllrst(1)       | D18 | wrxdat[3]        | J16      | wrxdat[16] | R4  | erxdat[9]       | V4  | erxprty    |

| A19 | gnd             | D19 | wrxdat[4]        | J17      | vccio(d)   | R5  | gnd             | V5  | erxenb     |

| B1  | pllrst(0)       | E1  | cellsize[3]      | J18      | wrxdat[17] | R6  | gnd             | V6  | ioctrl(a)  |

| B2  | gnd             | E2  | cellsize[2]      | J19      | wrxdat[18] | R7  | VCC             | V7  | etxdat[30] |

| В3  | wtxdat[5]       | E3  | vccio(g)         | K1       | vcc        | R8  | VCC             | V8  | etxdat[26] |

| B4  | wtxdat[6]       | E4  | cellsize[1]      | K2       | tck        | R9  | gnd             | V9  | etxdat[23] |

| B5  | wtxdat[7]       | E5  | gnd              | K3       | erxdat[22] | R10 | gnd             | V10 | clk(1)     |

| B6  | inref(f)        | E6  | vcc              | K4       | erxdat[23] | R11 | VCC             | V11 | clk(4)     |

| B7  | wtxdat[8]       | E7  | vcc              | K5       | gnd        | R12 | vcc             | V12 | etxdat[18] |

| B8  | wtxdat[9]       | E8  | vcc              | K15      | gnd        | R13 | vcc             | V13 | etxdat[14] |

| B9  | tms             | E9  | vcc              | K16      | wrxdat[19] | R14 | vcc             | V14 | inref(b)   |

| B10 | clk(6)          | E10 | gnd              | K17      | wrxdat[20] | R15 | gnd             | V15 | etxdat[9]  |

| B11 | wtxdat[10]      | E11 | gnd              | K18      | wrxdat[21] | R16 | etxdat[3]       | V16 | etxdat[6]  |

| B12 | wtxdat[11]      | E12 | vcc              | K19      | trstb      | R17 | vccio(c)        | V17 | etxdat[1]  |

| B13 | ioctrl(e)       | E13 | VCC              | L1       | erxdat[19] | R18 | etxenb          | V18 | gndpll(2)  |

| B14 | wtxdat[12]      | E14 | gnd              | L2       | erxdat[20] | R19 | wrx_err_stat[1] | V19 | gnd        |

| B15 | wtxdat[13]      | E15 | gnd              | L3       | vccio(h)   | T1  | erxdat[2]       | W1  | gnd        |

| B16 | wtxdat[14]      | E16 | wrxdat[5]        | L4       | erxdat[21] | T2  | erxdat[3]       | W2  | pllrst(3)  |

| B17 | vccpll(1)       | E17 | vccio(d)         | L5       | vcc        | T3  | erxdat[4]       | W3  | nc         |

| B18 | gndpll(1)       | E18 | inref(d)         | L15      | gnd        | T4  | erxdat[5]       | W4  | nc         |

| B19 | pllout(0)       | E19 | ioctrl(d)        | L16      | wrxdat[22] | T5  | erxdat[6]       | W5  | nc         |

| C1  | wtxdat[15]      | F1  | inref(g)         | L17      | vccio(c)   | T6  | ioctrl(a)       | W6  | erxclav[0] |

| C2  | vccpll(0)       | F2  | ioctrl(g)        | L18      | wrxdat[23] | T7  | etxdat[28]      | W7  | etxdat[31] |

| C3  | wtxdat[16]      | F3  | cellsize[5]      | L19      | wrxdat[24] | T8  | etxdat[24]      | W8  | etxdat[27] |

| C4  | wtxdat[17]      | F4  | cellsize[4]      | M1       | erxdat[15] | Т9  | etxdat[22]      | W9  | tdi        |

| C5  | vccio(f)        | F5  | gnd              | M2       | erxdat[16] | T10 | etxdat[21]      | W10 | etxclk     |

| C6  | ioctrl(f)       | F15 | VCC              | МЗ       | erxdat[17] | T11 | clk(3)          | W11 | etxdat[20] |

| C7  | wtxdat[18]      | F16 | ioctrl(d)        | M4       | erxdat[18] | T12 | etxdat[16]      | W12 | etxdat[19] |

| C8  | wtxdat[19]      | F17 | wrxdat[6]        | M5       | vcc        | T13 | etxdat[12]      | W13 | etxdat[15] |

| C9  | vccio(f)        | F18 | wrxdat[7]        | M15      | vcc        | T14 | etxdat[11]      | W14 | ioctrl(b)  |

| C10 | wrxclk          | F19 | wrxdat[8]        | M16      | inref(c)   | T15 | etxdat[8]       | W15 | etxdat[10] |

| C11 | vccio(e)        | G1  | erxdat[31]       | M17      | wrxdat[25] | T16 | etxdat[4]       | W16 | etxdat[7]  |

| C12 | wtxdat[20]      | G2  | cellsize[7]      | M18      | wrxdat[26] | T17 | vccpll(2)       | W17 | etxdat[2]  |

| C13 | wtxdat[21]      | G3  | ioctrl(g)        | M19      | wrxdat[27] | T18 | etxsoc          | W18 | etxdat[0]  |

| C14 | wtxdat[22]      | G4  | cellsize[6]      | N1       | ioctrl(h)  | T19 | etxclav[0]      | W19 | pllout(1)  |

| C15 | vccio(e)        | G5  | VCC              | N2       | erxdat[12] | U1  | erxsoc          |     | F 2 20(1)  |

| C16 | wtxdat[23]      | G15 | VCC              | N3       | erxdat[13] | U2  | erxdat[0]       |     |            |

| C17 | wtxdat[24]      | G16 | wrxdat[9]        | N4       | erxdat[14] | U3  | vccpll(3)       |     |            |

| C17 | wtxdat[25]      | G17 | wrxdat[10]       | N5       | vcc vcc    | U4  | erxdat[1]       |     |            |

| C19 | wtxdat[26]      | G17 | wrxdat[10]       | N15      | vcc        | U5  | vccio(a)        |     |            |

| CIS | wixudi[ZU]      | 910 | wixudi[11]       | GINI     | VCC .      | US  | νυσιυ(α)        |     |            |

### 11.0 References

• ATM Forum, Utopia Level 3, af-phy-0136.000, 1999

### 12.0 Contact

#### QuickLogic Corp.

Tel: 408 990 4000 (US)

: + 44 1932 57 9011 (Europe)

: + 49 89 930 86 170 (Germany)

: + 852 8106 9091 (Asia)

: + 81 45 470 5525 (Japan)

E-mail : info@quicklogic.com

Internet : www.quicklogic.com

20