Storage

Technology

# MERGED ARCHITECTURE CONTROLLER

2400126 2400328

MAC Chip

#### **FEATURES**

- Combines disk formatter and buffer controller functions in one VLSI chip

- Forty-three control, status, and parameter registers

- Interfaces easily to several popular microprocessors including the 68000, 80188, 80186 and 8031. The MAC interfaces directly to the 8031 with no additional circuitry.

# DESCRIPTION

The MAC chip is an integral part of a sophisticated high performance controller architecture developed at Emulex.

The Merged Architecture Controller (MAC) chip combines buffer management and disk formatter functions in a single chip. These two functions comprise the heart of modern, microprocessor-based disk controllers. The availability of these functions in a single package allows designers to create controllers that take only a few square inches of printed circuit board space.

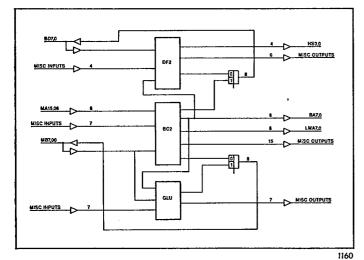

The MAC chip is implemented using CMOS technology. Figure 1 shows the major functional modules in the MAC.

#### **Buffer Controller**

- Directly controls up to 64K bytes of dynamic RAM (DRAM)

- Provides dynamic buffer memory timing and automatic refresh

- Checks and generates parity for buffer memory

- Connects the microprocessor bus directly to the buffer data bus, allowing microprocessor access to the buffer memory and external channels

- Decodes the microprocessor address for buffer memory and the I/O devices

Supports automatic address reload for three of the four DMA channels

#### **Disk Formatter**

- Supports ST-506/412, ESDI, SMD, and SMD/E drive formats

- Supports disk data rates to 24 Megabits/second

- Supports hard and soft sector modes

- Five-byte data FIFO

- Internal ID field comparator

- Forty-eight-bit ECC for data fields

- CRC generator/checker for ID fields

- Disk read, write, and format functions implemented using a comprehensive command set

- Interfaces directly to disk drive electronics for embedded applications

- Halts disk write operations on power fail detect

- Supports variable length sectoring from 1 to 4096 bytes

Storage

Technology

The disk formatter module, referred to as the DF2, is that part of the MAC chip which controls hard-disk format functions. It is compatible with the interface and format requirements of most 14, 8, 5¼ and 3½-inch disks operating in hard or soft sectored modes. It supports SMD, SMD-E, ESDI, and ST-506/412 type disks. The DF2 handles serial disk transfer at rates of up to 24M bits per second.

The buffer controller module, or BC2, which provides DMA control of local dynamic RAM has four programmable DMA channels (one of which is dedicated to the DF2). It also supports automatic refresh of buffer RAM. The BC2 provides a link between the microprocessor bus and the buffer data bus. This allows the microprocessor to access the buffer RAM, DF2 registers, host interface logic, and other VLSI devices on the buffer data bus.

A third module, the GLU module, provides various configuration and reset functions, including a watchdog timer.

The BC2 module is functionally compatible with the stand-alone version of the Emulex Buffer Controller 2. The DF2 design in the MAC is compatible with the stand-alone version of the Disk Formatter, but includes a number of additional features.

With some external logic the MAC chip can be controlled by a variety of microprocessors, including the 80188, 80186, and 68000. It interfaces directly to the Intel 8031 microprocessor with no additional circuitry.

Figure 1. MAC Chip Major Functional Blocks

# SYSTEM ORGANIZATION

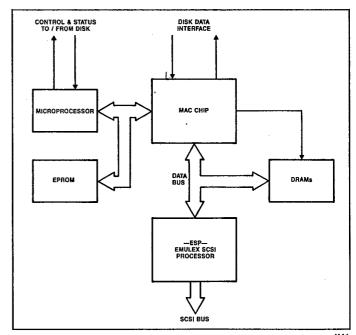

A typical disk controller block diagram is shown in Figure 2. An entire embedded SCSI-compatible disk controller design requires only the following parts:

| Part                           | Qty |

|--------------------------------|-----|

| 8031 Microprocessor            | 1   |

| 32K or 64K byte EPROM          | 1   |

| 64K X 4 DRAM                   | 2   |

| 64K X 1 DRAM (parity) optional | 1   |

| SCSI Protocol Controller (ESP) | 1   |

| MAC Chip                       | 1   |

| Total                          | 7   |

The Emulex controller architecture, of which the MAC chip is a part, uses two internal buses. By separating the microprocessor and buffer data buses, Emulex controllers are able to achieve superior performance using inexpensive components such as the 8031 microprocessor.

The BC2 module of the MAC makes this bus separation possible. It allows high speed DMA between the controller's buffer RAM and either the disk formatter or host interface without direct microprocessor intervention. This frees the microprocessor to decode a command from the host or to set up the disk drive for operation while data is being transferred into or out of the buffer RAM.

The microprocessor works with the DF2 portion of the MAC to handle all of the disk functions. The microprocessor controls head position, manages error correction, and monitors drive status. The DF2 is responsible for head selection, generation and comparison of ECCs, and transfer of serial NRZI data to and from the disk.

Figure 2. Disk Controller

#### **PACKAGING**

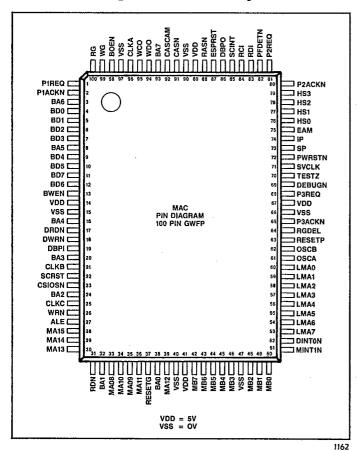

The MAC chip is available in two package types: a 100-pin gull-wing flat-pack for surface-mount applications and a 100-pin grid array (PGA) for throughhole mounting applications. The part numbers for the two packages are:

2400328

Gull-Wing Flat-Pack

2400126 Pin Grid Array

#### **GLU MODULE**

This module contains reset logic and the MAC Register, which is used to indicate reset status and to set some MAC chip configuration options. This module contains logic that is required for most controller applications and reduces the external logic required to design a controller around the MAC chip.

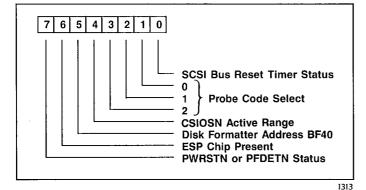

# **MAC Register**

The MAC Register resides in the microprocessor address space. It is used to determine which reset condition caused an interrupt and for controller configuration. Figure 3 defines the MAC Register bits.

Figure 3. MAC Register

#### 1.6 Millisecond Timer

This serves as a 'watchdog' timer to ensure that the controller is initialized after a SCSI bus reset. The timer starts after the SCSI bus "reset" signal becomes inactive. It must be turned off by the microprocessor within 1.6 msec or the timer generates a hard reset on output pins RESETP and RESETG.

### **Reset Functions**

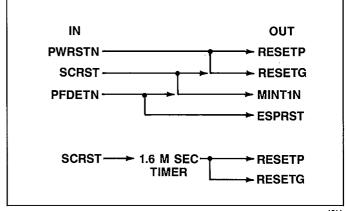

The GLU Module contains logic for the propagation, control, and status of reset signals to the controller. There are three input signals that are used to initialize the MAC chip, which are passed on through one of several reset outputs. Figure 4 is a simplified illustration of the propagation paths for the signals through the GLU module. The table below defines the signals. See also Pin Descriptions.

Figure 4. Reset Propagation

| Signal | Direction | Description                                                                                                              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| PWRSTN | IN        | Main Reset Signal for MAC chip; initializes MAC chip. It is passed on as RESETP and RESETG.                              |

| SCRST  | IN        | SCSI Bus Reset Signal: Starts 1.6 msec watchdog timer on transition from true to false. Causes MINT1N interrupt.         |

| PFDETN | IN        | Power Fail/Detect: Interrupts the processor (MINTIN) and resets the SCSI protocol chip (if MAC Register, bit 6, is set). |

| RESETP | OUT       | Reset Microprocessor: Can be held true by grounding DEBUGN for in-circuit emulator operation                             |

| RESETG | OUT       | Reset General: Used to reset all controller logic except the microprocessor.                                             |

| ESPRST | OUT       | Reset SCSI Protocol Chip:<br>Can be disabled by setting<br>MAC Register, bit 6.                                          |

Storage

Technology

Figure 5. Disk Formatter Block Diagram

1161

## **DISK FORMATTER**

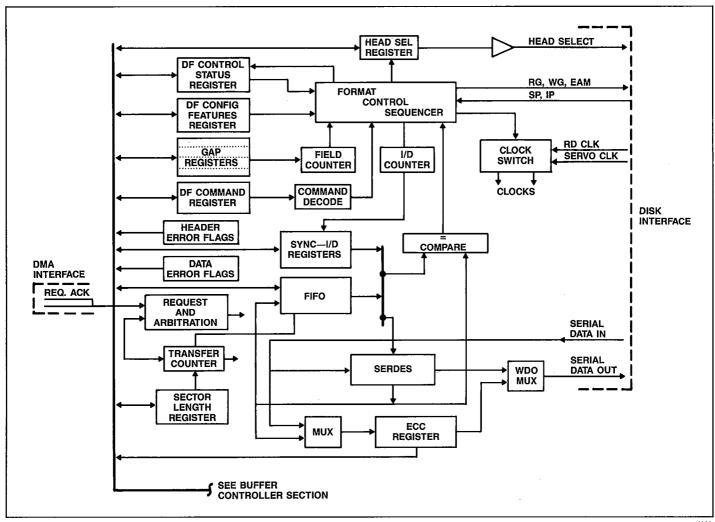

The Disk Formatter Module provides a complete serial, read/write interface to ST-506/412, ESDI, SMD, and SMD-E drives. It resides on DMA channel 0, the highest priority DMA channel.

The DF2 can be configured to support a wide variety of media formats, which gives it the flexibility necessary to support high density disk drives.

Figure 5 is a detailed block diagram of the DF2. The major functional blocks include:

The SERDES, which serializes and deserializes disk data

- The ECC Register, which generates and checks a 48-bit ECC for data fields and a 16-bit CRC for sector headers

- The Format Control Sequencer, which manages read, write, format and other commands in the sequence specified by the various configuration registers

#### **Error Correction Capabilities**

The MAC chip uses a 48-bit shift register (the ECC Register) to generate CRC and ECC fields for error detection and correction.

A sixteen-bit CRC code is used to detect errors in sector headers. The code used is the CRC-CCITT polynomial.

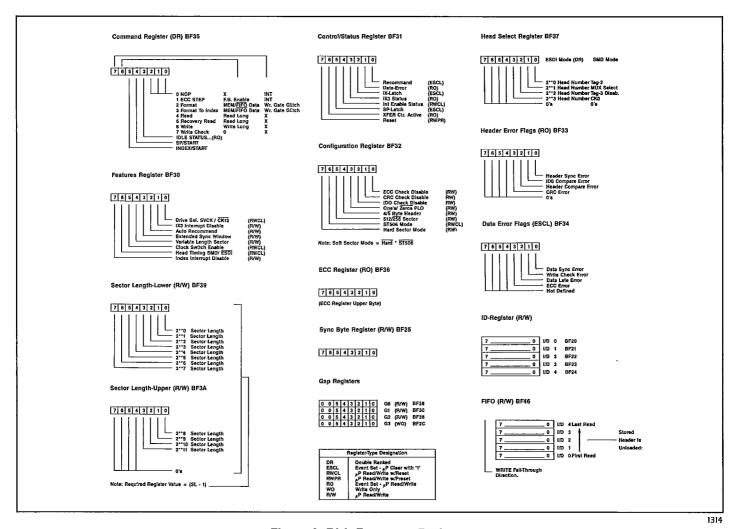

Figure 6. Disk Formatter Registers

The MAC chip generates a 48-bit ECC code to allow both detection and correction of errors in data fields.

The controller's microprocesser uses the ECC code to correct single burst errors up to 19-bits span-width on 256-byte sectors or 15-bits on 4096-byte sectors.

#### DF2 Registers

Figure 6 shows the 21 DF2 registers that are accessible to the microprocessor. Values loaded into these registers control all operations of the disk interface.

The following paragraphs are general descriptions of the register functions. The absolute hex addresses (as defined by setting MAC Register, bit 5) of the registers are also shown in Figure 6.

### **Control and Status Register**

This read/write register contains status and control information which allows the microprocessor to enable or disable interrupts, determine the cause of an interrupt, and reset the DF2 logic.

### **Configuration Register**

This read/write register is used by the microprocessor to select various media format options and modes of operation. Including, sector mode (hard or soft), sector size, header size, PLO sync byte contents, and CRC/ECC check disable and header compare disable.

Storage

Technology

## **Header Error Register**

This read-only register contains error bits associated with the header area of a sector. These include CRC, header compare, ID compare, and header sync errors.

## **Data Error Register**

This read/clear register contains error bits associated with the data area of the sector, including ECC check, data late, write check, and data sync errors. If any error bit is set, the DF2 will cancel a pending command and ignore any new commands. The microprocessor must clear the error and reissue any commands that were pending. The conditions that set these bits also cause a Data Error Interrupt.

## **Command Register**

This register is loaded with the next command to be executed by the DF2. The start of command execution is controlled by the value of bits 4 and 5:

| Bits<br>5 4 | Command Start<br>Condition |  |  |  |

|-------------|----------------------------|--|--|--|

| 00          | Immediate                  |  |  |  |

| 01          | Sector Pulse               |  |  |  |

| 10          | Index Pulse                |  |  |  |

| 1 1         | Sector or Index Pulse      |  |  |  |

The microprocessor must clear the latched index pulse before issuing a command to start on index.

The DF2 implements the following commands:

| Bits<br>210 | Command         |

|-------------|-----------------|

| 000         | No Operation    |

| 001         | ECC Step        |

| 010         | Format          |

| 011         | Format to Index |

| 100         | Read            |

| 101         | Recovery Read   |

| 110         | Write           |

| 111         | Write Check     |

This register is double ranked. Data is always written to the first rank and read from the second rank. This allows the microprocessor to issue the next command while the current command is still executing.

## **ID** Registers

The contents of these five registers hold the four or five bytes of the header. During read and write operations, the DF2 compares the contents of these registers with the corresponding bytes of the header read from the disk. During format operations, the DF2 writes the contents of these registers on the disk as the corresponding bytes of the header.

# Sync Byte Register

This register defines the sync byte pattern used to detect the start of the header and data fields. The DF2 compares the contents of this register with the contents of the SERDES shift register to detect the occurrence of the sync pattern within the sync window. When executing a Format or Write command, the contents of this register are loaded into the shift register when writing the sync pattern.

#### **FIFO Register**

This register is the data FIFO. Writing into this pseudoregister loads the top of the FIFO. Reading this register unloads the bottom of the FIFO. The FIFO is accessed by the microprocessor during error correction sequences, and to read the header of a sector from the disk, when it did not compare to the ID registers.

### Gap Registers

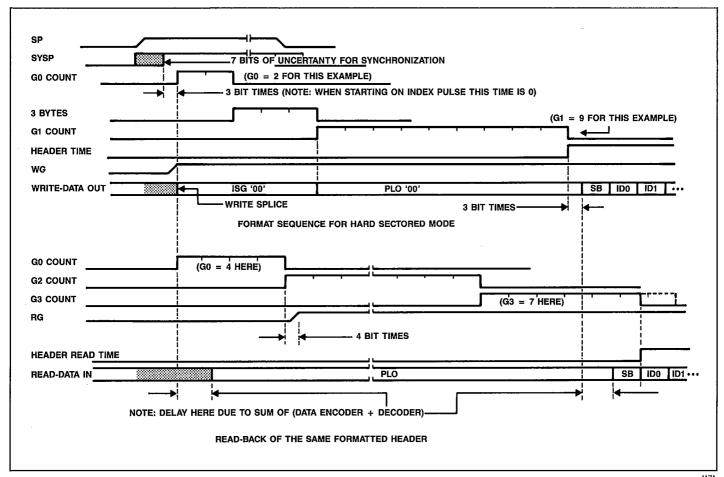

The four Gap Registers, known as G0, G1, G2, and G3, provide variable parameters for formatter gap timing. G0 defines the delay from command start to the assertion of Read Gate in hard sectored mode and the EAM delay time in soft sectored mode. G1 defines the length of the PLO sync area. G2 and G3 together define the start of the sync window and its length. The Gap Registers are 6 bits in length. The high-order 2 bits are zero when read. A Gap Register programmed with a binary number N counts N bytes with the exception of N equal to zero, which causes a count of 64 bytes.

#### ECC Register

This read-only register is the high-order eight bits of the ECC/CRC checker/generator. The ECC Register is loaded via the FIFO by using the Step command.

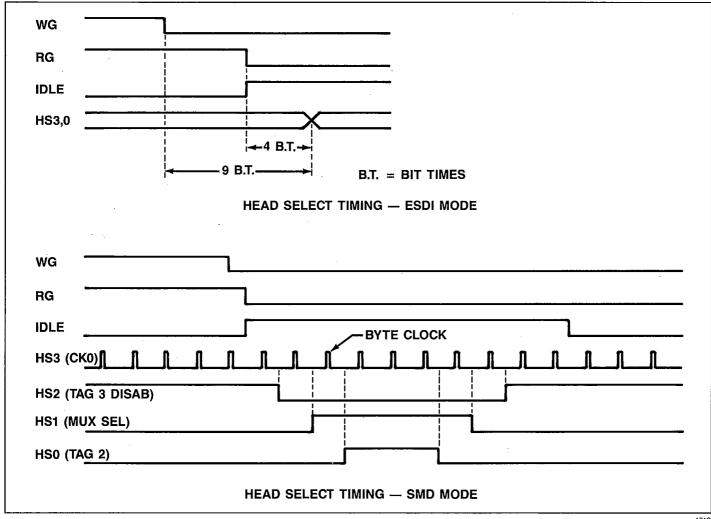

### **Head Select Register**

This register has two different definitions, depending on whether the DF2 is configured for ESDI or SMD operation:

- In ESDI mode it is a 4-bit double-ranked register used for head selection. The head select output pins are updated while the sequencer is idle or between commands. The double ranking allows the microprocessor to preload the next head selection value without affecting the current operation.

- In SMD mode, this register is written to start a head select sequence; the data written has no effect. For this mode, the HSn pins become TAG2 Disable, Mux Select, TAG 3 and clock 0.

## **Sector Length Registers**

These two read/write registers contain the 12-bit value used to define the number of bytes in the data field when variable length sectors are selected. The sector length is one byte longer than the value loaded into these registers.

# **Feature Register**

This read/write register allows the microprocessor to select certain features or modes of operation, including head select mode, variable length sectors, and auto re-command mode.

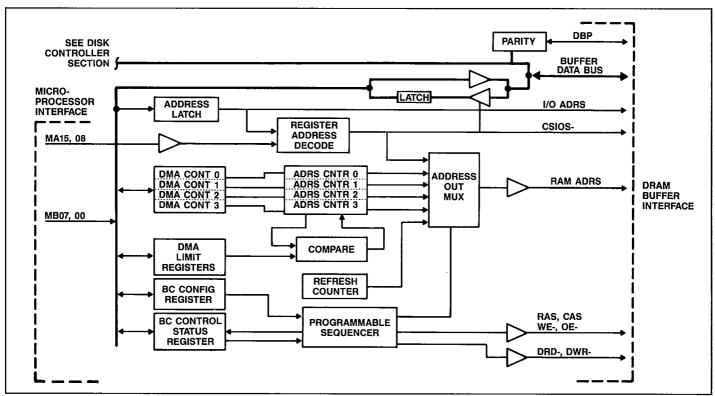

# **BUFFER CONTROLLER**

The buffer control module's basic function is to control data movement into and out of a dynamic RAM buffer memory, and to provide a connection between the two controller buses (the microprocessor bus and the buffer data bus). Figure 7 shows the internal organization of the BC2.

The BC2 supports four independent DMA channels, each with separate REQ/ACK signals to handle asynchronous data transfers. For DMA channel address management, the BC2 maintains separate 16-bit address pointer registers, limit registers, and reload registers. With the limit and reload registers, the microprocessor can create circular buffers on any modulo-256 byte boundary.

Figure 7. Buffer Controller Block Diagram

Storage

Technology

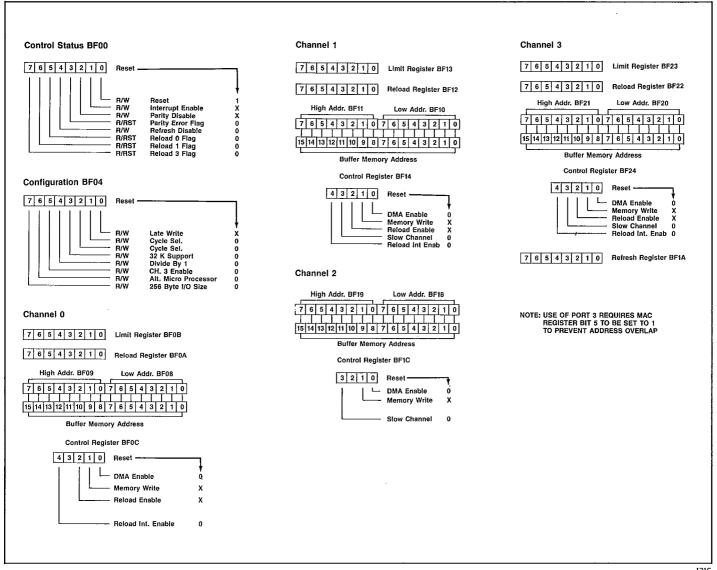

Figure 8. Buffer Controller Registers

1315

The BC2 interfaces to the eight-bit microprocessor bus and to the eight-bit buffer data bus. The microprocessor allows access to both buffer memory and the other devices on the buffer data bus. The BC2 outputs a multiplexed buffer address and directly controls signals RAS, CAS, BWEN and BOEN. This arrangement is suitable for directly addressing dynamic RAM memory chips.

# **Buffer Controller Registers**

The BC2 contains the registers shown in Figure 8, which are used by the microprocessor to configure, control, and monitor DMA transfers between buffer RAM and

external devices such as the Emulex SCSI Protocol Chip. A general description of the registers follows.

#### **Control/Status Register**

The Control and Status Register controls general BC2 functions. Three of the bits control parity generation and detection. Refresh can be disabled with the Refresh Disable bit. Another bit is used to reset the BC2 or indicate that it has been reset by the external RESET input. Additional bits allow the microprocessor to identify the DMA channel that interrupted on an address reload.

The microprocessor uses this register to configure the BC2 for operation in different controller environments.

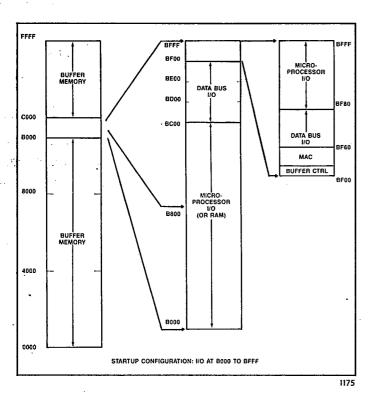

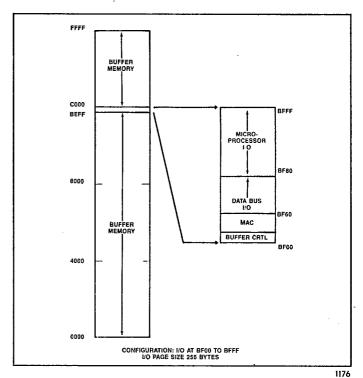

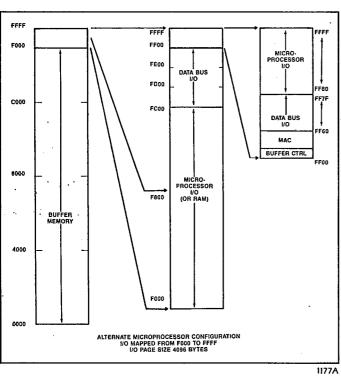

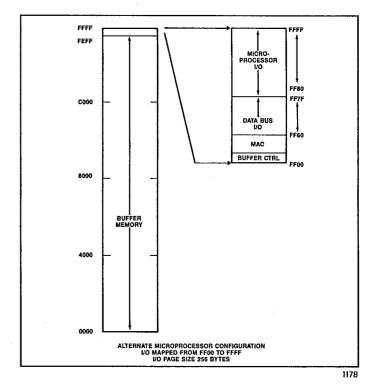

Because the BC2 decodes the microprocessor's memory addresses, the BC2 determines how the processor's address space is mapped. Figure 9 shows the four address maps that are supported. Setting bit 7 selects a page size of 256 bytes instead of 4096. Also, setting bit 6 causes the I/O page of memory to start at F000 instead of B000. These mapping options allow the MAC to support microprocessors other than the 8031.

Bits 2 and 1 of this register select the clock divide factor. Combining the four divide factors with various clock speeds allows the MAC to support a wide range of DRAM cycle times. See the following table.

| Bit              |             | Divide            | External Clock Speed       |                            |                                      |  |

|------------------|-------------|-------------------|----------------------------|----------------------------|--------------------------------------|--|

| 2                | 1           | Factor            | 24 MHz                     | 20 MHz                     | 16 MHz                               |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0 | 10<br>8<br>6<br>4 | 416 ns<br>333 ns<br>250 ns | 500 ns<br>400 ns<br>300 ns | 625 ns<br>500 ns<br>375 ns<br>250 ns |  |

|                  |             |                   | DRAM Cycle Time            |                            |                                      |  |

All four DMA channels use the cycle time established by this register. However, channels one, two, and three may be separately programmed to operate in 10-cycle mode by setting the slow-channel bit in the appropriate Channel Control Register. This feature allows the MAC to operate with devices such as floppy disk controller chips.

There are four sets of four registers which are used to configure and control the DMA channels. The register sets function identically; however, channel two (the lowest priority channel) does not support automatic reload, and channel zero (the highest priority channel) does not support the slow channel feature. The registers are discussed below. First, however, a general description of the DMA process:

To set up a DMA transfer, the microprocessor loads a DMA starting address into the buffer memory address counter (accessed via the High and Low Address Registers) and sets the DMA enable bit in the Port Control Register. The transfer is then controlled by the DMA device connected to that channel using the REQ/ACK signal pair. The DMA device contains the byte counter for the transfer.

If the reload feature is enabled, and if the buffer memory address equals the value in the limit register, the buffer memory address counter will be loaded with the value in the reload register.

Low and High Address Registers The microprocessor uses these read/write registers to load the 16-bit buffer memory address register, which contains the address pointer used by the BC2 to generate buffer addresses. During DMA, the buffer memory address register is incremented with every byte that is transferred.

Limit and Reload Registers These registers are used to implement the BC2's automatic address reload feature. The Limit Register contains the most significant byte of the limit address. The least significant byte is always FF. When the buffer memory address register equals the value specified in the Limit Register, it is loaded with the value in the Reload Register. The Reload Register contains the most significant byte of the reload address. The least significant byte of the new address will be 00.

This reload feature can be used to create large circular buffers without the microprocessor having to reload the buffer address. The buffers will be on modulo-256 byte boundaries.

**Channel Control Register** The microprocessor uses this register to select configurations specific to a DMA channel and to enable the DMA channel after configuring it.

## Refresh Register

This read/write register allows the microprocessor access to the refresh address counter. This counter supplies the row address the BC2 uses for refresh cycles on the dynamic RAM buffer.

When the BC2 is initialized, this counter is set to FF. The counter is incremented after each refresh cycle. Refresh cycle period is obtained by dividing the 20/24 MHz clock by 1.8, which produces a 10.7 or 12.8 microsecond period, respectively.

The refresh channel has the lowest priority of the BC2's five channels. However, normal DMA activity will refresh buffer memory should the refresh channel be locked out by higher priority channels.

### **PORTS**

The MAC chip has three basic ports: the microprocessor port, disk formatter port, and the buffer data port. These ports have some special features which are discussed below.

Storage .

Technology

Figure 9. Controller Memory Allocation

# **Microprocessor Port**

The MAC chip interfaces directly to the eight-bit multiplexed address and buffer data bus of the 8031 microprocessor. The microprocessor ALE signal controls an internal latch that holds the low-order address bits. The latched address is available on the LMA7-0 pins. Interfaces to non-multiplexed and 16-bit microprocessors can be implemented by the addition of external circuitries.

The MAC chip decodes the 8031's high-order address byte to distinguish between accesses to the I/O page or buffer memory. The MAC then generates the appropriate chip selects (I/O page) or multiplexed buffer address. This feature eliminates the requirement for discrete address decode logic and buffer memory address generation logic.

#### **Data Buffer Port**

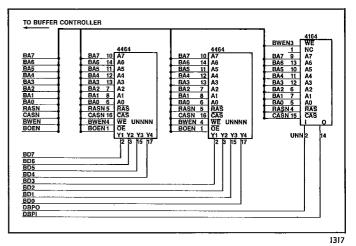

The Data Buffer Port connects the MAC chip to the data buffer. It consists of an eight-bit buffer data bus, a 16-bit multiplexed address bus, RAS, CAS, CASCAM, BWEN, and BOEN signals. It interfaces directly to most families of dynamic RAMs, including both by-one (64K x 1) and by-four (64K x 4) configurations of DRAMs. Figure 10 illustrates MAC chip applications with these two different DRAM types.

The Data Buffer Port also includes the REQ and ACKN signal pairs for each DMA channel (except channel 0, which is dedicated to the DF2 and therefore internal to the MAC). Other VLSI devices in the controller use the REQ and ACKN signals to control data transfers between themselves and the buffer RAM.

BA07-BA00 RAM Address Lines: The table below shows what addresses are presented on the associated RAM address lines during the row address strobe (RASN) and column address strobe (CASN) times.

Output Pins : BA07 BA06 BA05 BA04 BA03 BA02 BA01 BA00 at RASN time : A7 A6 A5 A4 A3 A2 A1 A0 at CASN time : A15 A8 A13 A12 A11 A10 A9 A14

The four DMA channels, microprocessor accesses, and refresh functions are prioritized to resolve potential conflicts between VLSI devices that attempt to conduct DMA at the same time (i.e., two REQ signals received at the same time). The priority is as follows:

| Function            | Rank | Comment |

|---------------------|------|---------|

| Microprocessor      | 0    | Highest |

| DMA Channel 0 (DF2) | 1    | -       |

| DMA Channel 1       | 2    |         |

| DMA Channel 3       | 3    |         |

| DMA Channel 2       | 4    |         |

| Refresh             | 5    |         |

Figure 10. 64K RAM Using 64K x 4 Parts

#### **Disk Formatter Port**

For embedded controller applications of the MAC chip, the disk interface signals can be connected directly to the drive electronics. When used in a stand-alone controller, additional control and status latches and interface drivers are usually required.

Serial input timing is derived from five disk signals: sector pulse (SP), index pulse (IP), servo clock (SVCLK), read clock (RCI), and read data (RDI). The DF2 generates serial output timing for the following disk signals: read gate (RG), write gate (WG), enable address mark (EAM), write clock out (WCO), write data (WDO), and head select (HSO-HS3).

Additional head select lines can be added by using a single, discrete read/write latch. The microprocessor would directly access the head select lines controlled by this latch.

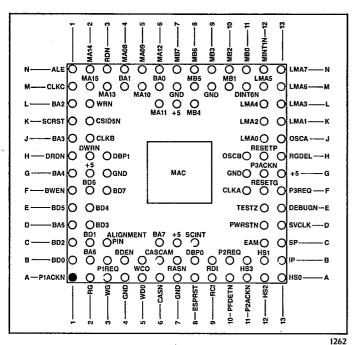

#### PIN DESCRIPTION

The pin designations for the two packages in which the MAC is available are shown in Figures 12 and 13. A description of pin functions are in the table that follows.

Storage

Technology

Figure 12. Pin Grid Array

Figure 13. Gull-wing Flat-Pack

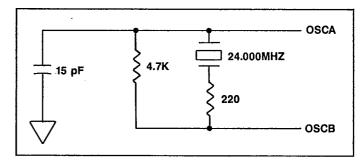

# **Crystal Oscillator Input**

The MAC provides for the use of a crystal oscillator or an external clock input. The crystal used should have the following parameters:

Crystal Type : AT Cut

Frequency : Fundamental

Mode : Series Resonant

Figure 14. Typical Crystal Oscillator Circuit

1165

| ·           | Pin      | No.        |      |                  |                                                |

|-------------|----------|------------|------|------------------|------------------------------------------------|

| Cianal      |          |            | D:-  | Deltara          | Fatla                                          |

| Signal      | Flat     | PGA        | Dir. | Driver           | Function                                       |

| RDN         | 31       | NO3        | ı    |                  | $_{\mu}$ P Read Enable                         |

| WRN         | 26       | LO2        | ı    |                  | $\mu$ P Write Enable                           |

| ALE         | 27       | NOI        | 1    |                  | $\mu$ P ALE                                    |

| MINTIN      | 51       | NIZ        | 0    | TTL2             | <sub>μ</sub> P Interrupt 1                     |

| DINTON      | 52       | MII        | 0    | TTL2             | μP Interrupt 0                                 |

| RESETP      | 63       | H12        | 0    | TTL2             | $_{\mu}$ P Reset Out                           |

| MA15        | 28       | M02        | 0    | TTL4             | μP Address Bus 15                              |

| MA14        | 29       | N02        | 0    | TTL4             | μP Address Bus 14                              |

| MA13        | 30       | M03        | 0    | TTL4             | <sub>μ</sub> P Address Bus 13                  |

| MA12        | 39       | N06        | 0    | TTL4             | $_{\mu}^{P}$ Address Bus 12                    |

| MA11        | 36       | L06        | 0    | TTL4             | $_{\mu}$ P Address Bus 11                      |

| MA10        | 34       | M05        | 0    | TTL4             | μP Address Bus 10                              |

| MA09        | 35       | N05        | 0    | TTL4             | μP Address Bus 09                              |

| MA08<br>MB7 | 33<br>42 | N04<br>N07 | 0    | TTL4             | μP Address Bus 08                              |

| MB6         | 43       | N08        | 110  | 3state<br>3state | μP Data/Address Bus 7<br>μP Data/Address Bus 6 |

| MB5         | 44       | M08        | 10   | 3state           | μP Data/Address Bus 5                          |

| MB4         | 45       | L08        | 110  | 3state           | μP Data/Address Bus 4                          |

| MB3         | 46       | N09        | 110  | 3state           | μP Data/Address Bus 3                          |

| MB2         | 48       | NIO        | 1/0  | 3state           | μP DatalAddress Bus 2                          |

| MB1         | 49       | MIO        | 1/0  | 3state           | μP Data/Address Bus 1                          |

| МВО         | 50       | NII        | 1/0  | 3state           | <sub>μ</sub> P Data/Address Bus 0              |

| LMA7        | 53       | N13        | o    | TTL4             | Latched <sub>µ</sub> P Address 7               |

| LMA6        | 54       | M13        | Ö    | TTL4             | Latched <sub>µ</sub> P Address 6               |

| LMA5        | 55       | M12        | o    | TTL4             | Latched $\mu$ P Address 5                      |

| LMA4        | 56       | L12        | 0    | TTL4             | Latched <sub>µ</sub> P Address 4               |

| LMA3        | 57       | L13        | 0    | TTL4             | Latched $\mu$ P Address 3                      |

| LMA2        | 58       | K12        | 0    | TTL4             | Latched <sub>µ</sub> P Address 2               |

| LMA1        | 59       | K13        | 0    | TTL4             | Latched <sub>u</sub> P Address 1               |

| LMAO        | 60       | J12        | 0    | TTL4             | Latched <sub>µ</sub> P Address 0               |

(continued)

# (continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (continued)                                                                                                                |                                                                                                                                                                     |                                                                                                                                                                      |                          |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            | Pin No.                                                                                                                                                             |                                                                                                                                                                      |                          |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Signal                                                                                                                     | Fiat                                                                                                                                                                | PGA                                                                                                                                                                  | Dir.                     | Driver                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIREQ<br>PIACKN<br>P2REQ<br>P2ACKN<br>P3REQ                                                                                | 1<br>2<br>81<br>80<br>68                                                                                                                                            | B03<br>A01<br>B10<br>A11<br>F13                                                                                                                                      | -0-0-                    |                                                                   | Channel 1 REQ<br>Channel 1 ACK<br>Channel 2 REQ<br>Channel 2 ACK<br>Channel 3 REQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P3ACKN                                                                                                                     | 65                                                                                                                                                                  | G12                                                                                                                                                                  | ó                        | TTL4                                                              | Channel 3 ACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DRDN<br>DWRN<br>CSIOSN<br>DBPO<br>DBPI                                                                                     | 17<br>18<br>23<br>86<br>19                                                                                                                                          | H01<br>H02<br>K02<br>B08<br>H03                                                                                                                                      | 000010                   | TTL4<br>TTL4                                                      | Data Bus Read Enable<br>Data Bus Write Enable<br>Data Bus CSN - IOSN<br>Data Bus Parity Out<br>Data Bus Parity In                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BD7<br>BD6<br>BD5<br>BD4<br>BD3<br>BD2<br>BD1<br>BD0<br>RASN<br>CASN                                                       | 11<br>12<br>10<br>9<br>7<br>6<br>5<br>4<br>88<br>91                                                                                                                 | F03<br>F02<br>E01<br>E02<br>D02<br>C01<br>C02<br>B01<br>B07<br>A06                                                                                                   | 10 10 10 10 10 0 0       | 3state<br>3state<br>3state<br>3state<br>3state<br>3state<br>TTL12 | Buffer Data Bus Bit 7 Buffer Data Bus Bit 6 Buffer Data Bus Bit 5 Buffer Data Bus Bit 4 Buffer Data Bus Bit 3 Buffer Data Bus Bit 2 Buffer Data Bus Bit 1 Buffer Data Bus Bit 0 Buffer Row Address Strobe Strobe                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| - Company and the second secon | CASCAM BWEN BOEN BA7 BA6 BA5 BA4 BA3 BA2 BA1 BA0 RG RGDEL WG EAM SP IP RDI RCI WDO WCO SVCLK HS0 HS1 HS2 HS3 PWRSTN PFDETN | 92<br>13<br>98<br>93<br>3<br>8<br>16<br>20<br>24<br>32<br>38<br>100<br>64<br>99<br>75<br>73<br>74<br>83<br>84<br>94<br>95<br>71<br>76<br>77<br>78<br>79<br>72<br>82 | B06<br>F01<br>B04<br>C06<br>B02<br>D01<br>G01<br>J01<br>L01<br>M06<br>A02<br>H13<br>A03<br>C12<br>C13<br>B13<br>B09<br>A05<br>B05<br>D13<br>A13<br>B12<br>A12<br>B11 | 000 00000000 0-0000-0000 | TTL12<br>TTL8<br>TTL8                                             | Strobe Buffer CASB/ CAM/ Probe Buffer Write Enable Buffer Output Enable Buffer Address 07 or 15 Buffer Address 06 or 08 Buffer Address 05 or 13 Buffer Address 04 or 12 Buffer Address 03 or 11 Buffer Address 02 or 10 Buffer Address 01 or 09 Buffer Address 00 or 14 Read Gate Out Read Gate Out Read Gate Out Enable Address Mark Sector Pulse Index Pulse Serial Read Data In Serial Read Clock In Serial Write Data Out Serial Write Data Out Serial Write Clock Out Servo Clock In Head Select 0 Head Select 1 Head Select 2 Head Select 3 Power-On Reset Power-Fail/Detect |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RESETG<br>ESPRST<br>SCINT<br>SCRST                                                                                         | 37<br>87<br>85<br>22                                                                                                                                                | F12<br>A08<br>C08<br>K01                                                                                                                                             | -00                      | TTL4<br>TTL4                                                      | General Reset Out<br>SCSI Chip Reset<br>SCSI Chip Interrupt<br>SCSI Bus Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

(continued)

# (continued)

|                                                                                             | Pin                  | Pin No.                                |      | Pin No. |                                               |  |  |

|---------------------------------------------------------------------------------------------|----------------------|----------------------------------------|------|---------|-----------------------------------------------|--|--|

| Signal                                                                                      | Flat                 | PGA                                    | Dir. | Driver  | Function                                      |  |  |

| OSCA                                                                                        | 61                   | J13                                    | 1    |         | XTAL In (External Clock)                      |  |  |

| OSCB                                                                                        | 62                   | H11                                    | 0    | TTL4    | XTAL Out                                      |  |  |

| CLKA                                                                                        | 96                   | F11                                    | 0    | TTL4    |                                               |  |  |

| CLKC                                                                                        | 25                   | M01                                    | 0    | TTL4    |                                               |  |  |

| CLKB                                                                                        | 21                   | J02                                    | 0    | TTL4    | Clock Div-2                                   |  |  |

| TESTZ                                                                                       | 70                   | E12                                    |      |         | Test Enable                                   |  |  |

| DEBUGN                                                                                      | V 69                 | E13                                    | ı    |         | ICE Enable                                    |  |  |

| V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>DD</sub>                    | 14<br>41<br>67<br>89 | G02<br>L07<br>G13<br>C07               |      |         | +5 V<br>+5 V<br>+5 V<br>+5 V                  |  |  |

| V <sub>SS</sub><br>V <sub>SS</sub><br>V <sub>SS</sub><br>V <sub>SS</sub><br>V <sub>SS</sub> | 47<br>66             | G03<br>M07<br>M09<br>G11<br>A07<br>A04 |      |         | GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND |  |  |

# **Operating Characteristics**

| Absolute Maximum Ratings (Referenced to V <sub>SS</sub> ) |                                        |                              |      |  |  |  |  |

|-----------------------------------------------------------|----------------------------------------|------------------------------|------|--|--|--|--|

| Symbol                                                    | Parameter                              | Limits                       | Unit |  |  |  |  |

| V <sub>DD</sub>                                           | DC Supply Voltage                      | -0.3 to +7.0                 | V    |  |  |  |  |

| VI                                                        | Input Voltage                          | -0.3 to V <sub>DD</sub> +0.3 | V    |  |  |  |  |

| łj                                                        | DC Input Current                       | ±10                          | mΑ   |  |  |  |  |

| T <sub>STG</sub>                                          | Storage Temperature<br>Range (Ceramic) | -65 to +150                  | ۰c   |  |  |  |  |

| T <sub>STG</sub> Storage Temperature Range (Plastic)      |                                        | -40 to +125                  | °C   |  |  |  |  |

| Rec                                                       | ommended Operatin                      | g Conditions                 |      |  |  |  |  |

| Symbol                                                    | Parameter                              | Range                        | Unit |  |  |  |  |

| $V_{DD}$                                                  | DC Supply Voltage                      | 5.0                          | V    |  |  |  |  |

| TA Operating Ambient<br>Temperature Range                 |                                        | 0 to +70                     | ۰c   |  |  |  |  |

| RCI, RDI, SVCLK Serial Data Bit Rate                      |                                        | 0 to 25                      | MHz  |  |  |  |  |

| OSCA-OSCB                                                 | Rate                                   | 0 to 24                      | MHz  |  |  |  |  |

Storage

Technology

#### **DC Electrical Characteristics**

|        | Specified at $V_{DD} = 5V \pm 5\%$ over the temperature of 0 to $\pm 70^{\circ}$ C |     |     |     |    |                                                          |

|--------|------------------------------------------------------------------------------------|-----|-----|-----|----|----------------------------------------------------------|

| Symbol | Parameter                                                                          | -   |     | Max |    |                                                          |

| VIL    | Low Level<br>Input Voltage                                                         |     |     | 0.8 | V  |                                                          |

| ViH    | High Level<br>Input Voltage                                                        | 2.0 | 1.7 |     | v  |                                                          |

| IN     | Input Current                                                                      | -10 | +1  | 10  | μA | $V_{IN} = +5 \text{ Vdc}$                                |

| Vон    | High Level<br>Output Voltage                                                       |     |     |     |    | Maximum Current (source)                                 |

|        | Type 3state                                                                        |     | 4.5 |     | V  | IOH = -4.0  mA                                           |

|        | Type TTL2                                                                          | l · | 4.5 |     | V  | $I_{OH} = -2.0 \text{ mA}$                               |

|        | Type TTL4                                                                          |     | 4.5 |     | V  | IOH = -4.0  mA                                           |

|        | Type TTL8                                                                          |     | 4.5 |     | V  | IOH = -8.0  mA                                           |

|        | Type TTL12                                                                         | 2.4 | 4.5 |     | V  | $I_{OH} = -12.0 \text{ mA}$                              |

| VOL    | Low Level<br>Output Voltage                                                        |     |     |     |    | Maximum Current<br>(sink)                                |

|        | Type 3state                                                                        | l   | 0.2 | 0.4 | V  | $I_{OL} = 4.0 \text{ mA}$                                |

|        | Type TTL2                                                                          |     | 0.2 | 0.4 | V  | $I_{OL} = 2.0 \text{ mA}$                                |

|        | Type TTL4                                                                          |     | 0.2 | 0.4 | V  | $I_{OL} = 4.0 \text{ mA}$                                |

|        | Type TTL8                                                                          | İ   | 0.2 | 0.4 | V  | $I_{OL} = 8.0 \text{ mA}$                                |

|        | Type TTL12                                                                         | 2.4 | 0.2 | 0.4 | V  | $I_{OL} = 12.0 \text{ mA}$                               |

| loz    | Tri-State Output<br>Leakage Current                                                | -10 | ±1  | 10  | μA | $V_{OH} = V_{SS}$ or $V_{DD}$                            |

| los    | Output Short <sup>1</sup><br>Circuit Current                                       | 25  |     | 90  | mΑ | V <sub>DD</sub> = Max,<br>VO = V <sub>DD</sub>           |

|        |                                                                                    | -7  |     | -28 | mΑ | $V_{DD} = Max,$ $VO = 0V$                                |

| lDD    | Quiescent Supply<br>Current                                                        |     | 100 |     | mA | V <sub>IN</sub> = +5Vdc<br>RCI = 15 MHz<br>OSCA = 24 MHz |

| CIN    | Input Capacitance                                                                  |     | 5   |     | ρF | Any Input <sup>2</sup>                                   |

| COUT   | Output Capacitance                                                                 |     | 7   |     | ρF | Any Output <sup>2</sup>                                  |

<sup>&</sup>lt;sup>1</sup> Type TTL8 output. Output short circuit current for other outputs will scale. Not more than one output may be shorted at a time for a maximum duration of one second.

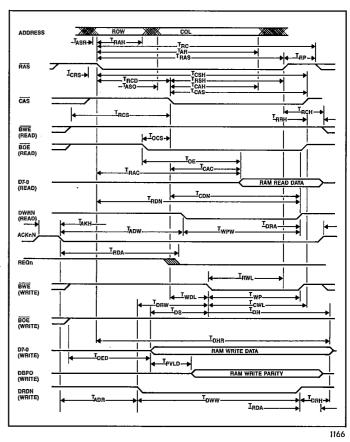

Figure 15. Buffer Memory Read and Write Operation

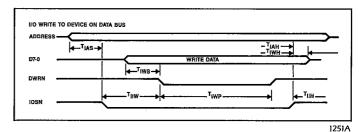

Figure 16. I/O Write to Device on Data Bus

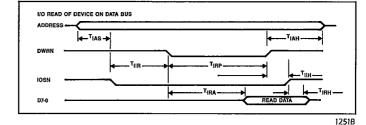

Figure 17. I/O Read of Device on Data Bus

# **AC Timing**

The following figures and the table of values that accompany them are illustrative of the MAC chip's AC timing characteristics. For definitive values, see the MAC Applications Manual or Specification.

<sup>&</sup>lt;sup>2</sup> Not applicable to bi-directional pins.

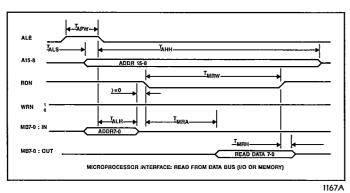

Figure 18. Microprocessor Interface: Read from Data Bus (I/O or Buffer)

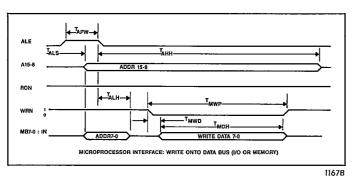

Figure 19. Microprocessor Interface: Write onto Data Bus (I/O or Buffer)

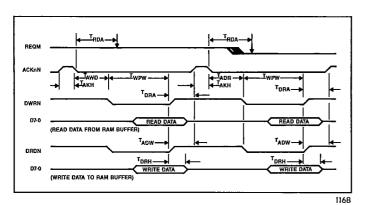

Figure 20. DMA Read/Write Handshake Timing

# **MAC Chip Buffer Control Timing**

| Oscillator Frequncy                                        | 24.00 | MHz         |  |  |  |

|------------------------------------------------------------|-------|-------------|--|--|--|

| Duty Cycle                                                 | 35/65 | Per Cent    |  |  |  |

| Cycle Time                                                 | 6     |             |  |  |  |

| Transfer Rate                                              | 4.00  | M Bytes/Sec |  |  |  |

| Conditions: 0 to 70°C, 4.75 to 5.25 V, 85 Pfd on all lines |       |             |  |  |  |

| Symbol             | Parameter                            | Min | Max   | Units |

|--------------------|--------------------------------------|-----|-------|-------|

| TADR               | ACKxN Active to DRDN Active          | 12  | 35    | Nsec  |

| TADW               | DRDN (L-H) to ACKxN (L-H) (end)      | 12  | 33    | Nsec  |

| TAHH               | High Order Address Hold <sup>1</sup> |     | 625   | Nsec  |

| TAKH               | Minimum ACKxN High                   | 9   | 29    | Nsec  |

|                    | (back to back)                       |     |       |       |

| TALH               | Address to ALE Hold                  | 17  |       | Nsec  |

| TALS               | Address to ALE Setup                 | 2   |       | Nsec  |

| TAPW               | ALE Pulse Width                      | 14  |       | Nsec  |

| $T_{AR}$           | Column Address Hold                  | 125 | 152   | Nsec  |

|                    | (reference RAS)                      |     |       |       |

| TASC               | Column Address Setup Time            | 10  | 29    | Nsec  |

| TASR               | Row Address Setup Time               | 83  | 125   | Nsec  |

| TAWD               | ACKxN (H-L) to DWRN (H-L)            | 83  | 91    | Nsec  |

| TCAC               | Access from CAS                      | 114 | 125   | Nsec  |

| TCAH               | Column Address Hold Time             | 83  | 111   | Nsec  |

| TCAS               | CAS Pulse Width                      | 120 | 125   | Nsec  |

| TCDN               | CASN (H-L) to DWRN (L-H)             | 95  | 112   | Nsec  |

| TCRS               | CAS to RAS Setup Time                | 83  | 89    | Nsec  |

| TCSH               | CAS Hold Time                        | 162 | 167   | Nsec  |

| TCWL               | BWEN to CASN Lead                    | 95  | 115   | Nsec  |

| TCYC               | OSCA Cycle Time                      | 0   | 24    | Mhz   |

| TDH                | Data in Hold (late write)            | 83  | 86    | Nsec  |

| TDHR               | Data in Hold Time (reference RAS)    | 133 | 154   | Nsec  |

| TDRA               | DWRN(L-H) to ACKxN (L-H) (end)       | 12  | 33    | Nsec  |

| TDRH               | Data Hold After DRDN (0-1)           | 0   | 12    | Nsec  |

| TDRW               | DRDN to BWEN (late write)            | 86  | 112   | Nsec  |

| TDS                | Data in Setup (late write)           | 86  | 112   | Nsec  |

| TDWW               | DRDN Pulse Width                     | 173 | 196   | Nsec  |

| TIAH               | I/O Address Hold Time                |     | 71    | Nsec  |

| TIAS               | I/O Address Setup Time               |     | 125   | Nsec  |

| l T <sub>IIH</sub> | I/O Select Off After DWRN Off        | 11  | 29    | Nsec  |

| T <sub>IIR</sub>   | I/O Select On to DRDN On             | 49  | 71    | Nsec  |

| TIIW               | I/O Strobe to DWRN                   | 95  | 115   | Nsec  |

| TIRH               | I/O Read, Read Data Hold Time        | 0   |       | Nsec  |

| T <sub>IRP</sub>   | I/O DRDN Pulse Width                 | 162 | 167.  | Nsec  |

| TIWH               | I/O Write Data Hold                  | 12  |       | Nsec  |

| T <sub>IWP</sub>   | I/O DWRN Pulse Width                 | 114 | 125   | Nsec  |

| T <sub>IWS</sub>   | I/O Write Data to DWRN               | 95  | 118   | Nsec  |

| T <sub>MRA</sub>   | Read Access (Data Bus) <sup>1</sup>  |     | 563   | Nsec  |

| TMRH               | Read Hold Data (Data Bus)            | 0   | 15    | Nsec  |

| T <sub>MRM</sub>   | RDN Width (Data Bus) <sup>1</sup>    | 625 | No    | Nsec  |

| į.                 |                                      |     | Limit |       |

| T <sub>MWD</sub>   | WRN to Write Data (Data Bus)         |     | 71    | Nsec  |

| TMWH               | Write Data Hold (Data Bus)           | -   | 563   | Nsec  |

| T <sub>MW/P</sub>  | WRN Pulse Width (Data Bus)           |     | 625   | Nsec  |

| TOCH               | OSCA/OSCB Minimum High Time          | 12  |       | Nsec  |

| TOCL               | OSCA/OSCB Minimum Low Time           | 12  |       | Nsec  |

| Tocs               | OE Setup to CASN-Out Disable         | 129 | 143   | Nsec  |

(continued)

Storage

Technology

# **MAC Chip Buffer Control Timing (continued)**

| Symbol           | Parameter                        | Min | Max | Units |

|------------------|----------------------------------|-----|-----|-------|

| TOE              | Access Time from BOEN            | 125 | 162 | Nsec  |

| TOED             | BOEN high to Data In             | 42  | 45  | Nsec  |

| TRAC             | Access from RAS                  | 144 | 167 | Nsec  |

| TRAH             | Row Address Hold Time            | 12  | 29  | Nsec  |

| T <sub>RAS</sub> | RAS Pulse Width (low)            | 137 | 158 | Nsec  |

| TRC              | Read Cycle Time                  | 250 | 250 | Nsec  |

| TRCD             | RAS to CAS Delay                 | 40  | 44  | Nsec  |

| TRCH             | Read Command Hold Time           | 95  | 108 | Nsec  |

|                  | (reference CAS)                  |     |     |       |

| T <sub>RCS</sub> | Read Command Setup Time          | 105 | 137 | Nsec  |

| TRDA             | Request Valid after PxACKN (1-0) | 102 | 154 | Nsec  |

| TRDE             | DRDN to CASN (early write)       | 81  | 83  | Nsec  |

# **MAC Chip Buffer Control Timing (continued)**

| Symbol           | Parameter                      | Min  | Max  | Units |

|------------------|--------------------------------|------|------|-------|

| TRON             | RASN (H-L) to DWRN (L-H)       | 137  | 154  | Nsec  |

| TREF             | Refresh Period                 | 2.69 | 2.77 | Nsec  |

| TRP              | RAS Precharge Time             | 91   | 112  | Nsec  |

| TRPW             | Reset Width (minimum 4 x OSCA) | 167  |      | Nsec  |

| TRRH             | Read Command Hold Time         | 125  | 131  | Nsec  |

|                  | (reference RAS)                |      |      |       |

| T <sub>RSH</sub> | RAS Hold Time                  | 99   | 120  | Nsec  |

| TRWL             | Write Command to RAS Lead      | 86   | 112  | Nsec  |

| TWDL             | CASN (H-L) to BWEN (H-L)       | 5    | 29   | Nsec  |

| TWP              | BWEN Pulse Width (late write)  | 54   | 74   | Nsec  |

| TWPW             | DWRN Pulse Width               | 114  | 125  | Nsec  |

<sup>&</sup>lt;sup>1</sup> During these cycles the microprocessor clock is generated one out of five cycles to insure specifications listed.

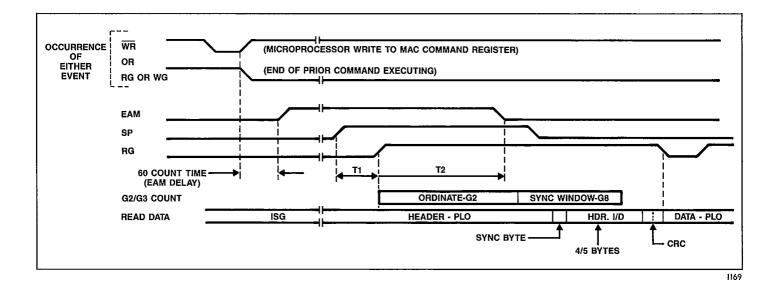

Figure 21. Hard Sector Read Timing

| Symbol | Condition                                        | Minimum | Maximum | Unit       |

|--------|--------------------------------------------------|---------|---------|------------|

| T1     | SP (Address Mark Found) to<br>Read Gate Asserted | 9       | 14      | Bit Times  |

| T2     | Read Gate Asserted to SP Off                     | 0       | G2-2    | Byte Times |

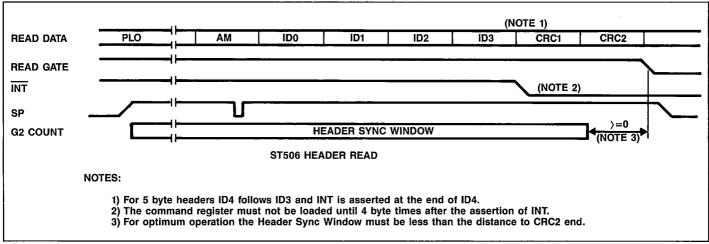

Figure 22. Soft Sector Read Timing

Figure 23. ST-506 Sector Read Timing

Storage

Technology

Figure 24. Head Select Timing