# HI-8182

# PRELIMINARY

#### ARINC 429 TRANSMITTER WITH DRIVERS AND DUAL RECEIVER

### **General Description**

The HI-8182 is identical to the HI-8282 except the DO and  $\overline{DO}$  pins are internally bonded to ARINC 429 voltage level drivers and a VEE pin is provided for the -12V supply level. For a full description of the HI-8182, excluding the bonding options, refer to the HI-8282 data sheet.

# **Functional Description**

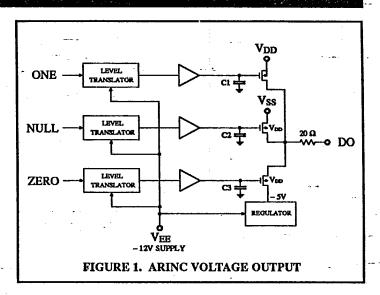

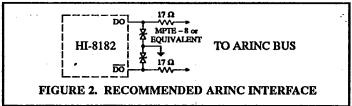

The output circuit of the HI-8182 is shown in Figure 1. A recommended interface circuit is shown in Figure 2. The logic signals, ONE, ZERO, and NULL are first translated from the  $V_{DD}$  to  $V_{SS}$  rails to the  $V_{DD}$  to  $V_{EE}$  rails. The following buffers provide the final translation to the ARINC 429 bus levels. An internal regulator provides the negative ARINC voltage level.

The maximum voltages at the output pins are 3.5 volts above  $V_{DD}$  and -10V with respect to  $V_{SS}$  for both the HI-8182 and HI-8282.

All configurations are available with the oscillator intenally disabled and not available at the package pins.

# **Absolute Maximum Ratings**

(Voltages referenced to Vss)

|   |                  |                             | 807 |                               | <br>                |                                        |       |

|---|------------------|-----------------------------|-----|-------------------------------|---------------------|----------------------------------------|-------|

|   | Supply Voltage   | V <sub>EE</sub>             |     | + 0.3V to - 15V               | Maximum Current IDD |                                        | 150mA |

| _ | Voltage at DO ar | rd $\overline{\mathrm{DO}}$ |     | $V_{DD} + 3.5V, V_{SS} - 10V$ | IEE                 | :<br>• • • • • • • • • • • • • • • • • | 150mA |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC Electrical Characteristics

$V_{\rm DD}$  = 5V ± 5%,  $V_{\rm SS}$  = 0V,  $V_{\rm EE}$  = - 12V ± 5%,  $T_{\rm A}$  = Operating Temperature Range (Unless otherwise specified)

| PARAMETER                            | SYMBOL | CONDITIONS         | MIN           | TYP   | MAX          | UNITS |

|--------------------------------------|--------|--------------------|---------------|-------|--------------|-------|

| VEE Supply Currents                  | VEE    | No Load            |               |       | 1.0          | mA    |

| DO & DO Outputs ONE Voltage          | Vouri  | No Load            | 4.75          | , -   | 5.25         | v     |

| NULL Voltage<br>ZERO Voltage         | Vouto  | No Load<br>No Load | -0.1<br>-5.25 |       | 0.1<br>-4.75 | V     |

| Short Circuit Current "ONE" I source | Iout1  | VO = 0V            | - 80          | - 125 |              | mA    |

| "ZERO" I sink                        | Iouro  | VO = 0V            | 80            | 125   |              | mA    |

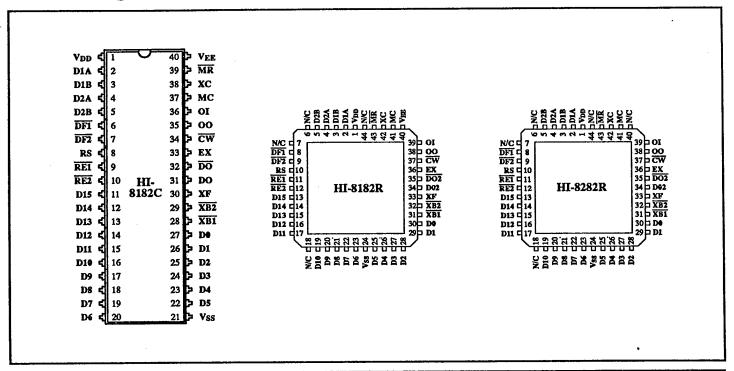

# Pin Configuration

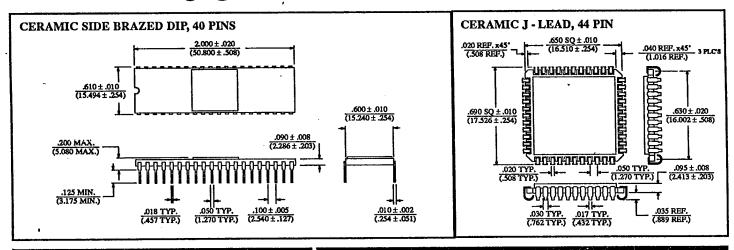

# Standard Packaging

# **Ordering Information**

HI-8182C - Ceramic DIP, 40 pins, Commercial HI-8182CM - Ceramic DIP, 40 pins, Military HI-8182R - Ceramic J-Lead, 44 pins, Commercial HI-8282R - Ceramic J-Lead, 44 pins, Commercial HI-8282RM - Ceramic J-Lead, 44 pins, Military

In addition to the above, other packaging and screening options are available upon request.

Information given by HOLT is believed to be accurate and reliable. However, HOLT reserves the right to change product specifications at any time without notice. All devices sold by HOLT are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. HOLT makes no warranty, express, statutory, implied or by description regarding the information set herein or regarding the freedom of the described devices from patent infringement.