MultiMediaCard™ 64 MByte

# **HITACHI**

ADE-203-1191A (Z) Rev. 1.0 Mar. 22, 2001

# **Description**

The Hitachi MultiMediaCard™ HB288064MM1 is a highly integrated flash memory with serial and random access capability. It is accessible via a dedicated serial interface optimized for fast and reliable data transmission. This interface allows several cards to be stacked by through connecting their peripheral contacts. The HB288064MM1 is fully compatible to a new consumer standard, called the MultiMediaCard system standard defined in the MultiMediaCard system specification [1]. The MultiMediaCard system is a new mass-storage system based on innovations in semiconductor technology. It has been developed to provide an inexpensive, mechanically robust storage medium in card form for multimedia consumer applications. MultiMediaCard allows the design of inexpensive players and drives without moving parts. A low power consumption and a wide supply voltage range favors mobile, battery-powered applications such as audio players, organizers, palmtops, electronic books, encyclopedia and dictionaries. Using very effective data compression schemes such as MPEG, the MultiMediaCard will deliver enough capacity for all kinds of multimedia data: software/programs, text, music, speech, images, video etc.

Note: MultiMediaCard<sup>TM</sup> is a trademark of Infineon AG.

### **Features**

- 64 MByte memory capacity

- On card error correction

- MultiMediaCard system standard compatibility

- System specification version 2.11 compliant

- SPI interface supported

- Block and partial block read supported (Command classes 0 and 2)

- Stream read supported (Command class 1)

- Block write and erase supported (Command classes 4 and 5)

- Group write protection (Command classes 6)

- Stream write supported (Command classes 3)

- Password data access protection

- Small erase block size of 512 bytes, tagged erase supported

- Read block size programmable between 1 and 2048 bytes

- $V_{CC} = 2.7 \text{ V}$  to 3.6 V operation voltage range ( $V_{CC} = 2.0 \text{ V}$  to 3.6 V for the interface)

- No external programming voltage required

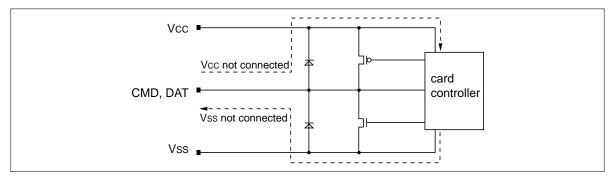

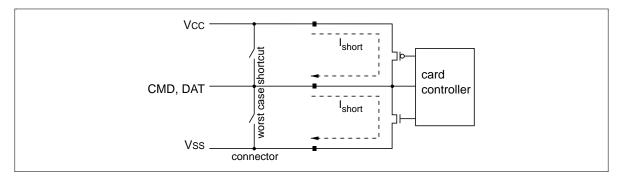

- Damage free powered card insertion and removal

- 4kV ESD protection

- · High speed serial interface with random access

- Read speed: sustained: 13.7 Mbits/s (multi-block read)

- burst (one block): 20 Mbit/s

- Write speed: sustained: 2.8 Mbit/s (multi-block write to pre-erased sectors)

- burst (one block): 20 Mbit/s

- Up to 10 stacked card (at 20 MHz,  $V_{CC} = 2.7$  to 3.6V)

- Access time:  $600 \,\mu s$  (max) (at 20 MHz,  $V_{CC} = 2.7$  to 3.6V, random byte access (Typical case))

- Low power dissipation

- High speed: 95 mW (max) (at 20 MHz,  $V_{CC} = 2.7 \text{ V}$ )

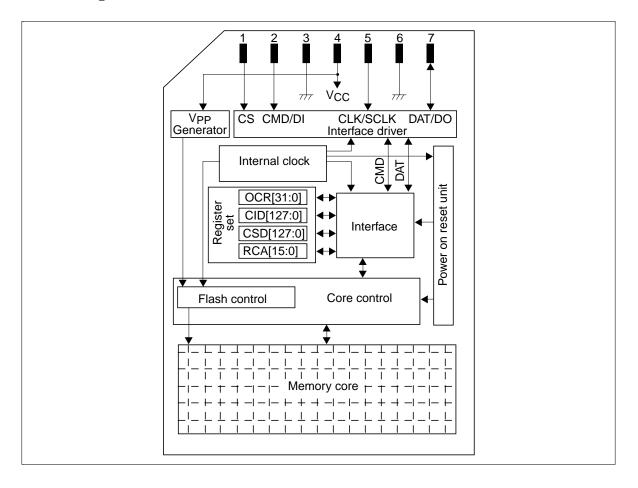

# **Block Diagram**

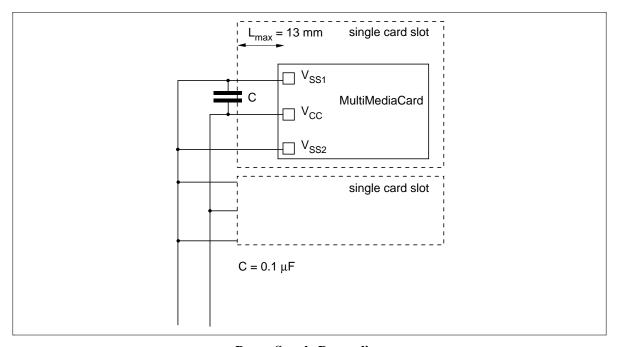

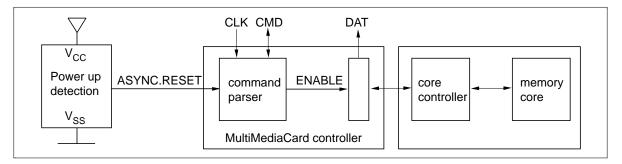

All units in the HB288064MM1 are clocked by an internal clock generator. The Interface driver unit synchronizes the DAT and CMD signals from external CLK to the internal used clock signal. The card is controlled by the three line MultiMediaCard interface containing the signals: CMD, CLK, DAT (refer to Chapter "Interfaces"). For the identification of the HB288064MM1 in a stack of MultiMediaCards a card identification register (CID) and a relative card address register (RCA) is foreseen. An additional register contains different types of operation parameters. This register is called card specific data register (CSD). The communication using the MultiMediaCard lines to access either the memory field or the registers is defined by the MultiMediaCard standard (refer to Chapter "Communication"). The card has its own power on detection unit. No additional master reset signal is required to setup the card after power on. It is protected against short circuit during insertion and removal while the MultiMediaCard system is powered up (refer to Chapter "Power Supply"). No external programming voltage supply is required. The programming voltage is generated on card. HB288064MM1 supports a second interface operation mode the SPI interface mode. The SPI mode is activated if the CS signal is asserted (negative) during the reception of the reset command (CMD0) (refer to Chapter "SPI Communication").

### Interface

The HB288064MM1 interface can operate in two different modes:

- MultiMediaCard mode

- SPI mode

Both modes are using the same pins. The default mode is the MultiMediaCard mode. The SPI mode is selected by activating (= 0) the CS signal (Pin1) and sending the CMD0.

### MultiMediaCard Mode

In the HB288064MM1, all data is transferred over a minimal number of lines:

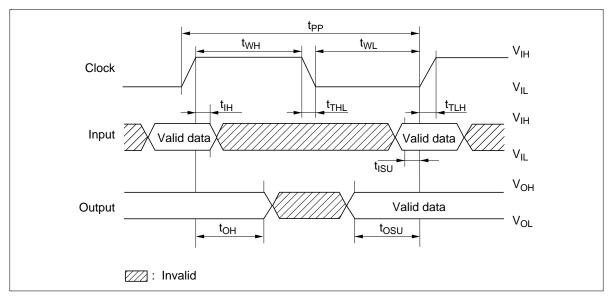

- CLK: with each cycle of this signal an one bit transfer on the command and data lines is done. The frequency may vary between zero and the maximum clock frequency. The MultiMediaCard bus master is free to generate these cycles without restrictions in the range of 0 to 20 MHz.

- CMD: is a bidirectional command channel used for card initialization and data transfer commands.

The CMD signal has two operation modes: open drain for initialization mode and push pull for fast

command transfer. Commands are sent from the MultiMediaCard bus master to the HB288064MM1

and responses vice versa.

- DAT: is a bidirectional data channel with a width of one line. The DAT signal of the HB288064MM1 operates in push pull mode.

- CS: is is pulled up with resistor (30 M $\Omega$  typ) in the MultiMediaCard. The external pull-up resistor should be recommended if the system requires.

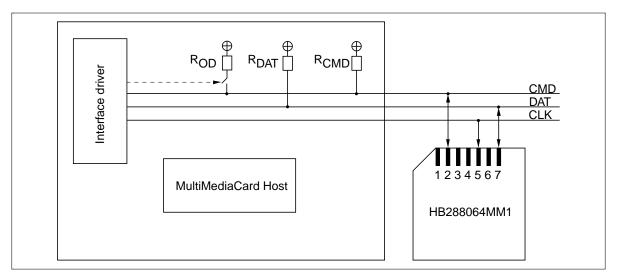

MultiMediaCard Mode Interface

All MultiMediaCards are connected directly to the lines of the MultiMediaCard bus. The following table defines the card contacts.

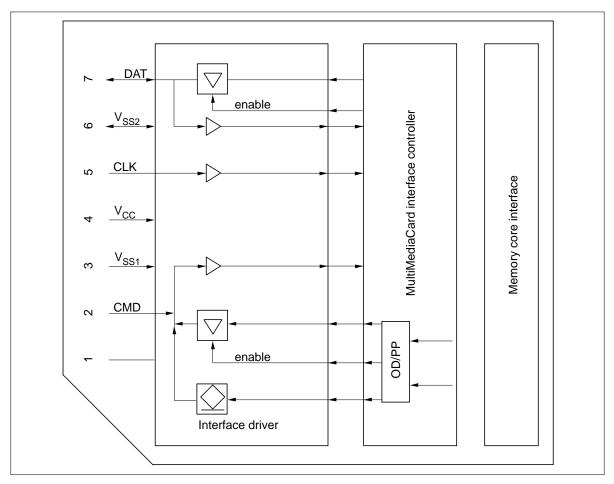

### MultiMediaCard Mode Pad Definition

| Pin No. | Name      | Type*1    | Description      |

|---------|-----------|-----------|------------------|

| 1       | RSV       | NC        | No connection    |

| 2       | CMD       | I/O/PP/OD | Command/Response |

| 3       | $V_{SS1}$ | S         | Ground           |

| 4       | $V_{cc}$  | S         | Power supply     |

| 5       | CLK       | I         | Clock            |

| 6       | $V_{SS2}$ | S         | Ground           |

| 7       | DAT       | I/O/PP    | Data             |

Note: 1. S: power supply; I: input; O: output; PP: push-pull; OD: open-drain; NC: No connection or V<sub>IH</sub>

MultiMediaCard Mode I/O-drivers

## HITACHI

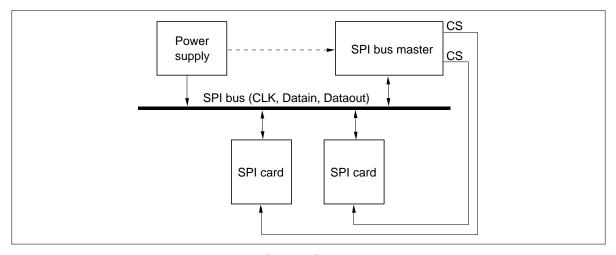

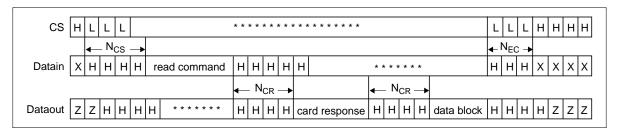

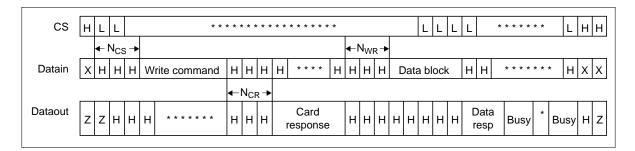

#### **SPI Mode**

The Serial Peripheral Interface (SPI) is a general-purpose synchronous serial interface originally found on certain Motorola microcontrollers. The MultiMediaCard SPI interface is compatible with SPI hosts available on the market. As any other SPI device the MultiMediaCard SPI interface consists of the following four signals:

**CS**: Host to card Chip Select signal.

CLK: Host to card clock signal

**Data in**: Host to card data signal.

Data out: Card to host data signal.

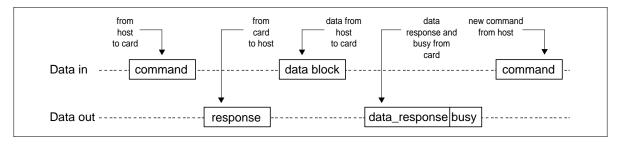

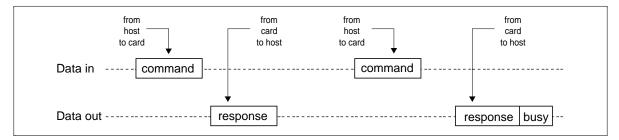

The MultiMediaCard card identification and addressing methods are replaced by a hardware Chip Select (CS) signal. There are no broadcast commands. For every command, a card (slave) is selected by asserting (active low) the CS signal (refer to Figure "SPI Bus System"). The CS signal must be continuously active for the duration of the SPI transaction (command, response and data). The only exception occurs during card programming, when the host can de-assert the CS signal without affecting the programming process. The bidirectional CMD and DAT lines are replaced by unidirectional data in and data out signals. This eliminates the ability of executing commands while data is being read or written and, therefore, makes the sequential and multi block read/write operations obsolete. Only single block read/write commands are supported by the SPI channel. The SPI interface uses the same seven signals of the standard MultiMediaCard bus (refer to Table "SPI Interface Pin Configuration").

**SPI Bus System**

# **SPI Interface Pin Configuration**

|         | MuitiMediaCard mode |           |                         | SPI mode         |      |                        |

|---------|---------------------|-----------|-------------------------|------------------|------|------------------------|

| Pin No. | Name                | Type*1    | Description             | Name             | Туре | Description            |

| 1       | RSV                 | NC        | Reserved for future use | CS               | I    | Chip select (neg true) |

| 2       | CMD                 | I/O/PP/OD | Command/Response        | DI               | Ī    | Data in                |

| 3       | V <sub>SS1</sub>    | S         | Ground                  | V <sub>ss</sub>  | S    | Ground                 |

| 4       | V <sub>CC</sub>     | S         | Power supply            | V <sub>cc</sub>  | S    | Power supply           |

| 5       | CLK                 | ļ         | Clock                   | SCLK             | Ī    | Clock                  |

| 6       | V <sub>SS2</sub>    | S         | Ground                  | V <sub>SS2</sub> | S    | Ground                 |

| 7       | DAT                 | I/O/PP    | Data                    | DO               | O/PP | Data out               |

Note: 1. S: power supply; I: input; O: output; PP: push-pull; OD: open-drain; NC: No connection or V<sub>IH</sub>

# Registers

The HB288064MM1 contains the following information registers:

| Name | Width | Туре                                                                | Description                                                                                                    |

|------|-------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| OCR  | 32    | Programmed by the manufacturer. Read only for user                  | Supported voltage range, card power up status bit                                                              |

| CID  | 128   | Programmed by the manufacturer. Read only for user                  | Card identification number, card individual number for identification.                                         |

| RCA  | 16    | Programmed during initialization, not readable                      | Relative card address, local system address of a card, dynamically assigned by the host during initialization. |

| CSD  | 128   | Programmed by the manufacturer. Partially programmable by the user. | Card specific data, information about the card operation conditions.                                           |

CID and RCA are used for identifying and addressing the HB288064MM1. The third register contains the card specific data record. This record is a set of information fields to define the operation conditions of the HB288064MM1.

For the user the CID and the OCR are read only registers. The CSD contains read only area and some of one-time or multiple programmable area by the customer or provider. They are read out by special commands (refer to Chapter "Commands"). The RCA registers are write only registers. Unlike CID and CSD, RCA looses its contents after powering down the card. Its value is reassigned in each initialization cycle. The MultiMediaCard registers usage in SPI mode is summarized in Table "MultiMediaCard Registers in SPI Mode":

## MultiMediaCard Registers in SPI Mode

| Name | Available in SPI mode | Width (Bytes) | Description                                                          |

|------|-----------------------|---------------|----------------------------------------------------------------------|

| OCR  | Yes                   | 32            | Operation condition register.                                        |

| CID  | Yes                   | 16            | Card identification data (serial number, manufacturer ID etc.)       |

| RCA  | No                    |               |                                                                      |

| CSD  | Yes                   | 16            | Card specific data, information about the card operation conditions. |

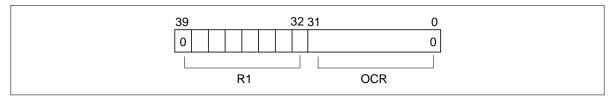

# **Operation Condition Register (OCR)**

This register indicates supported voltage range of HB288064MM1. It is a 32 bit wide register and for read only.

# **OCR Fields**

| OCR slice | slice Field                                    |        | Note |

|-----------|------------------------------------------------|--------|------|

| D31       | Card power up status bit (Busy).               | 0 or 1 |      |

| D[30-24]  | reserved                                       | 0      |      |

| D23       | 3.5 - 3.6V                                     | 1      |      |

| D22       | 3.4 - 3.5V                                     | 1      |      |

| D21       | 3.3 - 3.4V                                     | 1      |      |

| D20       | 3.2 - 3.3V                                     | 1      |      |

| D19       | 3.1 - 3.2V                                     | 1      |      |

| D18       | 3.0 - 3.1V                                     | 1      |      |

| D17       | 2.9 - 3.0V                                     | 1      |      |

| D16       | 2.8 - 2.9V                                     | 1      |      |

| D15       | 2.7 - 2.8V                                     | 1      |      |

| D14       | 2.6 - 2.7V                                     | 0      |      |

| D13       | 2.5 - 2.6V                                     | 0      |      |

| D12       | 2.4 - 2.5V                                     | 0      |      |

| D11       | 2.3 - 2.4V                                     | 0      |      |

| D10       | 2.2 - 2.3V                                     | 0      |      |

| D9        | 2.1 - 2.2V                                     | 0      |      |

| D8        | 2.0 - 2.1V                                     | 0      |      |

| D[7-0]    | Reserved by standard for under 1.8V operation. | 0      |      |

### Card Identification (CID)

This register contains the card identification information used during the card identification procedure. It is a 128 bit wide register, one-time programmable by the provider. The CID is divided into eight slices:

#### CID Fields

| Name                  | Field       | Width | CID-slice | Note |

|-----------------------|-------------|-------|-----------|------|

| Manufacturer ID       | MID         | 8     | [127:120] | 1    |

| OEM/Application ID    | OID         | 16    | [119:104] |      |

| Product name          | PNM         | 48    | [103:56]  |      |

| Product revision      | PRV         | 8     | [55:48]   |      |

| Product serial number | PSN         | 32    | [47:16]   |      |

| Manufacturing date    | MDT         | 8     | [15:8]    |      |

| CRC checksum          | CRC         | 7     | [7:1]     |      |

| not used, always 1    | <del></del> | 1     | [0:0]     |      |

Note: 1. The value of MID is 0x06.

The CID has to be error free. To ensure the correctness of the CID a CRC checksum is added to the end of the CID. The CRC checksum is computed by the following formula:

CRC Calculation:  $G(x) = x^7 + x^3 + 1$

$M(x) = CID[127]*x^{119} + ... + CID[8]*x^{0}$

$CRC[6...0] = Remainder [(M(x)*x^7)/G(x)]$

# Relative Card Address (RCA)

The 16-bit relative card address register carries the card address assigned by the host during the card identification. This address is used for the addressed host to card communication after the card identification procedure. The default value of the RCA register is 0x0001. The value 0x0000 is reserved to set all cards in Standby State with the command SELECT\_DESELECT\_CARD (CMD7). The RCA is programmed with the command SET\_RELATIVE\_ADDRESS (CMD3) during the initialization procedure. The content of this register is lost after power down. The default value is assigned when an internal reset is applied by the power up detection unit of the HB288064MM1.

# Card Specific Data (CSD)

The card specific data register describes how to access the card content. The CSD defines card operating parameters like maximum data access time, data transfer speed.

# The CSD Fields

| Name                                             | Field                  | Width | CSD-slice | Value                                | Туре      |

|--------------------------------------------------|------------------------|-------|-----------|--------------------------------------|-----------|

| CSD structure                                    | CSD_STRUCTURE          | 2     | [127:126] | 1                                    | read only |

| Spec version                                     | SPEC_VERS              | 4     | [125:122] | 2                                    | read only |

| Reserved                                         | _                      | 2     | [121:120] | 0                                    | read only |

| Data read access-time-1                          | TAAC                   | 8     | [119:112] | 0x0E (1 ms)                          | read only |

| Data read access-time-2 in CLK cycles (NSAC*100) | NSAC                   | 8     | [111:104] | 0x01 (100 cycles)                    | read only |

| Max. data transfer rate                          | TRAN_SPEED             | 8     | [103:96]  | 0x2A (20 Mbit/s)                     | read only |

| Card command classes                             | CCC                    | 12    | [95:84]   | 0x0FF (class 0, 1, 2, 3, 4, 5, 6, 7) | read only |

| Max. read data block length                      | READ_BLK_LEN           | 4     | [83:80]   | 0x9 (512 bytes)                      | read only |

| Partial blocks for read allowed                  | READ_BLK_PARTIAL       | 1     | [79:79]   | '1'*1 (Enabled)                      | read only |

| Write block misalignment                         | WRITE_BLK_MISALIG<br>N | 1     | [78:78]   | '0' (Disabled)                       | read only |

| Read block misalignment                          | READ_BLK_MISALIGN      | 1     | [77:77]   | '0' (Disabled)                       | read only |

| DSR implemented                                  | DSR_IMP                | 1     | [76:76]   | '0' (Disabled)                       | read only |

| Reserved                                         | _                      | 2     | [75:74]   | 0                                    | read only |

| Device size                                      | C_SIZE                 | 12    | [73:62]   | 0x7A7<br>(64 MByte)* <sup>2</sup>    | read only |

| Max. read current at V <sub>DD</sub> min         | VDD_R_CURR_MIN         | 3     | [61:59]   | 0x5 (35 mA)                          | read only |

| Max. read current at V <sub>DD</sub> max         | VDD_R_CURR_MAX         | 3     | [58:56]   | 0x5 (45 mA)                          | read only |

| Max. write current at V <sub>DD</sub> min        | VDD_W_CURR_MIN         | 3     | [55:53]   | 0x5 (35 mA)                          | read only |

| Max. write current at V <sub>DD</sub> max        | VDD_W_CURR_MAX         | 3     | [52:50]   | 0x5 (45 mA)                          | read only |

| Device size multiplier                           | C_SIZE_MULT            | 3     | [49:47]   | 4 (64 MByte)*3                       | read only |

| Erase sector size                                | SECTOR_SIZE            | 5     | [46:42]   | 0 (512 Bytes)                        | read only |

| Erase group size                                 | ERASE_GRP_SIZE         | 5     | [41:37]   | 0x0F (8 kByte)                       | read only |

| Name                             | Field             | Width | CSD-slice | Value           | Туре                 |

|----------------------------------|-------------------|-------|-----------|-----------------|----------------------|

| Write protect group size         | WP_GRP_SIZE       | 5     | [36:32]   | 0x01 (16 kByte) | read only            |

| Write protect group enable       | WP_GRP_ENABLE     | 1     | [31:31]   | '1'             | read only            |

| Manufacturer default ECC         | DEFAULT_ECC       | 2     | [30:29]   | 0               | read only            |

| Write speed factor               | R2W_FACTOR        | 3     | [28:26]   | 2 (4)           | read only            |

| Max. write data block length     | WRITE_BLK_LEN     | 4     | [25:22]   | 9 (512 Bytes)   | read only            |

| Partial blocks for write allowed | WRITE_BLK_PARTIAL | 1     | [21:21]   | '0'             | read only            |

| Reserved                         | _                 | 5     | [20:16]   | 0               | read only            |

| File format group                | FILE_FORMAT_GRP   | 1     | [15:15]   | ×               | read/write           |

| Copy flag (OTP)                  | COPY              | 1     | [14:14]   | ×* <sup>4</sup> | read/write           |

| Permanent write protection       | PERM_WRITE_PROTE  | 1     | [13:13]   | ×               | read/write           |

| Temporary write protection       | TMP_WRITE_PROTEC  | 1     | [12:12]   | ×               | read/write/<br>erase |

| File format                      | FILE_FORMAT       | 2     | [11:10]   | ×               | read/write           |

| ECC code                         | ECC               | 2     | [9:8]     | ×               | read/write/<br>erase |

| CRC                              | CRC               | 7     | [7:1]     | ×               | read/write/<br>erase |

| Not used, always 1               | _                 | 0     | [0:0]     | 1               | read only            |

Notes: 1. Access time from block to block within sector is 1  $\mu$ s. For blocks smaller than 256 Byte, it is 62  $\mu$ s.

- 2. This field is depended on the model. Refer to also C\_SIZE\_MULT

- 3. This field is depended on the model. Refer to also C\_SIZE

- 4. × means user programmable

Some of the CSD fields are one-time or multiple programmable by the customer or provider. All other field values are fixed. The following section describes the CSD fields and their values for the HB288064MM1:

### • CSD\_STRUCTURE

### **CSD Register Structure**

| CSD_STRUCTURE | CSD register structure |  |  |

|---------------|------------------------|--|--|

| '01'          | CSD version No. 1.1    |  |  |

The CSD version of the HB288064MM1 is related to the "MultiMediaCard system specification, Version 2.11". The parameter CSD\_STRUCTURE has permanently the value 1.

### SPEC\_VERS

Defines the Spec version supported by the card. It includes the commands set definition and the definition of the card responses. The card identification procedure is compatible for all spec versions!

#### **SPEC Version**

| SPEC_VERS | System specification version number |  |  |

|-----------|-------------------------------------|--|--|

| '0010'    | System specification version 2.11   |  |  |

The Spec version of the HB288064MM1 is related to the "MultiMediaCard system specification, Version 2.11". The parameter SPEC\_VERS has permanently the value 2.

#### TAAC

Defines the asynchronous data access time:

### **TAAC Access Time Definition**

| TAAC bit | Description   | Values                                                                                                                                                     |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0      | time exponent | $0 = 1 \text{ ns}, 1 = 10 \text{ ns}, 2 = 100 \text{ ns}, 3 = 1 \mu\text{s}, 4 = 10 \mu\text{s}, 5 = 100 \mu\text{s}, 6 = 1 \text{ ms}, 7 = 10 \text{ ms}$ |

| 6:3      | time mantissa | 0 = reserved, 1 = 1.0, 2 = 1.2, 3 = 1.3, 4 = 1.5,<br>5 = 2.0, 6 = 2.5, 7 = 3.0, 8 = 3.5, 9 = 4.0, A = 4.5,<br>B = 5.0, C = 5.5, D = 6.0, E = 7.0, F = 8.0  |

| 7        | reserved      | always '0'                                                                                                                                                 |

The value for the asynchronous delay for the HB288064MM1 is 1 ms. The coded TAAC value is 0x0E (= 1 ms). For more details refer to Chapter "Operating Characteristics".

#### NSAC

Defines the worst case for the synchronous data access time.  $N_{AC}$  is defined as 100\*NSAC clock cycles, where NSAC presents a binary value. Max. value for the data access time  $N_{AC}$  is 25.6k clock cycles. The total access time is the sum of both TAAC and  $N_{AC}$ \*clock period. The value of NSAC for the HB288064MM1 is 0x01 (100 cycles). For more details refer to Chapter "Operating Characteristics".

### TRAN SPEED

The following table defines the maximum data transfer rate TRAN\_SPEED:

#### **Maximum Data Transfer Rate Definition**

| TRAN_SPEED bit | Description                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0            | transfer rate exponent $0 = 100$ kbit/s, $1 = 1$ Mbit/s, $2 = 10$ Mbit/s, $3 = 100$ Mbit/s, $47 = reserved$                                                                                                                       |

| 6:3            | time mantissa $0x0$ = reserved, $0x1$ = 1.0, $0x2$ = 1.2, $0x3$ = 1.3, $0x4$ = 1.5, $0x5$ = 2.0, $0x6$ = 2.5, $0x7$ = 3.0, $0x8$ = 3.5, $0x9$ = 4.0, $0xA$ = 4.5, $0xB$ = 5.0, $0xC$ = 5.5, $0xD$ = 6.0, $0xE$ = 7.0, $0xF$ = 8.0 |

| 7              | reserved = '0'                                                                                                                                                                                                                    |

The HB288064MM1 supports a transfer rate between 0 and 20 Mbit/s. The parameter TRAN\_SPEED is 0x2A.

### • CCC

The MultiMediaCard command set is divided into subsets (command classes). The card command class register CCC defines which command classes are supported by this card. A set CCC bit means that the corresponding command class is supported. For command class definition refer to Table "HB288064MM1 Command Classes".

### **Supported Card Command Classes**

| CCC bit | Supported card command classes |

|---------|--------------------------------|

| 0       | class0                         |

| 1       | class1                         |

|         |                                |

| 11      | class11                        |

The HB288064MM1 supports the command classes 0, 1, 2, 3, 4, 5, 6 and 7. The parameter CCC is permanently assigned to the value 0x0FF.

#### READ BLK LEN

The data block length is computed as 2<sup>READ\_BLK\_LEN</sup>.

### Data Block Length

| READ_BLK_LEN | Block length          | Remark |

|--------------|-----------------------|--------|

| 0            | 2° = 1 byte           |        |

| 1            | $2^1 = 2$ bytes       |        |

|              |                       |        |

| 11           | $2^{11} = 2048$ bytes |        |

| 12–15        | reserved              |        |

The block length might therefore be in the range 1, 2, 4...2048 bytes. This parameter defines the block length if READ\_BLK\_PARTIAL is not set. If READ\_BLK\_PARTIAL is set this parameter contains the maximum allowed value of the block length in bytes. All block lengths between one and this value are permitted. The actual block size is programmed by the command SET\_BLOCKLEN (CMD16). The HB288064MM1 supports block lengths from 1 byte up to 2048 bytes. The parameter READ\_BLK\_LEN is permanently assigned to the value 0x9.

### READ\_BLK\_PARTIAL

READ\_BLK\_PARTIAL defines whether partial block sizes can be used in block read and block write commands. READ\_BLK\_PARTIAL = 0 means that only the block size defined by READ\_BLK\_LEN can be used for block-oriented data transfers. READ\_BLK\_PARTIAL = 1 means that smaller blocks can be used as well. The minimum block size will be equal to minimum addressable unit (one byte). The HB288064MM1 supports partial block read. The parameter READ\_BLK\_PARTIAL is permanently assigned to the value '1'.

## WRITE\_BLK\_MISALIGN

Defines if the data block to be written by one command can be spread over more than one physical blocks of the memory device. The size of the memory block is defined in WRITE\_BLK\_LEN. WRITE\_BLK\_MISALIGN is permanently assigned to the value '0', signalling that crossing physical block boundaries is not allowed.

### • READ BLK MISALIGN

Defines if the data block to be read by one command can be spread over more than one physical block of the memory device. The size of the data block is defined in READ\_BLK\_LEN. READ\_BLK\_MISALIGN = 0 signals that crossing physical block boundaries is not allowed. READ\_BLK\_MISALIGN = 1 signals that crossing physical block boundaries is allowed. The HB288064MM1 does not support read block operations with boundary crossing. The parameter READ\_BLK\_MISALIGN is permanently assigned to the value '0'.

#### DSR IMP

Defines if the configurable driver stage option is integrated on the card or not. If implemented a driver stage register (DSR) must be implemented also.

### **DSR** Implementation

| DSR_IMP | DSR type             |  |  |  |  |  |

|---------|----------------------|--|--|--|--|--|

| 0       | 0 no DSR implemented |  |  |  |  |  |

| 1       | DSR implemented      |  |  |  |  |  |

The HB288064MM1 output drivers are not configurable. The parameter DSR\_IMP is permanently assigned to the value '0'.

### • C\_SIZE

This parameter is used to compute the card capacity. The memory capacity of the card is computed from the entries C\_SIZE, C\_SIZE\_MULT and READ\_BLK\_LEN as follows:

memory capacity = BLOCKNR\*BLOCK\_LEN

#### Where

$$\begin{split} & \text{BLOCKNR} = (\text{C\_SIZE+1})*\text{MULT} \\ & \text{MULT} = 2^{\text{C\_SIZE\_MULT+2}} \ (\text{C\_SIZE\_MULT} < 8) \\ & \text{BLOCK\_LEN} = 2^{\text{READ\_BLK\_LEN}}, \ (\text{READ\_BLK\_LEN} < 12) \end{split}$$

Therefore, the maximal capacity which can be coded is 4096\*512\*512 = 1 GBytes.

Example: A 64 MBytes card with BLOCK\_LEN = 512 can be coded with C\_SIZE\_MULT = 4 and C\_SIZE = 1959.

The card capacity is 64 MBytes.

The value of the parameter C SIZE used in the formula above for the HB288064MM1 is 0x7A7.

## • VDD\_R\_CURR\_MIN, VDD\_W\_CURR\_MIN

The maximum supply current at the minimum supply voltage  $V_{CC}$  (2.7 V) is coded as follows:

# Maximum Supply Current Consumption at $V_{CC} = 2.7 \text{ V}$

| VDD_R_CURR_MIN VDD_W_CURR_MIN | Code for current consumption at 2.7 V                                                  |

|-------------------------------|----------------------------------------------------------------------------------------|

| 2:0                           | 0 = 0.5 mA; 1 = 1 mA; 2 = 5 mA; 3 = 10 mA; 4 = 25 mA; 5 = 35 mA; 6 = 60 mA; 7 = 100 mA |

The parameter VDD\_R\_CURR\_MIN and VDD\_W\_CURR\_MIN are permanently assigned to the value 5 (35 mA).

## • VDD\_R\_CURR\_MAX, VDD\_W\_CURR\_MAX

The maximum supply current at the maximum supply voltage V<sub>CC</sub> (3.6 V) is coded as follows:

# Maximum Supply Current Consumption at $V_{CC} = 3.6 \text{ V}$

| VDD_R_CURR_MAX<br>VDD_W_CURR_MAX | Code for current consumption at 3.6 V                                                 |

|----------------------------------|---------------------------------------------------------------------------------------|

| 2:0                              | 0 = 1 mA; 1 = 5 mA; 2 = 10 mA; 3 = 25 mA; 4 = 35 mA; 5 = 45 mA; 6 = 80 mA; 7 = 200 mA |

The parameter VDD\_R\_CURR\_MAX and VDD\_W\_CURR\_MAX are permanently assigned to the value 5 (45 mA). For more details refer to Chapter "Characteristics".

#### C SIZE MULT

This parameter is used for coding a factor MULT for computing the total device size (refer to "C\_SIZE"). The factor MULT is defined as 2<sup>C\_SIZE\_MULT+2</sup>.

### **Multiply Factor for the Device Size**

| C_SIZE_MULT | MULT                 | Remark |

|-------------|----------------------|--------|

| 0           | $2^2 = 4$            |        |

| 1           | $2^3 = 8$            |        |

| 2           | 2 <sup>4</sup> = 16  |        |

| 3           | 2 <sup>5</sup> = 32  |        |

| 4           | $2^6 = 64$           |        |

| 5           | $2^7 = 128$          |        |

| 6           | 2 <sup>8</sup> = 256 |        |

| 7           | 2 <sup>9</sup> = 512 |        |

The card capacity is 64 MBytes. The value of the parameter C\_SIZE\_MULT used in the formula to calculate the card capacity (refer to parameter "C\_SIZE") for the HB288064MM1 is 4 (multiplier = 64).

### • SECTOR SIZE

The size of an erasable or write protection sector. The content of this register is a binary coded value defining the number of write blocks (refer to "WRITE\_BLK\_LEN") of a sector. The sector size of the HB288064MM1 is set to 0 (= one write block = 512 bytes).

### • ERASE\_GROUP\_SIZE

The size of an erasable group. The content of this register is a binary coded value defining the number of sectors (refer to "SECTOR\_SIZE") of a group. This parameters value is 15 which means a group size of (15+1)\*512 bytes = 8 kByte.

#### WP GRP SIZE

The size of a write protection group. The content of this register is a binary coded value defining the number of sectors (refer to "SECTOR\_SIZE") of a group. This parameters value is 1 which means a group size of  $(1+1)*(ERASE\ GROUP\ SIZE) = 16\ kByte$ .

### • WP\_GRP\_ENABLE

The value is set to '1', meaning group write protection is enabled.

#### DEFAULT ECC

Set by the card manufacturer and defines the ECC code which is recommended to use (e.g. the device is tested for). The value is set to '0', indicating that no designated ECC is recommended.

### R2W\_FACTOR

Defines the typical block program time as a multiple of the read access time. The following table defines the field format.

### R2W\_FACTOR

| R2W_FACTOR | Multiples of read access time  |

|------------|--------------------------------|

| 0          | 1                              |

| 1          | 2 (write half as fast as read) |

| 2          | 4                              |

| 3          | 8                              |

| 4          | 16                             |

| 5          | 32                             |

| 6, 7       | reserved                       |

This parameter value is 2 for the HB288064MM1.

### • WRITE\_BLK\_LEN

The data block length is computed as 2 WRITE\_BLK\_LEN.

### **Data Block Length**

| WRITE_BLK_LEN | Block length             | Remark |

|---------------|--------------------------|--------|

| 0             | $2^0 = 1$ byte           |        |

| 1             | 2 <sup>1</sup> = 2 bytes |        |

|               |                          |        |

| 11            | $2^{11} = 2048$ bytes    |        |

| 12–15         | reserved                 |        |

The block length might therefore be in the range 1, 2, 4...2048 bytes. This parameter defines the block length if WRITE\_BLK\_PARTIAL is not set. If WRITE\_BLK\_PARTIAL is set this parameter contains the maximum allowed value of the block length in bytes. All block lengths between one and this value are permitted. The actual block size is programmed by the command SET\_BLOCKLEN (CMD16). The HB288064MM1 supports blocks with the length 512 bytes. The parameter WRITE\_BLK\_LEN is permanently assigned to the value 0x9.

#### HITACHI

### WRITE\_BLK\_PARTIAL

WRITE\_BLK\_PARTIAL defines whether partial block sizes can be used in block read and block write commands. WRITE\_BLK\_PARTIAL = 0 means that only the block size defined by WRITE\_BLK\_LEN can be used for block-oriented data transfers. WRITE\_BLK\_PARTIAL = 1 means that smaller blocks can be used as well. The minimum block size will be equal to minimum addressable unit (one byte). The HB288064MM1 supports no partial block write. The parameter WRITE\_BLK\_PARTIAL is permanently assigned to the value '0'.

#### FILE FORMAT GRP

Indicates the selected group of file formats. The default value is '0'. The usage of this field is shown in table "File\_Formats".

#### COPY

Defines if the contents are an original (COPY = "0") or a copy (= "1"). The COPY bit is a one time programmable bit, being set by the customer. The default value is '0'.

### PERM\_WRITE\_PROTECT

Permanently protects the whole card content against overwriting or erasing (all write and erase commands for this card is permanently disabled). This parameter is one-time programmable by the customer. The default value is '0' (not protected).

### • TMP\_WRITE\_PROTECT

Temporarily protects the whole card content from being overwritten or erased (all write and erase commands for this card are temporarily disabled). This parameter is programmable by the customer. The default value is '0' (not protected).

#### • FILE FORMAT

Indicates the file format on the card. This field is read-only for ROM. The default value is '0'. The following formats are defined:

#### **File Formats**

#### FILE\_FORMAT\_GRP FILE\_FORMAT Type

| 0 | 0          | Hard disk-like file system with partition table                  |

|---|------------|------------------------------------------------------------------|

| 0 | 1          | DOS FAT (floppy-like) with boot sector only (no partition table) |

| 0 | 2          | Universal File Format                                            |

| 0 | 3          | Others/Unknown                                                   |

| 1 | 0, 1, 2, 3 | Reserved                                                         |

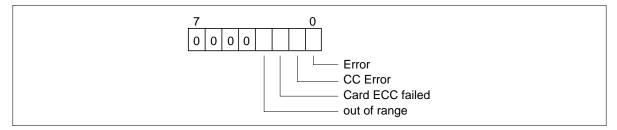

#### ECC

Defines the ECC code that was used for storing data on the card. This field is used by the host (or application) to decode the user data. The following table defines the field format.

# **ECC Type**

| ECC | ECC type       | Maximum number of correctable bits |

|-----|----------------|------------------------------------|

| 0   | none (default) | none                               |

| 1   | BCH (542,512)  | 3                                  |

| 2–3 | reserved       | _                                  |

The content provider or customer defines which kind of error correction may be used to protect the contents of the HB288064MM1. This value is programmable.

#### CRC

The CRC register contains the check sum for the CSD content. The check sum is computed by the following formulas: Generator polynomial:

$$G(x) = x^7 + x^3 + 1$$

$M(x) = CSD[127]*x^{119} + ... + CSD[8]*x^0 CRC[6...0] = Remainder [(M(x)*x^7)/G(x)]$

The user has to recalculate a new CRC after defining a new CSD.

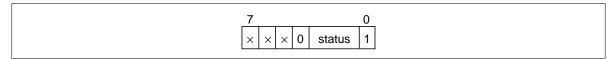

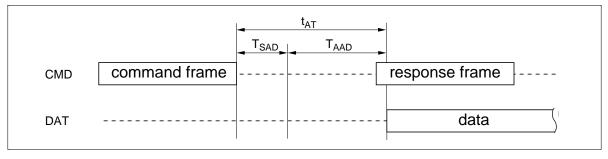

### MultiMediaCard Communication

All communication between host and cards is controlled by the host (master). The host sends commands and, depending on the command, receives a corresponding response from the selected card. In this chapter the commands to control the HB288064MM1, the card responses and the contents of the status and error field included in the responses, are defined.

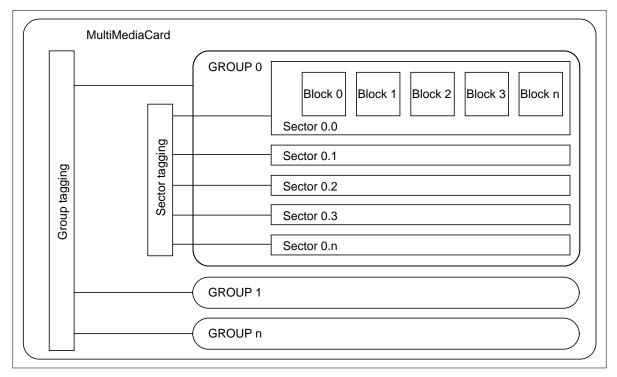

## **Memory Array Partitioning**

The basic unit of data transfer to/from the MultiMediaCard is one byte. All data transfer operations which require a block size always define block lengths as integer multiples of bytes. Some special functions need other partition granularity. For block-oriented commands, the following definition is used:

Block: is the unit which is related to the block-oriented read and write commands. Its size is the

number of bytes which will be transferred when one block command is sent by the host. The size of a

block is either programmable or fixed. The information about allowed block sizes and the

programmability is stored in the CSD.

For devices which have erasable memory cells, special erase commands are defined. The granularity of the erasable units is in general not the same as for the block-oriented commands:

- Sector: is the unit which is related to the erase commands. Its size is the number of blocks which will be erased in one portion. The size of a sector is fixed for each device. The information about the sector size (in blocks) is stored in the CSD.

- Group: is a number of sectors. Its size is the number of consecutive sectors which will be erased at once. The size of a group is fixed for each device. The information about the size is stored in the CSD.

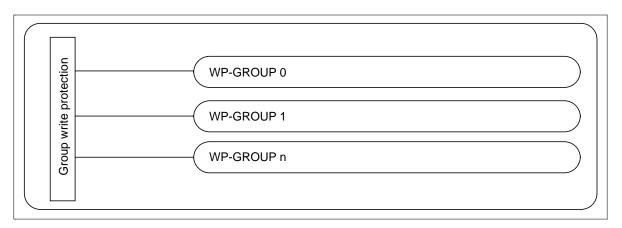

For devices which include a write protection:

• WP-Group: is the minimal unit which may have individual write protection. Its size is the number of sectors which will be write protected by one bit. The size of a WP-group is fixed for each device. The information about the size is stored in the CSD.

Each erasable unit (group and sector) has a special "tag" bit. This bit may be set or cleared by special commands to tag the unit. All tagged units will be erased in parallel by one erase command following a number of tag commands. All tag bits are cleared by each command except a tag or untag command. Therefore, immediately after a sequence of tag commands an erase command has to be sent by the host. Commands others than tagging or erasing abort a tag-erase cycle irregularly.

**Erase Tagging Hierarchy**

Each WP-group may have an additional write protection bit. The write protection bits are programmable via special commands (refer to Chapter "Commands"). The information about the availability is stored in the CSD.

**Write Protection**

#### Commands

The command set of the MultiMediaCard system is divided into classes corresponding to the type of card (see also [1]). The HB288064MM1 supports the following command classes:

### HB288064MM1 Command Classes (Class 0 to Class 2)

|                          |                   | Supported commands |   |   |   |   |   |   |    |    |    |    |    |    |    |    |

|--------------------------|-------------------|--------------------|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| Card command class (CCC) | Class description | 0                  | 1 | 2 | 3 | 4 | 7 | 9 | 10 | 11 | 12 | 13 | 15 | 16 | 17 | 18 |

| Class 0                  | basic             | +                  | + | + | + | + | + | + | +  |    | +  | +  | +  |    |    |    |

| Class 1                  | stream read       |                    |   |   |   |   |   |   |    | +  |    |    |    |    |    |    |

| Class 2                  | block read        |                    |   |   |   |   |   |   |    |    |    |    |    | +  | +  | +  |

### HB288064MM1 Command Classes (Class 3 to Class 8)

|                          |                   | Supported commands |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|--------------------------|-------------------|--------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Card command class (CCC) | Class description | 20                 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 42 |

| Class 3                  | stream write      | +                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Class 4                  | block write       |                    | +  | +  | +  | +  |    |    |    |    |    |    |    |    |    |    |    |

| Class 5                  | erase             |                    |    |    |    |    |    |    |    | +  | +  | +  | +  | +  | +  | +  |    |

| Class 6                  | write protection  |                    |    |    |    |    | +  | +  | +  |    |    |    |    |    |    |    |    |

| Class 7                  | lock card         |                    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | +  |

Class 0 is mandatory and supported by all cards. It represents the card identification and initialization commands, which are intended to handle different cards and card types on the same bus lines. The Card Command Class (CCC) is coded in the card specific data register of each card, so that the host knows how to access the card. There are four kinds of commands defined on the MultiMediaCard bus:

- broadcast commands (bc) sent on CMD line, no response

- broadcast commands with response (bcr) sent on CMD line, response (all cards simultaneously) on CMD line

- addressed (point-to-point) commands (ac) sent on CMD line, response on CMD line

- addressed (point-to-point) data transfer commands (adtc) sent on CMD line, response on CMD line, data transfer on DAT line

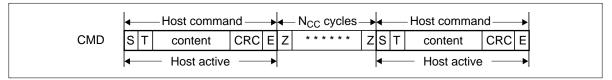

The command transmission always starts with the MSB. Each command starts with a start bit and ends with a CRC command protection field followed by an end bit. The length of each command frame is fixed to 48 bits  $(2.4 \,\mu s)$  at  $20 \,MHz$ :

| 0         | 1    | bit5bit0 | bit31bit0 | bit6bit0 | 1       |

|-----------|------|----------|-----------|----------|---------|

| start bit | host | command  | argument  | CRC*1    | end bit |

Note: 1. (Cyclic Redundancy Check)

The start bit is always '0' in command frames (sent from host to MultiMediaCard). The host bit is always '1' for commands. The command field contains the binary coded command number. The argument depends on the command (refer to Table "Basic Commands (class 0) and Table "Block-Oriented Read Commands (class 2)"). The CRC field is defined in Chapter "Cyclic Redundancy Check (CRC)". The HB288064MM1 supports the following MultiMediaCard commands:

## Read, Write and Erase Time-out Conditions

The times after which a time-out condition for read/write/erase operations occurs are (card independent) 10 times longer than the access/program times for these operations given below. A card shall complete the command within this time period, or give up and return an error message. If the host does not get a response within the defined time-out it should assume the card is not going to respond anymore and try to recover (e.g. reset the card, power cycle, reject, etc.). The typical access and program times are defined as follows:

#### Read

The read access time is defined as the sum of the two times given by the CSD parameters TAAC and NSAC (refer to Table "Card Specific Data (CSD)"). These card parameters define the typical delay between the end bit of the read command and the start bit of the data block. This number is card dependent and should be used by the host to calculate throughput and the maximal frequency for stream read.

#### Write

The R2W\_FACTOR field in the CSD is used to calculate the typical block program time obtained by multiplying the read access time by this factor. It applies to all write/erase commands (e.g. SET(CLEAR)\_WRITE\_PROTECT, PROGRAM\_CSD(CID) and the block write commands). It should be used by the host to calculate throughput and the maximal frequency for stream write.

#### Erase

The duration of an erase command will be (order of magnitude) the number of sectors to be erased multiplied by the block write delay.

Basic Commands (class 0) and Read Stream Command (class 1)

| CMD<br>index | Туре | Argument                         | Resp                                  | Abbreviation             | Command description                                                                                                                                                                                                                                |

|--------------|------|----------------------------------|---------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD0         | bc   | [31:0] stuff bits                |                                       | GO_IDLE_STATE            | resets all cards to Idle State                                                                                                                                                                                                                     |

| CMD1         | bcr  | [31:0] OCR<br>without busy       | R3                                    | SEND_OP_COND             | checks for cards not supporting the full range of 2.0 V to 3.6 V. After receiving CMD1 the card sends an R3 response (refer to Chapter "Responses").                                                                                               |

| CMD2         | bcr  | [31:0] stuff bits                | R2                                    | ALL_SEND_CID             | asks all cards in ready state to send their CID*1 numbers on CMD-line                                                                                                                                                                              |

| CMD3         | ac   | [31:16] RCA<br>[15:0] stuff bits | R1                                    | SET_RELATIVE_A<br>DDR    | assigns relative address to the card in identification state.                                                                                                                                                                                      |

| CMD4         | bc   | [31:16] DSR<br>[15:0] stuff bits |                                       | SET_DSR                  | programs the DSR of all cards in stand-by state.                                                                                                                                                                                                   |

| CMD7         | ac   | [31:16] RCA<br>[15:0] stuff bits | R1b (only<br>the<br>selected<br>card) | SELECT/<br>DESELECT_CARD | command toggles a card between the standby and transfer states or between the programming and disconnect state. In both cases the card is selected by its own relative address while deselecting the prior selected card. Address 0 deselects all. |

| CMD9         | ac   | [31:16] RCA<br>[15:0] stuff bits | R2                                    | SEND_CSD                 | asks the addressed card to send its card-specific data (CSD)*2 on CMD-line.                                                                                                                                                                        |

| CMD10        | ac   | [31:16] RCA<br>[15:0] stuff bits | R2                                    | SEND_CID                 | asks the addressed card to send its card identification (CID) on CMD- line.                                                                                                                                                                        |

| CMD11        | adtc | [31:0] data<br>address           | R1                                    | READ_DAT_UNTIL<br>_STOP  | reads data stream from the card, starting at the given address, until a STOP_TRANSMISSION follows.                                                                                                                                                 |

| CMD12        | ac   | [31:0] stuff bits                | R1b*3                                 | STOP_TRANSMIS<br>SION    | forces the card to stop transmission                                                                                                                                                                                                               |

| CMD13        | ac   | [31:16] RCA<br>[15:0] stuff bits | R1                                    | SEND_STATUS              | Asks the addressed card to send its status register.                                                                                                                                                                                               |

| CMD15        | ac   | [31:16] RCA<br>[15:0] stuff bits | _                                     | GO_INACTIVE_ST<br>ATE    | Sets the card to inactive state in order to protect the card stack against communications breakdowns.                                                                                                                                              |

Notes: 1. CID register consists of 128 bits (starting with MSB, it is preceded by an additional start bit, ends with an end bit)

<sup>2.</sup> CSD register consists of 128 bits (starting with MSB, it is preceded by an additional start bit, ends with an end bit)

<sup>3.</sup> This command is indicating the busy status of the MultiMediaCard via the data channel.

### **Block-Oriented Read Commands** (class 2)

| CMD<br>index | Туре | Argument               | Resp | Abbreviation            | Command description                                                                    |

|--------------|------|------------------------|------|-------------------------|----------------------------------------------------------------------------------------|

| CMD16        | ac   | [31:0] block<br>length | R1   | SET_BLOCKLEN            | Selects a block length (in bytes) for all following block commands (read and write).*1 |

| CMD17        | adtc | [31:0] data<br>address | R1   | READ_SINGLE_BL<br>OCK   | Reads a block of the size selected by the SET_BLOCKLEN command.*2                      |

| CMD18        | adtc | [31:0] data<br>address | R1   | READ_MULTIPLE_<br>BLOCK | Continuously send blocks of data until interrupted by a stop.                          |

Notes: 1. The default block length is as specified in the CSD.

2. The data transferred must not cross a physical block boundary unless RD\_BLK\_MISALIGN is set in the CSD.

## **Stream Write Command** (class 3)

| CMD<br>index | Туре | Argument               | Resp | Abbreviation             | Command description                                                                                 |

|--------------|------|------------------------|------|--------------------------|-----------------------------------------------------------------------------------------------------|

| CMD20        | adtc | [31:0] data<br>address | R1   | WRITE_DAT_<br>UNTIL_STOP | writes data stream from the host, starting at the given address, until a STOP_TRANSMISSION follows. |

# **Block-Oriented Write Commands** (class 4)

| CMD<br>index | Туре | Argument               | Resp | Abbreviation              | Command description                                                                                                                                                                                                                                |

|--------------|------|------------------------|------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD24        | adtc | [31:0] data<br>address | R1   | WRITE_BLOCK               | Writes a block of the size selected by the SET_BLOCKLEN command.*1                                                                                                                                                                                 |

| CMD25        | adtc | [31:0] data<br>address | R1   | WRITE_MULTIPLE<br>_ BLOCK | Continuously writes blocks of data until a STOP_TRANSMISSION follows.                                                                                                                                                                              |

| CMD26        | adtc | [31:0] stuff bits      | R1   | PROGRAM_CID               | Programming of the card identification register. This command is only done once per MultiMediaCard card. The card has some hardware to prevent this operation after the first programming. Normally this command is reserved for the manufacturer. |

| CMD27        | adtc | [31:0] stuff bits      | R1   | PROGRAM_CSD               | Programming of the programmable bits of the CSD.                                                                                                                                                                                                   |

Note: 1. The data transferred must not cross a physical block boundary unless WRITE\_BLK\_MISALIGN is set in the CSD.

### **Erase Commands** (class 5)

| CMD<br>index | Туре | Argument               | Resp | Abbreviation              | Command description                                                                                                                                                   |

|--------------|------|------------------------|------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD32        | ac   | [31:0] data<br>address | R1   | TAG_SECTOR_ST<br>ART      | Sets the address of the first sector of the erase group.                                                                                                              |

| CMD33        | ac   | [31:0] data<br>address | R1   | TAG_SECTOR_EN D           | Sets the address of the last sector in a continuous range within the selected erase group to be selected for erase, or the address of a single sector to be selected. |

| CMD34        | ac   | [31:0] data<br>address | R1   | UNTAG_SECTOR              | Removes one previously selected sector from the erase selection.                                                                                                      |

| CMD35        | ac   | [31:0] data<br>address | R1   | TAG_ERASE_GRO<br>UP_START | Sets the address of the first erase group within a range to be selected for erase                                                                                     |

| CMD36        | ac   | [31:0] data<br>address | R1   | TAG_ERASE_GRO<br>UP_END   | Sets the address of the last erase group within a continuous range to be selected for erase                                                                           |

| CMD37        | ac   | [31:0] data<br>address | R1   | UNTAG_ERASE_G<br>ROUP     | Removes one previously selected erase group from the erase selection                                                                                                  |

| CMD38        | ac   | [31:0] stuff bits      | R1b  | ERASE                     | Erases all previously selected sectors                                                                                                                                |

# Write Protection Commands (class 6)

| CMD<br>index | Туре | Argument                                | Resp | Abbreviation        | Command description                                                                                                                                                                                 |

|--------------|------|-----------------------------------------|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD28        | ac   | [31:0] data<br>address                  | R1b  | SET_WRITE_PROT      | if the card has write protection features, this command sets the write protection bit of the addressed group. The properties of write protection are coded in the card specific data (WP_GRP_SIZE). |

| CMD29        | ac   | [31:0] data<br>address                  | R1b  | CLR_WRITE_PROT      | if the card provides write protection features, this command clears the write protection bit of the addressed group.                                                                                |

| CMD30        | adtc | [31:0] write<br>protect data<br>address | R1   | SEND_WRITE_PR<br>OT | if the card provides write protection<br>features, this command asks the card<br>to send the status of the write<br>protection bits.*1                                                              |

Note: 1. 32 write protection bits (representing 32 write protect groups starting at the specified address) followed by 16 CRC bits are transferred in a payload format via the data line. The last (least significant) bit of the protection bits corresponds to the first addressed group. If the addresses of the last groups are outside the valid range, then the corresponding write protection bits shall be set to zero.

# **Lock Card Command** (class 7)

| ^ | B. // | $\mathbf{r}$ |

|---|-------|--------------|

| u | IVI   | v            |

| index | Type | Argument          | Resp | Abbreviation | Command description                                                                                                     |

|-------|------|-------------------|------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| CMD42 | adtc | [31:0] stuff bits | R1b  | LOCK_UNLOCK  | used to set/reset the password or lock/unlock the card. The size of the data block is set by the SET_BLOCK_LEN command. |

# **Other Command**

## **CMD** index

| Omb mack       | Туре             | Argument | Resp | Abbreviation | <b>Command description</b> |

|----------------|------------------|----------|------|--------------|----------------------------|

| CMD5           | reserved         |          |      |              |                            |

| CMD6           | reserved         |          |      |              |                            |

| CMD8           | reserved         |          |      |              |                            |

| CMD14          | reserved         | -1-      |      |              |                            |

| CMD19          | reserved         |          |      |              |                            |

| CMD21<br>CMD23 | reserved         | "        |      |              |                            |

| CMD23          | reserved         |          |      |              |                            |

| CMD31          | reserved         |          | ,    |              |                            |

| CMD39          | Not<br>supported |          |      |              |                            |

| CMD40          | Not<br>supported |          |      |              |                            |

| CMD41          | reserved         |          |      |              |                            |

| CMD43<br>CMD54 | reserved         |          |      |              |                            |

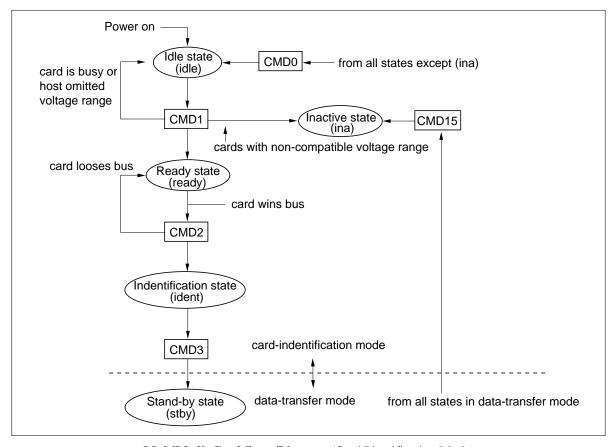

#### Card identification mode

All the data communication in the card identification mode uses only the command line (CMD).

MultiMediaCard State Diagram (Card Identification Mode)

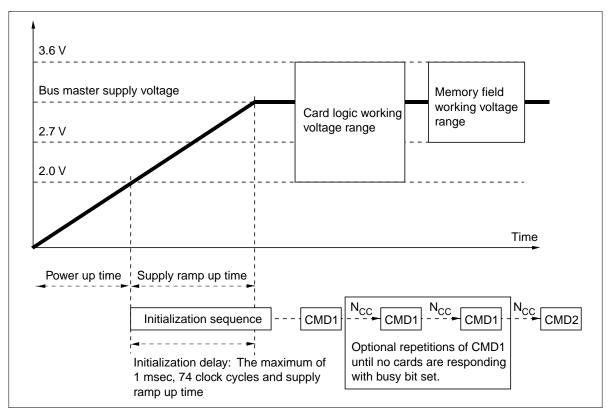

The host starts the card identification process in open drain mode with the identification clock rate  $f_{OD}$  (generated by a push pull driver stage). The open drain driver stages on the CMD line allow the parallel card operation during card identification. After the bus is activated the host will request the cards to send their valid operation conditions with the command SEND\_OP\_COND (CMD1). Since the bus is in open drain mode, as long as there is more than one card with operating conditions restrictions, the host gets in the response to the CMD1 a "wired or" operation condition restrictions of those cards. The host then must pick a common denominator for operation and notify the application that cards with out of range parameters (from the host perspective) are connected to the bus. Incompatible cards go into Inactive State (refer to also Chapter "Operating Voltage Range Validation"). The busy bit in the CMD1 response can be used by a card to tell the host that it is still working on its power-up/reset procedure (e.g. downloading the register information from memory field) and is not ready yet for communication. In this case the host must repeat CMD1 until the busy bit is cleared. After an operating mode is established, the host asks all cards for their unique card identification (CID) number with the broadcast command ALL\_SEND\_CID (CMD2). All not already identified cards (i.e. those which are in Ready State) simultaneously start sending their CID numbers serially, while bit-wise monitoring their outgoing bitstream. Those cards, whose outgoing CID

bits do not match the corresponding bits on the command line in any one of the bit periods, stop sending their CID immediately and must wait for the next identification cycle (cards stay in the Ready State). There should be only one card which successfully sends its full CID-number to the host. This card then goes into the Identification State. The host assigns to this card (using CMD3, SET\_RELATIVE\_ADDR) a relative card address (RCA, shorter than CID), which will be used to address the card in future communication (faster than with the CID). Once the RCA is received the card transfers to the Standby State and does not react to further identification cycles. The card also switches the output drivers from the open-drain to the push-pull mode in this state. The host repeats the identification process as long as it receives a response (CID) to its identification command (CMD2). When no card responds to this command, all cards have been identified. The time-out condition to recognize this, is waiting for the start bit for more than 5 clock periods after sending CMD2.

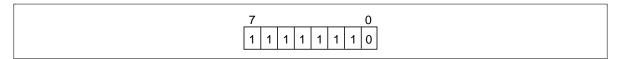

# **Operating Voltage Range Validation**

The MultiMediaCard standards operating range validation is intended to support reduced voltage range MultiMediaCards. The HB288064MM1 supports the range of 2.7 V to 3.6V supply voltage. So the HB288064MM1 sends a R3 response to CMD1 which contains an OCR value of 0x80FF8000 if the busy flag is set to "ready" or 0x00FF8000 if the busy flag is active (refer to Chapter "Responses"). By omitting the voltage range in the command, the host can query the card stack and determine the common voltage range before sending out-of-range cards into the Inactive State. This bus query should be used if the host is able to select a common voltage range or if a notification to the application of non usable cards in the stack is desired. Afterwards, the host must choose a voltage for operation and reissue CMD1 with this condition, sending incompatible cards into the Inactive State.

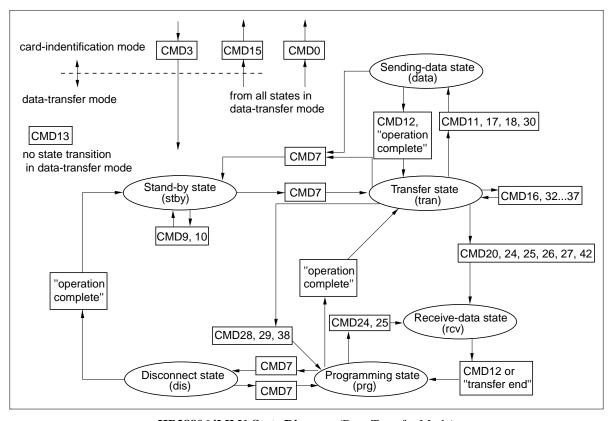

#### **Data Transfer Mode**

When in Standby State, both CMD and DAT lines are in the push-pull mode. As long as the content of all CSD registers is not known, the f<sup>PushPull</sup> clock rate is equal to the slow f<sup>OpenDrain</sup> clock rate. SEND\_CSD (CMD9) allows the host to get the Card Specific Data (CSD register), e.g. ECC type, block length, card storage capacity, maximum clock rate etc..

HB288064MM1 State Diagram (Data Transfer Mode)

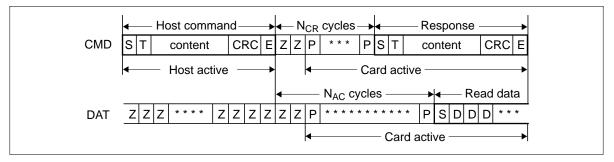

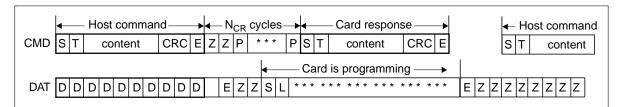

The command SELECT\_DESELECT\_CARD (CMD7) is used to select one card and place it in the Transfer State. If a previously selected card is in the Transfer State its connection with the host is released and it will move back to the Stand-by State. Only one card can be, at any time, in the Transfer State. A selected card is responding the CMD7, the deselected one does not respond to this command. When CMD7 is sent including the reserved relative card address "0x0000", all cards transfer back to Stand-by State. This command is used to identify new cards without resetting other already acquired cards. Cards to which an RCA has already been assigned, do not respond to the identification command flow in this state. All the data communication in the Data Transfer Mode is consequently a point-to point communication between the host and the selected card (using addressed commands). All addressed commands are acknowledged by a response on the CMD line. All read commands (data is sent from the card via data lines) can be interrupted at any time, by a stop command. The data transfer will terminate and the card will stop or start working on the next command. The DAT bus line signal level is high when no data is transmitted. A transmitted data block consists of a start bit (LOW), followed by a continuous data stream.

The data stream contains the net payload data (and error correction bits if an off-card ECC is used). The data stream ends with an end bit (HIGH). The data transmission is synchronous to the clock signal. The payload for block-oriented data transfer is preserved by a CRC check sum (refer to Chapter "Cyclic Redundancy Check (CRC)").

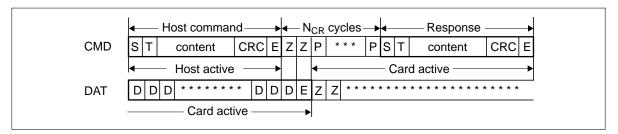

#### Stream read

There is a stream oriented data transfer controlled by READ\_DAT\_UNTIL\_STOP (CMD11). This command instructs the card to send its payload, starting at a specified address, until the host sends a STOP\_TRANSMISSION command (CMD12). The stop command has an execution delay due to the serial command transmission. The data transfer stops after the end bit of the stop command. If the end of the memory range is reached while sending data and no stop command has been sent yet by the host, the contents of the further transferred payload is undefined. The maximum clock frequency for stream read operation is given by the following formula:

```

max. speed = min (TRAN_SPEED, (8*2^{READ\_BL\_LEN}-NSAC)/TAAC), = min (20, (8*2^9 - 100 \text{ [cycles]})/1000 \text{ [}\mu\text{s]})[MHz] = min (20, 3.996) 3.996 [MHz]

```

these parameters being defined in Chapter "Registers". If the host attempts to use a higher frequency, the card may not be able to sustain data transfer. If this happens, the card will set the UNDERRUN error bit in the status register, abort the transmission and wait in the data state for a stop command.

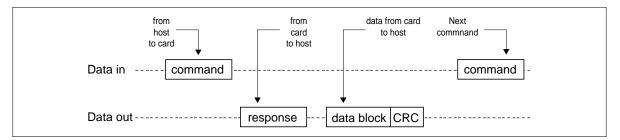

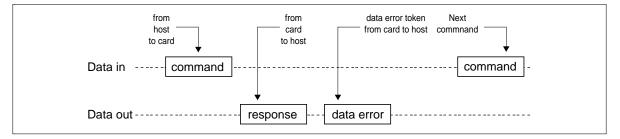

#### · Block read

The basic unit of data transfer is a block whose maximum size is defined in the CSD (READ\_BLK\_LEN). READ\_BLK\_PARTIAL is set, thus smaller blocks whose starting and ending address are wholly contained within one physical block (as defined by READ\_BLK\_LEN) may also be transmitted. A CRC is appended to the end of each block ensuring data transfer integrity. READ\_SINGLE\_BLOCK (CMD17) starts a block read and after a complete transfer the card goes back to Transfer State. READ\_MULTIPLE\_BLOCK (CMD18) starts a transfer of several consecutive blocks. Blocks will be continuously transferred until a stop is issued.

#### Stream write

Stream write (CMD20) starts the data transfer from the host to the card beginning from the starting address until the host issues a stop command. If partial blocks are allowed (if CSD parameter WRITE\_BL\_PARTIAL is set) the data stream can start and stop at any address within the card address space, otherwise it shall start and stop only at block boundaries. Since the amount of data to be transferred is not determined in advance, CRC can not be used. If the end of the memory range is reached while sending data and no stop command has been sent by the host, all further transferred data is discarded. The maximum clock frequency for stream write operation is given by the following formula:

```

max. speed = min ( TRAN_SPEED, (8*2^{WRITE\_BL\_LEN}-NSAC)/(TAAC*R2W\_FACTOR)), = min (20, (8*2^9 - 100 \text{ [cycles]})/1000 \text{ [}\mu\text{s]}^*4)[MHz] = min (20, 0.999) 0.999 [MHz]

```

these parameters being defined in Chapter "Registers". If the host attempts to use a higher frequency, the card may not be able to process the data and will stop programming, set the OVERRUN error bit in the status register, and while ignoring all further data transfer, wait (in the Receive-data-State) for a stop command. The write operation shall also be aborted if the host tries to write over a write-protected area. In this case, however, the card shall set the WP VIOLATION bit.

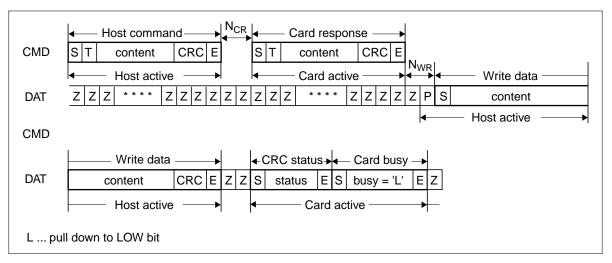

#### Block write

Block write (CMD24 - 27) means that one or more blocks of data are transferred from the host to the card with a CRC appended to the end of each block by the host. A card supporting block write must always be able to accept a block of data defined by WRITE\_BLK\_LEN. If the CRC fails, the card will indicate the failure on the DAT line; the transferred data will be discarded and not written and all further transmitted blocks (in multiple block write mode) will be ignored. If the host uses partial blocks whose accumulated length is not block aligned and block misalignment is not allowed (CSD parameter WRITE\_BLK\_MISALIGN is not set), the card will detect the block misalignment error and abort programming before the beginning of the first misaligned block. The card will set the ADDRESS\_ERROR error bit in the status register, and wait (in the Receive-data-State) for a stop command while ignoring all further data transfer. The write operation will also be aborted if the host tries to write over a write-protected area. In this case, however, the card will set the WP\_VIOLATION bit. Programming of the CID and CSD register does not require a previous block length setting. The transferred data is also CRC protected.

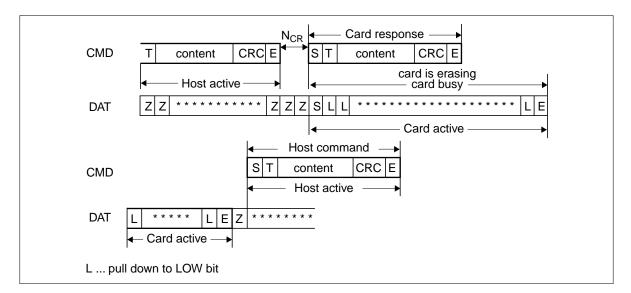

#### Erase

It is desirable to erase as many sectors at a time as possible in order to enhance the data throughput. Identification of these sectors is accomplished with the TAG\_\* commands. Either an arbitrary set of sectors within a single erase group, or an arbitrary selection of erase groups may be erased at one time, but not both together. That is, the unit of measure for determining an erase is either a sector or an erase group, but if a sector, all selected sectors must lie within the same erase group. To facilitate selection, a first command with the starting address is followed by a second command with the final address, and all sectors within this range will be selected for erase. After a range is selected, an individual sector (or group) within that range can be removed using the UNTAG command. The host must adhere to the following command sequence; TAG SECTOR START, TAG SECTOR END, UNTAG SECTOR (up to 16 untag sector commands can be sent for one erase cycle) and ERASE (or the same sequence for group tagging). The following exception conditions are detected by the card: An erase or tag/untag command is received out of sequence. The card will set the ERASE SEQUENCE error bit in the status register and reset the whole sequence. An out of sequence command (except SEND\_STATUS) is received. The card will set the ERASE\_RESET status bit in the status register, reset the erase sequence and execute the last command. If the erase range includes write protected sectors, they will be left intact and only the non-protected sectors will be erased. The WP ERASE SKIP status bit in the status register will be set. The address field in the tag commands is a sector or a group address in byte units. The card will ignore all LSB's below the group or sector size. The number of untags commands (CMD34 and CMD37) which are used in a sequence is limited up to 16. As described above for block write, the card will indicate that an erase is in progress by holding DAT low. The actual erase time may be quite long, and the host may choose to deselect the card using CMD7.

#### Write protect management

Card data may be protected against either erase or write. The entire card may be permanently write protected by the manufacturer or content provider by setting the permanent or temporary write protect bits in the CSD. Portions of the data may be protected (in units of WP\_GRP\_SIZE sectors as specified in the CSD), and the write protection may be changed by the application. The SET\_WRITE\_PROT command sets the write protection of the addressed write-protect group, and the CLR\_WRITE\_PROT command clears the write protection of the addressed write-protect group. The SEND\_WRITE\_PROT command is similar to a single block read command. The card shall send a data block containing 32 write protection bits (representing 32 write protect groups starting at the specified address) followed by 16 CRC bits. The address field in the write protect commands is a group address in byte units. The card will ignore all LSB's below the group size.

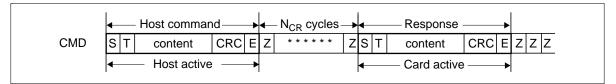

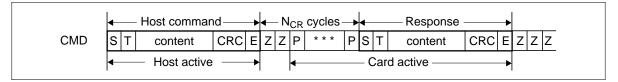

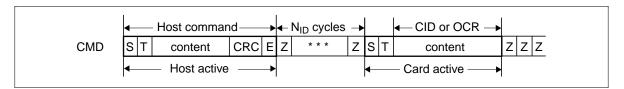

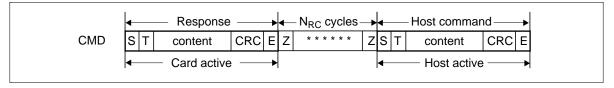

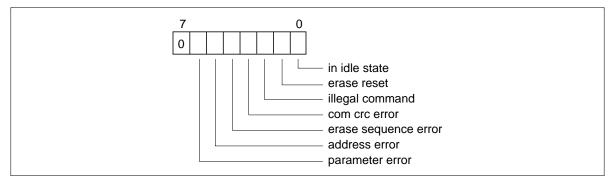

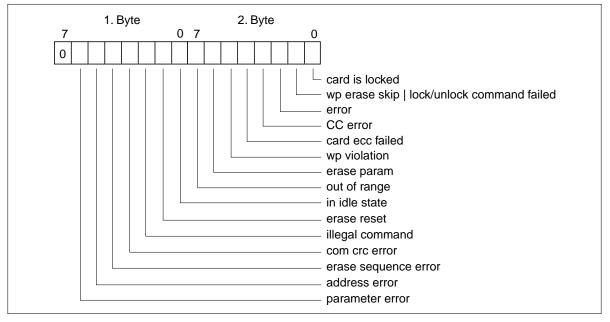

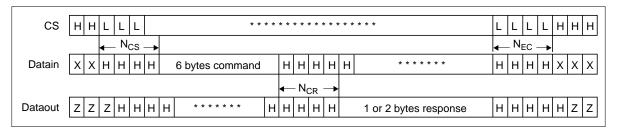

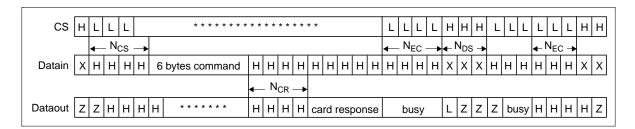

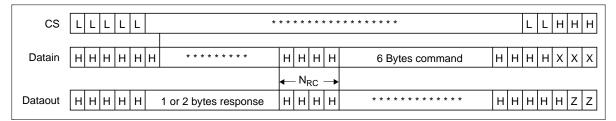

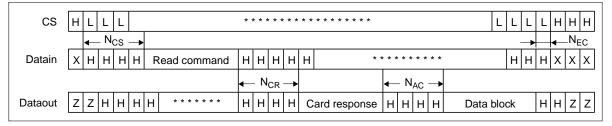

#### Card lock/unlock operation