# **IMS G300C**

# **COLOR VIDEO CONTROLLER**

PRODUCT OVERVIEW

#### **FEATURES**

Software configurable video timing generator Interlaced or non-interlaced video Generates Studio broadcast standard Sync signals Supplies blanked analogue video outputs Internal or external Sync options Single or synchronous multiple operation

Variable multiplexed Pixel input

1, 2, 4, 8 and 24 bit pixels

On chip triple lookup table

Triple high speed 8 bit video DACs

CCIR and EIA 343-A compatible

Full color mode with hardware gamma translation

General purpose Video RAM support Synchronous VRAM Data Transfer strobing Video RAM Row address auto-increment Screen width independent of VRAM architecture On-chip phase-locked loop (PLL) All external signals and clocks at 1/4 video rate

#### **APPLICATIONS**

High resolution graphics and imaging Broadcast/CC television systems

Color X-terminals

Low-cost workstations

High-resolution color PC add in boards

Multimedia display systems

#### DESCRIPTION

The IMS G300 is a high performance CMOS device which provides high integration and flexibility for the control of a color graphics display subsystem.

The IMS G300 has now been superseded by the IMS G335, which boasts a number of new features as well as a higher maximum pixel rate (up to 135MHz). The IMS G300 is not recommended for new designs, and will be obsoleted early in 1993. An Application Note is available describing the conversion of IMS G300 designs to IMS G335, providing a more cost-effective solution. Please contact your local sales office for a copy.

September 1992

42 1576 00

### TABLE OF CONTENTS

| 1.1 | Introduction           | 323 |

|-----|------------------------|-----|

| 1.2 | Package specifications | 32  |

| 1 2 | Ordoring information   | 329 |

### 16.1 Introduction

The IMS G300C is a dedicated support chip which provides all necessary functions for controlling real time operation of a raster scan video system, using dual ported video DRAMs. The facilities provided are designed to isolate the host processor from the constraints of the real time system without in any way interfering with the ability of the processor to specify and manipulate screen data.

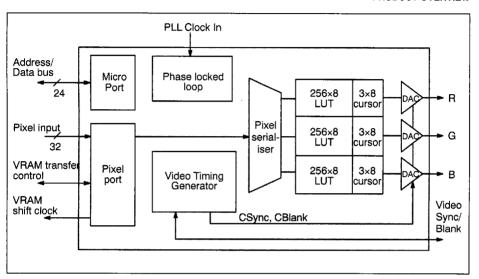

The device consists of a programmable video timing generator with screen refresh and auto line increment capability, a triple 256 location by 8 bit lookup table (LUT), a triple 8 bit video DAC and an on chip phase-locked loop (PLL); see Figure 16.1.

Figure 16.1 IMS G300C Block Diagram

### 16.1.1 Clocks

Use of the phase-locked loop allows the part to be driven from a low speed clock in the 5MHz to 10MHz range, which is internally multiplied by a user-specified factor to achieve video data rates. The controller can be clocked by a full rate system clock if desired, although at a reduced frequency compared to that achievable with the PLL.

## 16.1.2 Micro port

The IMS G300C has a memory mapped architecture which enables fast configuration and color cycling through the use of block move or some other simple memory write cycle. Its micro-port appears as a block of memory (occupying 1/2Kword of address space) with the additional capability of operating in byte-wide or word-wide (24-bit) modes.

## 16.1.3 Video timing

The video timing generator is a programmable finite state machine which is programmed by loading a number of screen description parameters. It can be configured to free run, providing composite or separate sync, or to lock onto an external synchronizing source which may be another IMS G300C, giving the potential for multiple, synchronous video systems. In either mode, it supplies composite blank and can

supply tesselated or plain composite sync to the video DACs. The timing generator runs at one quarter of the video dot rate and the screen parameters are defined in terms of its resolution. Thus the screen is defined in multiples of four pixels.

### 16.1.4 Framestore management

Video RAM support is provided by a screen refresh mechanism which performs a DMA to the video RAM and which allows seamless mid-line update of the screen. The video RAM shift register can be made to behave as though it is infinitely long and the flow of pixels onto the screen is controlled by starting and stopping the pixel shift clock at the appropriate times (a true serial clock output is also provided for system synchronization). This method of control divorces the screen line length from dependence on the video RAM shift register length, allowing for very long display lines without extra multiplexing and for efficient use of memory irrespective of screen dimensions.

### 16.1.5 Pixel port

The pixel port is 32 bits wide and has a number of operating modes, which are selectable in software.

In pseudo color mode (mode 1), the 32 bit word can be interpreted as consisting of one, two, four or eight bit pixels. These are loaded at the relevant multiplex ratio and accelerated to the full dot rate before addressing the LUT. The 24 bits of pixel data thus accessed are then sent to the video DACs for display.

In full color mode (mode 2), the top byte of the input word is ignored and the remaining three bytes are used as separate addresses into the triple LUT. No acceleration takes place before the data is sent to the LUT.

Mode 2 is usable only when an external dot-rate clock is supplied, mode 1 can also be used with the phase-locked loop.

#### 16.1.6 Video DACs

The triple video DAC has 8 bit resolution at the full video rate and produces blanked video signals. It is possible to select various styles of analogue output to conform with generally approved monitor and broadcast television output levels and timings, including EIA-343 and CCIR.

### 16.1.7 System Operation

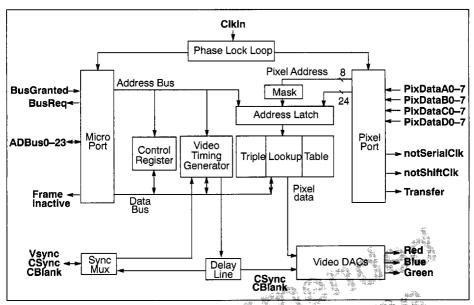

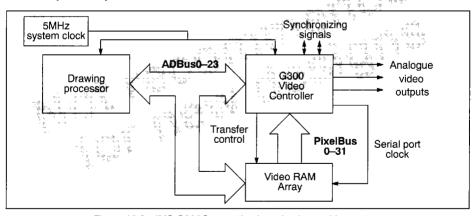

Figure 16.2 IMS G300C operating in a simple graphics system

Figure 16.2 shows how the IMS G300C would fit into a typical single-bitmap display system. The clock is sourced from a 5MHz crystal and the video data is being streamed to the screen at the full video rate of 110MHz. The video RAM array is directly accessed by the drawing processor and screen management is performed by the G300C on a DMA basis. All external digital signals and clocks are running at one quarter of the video rate.

# 16.2 Package specifications

# 16.2.1 84 pin grid array package

| Г | 1_              | 2                    | 3                    | 4              | 5           | 6                 | 7             | 8             | 9             | 10            |

|---|-----------------|----------------------|----------------------|----------------|-------------|-------------------|---------------|---------------|---------------|---------------|

| A | AD<br>Bus16     | AD<br>Bus18          | AD<br>Bus20          | AD<br>Bus21    | Reset       | VSync             | VDD           | Pix<br>DataB7 | Pix<br>DataA7 | Pix<br>DataD5 |

| В | AD<br>Bus11     | AD<br>Bus14          | AD<br>Bus15          | AD<br>Bus19    | AD<br>Bus23 | Ground            | Pix<br>DataD7 | Pix<br>DataD6 | Pix<br>DataB6 | Pix<br>DataB5 |

| С | AD<br>Bus10     | AD<br>Bus12          | AD<br>Bus13          | AD<br>Bus17    | AD<br>Bus22 | CorH<br>Sync      | Pix<br>DataC7 | Pix<br>DataC6 | Pix<br>DataA6 | Pix<br>DataD4 |

| D | AD<br>Bus7      | AD<br>Bus8           | AD<br>Bus9           | Index          | (           |                   | Pix<br>DataC5 | Pix<br>DataA5 | Pix<br>DataC4 |               |

| E | AD<br>Bus4      | AD<br>Bus6           | AD<br>Bus5           |                | IMS G       | 300C<br>rid array | Pix<br>DataB4 | Pix<br>DataA4 | Pix<br>DataD3 |               |

| F | AD<br>Bus3      | Vdd                  | Ground               |                |             | view              | Pix<br>DataB3 | Pix<br>DataA3 | Pix<br>DataC3 |               |

| G | AD<br>Bus2      | AD<br>Bus0           | not<br>Serial<br>Clk |                |             |                   | Pix<br>DataD2 | VDD           | Ground        |               |

| н | AD<br>Bus1      | Frame<br>Inactive    | notCS                | Bus<br>Granted | Blue        | Pix<br>DataA0     | Pix<br>DataB1 | CBlank        | Pix<br>DataA2 | Pix<br>DataC2 |

| J | not<br>ShiftClk | Read<br>not<br>Write | Cap<br>Minus         | BusReq         | Ground      | lref              | Pix<br>DataD0 | Pix<br>DataD1 | AVdd          | Pix<br>DataB2 |

| κ | Transfer        | Cap:                 | Cikin                | · VDD          | Green.      | Red               | Pix<br>DataB0 | Pix<br>DataC0 | Pix<br>DataA1 | Pix<br>DataC1 |

|   |                 |                      |                      |                |             |                   |               |               |               |               |

Figure 16.3 IMS G300C 84 pin grid array package pinout

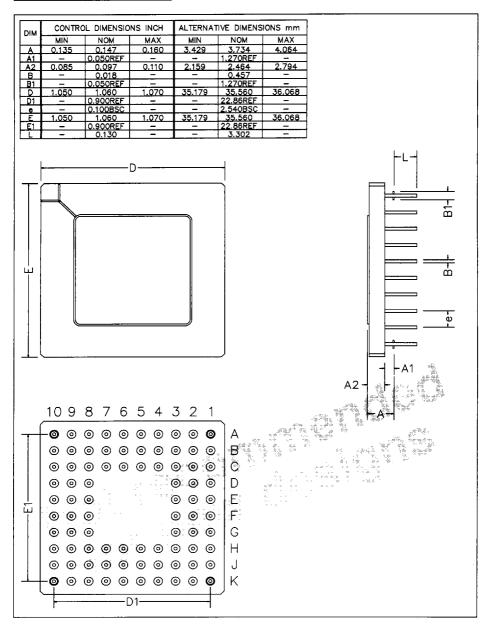

Figure 16.4 84 pin grid array package dimensions

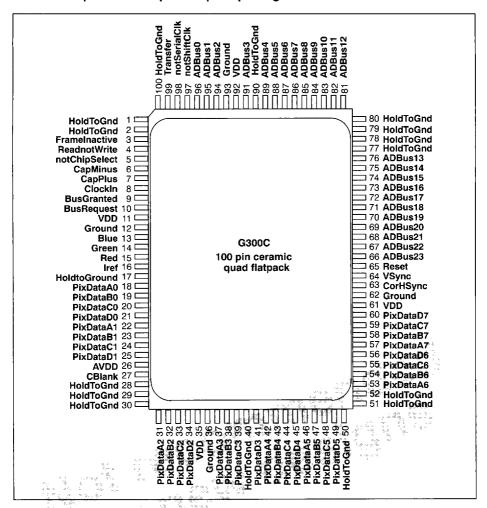

### 16.2.2 100 pin ceramic quad flatpack package

Figure 16.5 IMS G300C ceramic quad flatpack package pinout

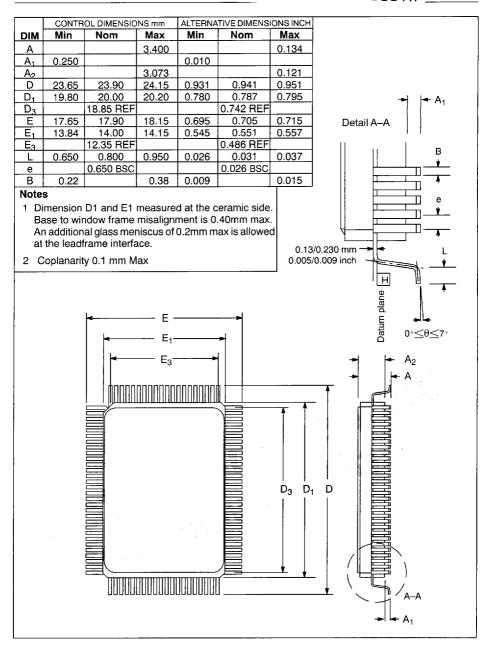

Figure 16.6 100 pin cavity-up ceramic quad flat pack dimensions

# 16.3 Ordering information

| Device    | Clock rate | Package                       | Part number   |

|-----------|------------|-------------------------------|---------------|

| IMS G300C | 85MHz      | 84 pin PGA                    | IMS G300G-85C |

| IMS G300C | 100MHz     | 84 pin PGA                    | IMS G300G-10C |

| IMS G300C | 110MHz     | 84 pin PGA                    | IMS G300G-11C |

| IMS G300C | 85MHz      | 100 pin ceramic quad flatpack | IMS G300F-85C |

| IMS G300C | 100MHz     | 100 pin ceramic quad flatpack | IMS G300F-10C |

| IMS G300C | 110MHz     | 100 pin ceramic quad flatpack | IMS G300F-11C |