# Agilent HFCT-701XB, 10 Gb Ethernet, 1310 nm, 10 km 10GBASE-LR, XENPAK LAN-PHY

**Data Sheet**

#### **Description**

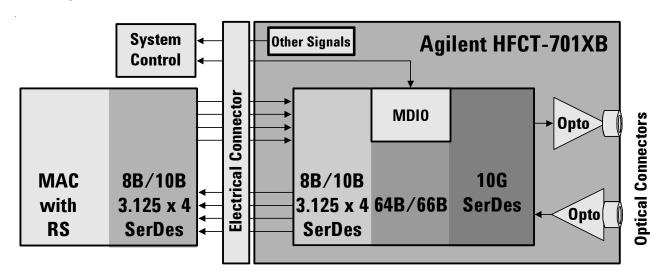

The HFCT-701XB is an "intelligent" optical module which incorporates the complete physical layer functionality from the 10.3125 Gb/s 64B/66B encoded optical interface to a XAUI compliant (4 channel x 3.125 Gb/s) 8B/10B encoded electrical interface and vice versa. The control interface (MDIO) is also integrated.

The HFCT-701XB module includes a transmitter that incorporates an uncooled, directly modulated 1310 nm DFB laser. The receiver subassembly includes a highly reliable PIN photodiode. The MUX/DEMUX, XAUI interface and MDIO management functions are all integrated into the module, as is a precision oscillator that removes any need for an external reference clock.

#### **Features**

- IEEE Std 802.3ae type 10GBASE-LR PMD (10 Gigabit Ethernet standard)

- Compliant with XENPAK MSA Draft 3.0

- Standard SC Duplex fiber optic connector

- Standard 70 pin electrical connector

- · Four wide XAUI Electrical interface

- · MDIO Management Interface

- Only 3.3 V and 1.8 V supplies required (compatible with the XENPAK APS)

- 5 diagnostic loopback modes

- · Front panel hot pluggable

- Excellent thermal and EMI integrity performance supports high port densities

- Hot plug power up circuit removes PSU sequence dependency and reduces inrush current

- Precision onboard oscillator no external clocks required

### **Applications**

- · Enterprise to Metro Uplinks

- · Campus Trunking

- · Data Aggregation

- Exchange Point-to-Point Links

# **Table of Contents**

# **General Specifications**

| General Optical Specifications                                     | 3      |

|--------------------------------------------------------------------|--------|

| General Electrical Specifications                                  | 3      |

| Environmental Specifications                                       | 3      |

| Technical Specifications                                           |        |

| Absolute Maximum Ratings                                           | 4      |

| Typical Operating Conditions                                       | 4      |

| Optical Specifications Electrical Control and Sense I/O Parameters | 5<br>5 |

| Electrical Specifications                                          | 8      |

| Mechanical Specifications                                          | 13     |

| ·                                                                  |        |

| Functional Descriptions                                            |        |

| Block Diagram                                                      | 17     |

| Transmitter Path Summary                                           | 17     |

| Receiver Path Summary                                              | 18     |

| Management Data Input Output (MDIO) Interface                      | 18     |

| EEPROM Interface                                                   | 19     |

| Monitor and Diagnostic Features                                    | 21     |

| Loopbacks                                                          | 24     |

| Reset Operation                                                    | 24     |

| Internal Clock Functionality                                       | 26     |

| HFCT-701XB Registers                                               |        |

| HFCT-701XB Device 1 PMA/PMD Registers                              | 28     |

| HFCT-701XB Device 3 PCS Registers                                  | 42     |

| HFCT-701XB Device 4 PHYXS Registers                                | 48     |

| Regulatory Compliance                                              |        |

| Electrostatic Discharge (ESD)                                      | 53     |

| Electromagnetic Interference (EMI)                                 | 53     |

| Immunity                                                           | 53     |

| Glossary                                                           | 53     |

|                                                                    |        |

# **General Specifications**

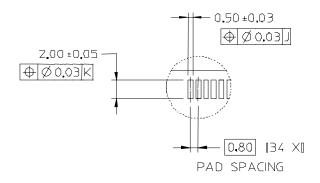

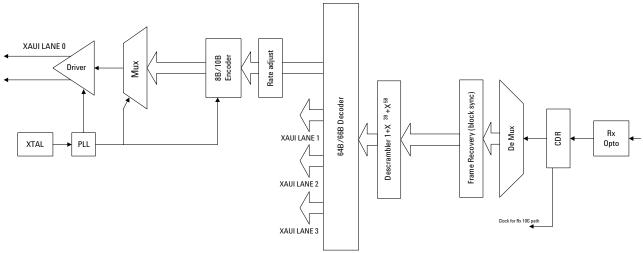

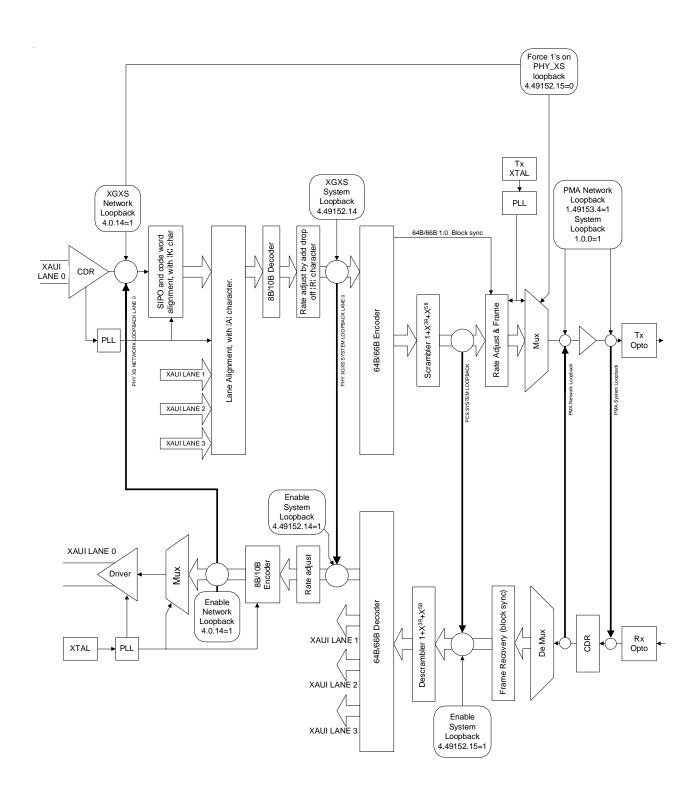

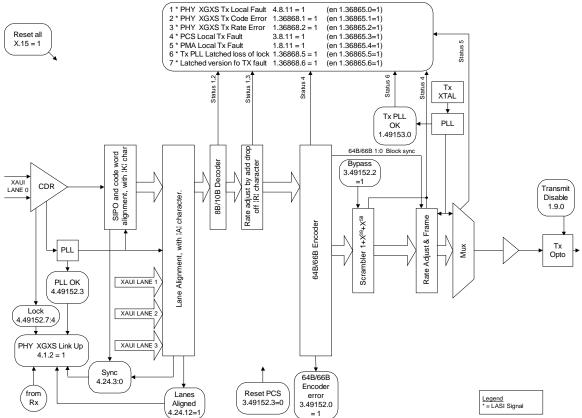

Figure 1. High level block diagram

## **General Optical Specifications**

Optical Connector:

SC Duplex

Optical Line rate:

10.3125 Gb/s

Link Length:

10 km, with G.652 fiber

Laser:

1310 nm, directly modulated, uncooled DFB

Detector:

PIN diode

#### **General Electrical Specifications**

Connector:

70-pin, mates to Tyco/AMP Part No. 1367337-1 or equivalent Supply Voltages: +1.8 V and +3.3 V E->O Coding (Transmit Direction): 8B/10B coding removed, 64B/ 66B added O->E Coding (Receive Direction): 64B/66Bremoved, 8B/10B coding added XAUI interface: 100  $\Omega$  Differential, AC- coupled I/O on Tx and Rx, per IEEE 802.3ae Clause 47 Control interface: MDIO, 1.2 V, per IEEE 802.3ae Clause 45.3

Non Volatile memory: 48 byte user space

#### **Environmental Specifications**

Operating temperature: 0 °C to +70 °C case Power consumption: 6.0 W maximum

# **Technical Specifications**

# **Absolute Maximum Ratings**<sup>1</sup>

| Parameter                 | Minimum | Typical | Maximum | Units | Notes            |

|---------------------------|---------|---------|---------|-------|------------------|

| Storage Temperature       | 0       |         | 85      | °C    |                  |

| Operating Temperature     | 0       |         | 70      | °C    | Case temperature |

| Supply Voltage (3.3 V)    |         |         | 3.6     | V     |                  |

| Supply Voltage (1.8 V)    |         |         | 2.0     | V     |                  |

| Voltage on any XAUI pin   |         |         | 2.5     | V     |                  |

| Voltage on any LVCMOS pin | -0.7    |         | 4.0     | V     |                  |

# $Recommended\ Operating\ Conditions^2$

| Parameter                      | Minimum | Typical | Maximum | Units | Conditions                      |

|--------------------------------|---------|---------|---------|-------|---------------------------------|

| Stabilization Time             |         | 0.5     | 5       | sec   |                                 |

| Input Voltage                  | 3.135   | 3.3     | 3.465   | V     |                                 |

| Input Voltage (APS)            | 1.71    | 1.8     | 1.89    | V     |                                 |

| Supply Current (@ 3.3 V)       |         | 1.5     | 1.6     | А     |                                 |

| Supply Current (@ 1.8 V)       |         | 0.15    | 0.4     | А     |                                 |

| Power Consumption              |         | 5.2     | 6.0     | W     |                                 |

| Inrush current during hot plug |         |         | 50      | mA/ms |                                 |

| Inrush current (per power pin) |         |         | 0.75    | А     | 150% x 0.5A steady state rating |

#### Notes:

<sup>1.</sup> Absolute maximum ratings are those values beyond which functional performance is not intended, device reliability is not implied, and damage to the device may occur.

<sup>2.</sup> Typical operating conditions are those values for which functional performance and device reliability is implied.

# **Optical Specifications**

| Parameter                                | Minimum | Typical | Maximum | Units    | Notes        |

|------------------------------------------|---------|---------|---------|----------|--------------|

| Transmitter                              |         |         |         |          |              |

| Laser OMA output power                   | -5.2    |         |         | dBm OMA  | 1, 2         |

| Laser mean output power                  | -8.2    |         | 0.5     | dBm mean | 1, 2, 3      |

| Extinction ratio                         | 3.5     |         | -       | dB       | 1, 2         |

| Wavelength                               | 1260    |         | 1355    | nm       |              |

| Transmitter and dispersion penalty (TDP) |         |         | 3.2     | dB       | 1, 2         |

| Side mode suppression ratio              | 30      |         |         | dB       | 1            |

| OMA - TDP                                | -6.2    |         |         | dBm OMA  | 1, 2         |

| RIN <sub>12</sub> OMA                    |         |         | -128    | dB/Hz    | 1            |

| Optical Return Loss                      |         |         | 12      | dB       |              |

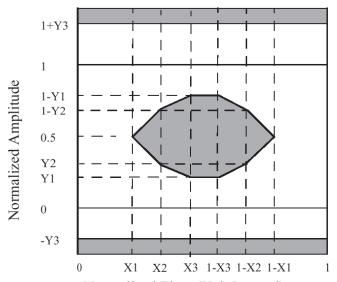

| TX eye definition                        |         |         |         |          | See Figure 2 |

| Receiver                                 |         |         |         |          |              |

| Stressed sensitivity                     | -       |         | -10.3   | dBm OMA  | 1            |

| Nominal sensitivity                      | -       |         | -12.6   | dBm OMA  | 1, 3         |

| Receive Power Overload                   | 0.5     |         |         | dBm mean | 1, 4         |

| Reflectance loss                         |         |         | -12     | dB       | 1            |

| Wavelength                               | 1260    |         | 1355    | nm       | 1            |

| Signal detect On                         | -30     |         |         | dBm      |              |

| Signal detect Off                        |         |         | -16     | dBm      |              |

| Signal detect Hysteresis                 | 0.5     |         |         | dB       |              |

# General Specification Considerations (Notes)

- 1. IEEE 802.3ae compliant.

- 2. These parameters are interrelated: see IEEE 802.3ae.

- 3. Information purposes only.

- 4. Up to 1.5 dB without damage.

$Normalized\ Time\ (Unit\ Interval)$  Note: where X1, X2, X3, Y1, Y2, Y3 = 0.25, 0.40, 0.45, 0.25, 0.28, 0.40 respectively

Figure 2. Transmitter Eye Mask Definition

# **Electrical Control and Sense I/O Parameters**

Table 1 - CMOS DC Parameters (MDC, PRTAD<4:0>, LASI)

| Parameter | Description                | Minimum | Typical | Maximum | Units | Conditions                            |

|-----------|----------------------------|---------|---------|---------|-------|---------------------------------------|

| Vol       | Output low voltage         |         |         | 0.15    | V     | ext. Rpullup = 10 k $\Omega$ to 1.2 V |

| Voh       | Output high voltage        | 1.0     |         | 1.5     | V     | ext. Rpullup = 10 k $\Omega$ to 1.2V  |

| Vih       | Input high voltage         | 0.84    |         | 1.25    | V     |                                       |

| Vil       | Input low voltage          |         |         | 0.36    | V     |                                       |

| lpd       | Input pad pulldown current | 20      | 40      | 120     | μА    | Vin = 1.2 V                           |

| Trise     | Rise time                  |         |         | 30      | us    | Cload = 300 pF                        |

| Tfall     | Fall time                  |         | 25      | 50      | ns    | Cload = 300 pF                        |

# **Electrical MDIO Parameters**

Table 2 - MDIO 1.2 V dc parameters

| Parameter | Description         | Minimum | Typical | Maximum | Units | Conditions    |

|-----------|---------------------|---------|---------|---------|-------|---------------|

| Voh       | Output high voltage | 1.0     |         | 1.5     | V     | Ioh = -100 uA |

| Vol       | Output low voltage  | -0.3    |         | 0.2     | V     | IoI = +100 uA |

| lol       | Output low current  | -4      |         |         | mA    | Vin = 0.3     |

| Vih       | Input high voltage  | 0.84    |         | 1.5     | V     |               |

| Vil       | Input low voltage   | -0.3    |         | 0.36    | V     |               |

| Cin       | Input capacitance   |         |         | 10      | pF    |               |

**Table 3 - MDIO AC Parameters**

| Parameter | Description                                       | Minimum | Typical | Maximum | Units | Conditions |

|-----------|---------------------------------------------------|---------|---------|---------|-------|------------|

| Thold     | MDIO data hold time                               | 10      |         |         | ns    |            |

| Tsetup    | MDIO data setup time                              | 10      |         |         | ns    |            |

| Tdelay    | Delay from MDC rising edge to<br>MDIO data change | 0       |         | 300     | ns    |            |

| Fmax      | Maximum MDC clock rate                            |         |         | 2.5     | MHz   |            |

# **Electrical High Speed I/O Parameters**

Table 4 - 3.125 Gb/s XAUI Input Interface

| Parameter | Description                                                                | Minimum | Typical | Maximum   | Units  | Conditions                                         |

|-----------|----------------------------------------------------------------------------|---------|---------|-----------|--------|----------------------------------------------------|

|           | BAUD rate                                                                  |         | 3.125   |           | Gb/s   |                                                    |

|           | BAUD rate tolerance                                                        | -100    |         | 100       | ppm    |                                                    |

|           | Differential input amplitude                                               | 200     |         | 2500      | mVpp   | Note 1                                             |

|           | Differential return loss                                                   |         |         | -10       | dB     | 100 MHz to 2.5 GHz ref to 100 $\!\Omega$ impedance |

|           | Common mode return loss                                                    |         |         | -6        | dB     | 100 MHz to 2.5 GHz ref to 25 $\!\Omega$            |

|           | Input Differential Skew                                                    |         |         | 75        | ps P-P | at crossing point, Note 2                          |

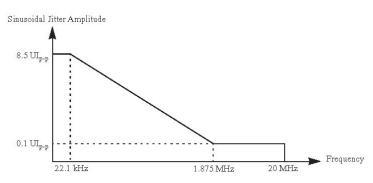

|           | Jitter amplitude tolerance<br>deterministic + random jitter +<br>Sj jitter |         |         | 0.55 + Sj | Ulpp   | See Figure 2a for SJ<br>jitter graph               |

Table 5 - 3.125 Gb/s XAUI Driver Characteristics

| Parameter | Description                     | Minimum | Typical | Maximum | Units | Conditions                                                                                       |

|-----------|---------------------------------|---------|---------|---------|-------|--------------------------------------------------------------------------------------------------|

|           | BAUD rate                       |         | 3.125   |         | Gb/s  |                                                                                                  |

|           | BAUD rate variation             | -100    |         | 100     | ppm   |                                                                                                  |

|           | Differential amplitude          | 800     |         | 1600    | mVpp  |                                                                                                  |

|           | Transition times (20-80%)       | 60      | 90      | 130     | ps    | Note 2                                                                                           |

|           | Total output jitter             |         |         | ± 0.175 | UI    | no pre-equalization                                                                              |

|           | Output deterministic jitter     |         |         | ± 0.085 | UI    | no pre-equalization                                                                              |

|           | Output differential skew        |         |         | 15      | ps    | at crossing point                                                                                |

|           | Differential output return loss |         |         |         | dB    | 312.5 MHz to 625<br>MHz: -10 dB<br>625 MHz to 3.125 GHz:<br>as per equation 47-1<br>IEEE 802.3ae |

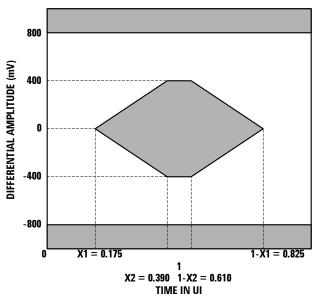

|           | Electrical eye mask             |         |         |         |       | See Figure 3                                                                                     |

#### Note

# $2. \quad For information only. \\$

Figure 2a. Single-tone sinusoidal jitter mask

<sup>1.</sup> Maximum amplitude of 2500 mVpp is the combined effect of the driver maximum output signal of 1600 mVpp and the receiver input impedance mismatch.

# **Electrical Eye Mask**

Figure 3 - XAUI Driver Near End Template

#### **General Connector Considerations**

- 1. Ground connections are common for Tx and Rx.

- 2.  $V_{\rm CC}$  contacts are each rated at 0.5 A nominal.

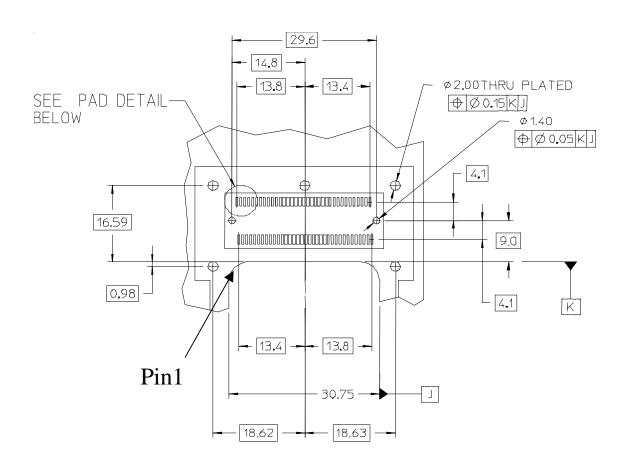

- 3. See Figure 8 for layout of Host PCB and location of Pin1.

Table 6 - General I/O Pin Summary

| Signal Type                 | Pins                                                     | Direction | Function                           |

|-----------------------------|----------------------------------------------------------|-----------|------------------------------------|

| Power Supply Pins           |                                                          |           |                                    |

| Ground                      | 1:3, 33:37, 40, 43, 46, 49, 52:54, 57, 60, 63, 66, 69:70 |           | Electrical ground                  |

| 3.3 V                       | 5:6, 30:31                                               | ı         | 3.3 V power supply                 |

| 5.0 V                       | 4, 32                                                    | I         | 5.0 V power supply not used        |

| Adaptive power supply       | 7:8, 28:29                                               | I         | Adaptive power supply (1.8 V)      |

| Adaptive power supply set   | 25                                                       | I         | APS set connection                 |

| Adaptive power supply sense | 27                                                       | I         | APS sense connection               |

| Control & Sense I/O Pins    |                                                          |           |                                    |

| LASI                        | 9                                                        | 0         | 1.2 V CMOS pull up on host         |

| Reset                       | 10                                                       | I         | 1.2 V CMOS pull up on module       |

| Transmitter ON/OFF          | 12                                                       | I         | 1.2 V CMOS pull up on module       |

| Port address 4:0            | 19:23                                                    | 1         | 1.2 V CMOS pull up on module       |

| MDIO Pins                   |                                                          |           |                                    |

| MOD DETECT                  | 14                                                       | 0         | 1 kW pull down to ground on module |

| Management data IO          | 17                                                       | 1/0       | 1.2 V per IEEE802.3ae clause 45.3  |

| Management data clock       | 18                                                       | I         | 1.2 V per IEEE802.3ae clause 45.3  |

| High Speed I/O Pins         |                                                          |           |                                    |

| Receiver lane 0:3 +         | 41, 44, 47, 50                                           | 0         | XAUI per IEEE802.3ae clause 47     |

| Receiver lane 0:3 -         | 42, 45, 48, 51                                           | 0         | XAUI per IEEE802.3ae clause 47     |

| Transmitter lane 0:3 +      | 55, 58, 61, 64                                           | 1         | XAUI per IEEE802.3ae clause 47     |

| Transmitter lane 0:3 -      | 56, 59, 62, 65                                           | 1         | XAUI per IEEE802.3ae clause 47     |

| Non Connected Pins          |                                                          |           |                                    |

| Not connected               | 4, 11, 13, 15:16, 24, 26, 32, 38:39, 67:68               |           | NC on module                       |

# **Electrical Pin Out**

| 70 | GND           | 1  | GND           |

|----|---------------|----|---------------|

| 69 | GND           | 2  | GND           |

| 68 | NOT CONNECTED | 3  | GND           |

| 67 | NOT CONNECTED | 4  | 5.0V          |

| 66 | GND           | 5  | 3.3V          |

| 65 | TX LANE3-     | 6  | 3.3V          |

| 64 | TX LANE3+     | 7  | APS           |

| 63 | GND           | 8  | APS           |

| 62 | TX LANE2-     | 9  | LASI          |

| 61 | TX LANE2+     | 10 | RESET         |

| 60 | GND           | 11 | NOT CONNECTED |

| 59 | TX LANE1-     | 12 | TX ON/OFF     |

| 58 | TX LANE1+     | 13 | NOT CONNECTED |

| 57 | GND           | 14 | MOD DETECT    |

| 56 | TX LANEO-     | 15 | NOT CONNECTED |

| 55 | TX LANEO+     | 16 | NOT CONNECTED |

| 54 | GND           | 17 | MDIO          |

| 53 | GND           | 18 | MDC           |

| 52 | GND           | 19 | PRTAD4        |

| 51 | RX LANE3-     | 20 | PRTAD3        |

| 50 | RX LANE3+     | 21 | PRTAD2        |

| 49 | GND           | 22 | PRTAD1        |

| 48 | RX LANE2-     | 23 | PRTAD0        |

| 47 | RX LANE2+     | 24 | NOT CONNECTED |

| 46 | GND           | 25 | APS SET       |

| 45 | RX LANE1-     | 26 | NOT CONNECTED |

| 44 | RX LANE1+     | 27 | APS SENSE     |

| 43 | GND           | 28 | APS           |

| 42 | RX LANEO-     | 29 | APS           |

| 41 | RX LANE0+     | 30 | 3.3V          |

| 40 | GND           | 31 | 3.3V          |

| 39 | NOT CONNECTED | 32 | 5.0V          |

| 38 | NOT CONNECTED | 33 | GND           |

| 37 | GND           | 34 | GND           |

| 36 | GND           | 35 | GND           |

Figure 4. Electrical Pin Out

# Electrical Pin Out Definitions Table 7 - Pin Function Definitions (Lower Row)

| Pin No | Name          | Direction | Function                                                                                        | Note         |

|--------|---------------|-----------|-------------------------------------------------------------------------------------------------|--------------|

| 1      | GND           |           | Electrical ground                                                                               |              |

| 2      | GND           |           | Electrical ground                                                                               |              |

| 3      | GND           |           | Electrical ground                                                                               |              |

| 4      | NOT CONNECTED |           | 5.0 V power supply                                                                              |              |

| 5      | 3.3 V         | I         | 3.3 V power supply                                                                              |              |

| 6      | 3.3 V         | I         | 3.3 V power supply                                                                              |              |

| 7      | APS           | I         | Adaptive power supply (1.8 V)                                                                   |              |

| 8      | APS           | I         | Adaptive power supply (1.8 V)                                                                   |              |

| 9      | LASI          | 0         | Logic high: normal operation<br>Logic low: LASI asserted                                        | See Table 10 |

| 10     | RESET         | I         | Logic high: normal operatio<br>Logic low: reset                                                 |              |

| 11     | NOT CONNECTED |           |                                                                                                 |              |

| 12     | TX ON/OFF     | 1         | Pulled up inside module via 10 k $\Omega$ Logic high: transmitter on Logic low: transmitter off |              |

| 13     | NOT CONNECTED |           |                                                                                                 |              |

| 14     | MOD DETECT    | 0         | Pulled low inside module through 1 k to GND                                                     |              |

| 15     | NOT CONNECTED |           |                                                                                                 |              |

| 16     | NOT CONNECTED |           |                                                                                                 |              |

| 17     | MDIO          | 1/0       | Management data IO                                                                              |              |

| 18     | MDC           | I         | Management data clock                                                                           |              |

| 19     | PRTAD4        | I         | Port address bit 4                                                                              |              |

| 20     | PRTAD3        | I         | Port address bit 3                                                                              |              |

| 21     | PRTAD2        | I         | Port address bit 2                                                                              |              |

| 22     | PRTAD1        | I         | Port address bit 1                                                                              |              |

| 23     | PRTAD0        | I         | Port address bit 0                                                                              |              |

| 24     | NOT CONNECTED |           |                                                                                                 |              |

| 25     | APS SET       | I         | APS set connection                                                                              |              |

| 26     | NOT CONNECTED |           |                                                                                                 |              |

| 27     | APS SENSE     | I         | APS sense connection                                                                            |              |

| 28     | APS           | I         | Adaptive Power Supply (1.8 V)                                                                   |              |

| 29     | APS           | 1         | Adaptive Power Supply (1.8 V)                                                                   |              |

| 30     | 3.3 V         | I         | Power                                                                                           |              |

| 31     | 3.3 V         | I         | Power                                                                                           |              |

| 32     | NOT CONNECTED |           | 5.0 V Power Supply                                                                              |              |

| 33     | GND           |           | Electrical Ground                                                                               |              |

| 34     | GND           |           | Electrical Ground                                                                               |              |

| 35     | GND           |           | Electrical Ground                                                                               |              |

|        |               |           |                                                                                                 |              |

Table 8 - Pin Function Definitions (Upper Row)

| Pin No | Name          | Direction | Function                   | Note |

|--------|---------------|-----------|----------------------------|------|

| 36     | GND           |           | Electrical Ground          |      |

| 37     | GND           |           | Electrical Ground          |      |

| 38     | NOT CONNECTED |           |                            |      |

| 39     | NOT CONNECTED |           |                            |      |

| 40     | GND           |           | Electrical Ground          |      |

| 41     | RX LANE 0+    | 0         | Module XAUI Output Lane 0+ |      |

| 42     | RX LANE 0-    | 0         | Module XAUI Output Lane 0- |      |

| 43     | GND           |           | Electrical Ground          |      |

| 44     | RX LANE 1+    | 0         | Module XAUI Output Lane 1+ |      |

| 45     | RX LANE 1-    | 0         | Module XAUI Output Lane 1- |      |

| 46     | GND           |           | Electrical Ground          |      |

| 47     | RX LANE 2+    | 0         | Module XAUI Output Lane 2+ |      |

| 48     | RX LANE 2-    | 0         | Module XAUI Output Lane 2- |      |

| 49     | GND           |           | Electrical Ground          |      |

| 50     | RX LANE 3+    | 0         | Module XAUI Output Lane 3+ |      |

| 51     | RX LANE 3-    | 0         | Module XAUI Output Lane 3- |      |

| 52     | GND           |           | Electrical Ground          |      |

| 53     | GND           |           | Electrical Ground          |      |

| 54     | GND           |           | Electrical Ground          |      |

| 55     | TX LANE 0+    | I         | Module XAUI Input Lane 0+  |      |

| 56     | TX LANE 0-    | I         | Module XAUI Input Lane 0-  |      |

| 57     | GND           |           | Electrical Ground          |      |

| 58     | TX LANE 1+    | I         | Module XAUI Input Lane 1+  |      |

| 59     | TX LANE 1-    | I         | Module XAUI Input Lane 1-  |      |

| 60     | GND           |           | Electrical Ground          |      |

| 61     | TX LANE 2+    | I         | Module XAUI Input Lane 2+  |      |

| 62     | TX LANE 2-    | I         | Module XAUI Input Lane 2-  |      |

| 63     | GND           |           | Electrical Ground          |      |

| 64     | TX LANE3+     | I         | Module XAUI Input Lane 3+  |      |

| 65     | TX LANE3-     | I         | Module XAUI Input Lane 3-  |      |

| 66     | GND           |           | Electrical Ground          |      |

| 67     | NOT CONNECTED |           |                            |      |

| 68     | NOT CONNECTED |           |                            |      |

| 69     | GND           |           | Electrical Ground          |      |

| 70     | GND           |           | Electrical Ground          |      |

| 1.0    |               |           |                            |      |

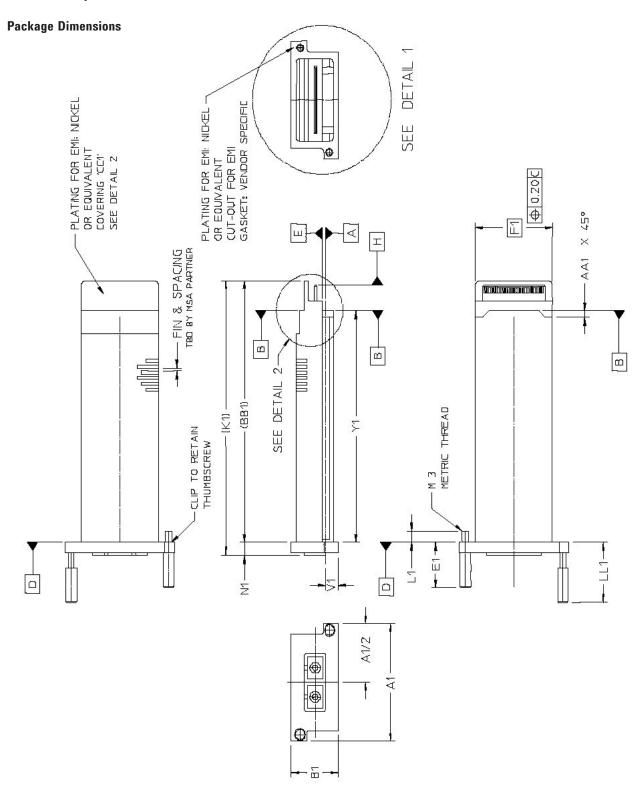

# **Mechanical Specifications**

Figure 5.

#### Note:

It is recommended that the user refers to the XENPAK MSA at www.xenpak.org for full mechanical detail.

# Dimensions Table (Figure 5)

| -   | Values  |       | Tolerance | Comments                                                           |

|-----|---------|-------|-----------|--------------------------------------------------------------------|

|     | mm      | inch  | mm        |                                                                    |

| A1  | 51.3    | 2.020 | ±0.20     | Width of Bezel overall                                             |

| B1  | 22.4    | 0.882 | ±0.20     | Height of Bezel overall                                            |

| E1  | 20.75   | 0.817 | Maximum   | Extension of captive screw                                         |

| F1  | 36.0    | 1.417 | ±0.20     | Width of Transceiver body                                          |

| K1  | (121.0) | 4.764 | REF       | Length of Transceiver overall minus protruding captive screw heads |

| L1  | 5.00    | 0.197 | ±0.20     | Length of captive screw from Datum "D" to end of threaded end      |

| N1  | 5.8     | 0.228 | ±0.20     | Datum "D" to front of Transceiver Bezel                            |

| V1  | 7.92    | 0.312 | ±0.20     | Datum "E" to Bottom of Transceiver Bezel                           |

| Y1  | 102.20  | 4.024 | ±0.20     | Datum "D" to Datum "B"                                             |

| AA1 | 3.0     | 0.118 | ±0.50     | Datum "B" to end of 45° chamfer                                    |

| BB1 | (115.2) | 4.535 | REF       | Length of Module from Datum "D" to rear Over-hanging Ledge         |

| LL1 | 25.8    | 1.016 | Maximum   | Length of Thumbscrew                                               |

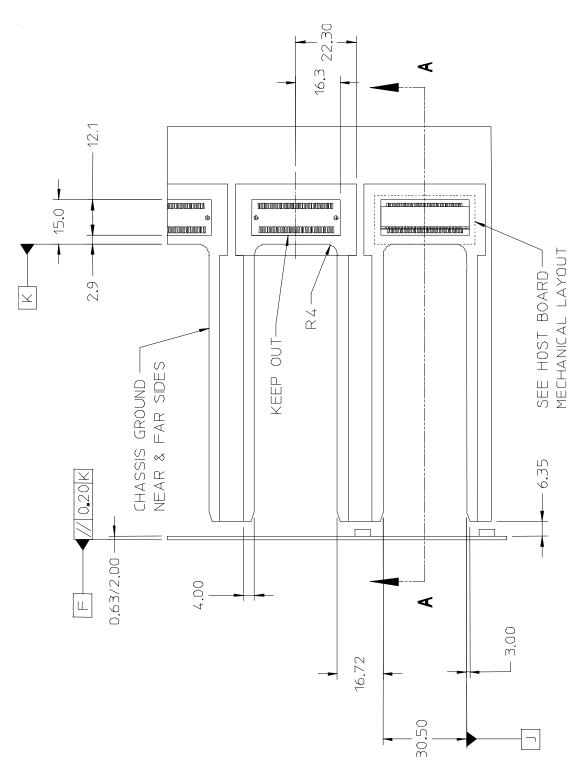

Figure 6.

Note:

Case Ground is separated from the common Rx and Tx signal ground

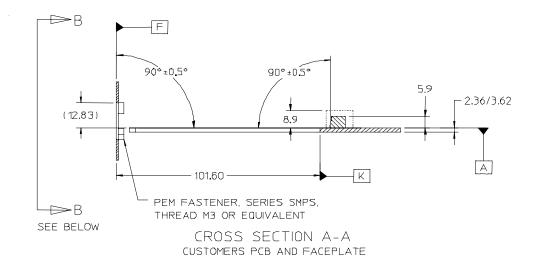

Figure 7.

PAD DETAIL SCALE 4X

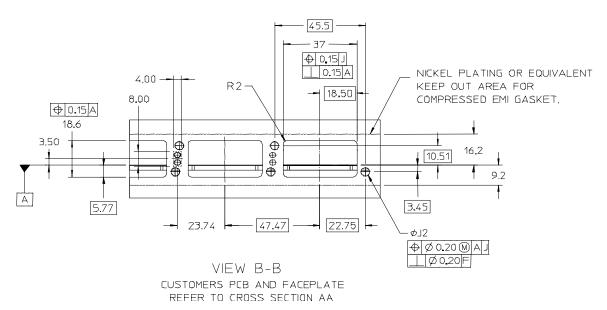

Figure 8. Host board layout for 70 pin connector

#### **Functional Descriptions**

### **Block Diagram**

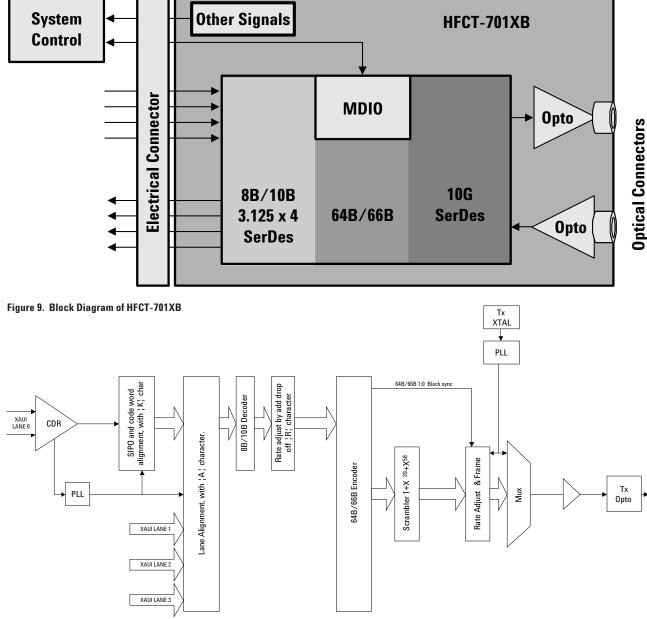

Figure 9 shows a block diagram of the HFCT-701XB. Figures 10 and 11 show greater detail of the transmitter and receiver paths.

#### **Transmitter Path Summary**

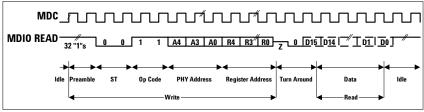

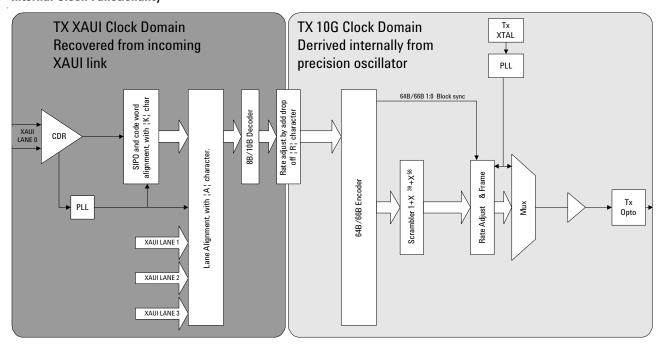

Figure 10 shows a block diagram of the transmit path, from the four XAUI differential inputs to the optical output. The incoming 4 x 3.125 Gb/s XAUI differential 8B/10B encoded electrical inputs, are reformatted and transmitted onto the outgoing fiber optic interface at 10.3125 Gb/s, using 64B/66B encoding.

Figure 10. Transmit Path High Level Overview

#### **Receiver Path Summary**

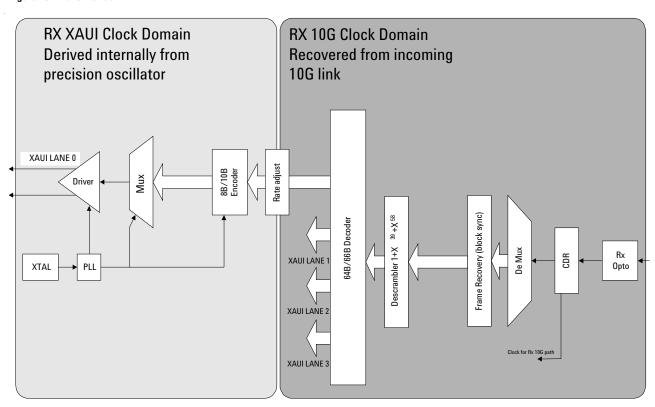

Figure 11 shows a block diagram of the receiver path, from the incoming 10.3125 Gb/s, 64B/66B encoded optical interface to the four 3.125 Gb/s differential 8B/10B encoded XAUI electrical output interface. The XAUI output drivers provide lowswing differential output with 100  $\Omega$  differential output impedance and are ac coupled.

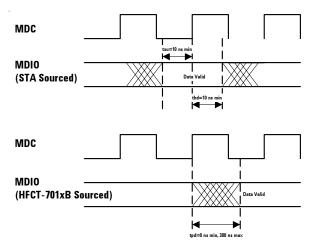

# Management Data Input/Output (MDIO) Interface

The MDIO interface provides a simple, two wire, serial interface to connect a station management entity (STA) and a managed PHY for the purpose of controlling the PHY and gathering status from the PHY. The management interface consists of the two wire physical interface, a frame format, a protocol specification for exchanging the frames and a register set that can be read and written using these frames. The two wires of the physical interface are the Management Data Clock (MDC) and the Management Data I/O (MDIO).

#### Management Data Clock (MDC)

The MDC is sourced by the Station Management entity (STA) to the PHY as the timing reference for transfer of information on the MDIO signal. MDC is an aperiodic signal that has no maximum high or low times.

#### Management Data I/O (MDIO)

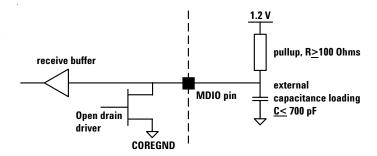

MDIO is a bidirectional signal between the PHY (HFCT-701XB) and the STA. It is used to transfer control and status information. Data is always driven and sampled synchronously with respect to MDC. Figure 13 shows that MDIO open drain driver configuration.

#### MDIO Timing relationship to MDC

MDIO is a bidirectional signal that can be sourced by the STA or the HFCT-701XB. When the STA sources the MDIO signal, the STA shall provide a minimum of 10 ns of setup time and a minimum of 10 ns of hold time referenced to the rising edge of MDC (see Figure 12). When the MDIO signal is sourced by the HFCT-701XB, it is sampled by the STA synchronously with respect to the rising edge of MDC. The clock output delay from the HFCT-701XB shall be a minimum of 0 ns and a maximum of 300 ns.

Figure 12. MDIO/MDC Timing

Figure 11. Receive Path High Level Overview

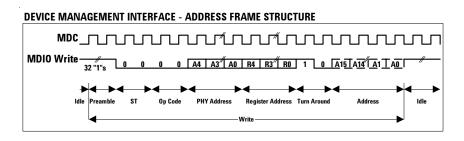

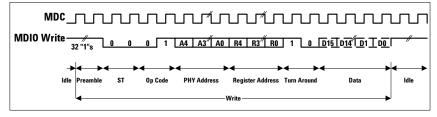

#### **Management Frame Format**

The HFCT-701XB has an internal address register which is used to store the address for MDIO reads and writes. This MDIO address register can be set by using an address frame that specifies the register address to be accessed within a particular port device.

The following write, read or a post-read-increment-address frame to the same port device shall access the register whose address is stored in the HFCT-701XB MDIO address register. An address frame should be followed immediately by its associated write, read or post-read-increment-address frame.

Upon receiving a post-read-increment-address frame and having completed the read operation, the HFCT-701XB shall increment and store the address of the register accessed. If no address cycle is received before the next write, read or post-read-increment-address frame, then the HFCT-701XB shall use the stored address for that register access.

The Management Frame Format for Indirect Access is specified in Table 9.

#### **PRE - Preamble**

At the beginning of each transaction the STA shall send a preamble sequence of 32 contiguous logic one bits on MDIO with 32 corresponding cycles on MDC, to provide the HFCT-701XB with a pattern that it can use to establish synchronization. The HFCT-701XB must observe this preamble sequence before it responds to any transaction.

### ST - Start

The Start of Frame is indicated by a <00> pattern. This pattern ensures transitions from the default logic one line to zero and back to one.

Figure 13. MDIO open Drain Driver Configuration

Table 9. Frame Format

|          | Mana | geme | ent Fr | ame Fields |         |    |           |      |

|----------|------|------|--------|------------|---------|----|-----------|------|

| FRAME    | PRE  | ST   | 0P     | PRTAD      | DEVAD   | TA | ADDR/DATA | IDLE |

| ADDRESS  | 11   | 00   | 00     | PRTAD[4:0] | DA[4:0] | 10 | D[15:0]   | Z    |

| WRITE    | 11   | 00   | 01     | PRTAD[4:0] | DA[4:0] | 10 | D[15:0]   | Z    |

| READ     | 11   | 00   | 11     | PRTAD[4:0] | DA[4:0] | Z0 | D[15:0]   | Z    |

| READ INC | 11   | 00   | 10     | PRTAD[4:0] | DA[4:0] | Z0 | D[15:0]   | Z    |

#### **OP - Operation Code**

Table 10. OP Code Definitions

| OP Code | Operation                     |

|---------|-------------------------------|

| 00      | Register Address              |

| 01      | Write Data                    |

| 11      | Read Data                     |

| 10      | Post Read Data +<br>Increment |

#### **PRTAD**

The Port Address is five bits, allowing 32 unique port addresses. HFCT-701XB's port address is set through pins PRTAD<0:4>.

#### **DEVAD**

The Device Address is five bits, allowing 32 unique devices per port. The HFCT-701XB supports device addresses 1 (PMA/PMD), 3 (PCS) and 4 (PHY XS).

#### TA

The Turnaround time is a two bit time spacing between the Register Address field and the Data field of a management frame to avoid contention during a read transaction (see IEEE 802.3ae).

#### ADDR/DATA

The Data/Address field is 16 bits. The first bit transmitted/received is bit 15 and the last bit is bit 0.

#### **IDLE**

The idle condition is a highimpedance state. The MDIO line will be pulled to a one.

#### **EEPROM Interface**

### NVR

There are two main memory/register types in the HFCT-701XB which comply with the IEEE 802.3ae and XENPAK standard: volatile and nonvolatile. These areas can be further divided into user readable and writeable areas.

At power up the module register space is initialized and, where appropriate, default values are loaded from the non user accessible nonvolatile memory. The user accessible nonvolatile memory is also uploaded entirely into the user accessible volatile memory.

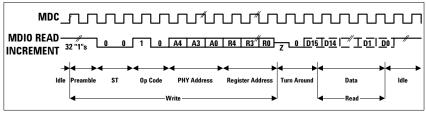

#### **DEVICE MANAGEMENT INTERFACE - WRITE FRAME STRUCTURE**

#### DEVICE MANAGEMENT INTERFACE - READ INCREMENT FRAME STRUCTURE

#### **DEVICE MANAGEMENT INTERFACE - READ FRAME STRUCTURE**

Figure 14. MDIO Frame Formats

It is important to note that writes to the user accessible volatile memory are not stored to the corresponding user nonvolatile area and will therefore be lost upon a power down or reset. For such writes to be permanent the data must be written first to the user accessible nonvolatile area and then a reload invoked via the NVR Control/Status register, see Register 1.32768.

#### Access

The XENPAK MSA related Nonvolatile Control/Status register is only needed for performing writes to the nonvolatile user accessible area within the HFCT-701XB because nonvolatile memory cannot be written to by normal MDIO write cycles. Other writes to volatile memory and registers may be performed directly via normal MDIO write cycles. All volatile and nonvolatile locations may be read directly via MDIO read cycles, it is not necessary to use the NVR Control/Status register, other than for status.

#### Read/Write Command (bit5)

The XENPAK MSA related 1.32768.5 register must be set to 1 to perform writes to the NVR and zero (read) otherwise a zero written to bit 5 initiates an NVR read. A 1 written to bit 5 initiates an NVR write.

**Table 11. LASI Control Registers**

If the NVR register bit 5 is set to zero and the extended command bits set to 11 forces an upload of all values in the NVR to the volatile areas, including default register values. Such an upload is performed automatically after a hard or soft reset.

## **EEPROM Checksum Checking**

The HFCT-701XB will perform a checksum calculation and compare after every successful 256 byte read. The checksum for comparison is in EEPROM register 118 =MDIO register 1.32893.7:0. The checksum is equal to the 8 LSB 's of the sum of bytes 0 to 117 of the EEPROM. The calculated checksum is stored in MDIO register 1.49156.15:8. The result of the calculated checksum compared with the one read from EEPROM is placed in MDIO register 1.49155.7.

#### **EEPROM 256 Byte Read Cycle**

An EEPROM 256 Byte Read Cycle is initiated by setting MDIO bits 1.32768.0,1 to 0 and 1.32768.5 to 0.

The information to be read from the EEPROM stored in the 256 MDIO registers. A 256 byte read is initiated on hot plug or reset.

# **EEPROM Single Byte Read or Write Cycle**

An EEPROM Single Byte Read/ Write Cycle is initiated by setting MDIO EEPROM control register bits 1.32768.1:0 to 10. As for the 256 byte read/write commands, MDIO register 1.32768.5 determines if a read or a write cycle will be performed. The single byte EEPROM address is read from EEPROM control register 1.32768 bit15:8. The data is placed in/read from the associated MDIO register.

#### **Monitors and Diagnostic Features**

The LASI pin is used to indicate suboptimal performance in either the receive or transmit path. It can be used as an interrupt. It is the OR of the tx\_alarm, rx\_alarm and the ls\_alarm signals each gated with their respective enables. The enables are read from MDIO register 1.36867, LASI control.

LASI ={OR of (reg 1.36869.n 'bit wise AND ' reg 1.36866.n) for n=0 to 15}.

| Description                | MDIO Status Registers | Туре  | MDIO Enable Registers | Default Value |

|----------------------------|-----------------------|-------|-----------------------|---------------|

| ·                          |                       |       | <del>-</del>          |               |

| LS_ALARM                   | 1.36869.0             | RO/LH | 1.36866.0             | 0             |

| TX_ALARM                   | 1.36869.1             | RO/LH | 1.36866.1             | 0             |

| RX_ALARM                   | 1.36869.2             | RO/LH | 1.36866.2             | 0             |

| LASI test mode             | 1.36869.3             | RW    | 1.36866.3             | 0             |

| 1.8 V supply too low       | 1.36869.4             | RO/LH | 1.36866.4             | 0             |

| 3.3 V supply too low       | 1.36869.5             | RO/LH | 1.36866.5             | 0             |

| MON3P3V_IN voltage too low | 1.36869.6             | RO/LH | 1.36866.6             | 0             |

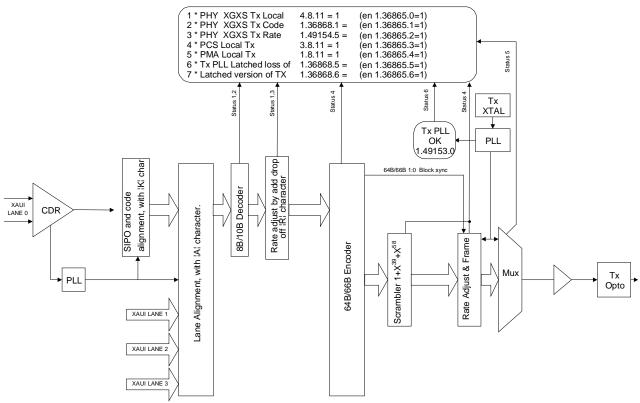

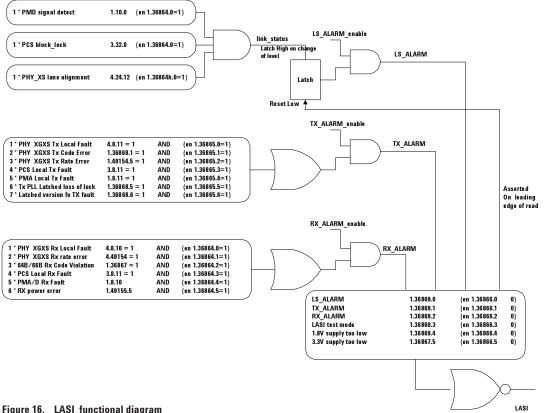

#### ls alarm

LS Alarm is latched high each time the link\_status signal changes state. LS\_ALARM is the output of this latch AND the LS\_ALARM enable register (see Figure 15). link\_status is an indicator of the link health.

link\_status = {PMD signal detect (MDIO 1.10.0) AND PCS block\_lock (MDIO 3.32.0) AND PHY\_XS lane\_alignment (MDIO 4.24.12)}

#### tx alarm

tx\_alarm is used to indicate a problem with the transmit path. tx\_alarm is the OR of several transmit path status registers in MDIO registers 1.36868 bit wise AND'd with the TX\_ALARM enable register. The ORing of each term is enabled by a companion MDIO register in 1.36865.

tx\_alarm = {OR of (reg 1.36868 'bit wise AND' reg 1.36865) for n=0 to 15} AND {TX\_ALARM enable (reg 1.36866)}

**Table 12. Receive Alarm Registers**

| Description                | MDIO Status<br>Registers (RO) | Mirrors   | Туре  | MDIO Enable<br>Registers (R/W) | Default |

|----------------------------|-------------------------------|-----------|-------|--------------------------------|---------|

| PHY_XS receive local fault | 1.36867.0                     | 4.8.10    | RO/LH | 1.36864.0                      | 1       |

| PHY_XS receive rate error  | 1.36867.1                     | 1.49154.3 | RO/LH | 1.36864.1                      | 0       |

| PCS receive code violation | 1.36867.2                     |           | RO/LH | 1.36864.2                      | 0       |

| PCS receive local fault    | 1.36867.3                     | 3.8.11    | RO/LH | 1.36864.3                      | 0       |

| PMA receive local fault    | 1.36867.4                     | 1.8.11    | RO/LH | 1.36864.4                      | 1       |

| Receive power error        | 1.36867.5                     |           | RO/LH | 1.36864.5                      | 0       |

Figure 15. Tx LASI Signals

#### Rx alarm

rx\_alarm is used to indicate a problem with the receive path. rx\_alarm is the OR of several receive path status registers in MDIO registers 1.36867.

The ORing of each term is enabled by a companion MDIO register in 1.36864 and the overall output is enabled by the RX\_ALARM enable register (1.36866.2h).

**Table 13. Transmit Alarm Registers** rx\_alarm ={OR of (reg 1.36867 'bit wise AND ' reg 1.36864..n) for n=0 to 15} AND {RX\_ALARM enable (1.36866.2h})

| Description                 | MDIO Status<br>Registers (RO) | Mirrors   | Туре  | MDIO Enable<br>Registers (R/W) | Default |

|-----------------------------|-------------------------------|-----------|-------|--------------------------------|---------|

| PHY_XS transmit local fault | 1.36868.0                     | 4.8.11    | RO/LH | 1.36865.0                      | 1       |

| PHY_XS code error           | 1.36868.1                     | -         | RO/LH | 1.36865.1                      | 0       |

| PHY_XS transmit rate error  | 1.36868.2                     | 1.49154.5 | RO/LH | 1.36865.2                      | 0       |

| PCS transmit local fault    | 1.36868.3                     | 3.8.11    | RO/LH | 1.36865.3                      | 1       |

| PMA transmit local fault    | 1.36868.4                     | 1.8.11    | RO/LH | 1.36865.4                      | 1       |

| latched version of txlock   | 1.36868.5                     | 1.49153.0 | RO/LH | 1.36865.5                      | 0       |

| latched version of TXFAULT  | 1.36868.6                     |           | RO/LH | 1.36865.6                      | 1       |

| laser temperature error     | 1.36868.7                     |           | RO/LH | 1.36865.7                      | 0       |

| laser bias error            | 1.36868.8                     |           | RO/LH | 1.36865.8                      | 0       |

| Tx output power error       | 1.36868.9                     |           | RO/LH | 1.36865.9                      | 0       |

Figure 16. LASI functional diagram

#### Loopbacks

When in any system (PMA, PCS or XGXS system) loopback mode the HFCT-701XB shall accept data from the transmit path and return it on the receive path.

During PMA loopback the XENPAK module will transmit the data received at the XAUI i/p's. In XGXS system loopback, the laser will default to mean power but without any modulation. In PCS loopback mode a continuous pattern of 0x0F0F will be output. Transmit data will be output instead if the associated 'loopback data out enable bit ' is set high for the enabled loopback mode.

When in PMA network loopback mode, the recovered and retimed 10.3125 GBd signal is looped to the transmitter. The receive path XAUI output data will be received data. XAUI idle codes will be output instead of the received data if the 'network loopback data out enable bit ' is set high.

In IEEE 802.3ae standard XGXS network loopback the recovered received data is looped back to the transmit path in the XAUI block

Enabling of more than one loopback path is invalid.

**Table 14. Loopback Summary**

| loopback name                               | loopback<br>direction | loopback<br>control<br>register | bypassed path<br>default output | data output enable<br>register | bypassed path<br>output control' =1 |

|---------------------------------------------|-----------------------|---------------------------------|---------------------------------|--------------------------------|-------------------------------------|

| PMA system loopback                         | Tx -> Rx              | 1.0.0                           | transmit data                   | NA                             | NA                                  |

| PCS loopback                                | Tx -> Rx              | 3.0.14                          | 0F0F                            | 3.49152.5                      | transmit data                       |

| XGXS network loopback<br>(802.3ae standard) | Rx -> Tx              | 4.0.14                          | Receive data at Rx<br>Xaui      | NA                             | NA                                  |

| XGXS system loopback                        | Tx -> Rx 4            | 4.49152.14                      | Mean power, no modulation       | 4.49152.15                     | transmit data                       |

| PMA network loopback                        | Rx -> Tx 1            | 1.49153.4                       | received data                   | 1.49153.9                      | idle at RxXAUI                      |

## **Reset Operation**

Writing a '1' to any of MDIO registers 1.0.15, 3.0.15 or 4.0.15 causes all the HFCT-701XB registers to be reset to their default values. These bits are all self-clearing after the reset function is complete.

Pulling the RESET pin low causes a full chip reset.

Writes to any bits of the Control register while the RESET is asserted are ignored. All status and control registers are reset to their default states. The NVR read sequence is started when RESET goes high. MDIO register bits 1.0.15, 3.0.15, and 4.0.15 will be held to 1 until the reset sequence is complete.

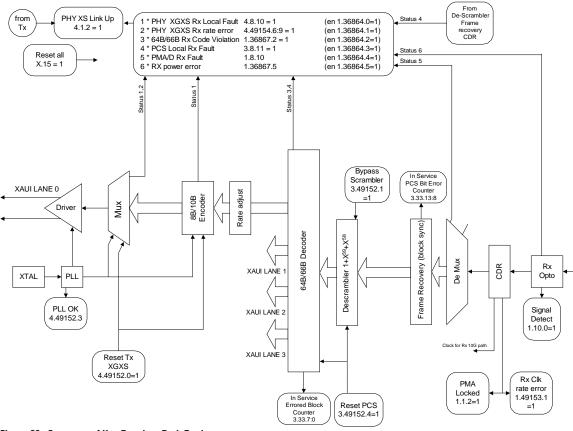

Figure 17. HFCT-701XB Loopback Modes

### **Internal Clock Functionality**

Figure 18. Transmit Path

Figure 19. Receive Path

#### **HFCT-701XB Registers**

Figure 20. Summary of Key Receiver Path Registers

Figure 21. Summary of Key Transmit Path Registers

HFCT-701XB Device 1 PMA/PMD Registers

| Device | From<br>Decimal | Hex  | To<br>Decimal | Hex  | Register Name                                         |

|--------|-----------------|------|---------------|------|-------------------------------------------------------|

| 1      | 0               | 0    |               |      | PMA/PMD Control 1                                     |

| 1      | 1               | 1    |               |      | PMA/PMD Status 1                                      |

| 1      | 2               | 2    | 3             | 3    | Device identifier                                     |

| 1      | 4               | 4    |               |      | PMA/PMD Speed Ability                                 |

| 1      | 5               | 5    | 6             | 6    | Devices in package                                    |

| 1      | 7               | 7    |               |      | 10G PMA/PMD Control 2                                 |

| 1      | 8               | 8    |               |      | 10G PMA/PMD Status 2                                  |

| 1      | 9               | 9    |               |      | 10G PMD transmit disable                              |

| 1      | 10              | А    |               |      | 10G PMD receive signal detect                         |

| 1      | 14              | E    | 15            | F    | Package identifier (OUI)                              |

| 1      | 32768           | 8000 |               |      | NVR Control/Status                                    |

| 1      | 32775           | 8007 |               |      | XENPAK MSA version supported                          |

| 1      | 32776           | 8008 | 32777         | 8009 | NVR size in bytes                                     |

| 1      | 32778           | 800A | 32779         | 800B | Number of bytes used                                  |

| 1      | 32780           | 800C |               |      | Basic Field Address                                   |

| 1      | 32781           | 800D |               |      | Customer Field Address                                |

| 1      | 32782           | 800E |               |      | Vendor Field Address                                  |

| 1      | 32783           | 800F | 32784         | 8010 | Extended Vendor Field Address                         |

| 1      | 32785           | 8011 |               |      | Reserved                                              |

| 1      | 32786           | 8012 |               |      | Transceiver type                                      |

| 1      | 32787           | 8013 |               |      | Optical connector type                                |

| 1      | 32788           | 8014 |               |      | Bit encoding                                          |

| 1      | 32789           | 8015 | 32790         | 8016 | Nominal Bit Rate in multiples of 1Mb/s                |

| 1      | 32791           | 8017 |               |      | Protocol Type                                         |

| 1      | 32792           | 8018 | 32801         | 8021 | Standards Compliance Codes 10GbE Code Byte 0          |

| 1      | 32802           | 8022 | 32803         | 8023 | Specifies transmission range in 10 m increments       |

| 1      | 32804           | 8024 | 32805         | 8025 | Fibre Type Byte 0 and Byte1                           |

| 1      | 32806           | 8026 | 32808         | 8028 | Centre Optical Wavelength in 0.01nm steps - Channel 0 |

| 1      | 32818           | 8032 | 32821         | 8035 | Package Identifier OUI                                |

| 1      | 32822           | 8036 | 32825         | 8039 | Transceiver Vendor OUI                                |

|        |                 |      |               |      |                                                       |

| Device | From<br>Decimal | Hex  | To<br>Decimal | Hex  | Register Name                                           |

|--------|-----------------|------|---------------|------|---------------------------------------------------------|

| 1      | 32826           | 803A | 32841         | 8049 | Transceiver vendor name in ASCII                        |

| 1      | 32842           | 804A | 32857         | 8059 | Part number provided by transceiver vendor in ASCII     |

| 1      | 32858           | 805A | 32859         | 805B | Revision level for part number provided by vendor ASCII |

| 1      | 32860           | 805C | 32875         | 806B | Vendor serial number in ASCII                           |

| 1      | 32876           | 806C | 32885         | 8075 | Vendor manufacturing date code in ASCII                 |

| 1      | 32886           | 8076 |               |      | 5 V stressed environment reference                      |

| 1      | 32887           | 8077 |               |      | 3.3 V stressed environment reference                    |

| 1      | 32888           | 8078 |               |      | APS stressed environment reference                      |

| 1      | 32889           | 8079 |               |      | Nominal APS voltage                                     |

| 1      | 32890           | 807A |               |      | DOM capability                                          |

| 1      | 32891           | 807B |               |      | Reserved                                                |

| 1      | 32893           | 807D |               |      | Basic Field Checksum                                    |

| 1      | 32894           | 807E | 32941         | 80AD | Customer Writeable Area                                 |

| 1      | 32942           | 80AE | 33030         | 8106 | Vendor Specific                                         |

| 1      | 33031           | 8107 | 36863         | 8FFF | Extended Vendor Specific                                |

| 1      | 36864           | 9000 |               |      | RX_ALARM Control                                        |

| 1      | 36865           | 9001 |               |      | TX_ALARM Control                                        |

| 1      | 36866           | 9002 |               |      | LASI Control                                            |

| 1      | 36867           | 9003 |               |      | RX_ALARM Status                                         |

| 1      | 36868           | 9004 |               |      | TX_ALARM Status                                         |

| 1      | 36869           | 9005 |               |      | LASI Status                                             |

| 1      | 49153           | C001 |               |      | Extended PMA features                                   |

| 1      | 49155           | C003 |               |      | PMA/PMD Vendor Specific                                 |

| 1      | 49156           | C004 |               |      | PMA/PMD Vendor Specific Checksum                        |

| 1      | 49188           | C024 |               |      | PMA Vendor Specific                                     |

# Register 1.0 - PMA/PMD Control 1

| Bit(s)   | Name            | Description                         | $R/W^1$ | <b>Default Value</b> |

|----------|-----------------|-------------------------------------|---------|----------------------|

| 1.0.15   | Reset           | 1 = PMA/PMD reset                   | RW      |                      |

|          |                 | 0 = Normal operation                |         |                      |

| 1.0.14   | Reserved        | Value always 0, writes ignored      | RW      |                      |

| 1.0.13   | Speed selection | 1 = Operation at 10 Gb/s and above  | RW      | 1                    |

|          |                 | 0 = Unspecified                     |         |                      |

| 1.0.12   | Reserved        | Value always 0, writes ignored      | RW      |                      |

| 1.0.11   | Low Power       | 1 = Low Power mode                  | RW      | 0                    |

|          |                 | 0 = Normal operation                |         |                      |

| 1.0.10:7 | Reserved        | Value always 0, writes ignored      | RW      |                      |

| 1.0.6    | Speed selection | 1 = Operation at 10 Gb/s and above  | RW      | 1                    |

|          |                 | 0 = Unspecified                     |         |                      |

| 1.0.5:2  | Speed selection | 5 4 3 2                             | RW      |                      |

|          |                 | $1 \times \times \times = Reserved$ |         |                      |

|          |                 | x 1 x x = Reserved                  |         |                      |

|          |                 | $x \times 1 x = Reserved$           |         |                      |

|          |                 | 0 0 0 1 = Reserved                  |         |                      |

|          |                 | $0\ 0\ 0\ 0 = 10\ Gb/s$             |         |                      |

| 1.0.1    | Reserved        | Values always 0, writes ignored     | RW      |                      |

| 1.0.0    | PMA loopback    | 1 = Enable PMA loopback mode        | RW      | 0                    |

|          |                 | 0 = Disable PMA loopback mode       |         |                      |

# Register 1.1 - PMA/PMD Status 1

| Bit(s)   | Name                | Description                                            | R/W¹  | Default Value |

|----------|---------------------|--------------------------------------------------------|-------|---------------|

| 1.1.15:8 | Reserved            | N/A                                                    | R0    |               |

| 1.1.7    | Fault               | 1 = Local fault condition detected in PMA/PMD          | R0    | N/A           |

|          |                     | 0 = Local fault condition not detected in PMA/PMD      |       |               |

|          |                     | (Set to a 1 when either 1.8.11 or 1.8.10 set to a one) |       |               |

| 1.1.6:3  | Reserved            | N/A                                                    | RO/LL |               |

| 1.1.2    | Receive link status | 1 = PMA locked to receive signal                       | RO/LL | N/A           |

|          |                     | 0 = PMA not locked to receive signal                   |       |               |

| 1.1.1    | Power down ability  | 1 = PMA/PMD supports low power mode                    | R0    | 1             |

|          |                     | 0 = PMA/PMD does not support low power mode            |       |               |

| 1.1.0    | Reserved            | N/A                                                    |       |               |

# Register 1.2 to 1.3 - Device Identifier

| Bit(s)   | Name           | Description | R/W¹ | Default Value |

|----------|----------------|-------------|------|---------------|

| 1.3.15:0 | PMA Identifier |             | RO   |               |

| 1.2.15:0 | PMA Identifier |             | R0   |               |

# Register 1.4 PMA/PMD Speed Ability

| Bit(s)   | Name                | Description                                       | R/W¹ | Default Value |

|----------|---------------------|---------------------------------------------------|------|---------------|

| 1.4.15:1 | Reserved for future |                                                   | R0   | N/A           |

|          | speeds              |                                                   |      |               |

| 1.4.0    | 10 G capable        | 1 = PMA/PMD is capable of operating at 10 Gb/s    | R0   | 1             |

|          |                     | 0 = PMA/PMD is not capable of operating at 10Gb/s |      |               |

# Note:

1. RW = Read/Write, R0 = Read Only, LL = Latching Low

Register 1.5 to 1.6 - PMA/PMD Devices in Package

| Bit(s)   | Name                   | Description                                         | $R/W^1$ | Default Value |

|----------|------------------------|-----------------------------------------------------|---------|---------------|

| 1.6.15   | Vendor Specific Device | 1 = Vendor specific device 2 present in package     | RO      | 1             |

|          | 2 present              | 0 = Vendor specific device 2 not present in package |         |               |

| 1.6.14   | Vendor Specific        | Reserved                                            | R0      |               |

| 1.6.13:0 | Reserved               | N/A                                                 | R0      |               |

| 1.5.15:6 | Reserved               | N/A                                                 | R0      |               |

| 1.5.5    | DTE XS present         | 1 = DTE XS present in package                       | RO      | 0             |

|          |                        | 0 = DTE XS not present in package                   |         |               |

| 1.5.4    | PHY XS present         | 1 = PHY XS present in package                       | RO      | 1             |

|          |                        | 0 = PHY XS not present in package                   |         |               |

| 1.5.3    | PCS present            | 1 = PCS present in package                          | R0      | 1             |

|          |                        | 0 = PCS not present in package                      |         |               |

| 1.5.2    | WIS present            | 1 = WIS present in package                          | R0      | 0             |

|          |                        | 0 = WIS not present in package                      |         |               |

| 1.5.1    | PMD/PMA present        | 1 = PMD/PMA present in package                      | R0      | 1             |

|          |                        | 0 = PMD/PMA not present in package                  |         |               |

| 1.5.0    | Clause 22 registers    | 1 = Clause 22 registers present in package          | R0      | 0             |

|          | present                | 0 = Clause 22 registers not present in package      |         |               |

# Register 1.7 - 10 G PMA/PMD Control 2

| Bit(s)   | Name         | Description                      | R/W¹ | Default Value |

|----------|--------------|----------------------------------|------|---------------|

| 1.7.15:3 | Reserved     | N/A                              |      |               |

| 1.7.2:0  | PMA/PMD type | 2 1 0                            | RW   | 110           |

|          | selection    | 1 1 1 = 10GBASE-SR PMA/PMD type  |      |               |

|          |              | 1 1 0 = 10GBASE-LR PMA/PMD type  |      |               |

|          |              | 1 0 1 = 10GBASE-ER PMA/PMD type  |      |               |

|          |              | 1 0 0 = 10GBASE-LX4 PMA/PMD type |      |               |

|          |              | 0 1 1 = 10GBASE-SW PMA/PMD type  |      |               |

|          |              | 0 1 0 = 10GBASE-LW PMA/PMD type  |      |               |

|          |              | 0 0 1 = 10GBASE-EW PMA/PMD type  |      |               |

|          |              | 0 0 0 = Reserved                 |      |               |

#### Note:

1. RW = Read/Write, RO = Read Only,

Register 1.8 - 10 G PMA/PMA Status 2

| Bit(s)    | Name                 | Description                                               | $R/W^1$ | Default Value |

|-----------|----------------------|-----------------------------------------------------------|---------|---------------|

| 1.8.15:14 | Device present       | 15 14                                                     | R0      | 10            |

|           |                      | 1 0 = Device responding at this address                   |         |               |

|           |                      | 1 1 = No device responding at this address                |         |               |

|           |                      | 0 1 = No device responding at this address                |         |               |

|           |                      | 0 0 = No device responding at this address                |         |               |

| 1.8.13    | Transmit local fault | 1 = PMA/PMD has the ability to detect a local fault       | R0      | 1             |

|           | ability              | condition on the transmit path                            |         |               |

|           |                      | 0 = PMA/PMD does not have the ability to detect a fault   |         |               |

|           |                      | condition on the transmit path                            |         |               |

| 1.8.12    | Receive local fault  | 1 = PMA/PMD has the ability to detect a local fault       | R0      | 1             |

|           | ability              | condition on the receive path                             |         |               |

|           |                      | 0 = PMA/PMD does not have the ability to detect a fault   |         |               |

|           |                      | condition on the receive path                             |         |               |

| 1.8.11    | Transmit local fault | 1 = Local fault condition on transmit path                | RO/LH   | N/A           |

|           |                      | 0 = No local fault condition on transmit path             |         |               |

| 1.8.10    | Receive local fault  | 1 = Local fault condition on receive path                 | RO/LH   | N/A           |

|           |                      | 0 = No local fault condition on receive path              |         |               |

| 1.8.9     | Reserved             | N/A                                                       | R0      |               |

| 1.8.8     | PMD transmit disable | 1 = PMD has the ability to disable the transmit path      | R0      | 1             |

|           | ability              | 0 = PMD does not have the ability to disable the transmit |         |               |

|           |                      | path                                                      |         |               |

| 1.8.7     | 10GBASE-SR ability   | 1 = PMA/PMD is able to perform 10GBASE-SR                 | R0      | 0             |

|           |                      | 0 = PMA/PMD is not able to perform 10GBASE-SR             |         |               |

| 1.8.6     | 10GBASE-LR ability   | 1 = PMA/PMD is able to perform 10GBASE-LR                 | R0      | 1             |

|           |                      | 0 = PMA/PMD is not able to perform 10GBASE-LR             |         |               |

| 1.8.5     | 10GBASE-ER ability   | 1 = PMA/PMD is able to perform 10GBASE-ER                 | R0      | 0             |

|           |                      | 0 = PMA/PMD is not able to perform 10GBASE-ER             |         |               |

| 1.8.4     | 10GBASE-LX4 ability  | 1 = PMA/PMD is able to perform 10GBASE-LX4                | R0      | 0             |

| 100       | 1000105 011/ 1111    | 0 = PMA/PMA is not able to perform 10GBASE-LX4            |         |               |

| 1.8.3     | 10GBASE-SW ability   | 1 = PMA/PMD is able to perform 10GBASE-SW                 | RO      | 0             |

| 400       | 4000405 114/ 117     | 0 = PMA/PMD is not able to perform 10GBASE-SW             |         | •             |

| 1.8.2     | 10GBASE-LW ability   | 1 = PMA/PMD is able to perform 10GBASE-SW                 | R0      | 0             |

| 1.0.1     | 1000 100 514/ 1:17   | 0 = PMA/PMD is not able to perform 10GBASE-LW             | DO.     | 0             |

| 1.8.1     | 10GBASE-EW ability   | 1 = PMA/PMD is able to perform 10GBASE-EW                 | R0      | 0             |

| 100       | DMA I                | 0 = PMA/PMD is not able to perform 10GBASE-EW             | DO.     | 1             |

| 1.8.0     | PMA loopback ability | 1 = PMA has the ability to perform a loopback function    | R0      | 1             |

|           |                      | 0 = PMA does not have the ability to perform a loopback   |         |               |

|           |                      | function                                                  |         |               |

# Register 1.9 - 10 G PMD Transmit Disable

| Bit(s)   | Name                 | Description          | R/W¹ | Default Value |

|----------|----------------------|----------------------|------|---------------|

| 1.9.15:5 | Reserved             | N/A                  | RW   |               |

| 1.9.4:1  | LX4 Signal Detect    | Not used             | RW   | 0             |

| 1.9.4:0  | PMD Transmit Disable | 1 = Transmit disable | RW   | 0             |

|          |                      | 0 = Transmit enable  |      |               |

#### Note:

<sup>1.</sup> RW = Read/Write, RO = Read Only, LH = Latch High, clear on read (note that if the condition exitsts following register read, the bit will not be cleared).

# Register 1.10 - 10 G PMD Receive Signal OK

| Bit(s)    | Name               | Description                        | R/W¹ | Default Value |

|-----------|--------------------|------------------------------------|------|---------------|

| 1.10.15:5 | Reserved           | Value always 0, writes ignored     | RO   |               |

| 1.10.4:1  | LX4 Signal Detect  | Not used                           | R0   |               |

| 1.10.0    | Global PMD Receive | 1 = Signal detected on receive     | RO   |               |

|           | signal detect      | 0 = Signal not detected on receive |      |               |

# Register 1.14 to 1.15 - Package Identifier (OUI)

| Bit(s)     | Name               | Description     | R/W¹ | Default Value |

|------------|--------------------|-----------------|------|---------------|

| 1.15.15    | Reserved           | Reserved        | RO   | 248           |

| 1.15.14:11 | Revision Number    | Revision Number | RO   |               |

| 1.15.11:8  | NVR Address        | NVR DEV Address | RO   |               |

| 1.15.7:6   | NVR Address        | NVR DEV Address | RO   |               |

| 1.15.5:0   | Package Identifier | XENPAK OUI      | RO   |               |

| 1.14.15:8  | Package Identifier | XENPAK OUI      | RO   | 34            |

| 1.14.7:0   | Package Identifier | XENPAK OUI      | RO   |               |

# Register 1.32768 - NVR Control/Status

| Bit(s)       | Name                            | Description                         | R/W¹            | Default Value |

|--------------|---------------------------------|-------------------------------------|-----------------|---------------|

| 1.32768.15:9 | Vendor Specific                 |                                     | RW              |               |

| 1.32768.7:6  | Reserved                        | N/A                                 | RO              |               |

| 1.32768.5    | Read/Write Command <sup>3</sup> | 0 = Read NVR                        | RW <sup>2</sup> |               |

|              |                                 | 1 = Write NVR                       |                 |               |

| 1.32768.4    | Reserved                        | N/A                                 | R0              |               |

| 1.32768.3:2  | Command Status                  | 00 = Idle                           | RO/LH           |               |

|              |                                 | 01 = Command completed successfully |                 |               |

|              |                                 | 10 = Command in progress            |                 |               |

|              |                                 | 11 = Command failed                 |                 |               |

| 1.32768.1:0  | Extended Commands               | 00 = Reserved                       | $RW^2$          |               |

|              |                                 | 01 = Reserved                       |                 |               |

|              |                                 | 10 = Read/Write 1 byte              |                 |               |

|              |                                 | 11 = Read all NVR contents          |                 |               |

# 1.32775 to 1.32782 - NVR Information

| Bit(s)      | Name          | Description                            | R/W¹ | Default Value (dec) |

|-------------|---------------|----------------------------------------|------|---------------------|

| 1.32775.7:0 | Version       | NVR Version number (MSB:LSB)           | RO   | 30                  |

| 1.32776.7:0 | NVR_Size      | NVR Size (upper byte) = 256 bytes      | R0   | 1                   |

| 1.32777.7:0 | NVR_Size      | NVR Size (lower byte) = 256 bytes      | RO   | 0                   |

| 1.32778.7:0 | Mem_Used      | Bytes used (upper byte) = 256 bytes    | R0   | 1                   |

| 1.32779.7:0 | Mem_Used      | Bytes used (lower byte) = 256 bytes    | R0   | 0                   |

| 1.32780.7:0 | Basic Addr    | Basic Field Address (MSB:LSB) Start    | R0   | 11                  |

| 1.32781.7:0 | Cust Addr     | Customer Field Address (MSB:LSB) Start | R0   | 119                 |