# FM24164 FRAM® Serial Memory

Product Preview\*

## **Features**

- 16Kbit Nonvolatile Ferroelectric RAM Organized as 2,048 x 8

- Very Low Power CMOS Technology

- 100µA Active (Read or Write)

- 25µA Standby Over Commercial Temperature Range

- Reliable Thin Film Ferroelectric Technology

- 10 Billion (1010) Cycle Read/Write Endurance

- 10 Year Data Retention

- High Performance

- No Write Delay

- 2Kbyte Sequential Write

- Two Wire I<sup>2</sup>C Serial Interface

- 100KHz and 400KHz Modes

- Direct Replacement for Xicor X24164

- Three Device Selects Allow Up to Eight Devices to Share a Common Two Wire Bus

- Hardware Write Protection

- True 5V Only Operation

- 8-Pin Mini DIP and SOIC Packages

- -40° to +85°C Operating Range

# **Description**

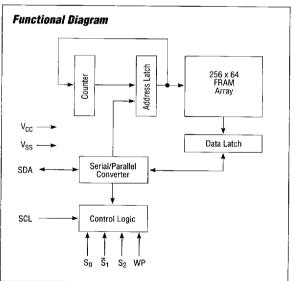

Ramtron's FM24164 ferroelectric random access memory, or FRAM® memory provides nonvolatile data integrity in a compact package. A two wire serial interface provides access to any byte within the memory while reducing the cost of the processor interface. The FM24164 is useful in a wide variety of applications for the storage of configuration information, user programmable data/features, and calibration data.

With Ramtron's ferroelectric technology, all writes are nonvolatile, eliminating long delays, extra page mode control, or high voltage pins. The technology is designed for highly reliable operation, offering extended endurance and 10 year data retention.

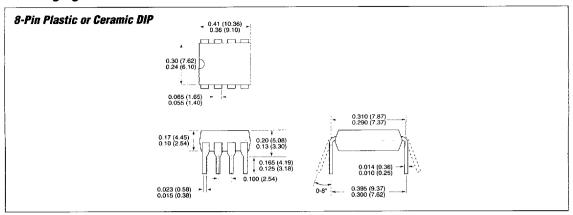

The part uses the industry standard two wire protocol for serial chip communication and is pin compatible with a number of parts from other vendors. It is available in 300 mil mini-DIP and 150 mil SOP packages.

| Pin Configurations                                    |     |  |

|-------------------------------------------------------|-----|--|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | SOP |  |

#### Pin Names

| Pin Names             | Function             |   |

|-----------------------|----------------------|---|

| $S_0, \bar{S}_1, S_2$ | Device Select Inputs |   |

| SDA                   | Serial Data/Address  |   |

| SCL                   | Serial Clock         |   |

| WP                    | Write Protect        |   |

| V <sub>SS</sub>       | Ground               |   |

| V <sub>CC</sub>       | Supply Voltage       | - |

1-41

<sup>\*</sup>This document describes a product under development. Ramtron reserves the right to change or discontinue this product without notice.

<sup>© 1994</sup> Ramtron International Corporation 1850 Ramtron Drive, Colorado Springs, CO 80921 Telephone (800) 545-FRAM, (719) 481-7000 Fax (719) 488-9095 R1 June 1994

## **Absolute Maximum Ratings**

| Description                                                                        | Ratings        |

|------------------------------------------------------------------------------------|----------------|

| Ambient Storage or Operating Temperature to Guarantee Nonvolatility of Stored Data | -40°C to +85°C |

| Voltage on Any Pin with Respect to Ground                                          | -1.0 to +7.0V  |

| D.C. Output Current                                                                | 5mA            |

| Lead Temperature (Soldering, 10 Seconds)                                           | 300°C          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Operating Conditions**

$T_A = -40$  °C to +85 °C,  $V_{CC} = 5.0V \pm 10\%$ , Unless Otherwise Specified

| Symbol                         | Parameter                      | Min                   | <i>Typ</i> <sup>(1)</sup> | Max                   | Units | Test Conditions                                                                                              |

|--------------------------------|--------------------------------|-----------------------|---------------------------|-----------------------|-------|--------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>                | Power Supply Voltage           | 4.5                   | 5.0                       | 5.5                   | ٧     |                                                                                                              |

| I <sub>CC</sub>                | V <sub>CC</sub> Supply Current |                       | 60                        | 100                   | μА    | SCL @ 100KHz, Read or Write<br>SCL CMOS Levels, All Other Inputs = V <sub>SS</sub> or V <sub>CC</sub> - 0.3V |

| lcc                            | V <sub>CC</sub> Supply Current |                       | 180                       | 300                   | μA    | SCL @ 400KHz, Read or Write SCL CMOS Levels, All Other Inputs = $V_{SS}$ or $V_{CC}$ - 0.3V                  |

| I <sub>SB</sub> <sup>(2)</sup> | Standby Current 0 to 70°C      |                       | 8                         | 25                    | μA    | SCL = SDA = $V_{CC}$ , All Other Inputs = $V_{SS}$ or $V_{CC}$                                               |

| I <sub>SB</sub> <sup>(2)</sup> | Standby Current -40 to 85°C    |                       | 16                        | 60                    | μA    | SCL = SDA = $V_{CC}$ , All Other Inputs = $V_{SS}$ or $V_{CC}$                                               |

| LI                             | Input Leakage Current          |                       |                           | 10                    | μА    | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>CC</sub>                                                         |

| I <sub>LO</sub>                | Output Leakage Current         |                       |                           | 10                    | μА    | V <sub>OUT</sub> = V <sub>SS</sub> to V <sub>CC</sub>                                                        |

| VIL                            | Input Low Voltage              | -1.0                  |                           | V <sub>CC</sub> x 0.3 | ٧     |                                                                                                              |

| V <sub>IH</sub>                | Input High Voltage             | V <sub>CC</sub> x 0.7 |                           | V <sub>CC</sub> + 0.5 | ٧     |                                                                                                              |

| V <sub>OL1</sub>               | Output Low Voltage             |                       |                           | 0.4                   | ٧     | I <sub>OL</sub> = 3mA                                                                                        |

| V <sub>OL2</sub>               | Output Low Voltage             |                       |                           | 0.6                   | ٧     | I <sub>OL</sub> = 6mA                                                                                        |

| V <sub>HYS</sub> (3)           | Input Hysteresis               | V <sub>CC</sub> x .05 |                           |                       | ٧     |                                                                                                              |

Unite

- (1) Typical values are measured at 25°C, 5.0V

- (2) Must perform a stop command prior to measurement.(3) This parameter is periodically sampled and not 100% tested.

- Endurance and Data Retention

| Lindbidiioo diid batt |     |     |  |

|-----------------------|-----|-----|--|

| Parameter             | Min | Max |  |

|                       |     |     |  |

| 0 Billion | R/W Cycles |

|-----------|------------|

| 10        | Years      |

|           |            |

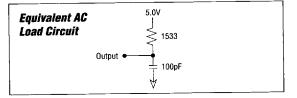

## **AC Conditions of Test**

Capacitance

| AC Conditions                  | Test                                           |  |

|--------------------------------|------------------------------------------------|--|

| Input Pulse Levels             | V <sub>CC</sub> x 0.1 to V <sub>CC</sub> x 0.9 |  |

| Input Rise and Fall Times      | 10ns                                           |  |

| Input and Output Timing Levels | V <sub>CC</sub> x 0.5                          |  |

## Power-Up Timing (4)

| Symbol    | Symbol Parameter            |   | Units |

|-----------|-----------------------------|---|-------|

| t PUR (4) | Power Up to Read Operation  | 1 | μs    |

| t PUW (4) | Power Up to Write Operation | 1 | μs    |

(4)  $t_{\rm FUR}$  and  $t_{\rm FUR}$  are the delays required from the time  $V_{\rm CC}$  is stable until the specified operation can be initiated. These parameters are periodically sampled and not 100% tested.

$T_A = 25$ °C, f = 1.0MHz,  $V_{CC} = 5$ V

| Symbol               | Test                           | Мах | Units | Conditions            |

|----------------------|--------------------------------|-----|-------|-----------------------|

| C <sub>1/0</sub> (3) | Input/Output Capacitance (SDA) | 8   | pF    | V <sub>I/O</sub> = 0V |

|                      | Input Capacitance (SCL, WP)    | 6   | pF    | V <sub>IN</sub> = 0V  |

(3) This parameter is periodically sampled and not 100% tested.

1-42

7555015 0000344 575

# 5

## Pin Descriptions

#### SCL — Serial Clock

When high, the SCL clocks data into and out of the FM24164. It is an input only. This input is built with a Schmitt trigger to provide increased noise immunity.

#### SDA — Serial Data Address

This bi-directional pin is used to transfer addresses to the FM24164 and data to or from the FM24164. It is an open drain output and intended to be wire-ORed with all other devices on the serial bus using an external pull-up resistor. The input circuitry on this pin is built with a Schmitt trigger to reduce noise sensitivity. The output section incorporates slope control for the falling edges.

#### WP — Write Protect

If tied to  $V_{CC}$ , write operations into the upper half of the memory (page select  $A_2$  set to 1 in the slave address) will be disabled. Read and write operations to the lower portion of memory will proceed normally. If the write protection feature is not desired, this pin must be tied to  $V_{SS}$ .

## **Bus Protocol**

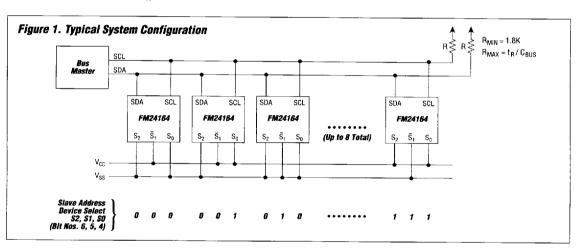

The FM24164 employs a bi-directional two wire bus protocol requiring a minimum of processor I/O pins. Figure 1 shows a typical system configuration connecting a microcontroller with eight FM24164 devices.

By convention, any device sending data onto the bus is the transmitter, while the device that is getting the data is the receiver. The device controlling the bus is the master and provides the clock signal for all operations. Devices being controlled are the slaves. The FM24164 is always a slave device.

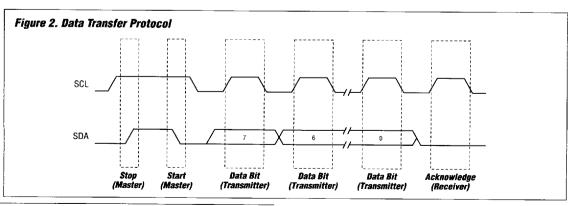

Transitions or states on the SDA and SCL lines denote one of four conditions: a start, stop, data bit, or acknowledge. Figure 2 shows the signaling for these conditions, while the following four sections describe their function.

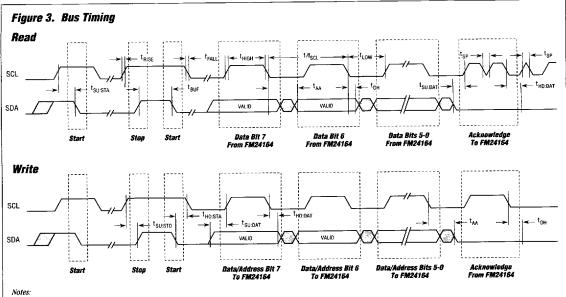

Figure 3 shows the detailed timing specifications for the bus. Note that all SCL specifications and the *start* and *stop* specifications apply to both read and write operations. They are shown on one or the other for clarity. Also, the write timing specifications apply to all transmissions to the FM24164, including the slave and word address, as well as write data sent to the FM24164 from the bus master

1-43

All start and stop timings apply to both read and write cycles identically.

Clock specifications are the same for both read and write.

Write timing specifications apply to slave address, word address, and write data.

These timing diagrams provide representative timing relationships of the signals. They are not intended to provide functional relationships between the signals. These are provided in Figures 5 through 9.

### Read and Write Cycle AC Parameters

$T_A = -40$  °C to +85 °C,  $V_{CC} = 5.0V \pm 10\%$ , Unless Otherwise Specified

| Symbol                | Parameter                                                     | Sta | andard Mode | Fä                                  | Units |       |

|-----------------------|---------------------------------------------------------------|-----|-------------|-------------------------------------|-------|-------|

|                       |                                                               | Min | Мах         | Min                                 | Max   | Uints |

| f <sub>SCL</sub>      | SCL Clock Frequency                                           | 0   | 100         | 0                                   | 400   | KHz   |

| t <sub>SP</sub>       | Noise Suppression Time Constant at SCL, SDA Inputs            |     | 50          |                                     | 50    | ns    |

| t <sub>AA</sub>       | SCL Low to SDA Data Out Valid                                 |     | 3           |                                     | 0.9   | μs    |

| t <sub>BUF</sub>      | Time the Bus Must Be Free Before a New Transmission Can Start | 4.7 |             | 1.3                                 |       | μs    |

| t <sub>HD:STA</sub>   | Start Condition Hold Time                                     | 4.0 |             | 0.6                                 |       | μs    |

| t <sub>LOW</sub>      | Clock Low Period                                              | 4.7 |             | 1.3                                 |       | μs    |

| tHIGH                 | Clock High Period                                             | 4.0 |             | 0.6                                 |       | μs    |

| t <sub>SU:STA</sub>   | Start Condition Setup Time (for a Repeated Start Condition)   | 4.7 |             | 0.6                                 |       | μs    |

| t <sub>HD:DAT</sub>   | Data In Hold Time                                             | 0   |             | 0                                   |       | ns    |

| t <sub>SU:DAT</sub>   | Data In Setup Time                                            | 250 |             | 100                                 |       | ns    |

| t <sub>RISE</sub> (3) | SDA and SCL Rise Time                                         |     | 1000        | 20+0.1C <sub>b</sub> <sup>(5)</sup> | 300   | ns    |

| t <sub>FALL</sub> (3) | SDA and SCL Fall Time                                         | -   | 300         | 20+0.1C <sub>b</sub> <sup>(5)</sup> | 300   | ns    |

| t <sub>SU:STO</sub>   | Stop Condition Setup Time                                     | 4.0 |             | 0.6                                 |       | μs    |

| t <sub>DH</sub>       | Data Out Hold Time (From SCL @ V <sub>IL</sub> )              | 0   |             | 0                                   |       | ns    |

| t <sub>OF</sub>       | Output Fall Time (VIH Min to VIL Max)                         |     | 250         | 20+0.1C <sub>b</sub> <sup>(3)</sup> | 250   | ns    |

<sup>(3)</sup> This parameter is periodically sampled and not 100% tested.

1-44

7555015 0000346 348 📟

<sup>(5)</sup> C<sub>b</sub> = Total Capacitance of One Bus Line in pF.

#### Start Condition

A start condition is indicated to the FM24164 when there is a high to low transition of SDA while SCL is high. All commands to the FM24164 must be preceded by a start. In addition, a start condition occurring at any point within an operation will abort that operation and ready the FM24164 to start a new one.

## Stop Condition

A *stop* condition is indicated to the FM24164 when there is a low to high transition of SDA while SCL is high. All operations to the FM24164 should end with a *stop*. In addition, any operation will be aborted at any point when this condition occurs.

#### Data/Address Transfers

Data/address transfers take place during the period when SCL is high. Except under the two conditions described above, the state of the SDA line may not change while SCL is high. Address transfers are always sent to the FM24164, while data transfers may either be sent to the FM24164 (for a write) or to the bus master (for a read).

#### Acknowledge

Acknowledge transfers take place on the ninth clock cycle after each eight-bit address or data transfer. During this clock cycle, the transmitter will release the SDA bus to allow the receiver to drive the bus low to acknowledge receipt of the byte.

If the receiver does not acknowledge any byte, the operation is aborted.

## **Device Operation**

#### Low Voltage Protection

When powering up, the FM24164 will automatically perform an internal reset and await a start signal from the bus master. The bus master should wait  $T_{PUR}$  (or  $T_{PUW}$ ) after  $V_{CC}$  reaches 4.5V before issuing the start for the first read or write access. Additionally, whenever  $V_{CC}$  falls below 3.5V (typical), the part goes into its low voltage protection mode. In this mode, all accesses to the part are inhibited and the part performs an internal reset. If an access was in progress when the power supply fails, it will be automatically aborted by the FM24164. When power rises back above 4.5V, a start signal must be issued by the bus master to initiate an access.

#### Slave Address

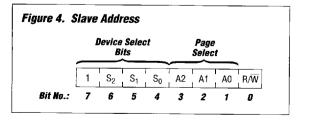

Following a *start*, the FM24164 will expect a slave address byte to appear on the bus (see Figure 4).

- Bit 7 is a binary 1.

- Bits 4, 5, and 6 are the device select bits. A system can have up to eight FM24164 devices on a single I²C bus. The eight addresses are defined by the state of the S<sub>0</sub>, /S<sub>1</sub>, and S<sub>2</sub> inputs (pins 1, 2, and 3). A device is selected when the device select bits (4 and 6) of the slave address match the state of the input pins 1 and 3, and bit 5 of the slave address matches the inverse of pin 2.

- Bits 1 through 3 are the page select bits. They select which 256-byte block of memory will be accessed by this operation.

- Bit 0 is the read/write bit. If set to a 1, a read operation is being performed by the master; otherwise, a write is intended.

### **Word Address**

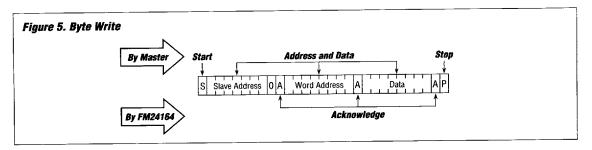

After a slave device *acknowledges* the slave address on a write operation, the master will place the word address on the bus. This byte, in addition to the three page select bits from the slave address byte, forms the address of the byte within the memory that is to be written. This 11-bit value is latched in the internal address latch. There is no word address specified during a read operation, although the upper three bits of the internal latch are set to the page select values in the slave address.

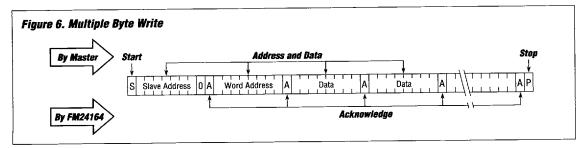

During the transmission of each data byte and before the acknowledge cycle, the address in the internal latch is incremented to allow the following byte to be accessed immediately. When the last byte in the memory is accessed (at address hex 7FF), the address is reset to 0. There is no alignment requirement for the first byte of a block cycle — any address may be specified. There is also no limit to the number of bytes that may be accessed in a single read or write operation.

#### Data Transfer

After all address bytes have been transmitted, data will be transferred between the FM24164 and the bus master. In the case of a read, the FM24164 will place each of the eight bits on the bus and then wait for an acknowledge from the bus master before performing a read on the subsequent address. For a write operation, the FM24164 will accept eight bits from the bus master and then drive the acknowledge on the bus.

All data and address bytes are transmitted most significant bit (bit 7) first.

After the acknowledge of a data byte transfer, the bus master may either begin another read or write on the subsequent byte, issue a *stop* command to terminate the block operation, or issue a *start* command to terminate the current operation and start a new one.

1-45

7555015 0000347 284

## Write Operations

All write operations start with a slave and word address transmission to the FM24164. In the slave address, bit 0 should be set to a 0 to denote a write operation. After they are acknowledged, the bus master transmits each data byte(s) to the FM24164. After each byte, the FM24164 will generate an acknowledge signal. Any number of bytes may be written in a single write sequence. After the last byte in the memory (address hex 7FF) is written, the address counter wraps around to zero so that the subsequent byte written will be the first (address 0).

There is no write delay on the FM24164. Any operation, either a read or write to some other address, may immediately follow a write. Acknowledge polling, a sequence used with EEPROM devices to let the bus master know when a write cycle is complete, will

return done immediately (the FM24164 will acknowledge the first correct slave address).

If a write cycle must be aborted (with a *start* or *stop* condition), this should take place *before* the transmission of the eighth bit in order that the memory not be altered.

The write protect (WP) pin on the FM24164 allows the upper half of the memory array (addresses hex 400 through 7FF) to be protected against accidental modification. When the pin is tied to  $V_{\rm CC}$ , slave and word addresses targeted at the FM24164 will still be acknowledged, but no acknowledge will occur on the data cycle if the address is in the upper half. In addition, no address incrementing occurs when writes are attempted to this half of the memory. If the write protection feature is not desired, this pin must be tied to  $V_{\rm SS}$ .

## Read Operations

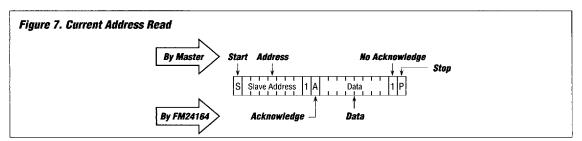

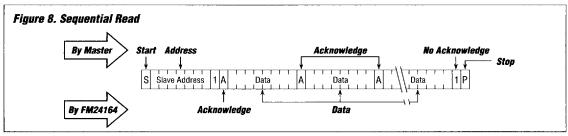

#### **Current Address or Sequential Read**

Sequential read operations take place from the address currently held in the internal address latch, and so require only that the bus master provide a slave address transfer before the FM24164 begins the transfer of data to the master. In this slave address, bit 0 should be set to a 1 to denote a read operation. Note that the most significant three bits of the 11-bit internal address latch are specified by the slave address word, and are therefore adways set during a read, regardless of which page the previous access referenced.

One or multiple bytes may be read from the FM24164 in a single read operation. In a multi-byte read, each acknowledge from the bus master indicates to the slave that another byte is being requested.

The read operation must be properly terminated after the final 8-bit byte has been read. The bus master can end the read sequence in one of four ways:

- (1) The first and recommended way is for the bus master to issue a no acknowledge in the ninth clock cycle and a stop in the tenth clock cycle. This is shown in Figures 7 through 9.

- (2) The second method is for the bus master to issue a no acknowledge in the ninth clock cycle and a start in the tenth clock cycle.

- (3) The bus master issues a stop in the ninth clock cycle.

- (4) The bus master issues a start in the ninth clock cycle.

After the last byte in the memory (address hex 7FF) is read, the address counter wraps around to zero so that the subsequent byte to be read will be the first location in the memory (address 0). These sequences are shown below in Figures 7 and 8.

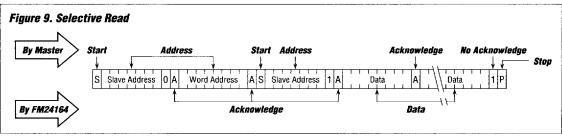

## Selective (Random) Read

Selective, or random, read operations are possible on the FM24164 by using the first two bytes of the write operation to load the internal address. The slave address for the part is sent out with bit 0 ( $R\overline{W}$ ) set to 0 to denote a write operation, and the word address is set to specify the least significant 8 bits of the desired address.

After the FM24164 acknowledges this word address, the bus master should abort the *write* and begin the read with a *start* command. A new slave address is then sent out, this time with the  $R/\overline{W}$  bit set to 1. Following the slave address and acknowledge, the FM24164 will immediately begin transmission of the requested data. Figure 9 shows this operation.

1-47

7555015 0000349 057

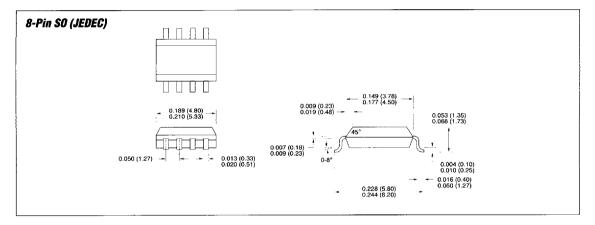

## **Packaging Information**

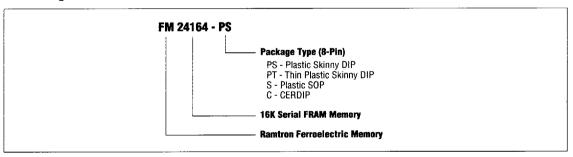

# **Ordering Information**

Ramtron International Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Ramtron product, nor does it convey or imply any license under patent or other rights.

FRAM is a Registered Trademark of Ramtron International Corporation.

© Copyright 1994 Ramtron International Corporation.

1-48

**7555015 0000350 879 🗯**