## HA166102FP, HA166104FP HA166102T, HA166104T Read/Write Amplifier for Hard Disk Drive

# **<b>OHITACHI**

Type

Preliminary Rev. 0 Nov. 1991

**Package**

The HA166102FP, HA166104FP, HA166102T and HA166104T are read/write amplifiers designed for use with two-terminal recording heads. They have the following functions and features.

#### **Functions**

- · Read amplifier circuit

- · Write driver circuit

- · Write error detection circuit

- · Constant write current setup circuit

#### **Features**

- Single power supply +5 V

- · Low power

read: 150 mW (typ) idle: 5 mW (typ)

- Low Noise: 0.7 nV/√Hz (typ)

- Read amplifier has high differential voltage gain

250 V/V (typ)

- · Built-in current and voltage monitors

- TTL compatible interface

- · Emitter-follower read amplifier outputs

- Input capacitance: 22 pF (typ)Write current range: 10 to 30 mA

- Designed for two-terminal MIG or thin-film heads

| HA166102FP | 2 | FP-16DA  |

|------------|---|----------|

| HA166104FP | 4 | FP-20DA  |

| HA166102T  | 2 | TTP-20DA |

| HA166104T  | 4 | TTP-20DA |

Channel

**Ordering Information**

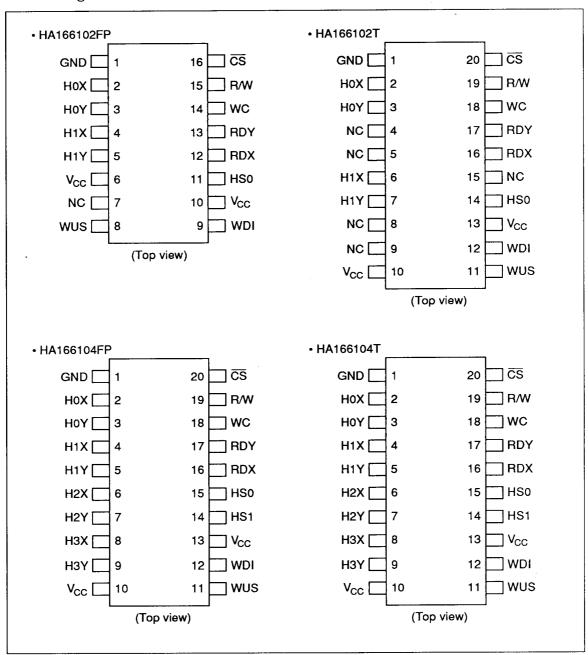

#### **Pin Arrangements**

### **Pin Description**

| Symbol          | Name                             | Description                                                                                                                                                   |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDX, RDY        | Read amplifier output            | Differential output pins for the read amp.  The signal read out from the head coil is amplified and provided on these pins.                                   |

| R/W             | R/W switch                       | Mode select switch for changing over the bias condition of the head coil                                                                                      |

|                 |                                  | A low level selects the write mode, while a high level selects the read mode.                                                                                 |

| CS              | Chip select                      | When this line is set high, the circuit goes into the standby state, a low power state. When this line is low, the chip is active.                            |

| HS0<br>HS1      | Head select 0<br>Head select 1   | Input pins for head select signals. The combination of these signals selects one head from head 0 to head 3.                                                  |

|                 |                                  | Refer to the head select table.                                                                                                                               |

| HoX, HoY        | Head 0X, 0Y                      | These pins are connected to the R/W head coil of channel 0.                                                                                                   |

| H1X, H1Y        | Head 1X, 1Y                      | These pins are connected to the R/W head coil of channel 1.                                                                                                   |

| H2X, H2Y        | Head 2X, 2Y                      | These pins are connected to the R/W head coil of channel 2.                                                                                                   |

| НЗХ, НЗҮ        | Head 3X, 3Y                      | These pins are connected to the R/W head coil of channel 3.                                                                                                   |

| WC              | Write current setting            | Write current setting pin. The write current is defined by the equation below by connecting the external resistance R <sub>WC</sub> between this pin and GND. |

|                 |                                  | Write current [mA] = $K/R_{WC}$ [k $\Omega$ ]                                                                                                                 |

| WDI             | Write data input                 | Write data input pin. The signal is devided in the IC, and drives the write driver.                                                                           |

| wus             | Write error<br>detection circuit | A high level output indicates the write error detection conditions.  WUS is high under the following conditions:                                              |

|                 | 23.33.13.11.3.1.30.1             | 1. Head short 2. Write current too small. 3. WDI input frequency too low.                                                                                     |

| V <sub>CC</sub> | 5 V                              | 5 V power supply                                                                                                                                              |

| GND             | Ground                           | Ground pins                                                                                                                                                   |

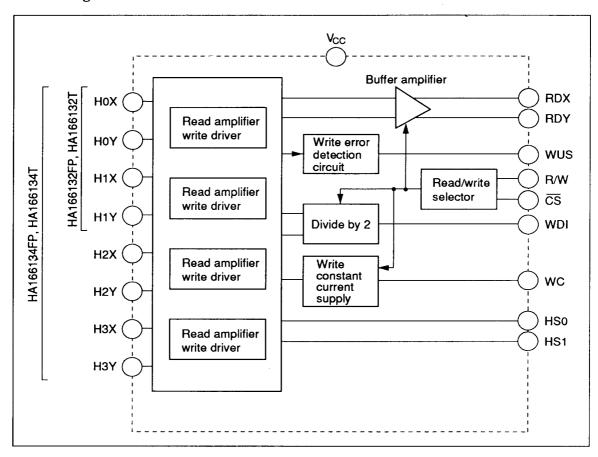

#### **Block Diagram**

#### **Absolute Maximum Ratings** (Ta = 25°C)

| Item                     | Symbol           | Rating          | Unit | Applicable Terminal    |

|--------------------------|------------------|-----------------|------|------------------------|

| Supply voltage           | V5               | -0.3 to +6.0    | V    | V <sub>CC</sub>        |

| Write current            | l <sub>W</sub>   | 35              | mA   |                        |

| Interface input voltage  | V <sub>IN</sub>  | -0.3 to V5 +0.3 | V    | HS0, HS1, WDI, R/W, CS |

| WUS voltage              | V <sub>WUS</sub> | 6.0             | V    | WUS                    |

| WUS output current       | lwus             | 12              | mA   | wus                    |

| Read data output current | I <sub>RO</sub>  | <b>–10</b>      | mA   | RDX, RDY               |

| Operating temperature    | Topr             | 0 to +70        | °C   |                        |

| Storage temperature      | Tstg             | -55 to +125     | °C   |                        |

### **Power Supply** ( $Ta = 25^{\circ}C$ )

| Item                 | Symbol          | Min  | Тур                 | Max                 | Unit    | Test Conditions                        |

|----------------------|-----------------|------|---------------------|---------------------|---------|----------------------------------------|

| Supply voltage range | V <sub>CC</sub> | 4.75 | 5.0                 | 5.25                | V       |                                        |

| +5 V supply current  | <b>I</b> 5      |      | 33                  | 45                  | mA      | Read mode<br>V <sub>CC</sub> = 5.25 V  |

|                      |                 |      | 21 + I <sub>W</sub> | 30 + I <sub>W</sub> | _       | Write mode<br>V <sub>CC</sub> = 5.25 V |

|                      |                 |      | 1.1                 | 3                   | <b></b> | Idle mode<br>V <sub>CC</sub> = 5.25 V  |

## Electrical Characteristics ( $V_{CC} = 5 \text{ V}$ , $Ta = 25^{\circ}\text{C}$ unless otherwise specified)

#### Digital Input

| Item                             | Symbol           | Min  | Тур | Max                   | Unit | Test Conditions            |

|----------------------------------|------------------|------|-----|-----------------------|------|----------------------------|

| Low level input voltage          | V <sub>IL</sub>  | -0.3 |     | 0.8                   | ٧    |                            |

| Low level input current          | l <sub>IL</sub>  | -100 |     | _                     | μА   | V <sub>IL</sub> = 0.8 V    |

| High level input voltage         | V <sub>IH</sub>  | 2.0  | ,   | V <sub>CC</sub> + 0.3 | ٧    |                            |

| High level input current         | I <sub>IH</sub>  |      |     | 100                   | μΑ   | V <sub>IH</sub> = 2.0 V    |

| Read/write transition time       | t <sub>RW</sub>  | -    |     | 1000                  | ns   |                            |

| Write/read transition time       | t <sub>WR</sub>  | _    |     | 1500                  | ns   |                            |

| Head select switching delay time | t <sub>HS</sub>  | -    |     | 1500                  | ns   | Read or write mode         |

| Chip disable transition time     | t <sub>IRW</sub> | -    |     | 12                    | μs   | R/W to Idle or Idle to R/W |

#### **Write Fault Detection**

| Item                      | Symbol          | Min          | Тур | Max | Unit        | · Test Conditions       |

|---------------------------|-----------------|--------------|-----|-----|-------------|-------------------------|

| Low level US voltage      | V <sub>OL</sub> | _            |     | 0.5 | V           | I <sub>OL</sub> = 8 mA  |

| High level US current     | l <sub>OH</sub> | <del>_</del> |     | 100 | μА          | V <sub>OH</sub> = 5.0 V |

| Unsafe to safe delay time | td <sub>2</sub> |              |     | 1.0 | μs          |                         |

| Safe to unsafe delay time | td <sub>1</sub> | 0.8          |     | 6.0 | <del></del> |                         |

#### **Head Select Table**

#### **Mode Select Table**

| HS1 | HS0 | Head Selected | <del>cs</del> | R/W | Mode  |

|-----|-----|---------------|---------------|-----|-------|

| L   | L   | 0             | L             | L   | Write |

|     | Н   | 1             |               | Н   | Read  |

| Н   | L   | 2             | Н             | L   | ldle  |

|     | Н   | 3             |               | Н   |       |

#### **Read Amplifier**

| Item                        | Symbol           | Min  | Тур  | Max          | Unit               | Test Conditions                                                                                 |

|-----------------------------|------------------|------|------|--------------|--------------------|-------------------------------------------------------------------------------------------------|

| Differential voltage gain   | Avd              | 220  | 250  | 280          | V/V                | f = 300 kHz                                                                                     |

| Bandwidth                   | V <sub>W</sub>   | 40   | 70   |              | MHz                | -3 dB                                                                                           |

| Input noise voltage         | Vn               |      | 0.7  | 0.85         | nV/√ <del>Hz</del> | f ≤ 15 MHz,<br>Inputs shorted                                                                   |

| Common mode rejection ratio | CMRR             | 60   | 80   |              | dB                 |                                                                                                 |

| Power supply stability      | PSRR             | 45   | 60   | _            |                    | $V_{CC} \pm 100 \text{ mVpp,}$<br>f = 5 MHz                                                     |

| Channel separation          | Sep              | 60   | 80   | _            |                    | Vin = 100 mVpp on<br>unselected channels and<br>Vin = 0 mVpp on selected<br>channels, f = 5 MHz |

| Output offset voltage       | Vo               | -300 | _    | 300          | mV                 | Inputs shorted                                                                                  |

| Differential input          | Rin              |      | 1.1  | _            | kΩ                 | f = 300 kHz                                                                                     |

| impedance                   |                  |      | 0.85 | _            | •                  | f = 5 MHz                                                                                       |

| Common mode output voltage  | Vocm             | 2.0  | 2.5  | 3.0          | V                  |                                                                                                 |

| Output source current       | I <sub>ODR</sub> | _    | -10  | _            | mA                 |                                                                                                 |

| Output sink current         | IOSDR            | 1.7  | 2.2  | <del>-</del> | ·                  |                                                                                                 |

#### **Write Driver**

| Item                                    | Symbol             | Min  | Тур  | Max  | Unit | Test Conditions                                  |

|-----------------------------------------|--------------------|------|------|------|------|--------------------------------------------------|

| Write current setting range             | l <sub>W</sub>     | 10   | _    | 30   | mA   |                                                  |

| Head current rise time                  | thex               | _    | 6    | 20   | ns   | Lh = 0 μH, Rh = 0 $\Omega$ ,<br>10% to 90% point |

| Head current switching delay time       | td <sub>3</sub>    | _    | 12   | 35   |      | Rh = 0 $\Omega$ , Lh = 0 $\mu$ H, from 50% point |

| Head current switching symmetry         | td <sub>4</sub>    | _    | _    | 1    |      | WDI duty cycle = 50%, rise/fall time = 1 ns      |

| WDI minimum input frequency             | fw                 | 1.8  |      | _    | MHz  | WUS = low                                        |

| Head current gain                       | lh/l <sub>WC</sub> |      | 20   | _    | _    | Head current/lwc                                 |

| WC output voltage                       | V <sub>wc</sub>    | _    | 1.35 | _    | ٧    |                                                  |

| Write current determination coefficient | K                  | 24.8 | 27   | 29.2 | _    |                                                  |

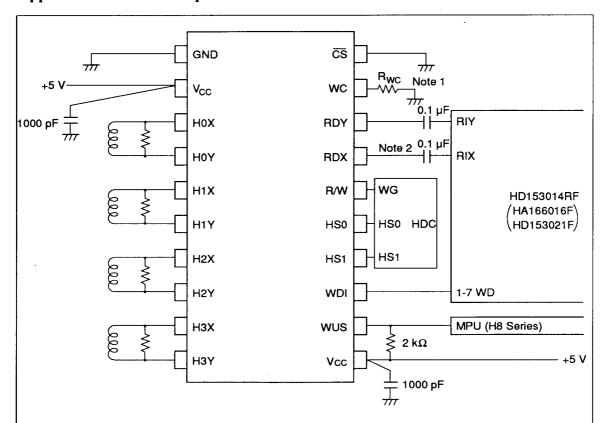

#### **Application Circuit Example**

Notes: 1. External resistance value  $R_{\mbox{WC}}$  is determined by following equation.

$$R_{WC}[k\Omega] = \frac{27 \text{ (typ)}}{\text{Write current [mA]}}$$

Also, write current ringing on changeover between read and write can be suppressed by locating the resistor  $R_{WC}$  as close as possible to the WC pin.

2. When the length of the wiring pattern increases, the RDX and RDY outputs might have some oscillation. This oscillation can be eliminated by inserting series resistors on these outputs as close to the pins as possible.

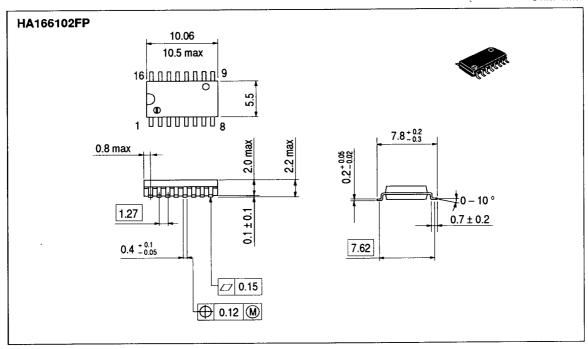

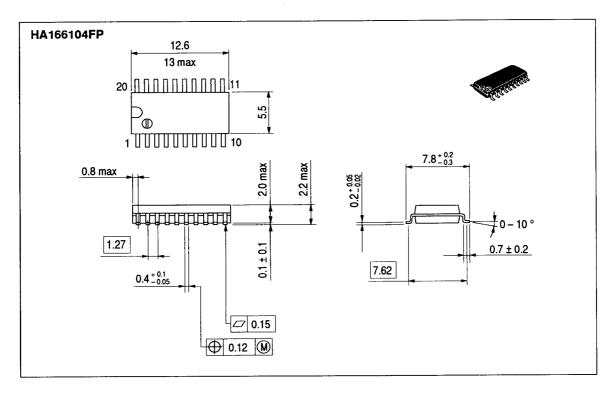

#### **Package Dimensions**

Unit: mm

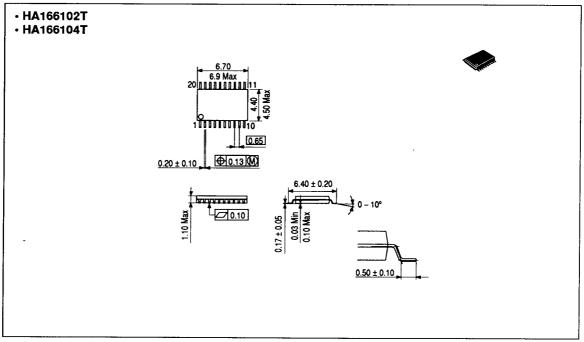

### Package Dimensions (cont)

Unit: mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

#### Hitachi, Ltd.

Semiconductor & IC Div.

Karukozaka MN Bldg., 2-1, Ageba-cho, Shinjuku-ku, Tokyo 162, Japan

Tel: Tokyo (03) 3266-9376 Fax: (03) 3235-2375

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1819

USA Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Div. Central Europe Headquarters Hans-Pinsel-Straße 10A 8013 Haar bei München F. R. Germany Tel: 089-46140

Fax: 089-463068

Hitachi Europe Ltd. Electronic Components Div. Northern Europe Headquarters Wihtebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA United Kingdom Tel: 0628-585000

Fax: 0628-778322

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsimshatsui, Kowloon Hona Kona Tel: 852-7359218

Fax: 852-7306071

11

SEP 0 5 1992

ADE-207-050 (H) Printed in Japan 030513 ¥ \_