# CMOS 16-Bit

# Microprogrammed ALU

#### **Features**

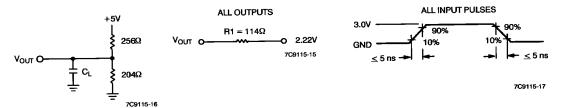

- Fast

- 35-ns worst-case propagation delay, I to Y

- Low power CMOS

- I<sub>CC</sub> (max. at 10 MHz) = 145 mA (commercial)

- —I<sub>CC</sub> (max. static) = 68 mA (commercial)

- V<sub>CC</sub> margin 5V ±10%

- All parameters guaranteed over commercial and military operating temperature range

- Instruction set and architecture optimized for high-speed controller applications

- CY7C9117 separate I/O

- One and two operand arithmetic and logical operations

- Bit manipulation, field insertion/ extraction instructions

- Eleven types of instructions

- Immediate instruction capability

- 16-bit barrel shifter capability

- 32-word x 16-bit register file

- 8-bit status register

- Four ALU status bits

- --- Link bit and three user-definable status bits

- Capable of withstanding greater than 2001V static discharge voltage

Pin compatible and functionally equivalent to 29116, 29116A, 29C116, 29117, 29117A, 29C117

#### **Functional Description**

The CY7C9115, CY7C9116, and CY7C9117 are high-speed 16-bit microprogrammed Arithmetic and Logic Units (ALUs).

The architecture and instruction set of the devices are optimized for peripheral controller applications such as disk controllers, graphics controllers, communications controllers, and modems. When used with the CY7C517 multiplier, the CY7C9115, CY7C9116, and CY7C9117 also support microprogrammed processor applications.

### Functional Description (continued)

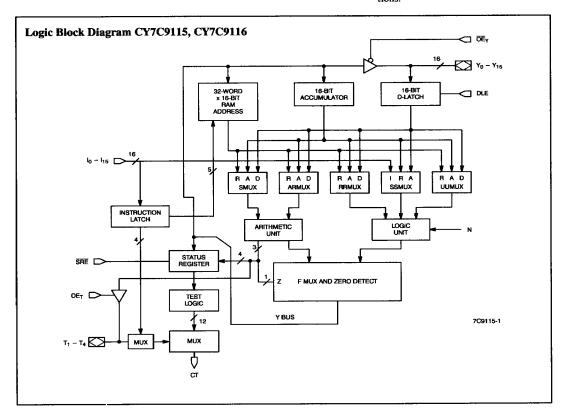

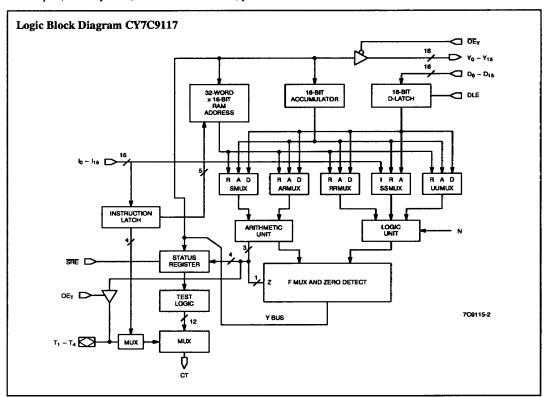

The CY7C9115, CY7C9116, and CY7C9117 (shown in the block diagrams) consist of a 32-word by 16-bit single-port RAM register file, a 16-bit arithmetic unit and logic unit, an instruction latch and decoder, a data latch, an accumulator register, a 16-bit barrel shifter, a priority encoder, a status register, a condition code generator and multiplexer, and three-state output buffers.

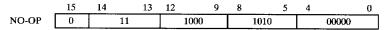

The instruction set of the CY7C9115, CY7C9116, and CY7C9117 can be divided into eleven instruction types: single-operand, two-operand, single-bit shifts, rotate and merge, rotate and compare, rotate by n-bits, bit-oriented instructions, priori-

tize, Cyclic Redundancy Check (CRC), status, and NO-OP. Instruction execution occurs in a single clock cycle except for Immediate Instructions, which require two clock cycles to execute.

The CY7C9116 and CY7C9117 are pin-compatible, functional equivalents of the industry-standard 29116, 29116A, 29C116, 29117, 29117A, and 29C117 with improved performance.

Fabricated in an advanced 1.2-micron, two-level metal CMOS process, the CY7C9115, CY7C9116, and CY7C9117 eliminate latch-up, have ESD protection greater than 2001V, and achieve superior performance with low power dissipation.

#### Selection Guide

|                        |            | 7C9115-35<br>7C9116-35<br>7C9117-35 | 7C9115-40, 45<br>7C9116-40, 45<br>7C9117-40, 45 | 7C9115-65<br>7C9116-65<br>7C9117-65 | 7C9115-79<br>7C9116-79<br>7C9117-79 |

|------------------------|------------|-------------------------------------|-------------------------------------------------|-------------------------------------|-------------------------------------|

| Worst-Case I - Y       | Commercial | 35                                  | 45                                              | 65                                  |                                     |

| Propagation Delay (ns) | Military   |                                     | 40                                              | 65                                  | 79                                  |

| Maximum Operating      | Commercial | 145                                 | 145                                             | 145                                 |                                     |

| Current @ 10 MHz (mA)  | Military   |                                     | 166                                             | 166                                 | 166                                 |

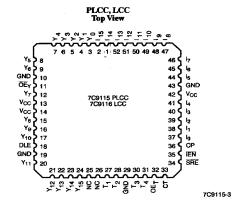

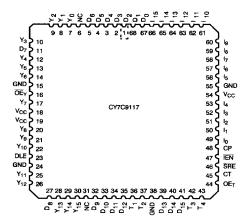

### **Pin Configurations**

# Pin Configurations (continued)

#### LCC/PLCC Top View

7C9115-7

#### 68 PGA Top View

|   |                | 51              | 49              | 47              | 45              | 44              | 42                | 40              | 38              | 36             |                |

|---|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|-----------------|----------------|----------------|

|   |                | D <sub>8</sub>  | Y <sub>14</sub> | GND             | D <sub>10</sub> | D <sub>11</sub> | T <sub>1</sub>    | GND             | D <sub>14</sub> | Тэ             |                |

| ſ | 53             | 52              | 50              | 48              | 46              | 43              | 41                | 39              | 37              | 35             | 34             |

|   | Y11            | Y <sub>12</sub> | Y <sub>13</sub> | ¥ <sub>15</sub> | Dg              | D <sub>12</sub> | T <sub>2</sub>    | D <sub>13</sub> | D <sub>15</sub> | T <sub>4</sub> | OΕτ            |

| ſ | 55             | 54              |                 | -               |                 |                 |                   |                 |                 | 33             | 32             |

| l | DLE            | GND             | L               |                 |                 |                 |                   |                 |                 |                | SRE            |

| ı | 57             | 56              |                 | Ī               |                 |                 |                   |                 |                 |                | 30             |

| l | Yg             | Y <sub>10</sub> |                 |                 | IEN             | CP-             |                   |                 |                 |                |                |

| ſ | 59             | 58              |                 |                 | 29              | 28              |                   |                 |                 |                |                |

|   | vcc            | Y <sub>8</sub>  |                 |                 |                 |                 |                   |                 | l <sub>0</sub>  | 4              |                |

| ſ | 60             | 61              |                 |                 | 26              | 27              |                   |                 |                 |                |                |

|   | NC             | Y <sub>7</sub>  |                 |                 | l <sub>3</sub>  | 12              |                   |                 |                 |                |                |

| ſ | 62             | 63              |                 |                 |                 |                 |                   |                 |                 | 25             | 24             |

| ı | ŌĒY            | GND             |                 |                 |                 |                 |                   |                 | lą.             | Vcc            |                |

|   | 64             | 65              |                 |                 |                 |                 |                   |                 |                 | 22             | 23             |

| l | Y <sub>6</sub> | Y <sub>5</sub>  |                 |                 |                 |                 |                   |                 | 15              | GND            |                |

| I | 66             | 67              |                 |                 |                 |                 |                   |                 |                 | 20             | 21             |

| l | Y4             | D <sub>7</sub>  |                 |                 |                 |                 |                   |                 |                 | 17             | l <sub>8</sub> |

| I | 68             | 49              | 51              | 53              | 55              | 57              | 12                | 14              | 16              | 18             | 19             |

| l | Y3             | Y <sub>2</sub>  | Yo              | D <sub>6</sub>  | D <sub>4</sub>  | D <sub>2</sub>  | l <sub>15</sub> . | 113             | 111             | lg             | le             |

|   |                | 50              | 52              | 54              | 56              | 58              | 59                | 13              | 15              | 17             |                |

|   | -              | Υ1              | GND             | D <sub>5</sub>  | D <sub>3</sub>  | D <sub>1</sub>  | D <sub>0</sub>    | 114             | 112             | 110            |                |

7C9115-6

#### **Description of Architecture**

The CY7C9115, CY7C9116, and CY7C9117 are 16-bit microprogrammed arithmetic and logic units comprised of the following sections (see block diagram):

- 32-Word x 16-Bit Register File

- Data Latch

- Instruction Latch and Decoder

- Accumulator

- Logic Unit with a 16-Bit Barrel Shift Capability

- Arithmetic Unit

- Priority Encoder

- Condition Code Generator and Multiplexer

- Status Register

- Output Buffers

#### 32-Word x 16-Bit Register File

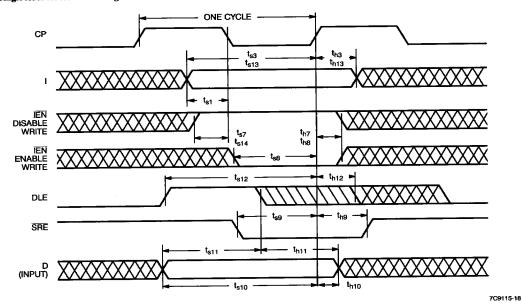

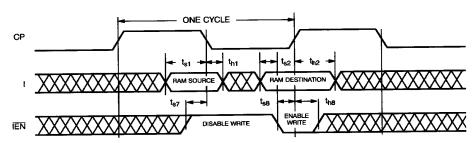

The 32-word x 16-bit register file is a single-port RAM with a 16-bit latch at the output. The latch is transparent while CP is HIGH and latched when CP is LOW. If IEN is LOW and the current instruction specifies the RAM at its destination, data is written into the RAM while CP is LOW. Word instructions write into all 16 bits of the RAM word addressed; byte instructions write into only the lower eight bits.

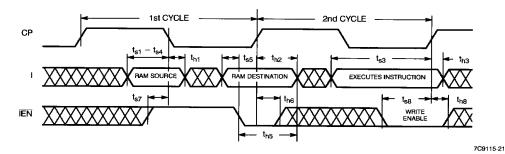

Use of an external multiplexer on five of the instruction inputs makes it possible to select separate read and write addresses for the same Non-immediate Instruction. Immediate Instructions do not allow this two-address operation for the 7C9115 and 7C9116. The 7C9117 does support two-address Immediate Instructions.

#### Data Latch

The data latch holds the 16-bit input to the CY7C9115, CY7C9116, and CY7C9117 from the Y (bidirectional) bus for the 7C9115 and 7C9116 and the data bus for the 7C9117. When DLE is HIGH, the latch is transparent, and it is latched when DLE is LOW.

#### Instruction Latch and Decoder

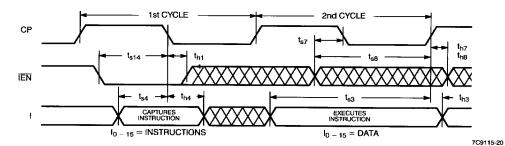

The 16-bit instruction latch is always transparent, except when Immediate Instructions are executed. The Instruction Decoder decodes the instruction inputs into the internal signals which control the CY7C9115, CY7C9116, and CY7C9117. All instructions other than Immediate Instructions execute in a single clock cycle.

Execution of Immediate Instructions takes two clock cycles. During the first clock cycle, the Instruction Decoder identifies the instruction as an Immediate Instruction and the Instruction Latch

| Static Discharge Voltage (Per MIL-STD-883 Method 3015) | >2001V  |

|--------------------------------------------------------|---------|

| Latch-Up Current (Outputs)                             | >200 mA |

## **Operating Range**

| Range                   | Ambient<br>Temperature | V <sub>CC</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ±10%         |

| Military <sup>[1]</sup> | - 55°C to +125°C       | 5V ±10%         |

#### Notes:

1. TA is the "instant on" case temperature.

captures the instruction at the instruction inputs. For Immediate Instructions, the data at the instruction inputs during the second clock cycle is used as one of the operands for the Immediate Instruction specified during the first clock cycle. Upon completion of the Immediate Instruction (the end of the second clock cycle), the Instruction Latch again becomes transparent.

#### Accumulator

The accumulator is a 16-bit edge-triggered register. If the IEN is LOW and the current instruction specifies the accumulator as its destination, the accumulator accepts Y-input data at the clock LOW-to-HIGH transition. Word instructions write into all 16 bits of the accumulator, byte instructions write into the lower eight bits.

#### 16-Bit Barrel Shifter

The barrel shifter can rotate data input to it from either the register file, the accumulator, or the data latch from 0 to 15 bit positions. In word mode, the barrel shifter rotates a 16-bit word; in byte mode, it only affects the lower eight bits. The barrel shifter is used as one of the ALU inputs.

#### **Arithmetic and Logic Unit**

The CY7C9115, CY7C9116, and the CY7C9117 have an arithmetic unit and a logic unit. The arithmetic unit is capable of operating on one or two operands while the logic unit is capable of operating on one, two, or three operands. The two units in parallel are able to execute the one and two operand instructions such as pass, complement, two's complement, add, subtract, AND, OR, EXOR, NAND, NOR, and EXNOR. Three operand instructions include rotate/merge and rotate/masked compare. There are three data types supported by the CY7C9115, CY7C9116, and CY7C9117; bit, byte, and 16-bit word.

All arithmetic and logic unit operations can be performed in either word or byte mode, with byte instructions performed only on the lower eight bits.

Three status outputs are generated by the arithmetic unit: carry (C), negative (N), and overflow (OVR). A zero flag (Z) detects a zero condition, though this flag is not generated by the arithmetic unit or the logic unit. These flags are generated in either word or byte mode, as appropriate.

The arithmetic unit uses full carry look-ahead across all 16 bits during arithmetic operations. The carry input to the arithmetic unit comes from the carry multiplexer, which can select either zero, one, or a stored carry bit (QC) from the status register. Multiprecision arithmetic uses QC as the carry input.

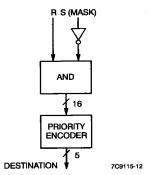

# **Description of Architecture** (continued) **Priority Encoder**

The priority encoder generates a binary-weighted code based on the location of the highest order ONE in its input word or byte. The operand to be prioritized may be ANDed with a mask to eliminate certain bits from the priority encoding. This masking is performed by the logic unit.

In word mode, the output is a binary one if bit 15 is the first (unmasked) HIGH encountered, a binary two if bit 14 is the first HIGH and so on. If bit 0 is the only HIGH, the output of the priority encoder is binary 16. If no bits are HIGH, a binary zero is output.

In byte mode, only bits 7 through 0 are examined. Bit 7 HIGH produces a binary one, bit 6 a binary two, and so on. If bit 0 is the only HIGH, a binary eight is output; if no bits are HIGH, a binary zero is output.

#### Condition Code Generator and Multiplexer

The twelve condition code test signals are generated in this section. The multiplexer selects one of these twelve and places it at the CT output. The multiplexer is addressed by either using the Test Instruction or by using the bidirectional T bus as an input. The test instruction specifies the test condition to be placed at the CT output, but it does not allow an ALU operation at the same time. Using the T bus as input, the CY7C9115, CY7C9116, and CY7C9117 may simultaneously test and execute an instruction. The test instruction lines  $(\mathbf{I_4}-\mathbf{I_0})$  take precedence over  $\mathbf{T_4}-\mathbf{T_1}$  for testing status.

#### Status Register

The 8-bit status word is held by the status register. The status register is updated at the end of all instructions except NO-OP, Save Status, and Test Status, provided the status register enable ( $\overline{RE}$ ) and instruction enable ( $\overline{IEN}$ ) are both LOW. The status register is inhibited from changing if either  $\overline{SRE}$  or  $\overline{IEN}$  are HIGH.

The lower four status bits are the ALU status: OVR (overflow), N (negative), C (carry), and Z (zero). The upper four bits are a link bit and three user-defined status bits (Flag1, Flag2, Flag3).

As stated above, when IEN and SRE are LOW, the status register is updated at the end of all instructions other than NO-OP, Save Status, and Test Status. The lower four status bits are updated under the above conditions, with the additional exception of when IEN and SRE are LOW and the Status Set/Reset instruction is performed on the upper four bits. When IEN and SRE are LOW, the upper four status bits are only changed during their corresponding Status Set/Reset instructions and during Status Load instructions in word mode. The Link-Status bit is also updated after every shift instruction.

The status register can be loaded via the internal Y bus; it can also be selected as a source for the internal Y bus. Loading the status register in word mode updates all eight bits of the status register. In byte mode, only the lower four bits are updated.

Using the status register as a source in the word mode loads all eight bits into the lower byte of the destination; the upper byte is zero-filled. In byte mode, the status register loads the lower byte of the destination; however the upper byte is unchanged. Interrupt and subroutine processing is facilitated by this store/load combination, which allows saving and restoring the status register. The lower four bits of the status register can be read directly by outputting them to the  $T_4-T_1$  outputs. These outputs are enabled when  $\mathrm{OE}_T$  is HIGH.

#### **Output Buffers**

Two sets of bidirectional buses exist on the CY7C9115 and CY7C9116. The bidirectional Y bus (16 bits) is controlled by  $\overline{OE}_Y$ . The three state outputs are enabled when  $\overline{OE}_Y$  is LOW, they are at high impedance when  $\overline{OE}_Y$  is HIGH. This will allow data to be input to the data latch from the external world. The second bidirectional bus is the four-bit T bus. These three-state buffers are enabled by a HIGH on  $OE_T$  which will output the internal ALU status bits (OVR, N, C, Z). If  $OE_T$  is LOW, the T outputs are at high impedance, and a test condition can be input on the T bus to determine the CT output.

The 7C9117 has separate Y bus output and Data Input buses. All other pins are functionally equivalent to the 7C9115 and 7C9116.

# Pin Definitions

| I III WYAIL                      | HOLOE |                                                                                                                                                                                                                                           |                                  |     |                                                                                                                                                                                                                                                           |

|----------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal<br>Name                   | I/O   | Description                                                                                                                                                                                                                               | Signal<br>Name                   | I/O | Description                                                                                                                                                                                                                                               |

| Y <sub>15</sub> - Y <sub>0</sub> | I/O   | Data Input/Output. These bidirectional lines are used to directly load the 16-bit data latch when $\overline{OE}_Y$ is HIGH. When $\overline{OE}_Y$ is LOW, the arithmetic unit or the logic unit output data is output on $Y_{15}-Y_0$ . | SRE                              | I   | Status Register Enable. The Status Register is updated at the end of all instructions except NO-OP, Save Status, and Test Status when SRE and IEN are both LOW. The Status Register is inhibited from changing when either SRE or IEN are HIGH.           |

| $I_{15} - I_0$                   | I     | Instruction Word. This 16-bit word selects the function performed by the 7C911X. These lines are also used to input data when executing Immediate Instructions.                                                                           | ŌĒ <sub>Y</sub>                  | I   | Y Output Enable. This controls the 16-bit $Y_{15} - Y_0 I/O$ port. When $\overline{OE}_Y$ is LOW, the Y outputs are enabled, when $\overline{OE}_Y$ is HIGH, the Y outputs are disabled (high impedance).                                                 |

| $T_4 - T_1$                      | I/O   | Status Input/Output. These bidirectional pins are used to output the lower four status bits (OVR, N, C, and $Z$ ) when $OE_T$ is HIGH. When $OE_T$ is LOW, these lines are used as                                                        | OE <sub>T</sub>                  | I   | T Output Enable. The four-bit T outputs are enabled when $OE_T$ is HIGH; they are disabled (high impedance) when $OE_T$ is LOW.                                                                                                                           |

|                                  |       | inputs to generate the conditional test (CT) output.                                                                                                                                                                                      | CP .                             | I   | Clock Pulse. The RAM output latch is transparent when CP is HIGH; the RAM output is                                                                                                                                                                       |

| СТ                               | 0     | Conditional Test. One of twelve condition code signals is selected by the condition code multiplexer to be placed on the CT output.  CT = HIGH for a pass condition; CT = LOW for a fail condition.                                       |                                  |     | latched when CP goes LOW. If IEN is LOW and the current instruction specifies the RAM as the destination, then data is written into the RAM while CP is LOW. If IEN is LOW, the Accumulator and Status Register will accept data at the clock LOW to HIGH |

| DLE                              | I     | Data Latch Enable. The 16-bit data latch is transparent when DLE is HIGH and latched when DLE is LOW.                                                                                                                                     |                                  |     | transition. The instruction latch becomes<br>transparent upon exiting an Immediate In-<br>struction during a LOW to HIGH clock tran-                                                                                                                      |

| IEN                              | I     | Instruction Enable. The following occurs with IEN LOW: Data may be written into the RAM when the clock is LOW, the accumulator can accept data during the clock LOW to                                                                    | $\mathbf{D}_{15} - \mathbf{D}_0$ | I   | sition.  These input lines are used to directly load the data latch.                                                                                                                                                                                      |

|                                  |       | HIGH transition, and the Status Register can be updated when SRE is LOW. If IEN is HIGH, CT is disabled as a function of the instruction inputs. IEN should be LOW during the first half of the first cycle of Immediate Instructions.    | Y <sub>15</sub> - Y <sub>0</sub> | I/O | These output lines are used to present the arithmetic unit or the logic unit output when $\overline{OE}_Y$ is LOW. (CY7C9117 $Y_{15}-Y_0$ and output only.)                                                                                               |

#### **Instruction Set**

The instruction set of the CY7C9115, CY7C9116, and CY7C9117 is optimized for peripheral controller applications. It features: Bit Set, Bit Reset, Bit Test, Rotate and Merge, Rotate and Compare, and Cyclic-Redundancy-Check (CRC) generation, in addition to standard Single- or Two-Operand logical and arithmetic instructions. A single clock cycle will execute all but the Immediate Instructionswhich take 2 clock cycles.

The CY7C9115, CY7C9116, and CY7C9117 can operate in three different data modes: bit, byte, and word (16 bits). The LSB of the word is used for Byte Mode. Also in Byte Mode when the status register is specified as the destination, only the LSH (OVR, N, C, Z) of the register is updated. Save Status and Test Status instructions do not change the status register. During Test Status instructions the Y bus (or D bus for the CY7C9117) is undefined; the result is in the CT output.

The eleven instruction types outlined below are described in detail on the following pages.

| Single-Operand   | Rotate and Compare |

|------------------|--------------------|

| Two-Operand      | Prioritize         |

| Single Bit Shift | CRC                |

| Bit-Oriented     | Status             |

| Rotate by n Bits | No-Op              |

| Rotate and Merge | •                  |

$\overline{OE}_{Y}$  is assumed LOW for all cases, allowing ALU outputs on the Y or D bus.

Instructions are individually distinguished by using OP-CODES and two assigned quadrant bits. Four quadrants, 0 to 3, have been assigned to each instruction type in order to ease groupings of instructions and addressing modes.

**Table 1. Operand Source-Destination Combinations**

| Instruction Type                         | Ope                                         | ations <sup>[2]</sup>                              |                                                    |  |  |

|------------------------------------------|---------------------------------------------|----------------------------------------------------|----------------------------------------------------|--|--|

|                                          | Source                                      | e (R/S)                                            | Destination                                        |  |  |

| SingleOperand<br>SOR<br>SONR             | RA<br>A(<br>I<br>D((<br>S(S                 | RAM<br>ACC<br>Y Bus<br>Status<br>ACC and<br>Status |                                                    |  |  |

|                                          | Source (R)                                  | Source (S)                                         | Destination                                        |  |  |

| Two Operand<br>TOR1<br>TOR2<br>TONR      | RAM   ACC   I   RAM   D   ACC   ACC   I   I |                                                    | RAM<br>ACC<br>Y Bus<br>Status<br>ACC and<br>Status |  |  |

|                                          | Source                                      | Destination                                        |                                                    |  |  |

| Single Bit Shift<br>SHFTR<br>SHFTNR      | RA<br>AG<br>AG<br>I<br>I<br>I               | RAM<br>ACC<br>Y Bus<br>RAM<br>ACC<br>Y Bus         |                                                    |  |  |

|                                          | Source                                      | e (R/S)                                            | Destination                                        |  |  |

| Bit Oriented<br>BOR1<br>BOR2<br>BONR     |                                             | AM<br>CC<br>O                                      | RAM<br>ACC<br>Y Bus                                |  |  |

|                                          | Source                                      | ce (U)                                             | Destination                                        |  |  |

| Rotate n Bits<br>ROTR1<br>ROTR2<br>ROTNR | RA<br>A(<br>I                               | RAM<br>ACC<br>Y Bus                                |                                                    |  |  |

|                                          | Rotated<br>Source (U)                       | Mask (S)                                           | Non-Rotated<br>Source/<br>Destination (R)          |  |  |

| Rotate and<br>Merge<br>ROTM<br>ROTC      | D<br>D<br>D<br>D<br>ACC<br>RAM              | I<br>RAM<br>I<br>ACC<br>I<br>I                     | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC             |  |  |

| Instruction Type                                              | Оре                                             | rand Combina                                                        | ations <sup>[2]</sup>                     |  |  |  |

|---------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------|--|--|--|

|                                                               | Rotated<br>Source (U)                           | Mask (S)                                                            | Non-Rotated<br>Source/<br>Destination (R) |  |  |  |

| Rotate and<br>Compare<br>CDAI<br>CDRI<br>CDRA<br>CRAI         | D<br>D<br>D<br>RAM                              | I<br>I<br>ACC<br>I                                                  | ACC<br>RAM<br>RAM<br>ACC                  |  |  |  |

|                                                               | Source (R)                                      | Mask (S)                                                            | Destination                               |  |  |  |

| Prioritize <sup>[4]</sup><br>PRT1<br>PRT2<br>PRTNR            | RAM<br>ACC<br>D                                 | RAM<br>ACC<br>I<br>O                                                | RAM<br>ACC<br>Y Bus                       |  |  |  |

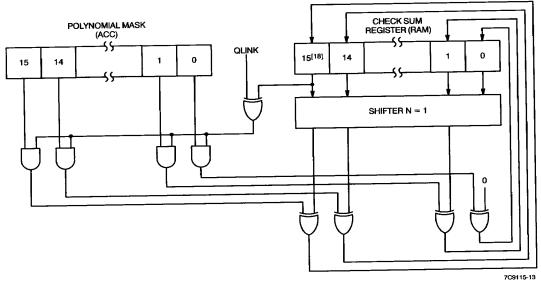

|                                                               | Data In                                         | Destination                                                         | Polynomial                                |  |  |  |

| Cyclic Redun-<br>dancy Check<br>CRCF<br>CRCR                  | QLINK                                           | RAM                                                                 | ACC                                       |  |  |  |

|                                                               |                                                 | Bits Affecte                                                        |                                           |  |  |  |

| Set Reset Status<br>SETST<br>RSTST<br>SVSTR<br>SVSTNR<br>TEST | OVR, N, C, Z<br>LINK<br>Flag1<br>Flag2<br>Flag3 |                                                                     |                                           |  |  |  |

|                                                               | Sou                                             | ırce                                                                | Destination                               |  |  |  |

| Store Status                                                  | Sta                                             | itus                                                                | RAM<br>ACC<br>Y Bus                       |  |  |  |

|                                                               | Source (R)                                      | Source (S)                                                          | Destination                               |  |  |  |

| Status Load                                                   | D<br>ACC                                        | ACC<br>I                                                            | Status<br>Status and<br>ACC               |  |  |  |

|                                                               | D                                               | I                                                                   |                                           |  |  |  |

|                                                               | Т                                               | (CT)                                                                |                                           |  |  |  |

| Test Status                                                   | (N ¥ O'<br>N ¥<br>O'<br>Lo                      | Z + $\overline{\mathbb{C}}$<br>N<br>LINK<br>Flag1<br>Flag2<br>Flag3 |                                           |  |  |  |

| No Operation<br>NOOP                                          |                                                 | _                                                                   |                                           |  |  |  |

Notes:

2. If there is no division between the R/S operand or SOURCE and DESTINATION, the two are a given pair. If a division exists, any combination is possible.

RAM cannot be used as source when both ACC and STATUS are designated as a DESTINATION.

<sup>4.</sup> OPERAND and MASK must be different sources.

### Instruction Set (continued) **Single-Operand Instructions**

Each Single-Operand instruction contains four designators:

- Mode (Byte or Word)

- Opcode 5.

- Source

- Address or Destination

These designators are divided into two basic categories, those that use RAM addresses and those that do not.

The instruction formats shown below are unique for each category. In both cases the desired operation, controlled by the instruction inputs, is performed on the source with the result either placed on the Y bus or stored in the destination or both. The functions of Extending Sign Bit (D(SE)) and Binary Zero (D(OE)) over 16 bits in Word mode are available for cases where 8-bit to 16-bit conversion is necessary. The functions performed using Single-Operand instructions update the LSB of the status register (OVR, N, C, Z) but do not effect the MSB (FLAG1, FLAG2, FLAG3, LINK). Singleoperand instructions are limited such that when both the ACC and the status register are the destination, the source cannot be RAM.

|      | 15  | 14       | 13   | 12     | 9 | 8        | 5 | 4           | 0 |

|------|-----|----------|------|--------|---|----------|---|-------------|---|

| SOR  | B/W | Quad     | rant | Opcode |   | SRC-Dest |   | RAM Address |   |

| •    | 15  | 14       | 13   | 12     | 9 | 8        | 5 | 4           | 0 |

| SONR | B/W | Quadrant |      | Opcode |   | SRC      |   | Destination |   |

Figure 1. Single-Operand Field Definitions

Table 2. Single-Operand Instruction Set

| 15 | 14 | 13 | 12 | 9 |

|----|----|----|----|---|

|    |    |    |    |   |

8 5

| 15 14 15 12 9              |                    |                     |                              |                            |                                                          | 0 3                                                                          |                                                                                 |                                                                  |                                                      |                                  |                           |                                                                    |

|----------------------------|--------------------|---------------------|------------------------------|----------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------|----------------------------------|---------------------------|--------------------------------------------------------------------|

| Instruction <sup>[5]</sup> | B/W <sup>[6]</sup> | Quad <sup>[7]</sup> |                              | Ope                        | code                                                     |                                                                              |                                                                                 | R/S <sup>[8]</sup> Dest <sup>[8]</sup>                           |                                                      | RAM Address/Destination          |                           | /Destination                                                       |

| SOR                        | 0 = B<br>1 = W     | 10                  | 1100<br>1101<br>1110<br>1111 | MOVE<br>COMP<br>INC<br>NEG | SRC ♦ Dest<br>SRC ♦ Dest<br>SRC+1 ♦ Dest<br>SRC+1 ♦ Dest | 0000<br>0010<br>0011<br>0100<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011 | SORA<br>SORY<br>SORS<br>SOAR<br>SODR<br>SOIR<br>SOZR<br>SOZER<br>SOSER<br>SOSER | RAM<br>RAM<br>RAM<br>ACC<br>D<br>I<br>O<br>D(OE)<br>D(SE)<br>RAM | ACC Y Bus Status RAM RAM RAM RAM RAM RAM RAM RAM RAM | 00000                            | R00<br>R31                | RAM Reg 31                                                         |

| Instruction                | B/W                | Quad                |                              | Op                         | code                                                     |                                                                              | R/S <sup>[8]</sup>                                                              |                                                                  |                                                      | Destination                      |                           |                                                                    |

| SONR                       | 0 = B<br>1 = W     | 11                  | 1100<br>1101<br>1110<br>1111 | MOVE<br>COMP<br>INC<br>NEG | SRC • Dest<br>SRC • Dest<br>SRC+1 • Dest<br>SRC+1 • Dest | 0100<br>0110<br>0111<br>1000<br>1001<br>1010                                 | SOA<br>SOD<br>SOI<br>SOZ<br>SOZE<br>SOSE                                        | ACC<br>D<br>I<br>O<br>D(OE)<br>D(SE)                             |                                                      | 00000<br>00001<br>00100<br>00101 | NRY<br>NRA<br>NRS<br>NRAS | Y Bus<br>ACC<br>Status <sup>[9]</sup><br>ACC,Status <sup>[9]</sup> |

Table 3. Y Bus and Status<sup>[10]</sup>

| Instruction | Opcode | Description  | B/W              | Y Bus       | Flag3 | Flag2 | Flag1 | LINK | OVR | N | C | Z |

|-------------|--------|--------------|------------------|-------------|-------|-------|-------|------|-----|---|---|---|

| SOR         | COMP   | SRC ♦ Dest   | 1 = W            | Y ♦ SRC     | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

| SONR        | INC    | SRC+1 → Dest | $0 = \mathbf{B}$ | Y ▶ SRC + 1 | NC    | NC    | NC    | NC   | U   | U | U | U |

|             | MOVE   | SRC Dest     |                  | Y ♦ SRC     | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

|             | NEG    | SRC+1 ♦ Dest |                  | Y ♦ SRC + 1 | NC    | NC    | NC    | NC   | U   | U | U | U |

- Instruction mnemonic.

- B = Byte Mode, W = Word Mode.

- Quadrant subdivides instructions into categories.

- R = Source; S = Source; Dest = Destination.

Status is destination,

i = 0 to 3 (byte mode) i = 0 to 7 (word mode) Status i 4 Yi

SRC = Source; NC = No Change; 1 = Set; U = Update; 0 = Reset; i = 0 to 15 when not specified

### Instruction Set (continued) Two-Operand Instructions

Each Two-Operand instruction is constructed of 5 fields:

- 1. Mode (Byte or Word)

- Opcode

- R Source

- S Source

- 5. Address or Destination

These instructions are further divided into those using RAM addresses and those that do not. The first type uses two formats which differ only by quadrant designator.

Functions are performed on the specified R and S sources and results are stored in the specified destination and/or placed on the Y bus. Arithmetic functions update the least significant nibble of the status register (OVR, N, C, Z), while logical functions affect only the N and Z bits. Executions of logical functions clear the OVR and C bits of the status register.

|      | 15  | 14   | 13    | 12    | 9        | 8   | 5   | 4    | 0       |

|------|-----|------|-------|-------|----------|-----|-----|------|---------|

| TOR1 | B/W | Quad | drant | SRC-S | RC, Dest | Орс | ode | RAM  | Address |

|      | 15  | 14   | 13    | 12    | 9        | 8   | 5   | 4    | 0       |

| TOR2 | B/W | Quad | drant | SRC-S | RC, Dest | Орс | ode | RAM  | Address |

|      | 15  | 14   | 13    | 12    | 9        | 8   | 5   | 4    | 0       |

| TONR | B/W | Quad | drant | SRC-S | RC, Dest | Орс | ode | Dest | ination |

Figure 2. Two-Operand Field Definitions

**Table 4. Two-Operand Instruction Set**

| Instruction | B/W            | Quad |                      |                         | $R^{[8]}$          | S <sup>[8]</sup> | Dest <sup>[8]</sup>     |                              | Opcode                        |                                                                                   |                 | RAM A | ddress                   |

|-------------|----------------|------|----------------------|-------------------------|--------------------|------------------|-------------------------|------------------------------|-------------------------------|-----------------------------------------------------------------------------------|-----------------|-------|--------------------------|

| TOR1        | 0 = B<br>1 = W | 00   | 0000<br>0010<br>0011 | TORAA<br>TORIA<br>TODRA | RAM<br>RAM<br>D    | ACC<br>I<br>RAM  | ACC<br>ACC<br>ACC       | 0000<br>0001                 | SUBR<br>SUBRC <sup>[11]</sup> | S minus R<br>S minus R<br>with carry                                              | 00000<br>ii1111 |       | RAM Reg 00<br>RAM Reg 31 |

|             |                |      | 1000<br>1010<br>1011 | TORAY<br>TORIY<br>TODRY | RAM<br>RAM<br>D    | ACC<br>I<br>RAM  | Y Bus<br>Y Bus<br>Y Bus | 0010<br>0011                 | SUBSC <sup>[11]</sup>         | R minus S<br>R minus S<br>with carry                                              |                 |       |                          |

|             |                |      | 1100<br>1110<br>1111 | TORAR<br>TORIR<br>TODRR | RAM<br>RAM<br>D    | ACC<br>I<br>RAM  | RAM<br>RAM<br>RAM       | 0101                         | ADD<br>ADDC                   | R plus S<br>R plus S<br>with carry                                                |                 |       |                          |

|             |                |      |                      |                         |                    |                  |                         | 0110<br>0111<br>1000<br>1001 | AND<br>NAND<br>EXOR<br>NOR    | $ \begin{array}{c} R \land S \\ R \land S \\ R \lor S \end{array} $               |                 |       |                          |

|             |                |      |                      |                         |                    |                  |                         | 1010<br>1011                 | OR<br>EXNOR                   | $\frac{R \vee S}{R \vee S}$                                                       |                 |       |                          |

| Instruction | B/W            | Quad |                      |                         | $\mathbf{R}^{[8]}$ | $S^{[8]}$        | Dest <sup>[8]</sup>     |                              | Opcode                        |                                                                                   |                 | RAM A | ddress                   |

| TOR2        | 0=B<br>1=W     | 10   | 0001<br>0010         | TODAR<br>TOAIR          | D<br>ACC           | ACC<br>I         | RAM<br>RAM              | 0000<br>0001                 | SUBR<br>SUBRC <sup>[11]</sup> | S minus R<br>S minus R                                                            | 00000           | R00   |                          |

|             |                |      | 0101                 | TODIR                   | D                  | 1                | RAM                     | 0010<br>0011                 | SUBSC[11]                     | with carry<br>R minus S<br>R minus S<br>with carry                                | 11111           | R31   | RAM Reg 31               |

|             |                |      |                      |                         |                    |                  |                         | 0100<br>0101                 | ADD<br>ADDC                   | R plus S<br>R plus S<br>with carry                                                |                 |       |                          |

|             |                |      |                      |                         |                    |                  |                         | 0111<br>1000                 |                               | $\begin{array}{c} R \wedge S \\ R \wedge S \\ R \vee S \end{array}$               |                 |       |                          |

|             |                |      |                      |                         |                    |                  |                         | 1001<br>1010<br>1011         | NOR<br>OR<br>EXNOR            | $   \begin{array}{c}     R \lor S \\     R \lor S \\     R \lor S   \end{array} $ |                 |       |                          |

**Notes:** 11. For subtraction the carry is interpreted as borrow.

Table 4. Two-Operand Instruction Set (continued)

| Instruction | B/W            | Quad |                      |                      | <b>R</b> <sup>[8]</sup> | S <sup>[8]</sup> |                                                                      | Opcode                                                        |                                        |                                  | Destin                    | ation                                                              |

|-------------|----------------|------|----------------------|----------------------|-------------------------|------------------|----------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------|----------------------------------|---------------------------|--------------------------------------------------------------------|

| TONR        | 0 = B<br>1 = W | 11   | 0001<br>0010<br>0101 | TODA<br>TOAI<br>TODI | D<br>ACC<br>D           | ACC<br>I<br>I    | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0111<br>1000<br>1001 | SUBR SUBRC[11] SUBS SUBSC[11] ADD ADDC AND NAND NAND EXOR NOR | S minus R<br>S minus R<br>with carry   | 00000<br>00001<br>00100<br>00101 | NRY<br>NRA<br>NRS<br>NRAS | Y Bus<br>ACC<br>Status <sup>[9]</sup><br>ACC,Status <sup>[9]</sup> |

|             |                |      |                      |                      |                         |                  | 1010<br>1011<br>1011                                                 | OR<br>EXNOR                                                   | $R \lor S$<br>$R \lor S$<br>$R \lor S$ |                                  |                           |                                                                    |

Table 5. Y Bus and Status<sup>[12]</sup>

| Instruction  | Opcode | Description          | B/W              | Y Bus                                                | Flag3 | Flag2 | Flag1 | LINK | OVR | N  | C | Z |

|--------------|--------|----------------------|------------------|------------------------------------------------------|-------|-------|-------|------|-----|----|---|---|

| TOR1         | ADD    | R plus S             | $0 = \mathbf{B}$ | Y ♦ R + S                                            | NC    | NC    | NC    | NC   | U   | U  | U | U |

| TOR2<br>TONR | ADDC   | R plus S with carry  | 1 = W            | Y ♠ R + S + QC                                       | NC    | NC    | NC    | NC   | U   | U  | U | U |

|              | AND    | R ∧ S                |                  | Y ♠ R <sub>i</sub> AND S <sub>i</sub>                | NC    | NC    | NC    | NC   | 0   | IJ | 0 | U |

|              | EXOR   | R¥S                  |                  | $Y_i \triangleleft R_i EXOR S_i$                     | NC    | NC    | NC    | NC   | 0   | U  | 0 | U |

|              | EXNOR  | R¥S                  |                  | Y <sub>i</sub> ♠ R <sub>i</sub> EXNOR S <sub>i</sub> | NC    | NC    | NC    | NC   | 0   | 0  | 0 | U |

|              | NAND   | RAS                  |                  | Y <sub>i</sub> ♦ R <sub>i</sub> NAND S <sub>i</sub>  | NC    | NC    | NC    | NC   | 0   | U  | 0 | U |

|              | NOR    | RVS                  |                  | $Y_i \triangleleft R_i NOR S_i$                      | NC    | NC    | NC    | NC   | 0   | U  | 0 | U |

|              | OR     | RVS                  |                  | $Y_i  lefta R_i OR S_i$                              | NC    | NC    | NC    | NC   | 0   | U  | 0 | U |

|              | SUBR   | S minus R            |                  | $Y \blacktriangleleft S + \overline{R} + 1$          | NC    | NC    | NC    | NC   | U   | U  | U | U |

|              | SUBRC  | S minus R with carry |                  | $Y \blacktriangleleft S + \overline{R} + QC$         | NC    | NC    | NC    | NC   | U   | U  | U | U |

|              | SUBS   | R minus S            |                  | $Y \triangleleft R + \overline{S} + 1$               | NC    | NC    | NC    | NC   | U   | U  | Ü | U |

|              | SUBSC  | R minus S with carry |                  | $Y \triangleleft R + \overline{S} + QC$              | NC    | NC    | NC    | NC   | U   | U  | U | U |

#### Note:

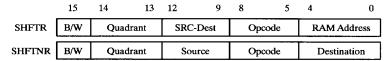

### **Single-Bit Shift Instructions**

Single-Bit Shift instructions are constructed of four fields:

- 1. Mode (Byte or Word)

- 2. Direction (up or down) and shift linkage

- 3. Source

- 4. Destination

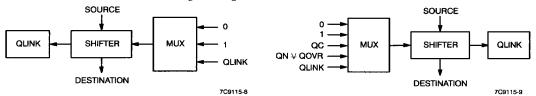

These instructions are further divided into those using RAM addresses and those that do not. The shift linkage indicator indicates what is to be loaded into the vacant bit.

During a shift up the LSB may be loaded with a zero, one, or with the link status bit (QLINK), while the MSB is shifted into the QLINK bit. During a shift down, the MSB is loaded with a zero, one, the status carry bit (QC), the exclusive-or of the negative-status bit and the overflow-status bit (QN  $\forall$  QOVR), or the link-status bit. The status register's N and Z bits are updated, while the OVR and C bits are reset. Shift down with QN  $\forall$  QOVR can be used in two's complement multiplication.

U = Update; NC = No Change; 0 = Reset; 1 = Set; i = 0 to 15 when not specified

Figure 3. Single Bit Shift Field Definitions

Figure 4. Shift Up Function

Figure 5. Shift Down Function

| Instruction | B/W            | Quad | <u> </u>     |              | U <sup>[13]</sup> | Dest <sup>[13]</sup> | <u> </u>                                                     | 0                                                                     | pcode                             |                                                                 | RAM A          | ddres      | s/Destination            |

|-------------|----------------|------|--------------|--------------|-------------------|----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------|----------------|------------|--------------------------|

| SHFTR       | 0=B<br>1=W     | 10   | 0110<br>0111 | SHRR<br>SHDR | RAM<br>D          | RAM<br>RAM           | 0000<br>0001<br>0010<br>0100<br>0101<br>0110<br>0111<br>1000 | SHUPZ<br>SHUP1<br>SHUPL<br>SHDNZ<br>SHDN1<br>SHDNL<br>SHDNC<br>SHDNOV | Up Up Up Down Down Down Down Down | 0<br>1<br>QLINK<br>0<br>1<br>QLINK<br>QC<br>QN \(\forall QOVR\) | 00000<br>11111 |            | RAM Reg 00<br>RAM Reg 31 |

| Instruction | B/W            | Quad |              |              | $U^{[13]}$        |                      |                                                              | o                                                                     | pcode                             |                                                                 |                | Destir     | nation                   |

| SHFTNR      | 0 = B<br>1 = W | 11   | 0110<br>0111 | SHA<br>SHD   | ACC<br>D          |                      | 0000<br>0001<br>0010<br>0100<br>0101<br>0110<br>0111<br>1000 | SHUPZ<br>SHUP1<br>SHUPL<br>SHDNZ<br>SHDN1<br>SHDNL<br>SHDNC<br>SHDNOV | Up Up Up Down Down Down Down Down | 0<br>1<br>QLINK<br>0<br>1<br>QLINK<br>QC<br>QN \(\forall QOVR\) | 00000<br>00001 | NRY<br>NRA | Y Bus<br>ACC             |

Table 7. Y Bus and  $Status^{[10]}$

| Instruction | Opcode                  | Description                    | B/W   | Y Bus                                                                                                                                                                           | Flag3 | Flag2 | Flag1 | LINK <sup>[14]</sup> | OVR | N                 | C | Z |

|-------------|-------------------------|--------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------------------|-----|-------------------|---|---|

| SHR<br>SHNR | SHUPZ<br>SHUP1<br>SHUPL | Up 0<br>Up 1                   | 1 = W | $Y_i \triangleleft SRC_{i-1}, i = 1 \text{ to } 15;$<br>$Y_0 \triangleleft Shift Input$                                                                                         | NC    | NC    | NC    | SRC <sub>15</sub>    | 0   | SRC <sub>14</sub> | 0 | U |

|             | SHUPL                   | Up QLINK                       | 0 = B | $Y_i \triangleleft SRC_{i-1}, i = 1 \text{ to } 7;$<br>$Y_0 \triangleleft Shift Input;$<br>$Y_8 \triangleleft SRC_7, Y_i \triangleleft SRC_{i-9}$<br>for $i = 9 \text{ to } 15$ | NC    | NC    | NC    | SRC <sub>7</sub>     | 0   | SRC <sub>6</sub>  | 0 | U |

|             | SHDNZ<br>SHDN1<br>SHDNL | Down 0<br>Down 1<br>Down OLINK | 1 = W | $Y_i \triangleleft SRC_{i+1}$ , $i = 0$ to 14;<br>$Y_{15} \triangleleft Shift Input$                                                                                            | NC    | NC    | NC    | SRC <sub>0</sub>     | 0   | Shift<br>Input    | 0 | U |

|             | SHDNC<br>SHCNOV         | Down QC<br>Down QN ↓<br>QOVR   | 0 = B | $Y_i \triangleleft SRC_{i+1}, i = 0 \text{ to } 6;$<br>$Y_i \triangleleft SRC_{i-7}, i = 8 \text{ to } 14;$<br>$Y_{7, 15} \triangleleft Shift Input$                            | NC    | NC    | NC    | SRC <sub>0</sub>     | 0   | Shift<br>Input    | 0 | U |

Notes: 13. U = Source; Dest = Destination

14. Shifted output is loaded into the QLINK.

# Instruction Set (continued) Bit-Oriented Instructions

Bit-Oriented instructions are constructed from four fields:

- 1. Mode (Byte or Word)

- 2. Operation

- 3. Source or Destination

- 4. Bit position operated on (0 = LSB)

These instructions are further divided into those using RAM addresses and those that do not. The specified function operates on the given source and the result is stored in the specified destination and/or on the Y bus.

Set Bit n: Forces the nth bit to ONE without affecting other bit positions.

**Reset Bit n:** Forces the nth bit to ZERO without affecting other bit positions.

Test Bit n: Sets the Z status bit to the state of bit n.

**Load 2<sup>n</sup>**: Loads ZERO in bit position n and sets all other bits.

Load  $2^n$ : Loads ONE in bit position n and clears all other bits.

Increment 2n: Adds 2n to the operand.

**Decrement 2<sup>n</sup>:** Subtracts 2<sup>n</sup> from the operand.

Load, Set, Reset, and Test instructions update N and Z status bits while forcing OVR and C bits to ZERO. Arithmetic operations affect the entire lower nibble of the status register (OVR, C, N, and Z).

|      | 15  | 14   | 13    | 12 |   | 9 | 8   | 5   | 4   | 0       |

|------|-----|------|-------|----|---|---|-----|-----|-----|---------|

| BOR1 | B/W | Quad | rant  |    | N |   | Opc | ode | RAM | Address |

| ,    | 15  | 14   | 13    | 12 |   | 9 | 8   | 5   | 4   | 0       |

| BOR2 | B/W | Quad | lrant |    | N |   | Opc | ode | RAM | Address |

| ·    | 15  | 14   | 13    | 12 |   | 9 | 8   | 5   | 4   | 0       |

| BONR | B/W | Quad | lrant |    | N |   | 110 | 00  | Op  | code    |

Figure 6. Bit-Oriented Field Definitions

**Table 8. Bit-Oriented Instruction Set**

| Instruction | B/W            | Quadrant | n       | Opcode                       |                                 |                                                                                                                 |                                                                                                                   | RAM                                                                                       | I Address                                                                                                                                                                                                                                                                              |

|-------------|----------------|----------|---------|------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOR1        | 0 = B<br>1 = W | 11       | 0 to 15 | 1101<br>1110<br>1111         | SETNR<br>RSTNR<br>TSTNR         | Set RAM, bit n<br>Reset RAM, bit n<br>Test RAM, bit n                                                           | 00000<br>iii111                                                                                                   | R00<br>R31                                                                                | RAM Reg 00<br>RAM Reg 31                                                                                                                                                                                                                                                               |

| Instruction | B/W            | Quadrant | n       |                              | •                               | Opcode                                                                                                          |                                                                                                                   | RAM                                                                                       | I Address                                                                                                                                                                                                                                                                              |

| BOR2        | 0=B<br>1=W     | 10       | 0 to 15 | 1100<br>1101<br>1110<br>1111 | LD2NR<br>LDC2NR<br>A2NR<br>S2NR | 2 <sup>n</sup> ♦ RAM<br>2 <sup>n</sup> ♦ RAM<br>RAM plus 2 <sup>n</sup> ♦ RAM<br>RAM minus 2 <sup>n</sup> ♦ RAM | 00000<br>iii111                                                                                                   | R00<br>R31                                                                                | RAM Reg 00<br>RAM Reg 31                                                                                                                                                                                                                                                               |

| Instruction | B/W            | Quadrant | n       |                              | (                               | Opcode                                                                                                          |                                                                                                                   | C                                                                                         | pcode                                                                                                                                                                                                                                                                                  |

| BONR        | 0 = B<br>1 = W | 11       | 0 to 15 | 1100                         |                                 |                                                                                                                 | 00000<br>00001<br>00010<br>00100<br>00101<br>00111<br>10000<br>10001<br>10010<br>10100<br>10101<br>10110<br>10111 | TSTNA RSTNA RSTNA SETNA A2NA S2NA LD2NA LDC2NA TSTND RSTND RSTND A2NDY S2NDY LS2NY LDC2NY | Test ACC, bit n Reset ACC, bit n Set ACC, bit n ACC plus 2 <sup>n</sup> ♦ ACC ACC minus 2 <sup>n</sup> ♦ ACC 2 <sup>n</sup> ♦ ACC Test D, bit n Reset D, bit n Set D, bit n D plus 2 <sup>n</sup> ♦ Y Bus D minus 2 <sup>n</sup> ♦ Y Bus 2 <sup>n</sup> ♦ Y Bus 2 <sup>n</sup> ♦ Y Bus |

# Instruction Set (continued) Rotate by n Bits Instructions

The Rotate by *n* Bits instructions contain four indicators: byte or word mode, source, destination, and the number of places the source is to be rotated. They are further subdivided into two types. The first type uses RAM as a source and/or a destination and the second type does not use RAM as a source or destination. The first type has two different formats and the only difference is in the quadrant. The second type has only one format as shown in *Table 9*. Under the control of instruction inputs, the n indicator specifies

the number of bit positions the source is to be rotated up (0 to 15), and the result is either stored in the specified destination or placed on the Y bus or both. An example of this instruction is given in Figure 8. In the Word mode, all 16 bits are rotated up; while in the Byte mode, only the lower 8 bits (0-7) are rotated up. In the Word mode, a rotate up by n bits is equivalent to a rotate down by (16-n) bits. Similarly, in the Byte mode a rotate up by n bits is equivalent to a rotate down by (8-n) bits. The N and Z bits of the status register are affected and OVR and C bits are forced to zero.

|       | 15  | 14   | 13   | 12 |   | 9 | 8   | 5     | 4   | 0       |

|-------|-----|------|------|----|---|---|-----|-------|-----|---------|

| ROTR1 | B/W | Quad | rant |    | n |   | SRC | -Dest | RAM | Address |

| ROTR2 | B/W | Quad | rant |    | n |   | SRC | -Dest | RAM | Address |

| ROTNR | B/W | Quad | rant |    | n |   | 11  | .00   | SRO | C-Dest  |

Figure 7. Rotate by n Bits Shift Field Definitions

| EXAMPLE: $n = 4$ , | Word Mod  | e    |      |      |

|--------------------|-----------|------|------|------|

| Source             | 0001      | 0011 | 0111 | 1111 |

| Destination        | 0011      | 0111 | 1111 | 0001 |

| EXAMPLE: $n = 4$ , | Byte Mode | ;    |      |      |

| Source             | 0001      | 0011 | 0111 | 1111 |

| Destination        | 0001      | 0011 | 1111 | 0111 |

#### Figure 8. Rotate by n Example

#### Table 9. Rotate by n Bits Instruction Set

| Instruction | B/W                                  | Quadrant | n       |                      |                      | $U^{[13]}$        | Dest <sup>[13]</sup> |                                  | RAM                          | Address    |                              |

|-------------|--------------------------------------|----------|---------|----------------------|----------------------|-------------------|----------------------|----------------------------------|------------------------------|------------|------------------------------|

| ROTR1       | $ 0 = \mathbf{B} \\ 1 = \mathbf{W} $ | 00       | 0 to 15 | 1100<br>1110<br>1111 | RTRA<br>RTRY<br>RTRR | RAM<br>RAM<br>RAM | ACC<br>Y Bus<br>RAM  | 00000<br>11111                   | R00<br>R31                   | RAM Re     | _                            |

| Instruction | B/W                                  | Quadrant | n       |                      |                      | $U^{[13]}$        | Dest <sup>[13]</sup> |                                  | RAM                          | Address    |                              |

| ROTR2       | 0 = B<br>1 = W                       | 01       | 0 to 15 | 0000<br>0001         | RTAR<br>RTDR         | ACC<br>D          | RAM<br>RAM           | 00000<br>iii111                  | R00<br><br>R31               | RAM Re     | _                            |

| Instruction | B/W                                  | Quadrant | n       |                      |                      |                   |                      |                                  | ·                            | $U^{[13]}$ | Dest <sup>[13]</sup>         |

| ROTNR       | 0 = B<br>1 = W                       | 11       | 0 to 15 | 1100                 |                      |                   |                      | 11000<br>11001<br>11100<br>11101 | RTDY<br>RTDA<br>RTAY<br>RTAA | D<br>ACC   | Y Bus<br>ACC<br>Y Bus<br>ACC |

#### Table 10. Y Bus and Status<sup>[10]</sup>

| Instruction    | Opcode | B/W              | Y Bus                                                                         | Flag3 | Flag2 | Flag1 | LINK | OVR | N                     | C | Z |

|----------------|--------|------------------|-------------------------------------------------------------------------------|-------|-------|-------|------|-----|-----------------------|---|---|

| ROTR1<br>ROTR2 |        | $1 = \mathbf{W}$ | $Y_i \triangleleft SRC_{(i-n) \mod 16}$                                       | NC    | NC    | NC    | NC   | 0   | SRC <sub>15 - n</sub> | 0 | U |

| ROTNR          |        | 0 = B            | $Y_i \blacktriangleleft SRC_{i+8} = SRC_{(i-n) \mod 8}$<br>for $i = 0$ to $7$ | NC    | NC    | NC    | NC   | 0   | SRC <sub>6 - n</sub>  | 0 | U |

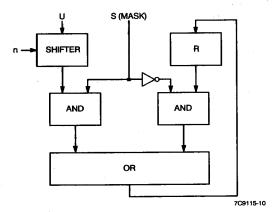

# Instruction Set (continued) Rotate and Merge Instructions

Each Rotate and Merge instruction consists of five fields:

- 1. Mode (Byte or Word)

- 2. Rotated Source (U)

- 3. Non-Rotated Source (R)

- 4. Mask Location (S)

- Number of bits Rotated (n)

This shift register rotates source U up n places. ANDing with the mask causes any bit i to be passed from the rotated source that corresponds to a set bit in mask position i. The R input is not shifted, but is masked by the compliment of mask S, so that a ZERO in mask bit i will pass bit i of R. The ORed result is stored in register R. Rotate and Merge operations update the N and Z status bits, while clearing the OVR and C bits.

Figure 9. Rotate and Merge Function

|      | 15  | 14          | 13            | 12     | 9    | 8     | . 5 | 4    | 0       |

|------|-----|-------------|---------------|--------|------|-------|-----|------|---------|

| ROTM | B/W | Quadra      | nt            |        | n    | U, R, | S   | RAN  | Address |

|      | EXA | MPLE: n =   | 4, <b>W</b> o | rd Mod | le   |       |     |      |         |

|      |     | U           |               | 0011   | 0001 | 0101  |     | 0110 |         |

|      |     | Rotated U   |               | 0001   | 0101 | 0110  |     | 0011 |         |

|      |     | R           |               | 1010   | 1010 | 1010  |     | 1010 |         |

|      |     | Mask(S)     |               | 0000   | 1111 | 0000  |     | 1111 |         |

|      |     | Destination |               | 1010   | 0101 | 1010  |     | 0011 |         |

Figure 10. Rotate and Merge Field Definitions

Table 11. Rotate and Merge Instruction Set

| Instruction | B/W        | Quadrant | n       |                                              |                                              | $U^{[15]}$                     | R/Dest[15]                             | S <sup>[15]</sup>              |                |  |                              |  |  |

|-------------|------------|----------|---------|----------------------------------------------|----------------------------------------------|--------------------------------|----------------------------------------|--------------------------------|----------------|--|------------------------------|--|--|

| ROTM        | 0=B<br>1=W | 01       | 0 to 15 | 0111<br>1000<br>1001<br>1010<br>1100<br>1110 | MDAI<br>MDAR<br>MDRI<br>MDRA<br>MARI<br>MRAI | D<br>D<br>D<br>D<br>ACC<br>RAM | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC | I<br>RAM<br>I<br>ACC<br>I<br>I | 00000<br>11111 |  | RAM Reg 00<br><br>RAM Reg 31 |  |  |

#### Notes:

# Table 12. Y Bus and Status<sup>[12]</sup>

| Instruction | Opcode | B/W   | Y Bus                                                                                                                                         | Flag3 | Flag2 | Flagi | LINK | OVR | .N | C | Z |

|-------------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|-----|----|---|---|

| ROTM        |        | 1 = W | $Y_i \spadesuit (\text{Non Rot Op})_i \bullet (\text{mask})_i + (\text{Rot Op})_{(i-n) \mod 16} \bullet (\text{mask})_i$                      | NC    | NC    | NC    | NC   | 0   | U  | 0 | U |

|             | : .    | 0 = B | $Y_i \spadesuit (\text{Non Rot Op})_i \bullet (\overline{\text{mask}})_i + (\text{Rot Op})_{(i-n) \mod 8} \bullet (\overline{\text{mask}})_i$ | NC    | NC    | NC    | NC   | 0   | Ū  | 0 | U |

U = Rotated Source; R/Dest = Non-Rotated Source/Destination;

S = Mask

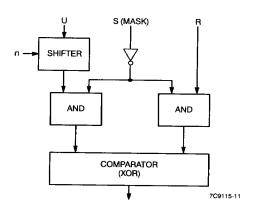

# Instruction Set (continued) Rotate and Compare Instructions

The five fields of the Rotate and Compare instructions are:

- 1. Mode (Byte or Word)

- 2. Rotated Source (U)

- 3. Non-Rotated Source (R)

- 4. Mask(S)

- 5. Number of bits Rotated (n)

Input U is rotated n bits, ANDed with the inversion of S and compared with the input R ANDed with the inversion of S. Thus, a zero in the mask S will allow that bit of both inputs to be compared. The Z bit of the status register is set if the comparison passes, and reset if it does not. OVR and C bits are reset in the status register.

Figure 11. Rotate and Compare Function

|      | 15  | 14         | 13      | 12    | 9    | 8     | 5 | 4    | 0       |

|------|-----|------------|---------|-------|------|-------|---|------|---------|

| ROTC | B/W | Quad       | rant    |       | n    | U, R, | s | RAM  | Address |

|      | EXA | MPLE: n :  | = 4, Wo | rd Mo | de   |       |   |      |         |

|      |     | U          | (       | 0011  | 0001 | 0101  |   | 0110 |         |

|      |     | Rotated U  | J (     | 0001  | 0101 | 0110  |   | 0011 |         |

|      |     | R          | (       | 0001  | 0101 | 1111  | 4 | 0000 |         |

|      |     | Mask(S)    | (       | 0001  | 0101 | 1111  |   | 1111 |         |

|      |     | Z (Status) | = 1     |       |      |       |   |      |         |

Figure 12. Rotate and Compare Field Definitions

Table 13. Rotate and Compare Instruction Set

| Instruction | B/W            | Quadrant | n       |                              |                              | U[16]              | $\mathbf{R}^{[16]}$      | $S^{[16]}$         |                |  |                          |  |  |

|-------------|----------------|----------|---------|------------------------------|------------------------------|--------------------|--------------------------|--------------------|----------------|--|--------------------------|--|--|

| ROTC        | 0 = B<br>1 = W | 01       | 0 to 15 | 0010<br>0011<br>0100<br>0101 | CDAI<br>CDRI<br>CDRA<br>CRAI | D<br>D<br>D<br>RAM | ACC<br>RAM<br>RAM<br>ACC | I<br>I<br>ACC<br>I | 00000<br>11111 |  | RAM Reg 00<br>RAM Reg 31 |  |  |

#### Notes:

16. U = Rotated Source; R = Non-Rotated Source; S = Mask

### Table 14. Y Bus and Status<sup>[12]</sup>

| Instruction | Opcode | B/W   | Y Bus                                                                                                             | Flag3 | Flag2 | Flag1 | LINK | OVR | N | C | Z |

|-------------|--------|-------|-------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|-----|---|---|---|

| ROTC        |        | 1 = W | $Y_i \spadesuit (Non Rot Op)_i \bullet (mask)_i \lor (Rot Op)_{(i-n)mod 16} \bullet (mask)_i$                     | NC    | NC    | NC    | NC   | 0   | Ū | 0 | U |

|             |        | 0 = B | $Y_i \triangleleft (Non Rot Op)_i \cdot (\overline{mask})_i \lor (Rot Op)_{(i-n)mod 8} \cdot (\overline{mask})_i$ | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

#### **Prioritize Instructions**

The four fields of the Prioritize instructions are:

- 1. Mode (Byte or Word)

- 2. Mask Source (S)

- 3. Operand Source (R)

- 4. Destination

The inverter mask, S is ANDed with R. A "one" in S prohibits that bit from participating in the priority encoding. From the 16-bit input, the priority encoder outputs a 5-bit binary weighted code indicating the bit-position of the highest priority active bit. If there are no active bits, the output is zero. See Figure 14 for operation in both word and byte mode. Using Prioritize updates the N and Z bits of the status register, and forces C and OVR to zero. This instruction is limited in that the operand and the mask must be different

Figure 13. Prioritize Function

| 15  | 14 13 | 1 12 9      | 8 5         | 4 0                         |

|-----|-------|-------------|-------------|-----------------------------|

| B/W | Quad  | Destination | Source (R)  | RAM Address/<br>Mask(S)     |

| B/W | Quad  | Mask (S)    | Destination | RAM Address/<br>Source (R)  |

| B/W | Quad  | Mask (S)    | Source (R)  | RAM Address/<br>Destination |

| B/W | Quad  | Mask(S)     | Source (R)  | Destination                 |

| Word M                         | lode              | Byte Mode <sup>[17]</sup>      |                   |  |  |  |

|--------------------------------|-------------------|--------------------------------|-------------------|--|--|--|

| Highest Priority<br>Bit Active | Encoder<br>Output | Highest Priority<br>Bit Active | Encoder<br>Output |  |  |  |

| None                           | 0                 | None                           | 0                 |  |  |  |

| 15                             | 1                 | 7                              | 1                 |  |  |  |

| 14                             | 2                 | 6                              | 2                 |  |  |  |

|                                | :                 | 1 : 1                          | :                 |  |  |  |

| 1                              | 15                | 1 1                            | 7                 |  |  |  |

| ō                              | 16                | 1 0 1                          | 8                 |  |  |  |

Figure 14. Prioritize Instruction Field Definitions

Note: 17. Bits 8 through 15 not available.

**Table 15. Prioritize Instruction Set**

| Instruction | B/W            | Quad |                      | Destinat             | ion                 |                      | Source (1            | R)              | R.                      | M Addr     | ess/Mask (S)                 |  |

|-------------|----------------|------|----------------------|----------------------|---------------------|----------------------|----------------------|-----------------|-------------------------|------------|------------------------------|--|

| PRT1        | 0 = B<br>1 = W | 10   | 1000<br>1010<br>1011 | PRIA<br>PR1Y<br>PR1R | ACC<br>Y Bus<br>RAM | 0111<br>1001         | RPT1A<br>PR1D        | ACC<br>D        | 00000<br>ii1111         | R00<br>R31 | RAM Reg 00<br>RAM Reg 31     |  |

| Instruction | B/W            | Quad |                      | Mask (               | S)                  |                      | Destinati            | on              | RA                      | M Addre    | ss/Source (R)                |  |

| PRT2        | 0 = B<br>1 = W | 10   | 1000<br>1010<br>1011 | PRA<br>PRZ<br>PRI    | ACC<br>O<br>I       | 0000<br>0010         | PR2A<br>PR2Y         | ACC<br>Y Bus    | 00000                   | R00<br>R31 | RAM Reg 00<br>RAM Reg 31     |  |