#### PRELIMINARY

### Spatializer<sup>®</sup> N-2-2<sup>™</sup> Digital Audio Processor with BBE<sup>®</sup> **BBE**. Spatializer<sup>®</sup> yiaryat National Distributed Distributed

### Description

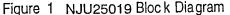

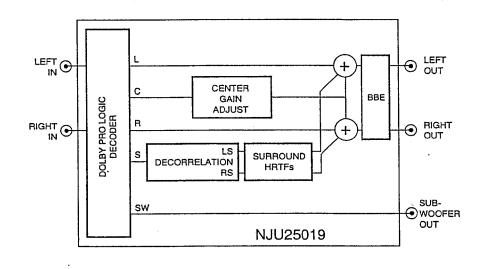

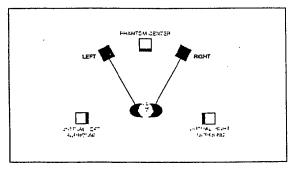

The NJU25019 is a digital 3D surround sound processor which decodes surround information from a stereo audio source and produces a 3D sonic image from two speakers. This application specific 24-bit DSP can operate in both Dolby<sup>®</sup> Pro Logic<sup>™</sup> and Virtual Dolby Surround (3D) mode. Based on Spatializer<sup>®</sup> Audio Laboratories Head Related Transfer Functions (HRTFs), N-2-2<sup>™</sup> technology allows the listener to experience realistic 3D sound while just two front speakers are playing. Spatializer N-2-2 has the unique ability of creating a wide sweet spot of 3D sound that is well suited for near field applications such as desktop multimedia computers or for far field applications such as TV's, home theater and stereo music.

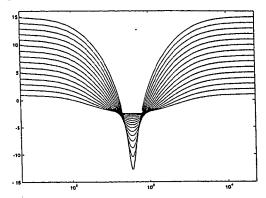

Digitally adjustable BBE<sup>®</sup> High Definition Sound processing is also incorporated in the NJU25019 which can be enabled on the output during any operating mode. BBE has the unique ability to dramatically improve the sound reproduced from loudspeakers by actively compensating for the increasing impedance inherent in loudspeakers as frequency increases. The BBE transfer function combines high and low frequency boost with phase correction, the combination of which greatly improves the transient response and clarity of loudspeakers.

The NJU25019 is also includes other system-level features not found in competing ICs: a full Dolby Pro Logic decoder, digital speaker crossover filters, and bass management. Home theater TVs, self-powered multimedia speakers for computers, and stereo systems can all benefit from the features and performance found in the NJU25019

#### Features

- ◆ Spatializer<sup>®</sup> N-2-2<sup>™</sup> 3D Surround Sound Processing 360° surround from two speakers Wide and accurate 3D listening area

- BBE<sup>®</sup> High Definition Sound Enhancement Programmable Lo Contour and Process levels Digital adjustment 0 to +15 dB in 1 dB increments

- Dolby Pro Logic Decoder With Optional Subwoofer Output 5.0 or 5.1ch output (L,R,SL,SR,C,SW) On-chip digital delay, 30ms max.

- Dolby 3 Stereo Mode With Optional Subwoofer Output

- System Level Audio Management Bass management Subwoofer filter

Front high pass filters

Default or custom cutoff frequencies

Master Volume Control

Clipping Indicator

- A Complete DSP-based 3D Audio Solution Includes on-chip surround time delay memory

BBE is a registered trademark of BBE Sound, inc

N-2-2 is a trademark and Spatializer is a registered trademark of Desper Products, Inc., a wholly owned subsidiary of Spatializer Audio Laboratories, Inc.

"Dolby," "Pro Logic," and the double-D symbol are trademarks of Dolby Laboratories. The NJU25019 may only be supplied to licensees of or companies authorized by Dolby Laboratories. Please refer all licensing inquiries to Dolby Laboratories, phone 415.558.0200, [ax 415.683,1373.

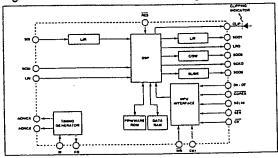

## Figure 2 N-2-2 Virtual Surr ound Sound

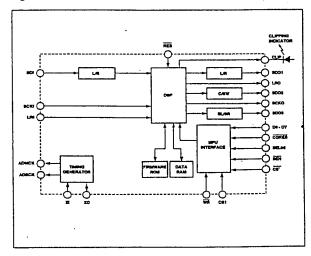

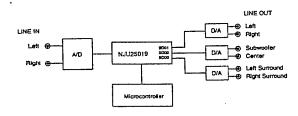

Figure 4 NJU25019 Functional Bloc k Diagram

Figure 5 PQFP-80 Package

4-218-

-New Japan Radio Co.,Ltd.-

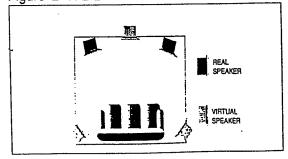

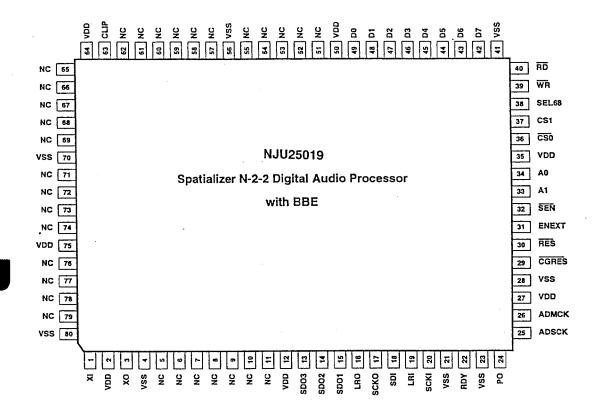

# Table 1 Pin Description

| 10.1     10.1     0.1     Constant     41     VSS     1     Ground       2     VOD     1     Power supply terminal: +5V     42     D7     1     MPU data, parallel input (MSB)       3     XO     O. Crystal     43     D6     1     MPU data, parallel input       4     VSS     1     Ground     44     D5     1     MPU data, parallel input       5     NC     No connect     45     O4     1     MPU data, parallel input       6     NC     No connect     46     D1     MPU data, parallel input       7     NC     No connect     49     D0     1     MPU data, parallel input (LSB), serial data inpu       8     NC     No connect     50     VDO     1     Power supply terminal: +SV       11     NC     No connect     51     NC     No connect     10       12     VDO     1     Power supply terminal: +SV     52     NC     No connect     11       13     SOO3     0     Digital                                                                                                                                                                           | <u></u> | Cumbel. | 10  | Fuendar                                         | No. | Symbol | vo                                           | Function                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-----|-------------------------------------------------|-----|--------|----------------------------------------------|----------------------------|

| 1     No.     1     Power supply terminal: +5V     42     D7     1     MPU data, parallel input       3     XO     O     Crystal     43     D6     1     MPU data, parallel input       4     VSS     1     Ground     44     D5     1     MPU data, parallel input       5     NC     No connect     45     D4     1     MPU data, parallel input       6     NC     No connect     46     D3     1     MPU data, parallel input       7     NC     No connect     47     D2     1     MPU data, parallel input       8     NC     No connect     49     D0     1     MPU data, parallel input       9     NC     No connect     51     NC     No connect     10       11     NC     No connect     51     NC     No connect     11       13     SDO2     0     Digital addo serial data out, crossove output     53     NC     No connect       14     SDO2     0     Digital addio serial data                                                                                                                                                                           |         |         |     |                                                 |     |        |                                              |                            |

| 3     XO     O     Crystal     43     D6     1     MPU data, parallel input       4     VSS     1     Ground     44     D5     1     MPU data, parallel input       5     NC     No connect     45     D4     1     MPU data, parallel input       6     NC     No connect     47     D2     1     MPU data, parallel input       7     NO     No connect     47     D2     1     MPU data, parallel input       8     NC     No connect     49     D0     1     MPU data, parallel input       9     NC     No connect     50     VD0     1     Power supply terminal: +SV       11     NC     No connect     51     NC     No connect     13       12     VDD     1     Power supply terminal: +SV     52     NC     No connect     14       13     SD03     0     Digital audio serial data out, FEC ouput     54     NC     No connect     15       14     SDC1     0     Duput                                                                                                                                                                                         |         |         |     |                                                 |     |        |                                              |                            |

| J     NG     O Julia       4     VSS     1     Ground     44     DS     1     MPU data, parallel input       5     NC     No connect     45     D4     1     MPU data, parallel input       6     NC     No connect     46     D3     1     MPU data, parallel input       7     NC     No connect     47     D2     1     MPU data, parallel input       8     NC     No connect     48     D1     MPU data, parallel input       9     NC     No connect     50     VD0     1     MPU data, parallel input       10     NC     No connect     50     VD0     1     No connect       12     VD0     1     Power supply terminal: +5V     S2     NC     No connect       13     SDC3     0     Digital adulo serial data out, PEO output     54     NC     No connect       14     SDC0     0     Digital adulo serial data     S6     VSS     1     Ground       15     SDC0 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                       |         |         |     |                                                 |     |        |                                              |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |         |     |                                                 |     |        |                                              |                            |

| 5     No     No </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                   |         |         |     |                                                 |     |        |                                              |                            |

| 7     NC     No connect     47     D2     1     MPU data, parallel input       9     NC     No connect     48     D1     MPU data, parallel input (LSB), sorial data input<br>(SEN = 0)       10     NC     No connect     49     D0     I     MPU data, parallel input (LSB), sorial data input<br>(SEN = 0)       11     NC     No connect     50     VDD     I     Power supply terminal: +SV       13     SOC0     D bigital aduids sarial data out, Oresover output     53     NC     No connect       14     SDO2     D bigital aduids sarial data out, OPEO output     54     NC     No connect       15     SDO1     O     Digital aduids serial data out, MU output     55     NC     No connect       16     LDO     O output digital aduids serial data     56     NC     No connect       17     SCKO     O     Digital aduids serial data     58     NC     No connect       18     LPU     Input digital aduids serial clock     60     NC     No connect       20     SCKI     I/O     Input dig                                                             |         |         |     |                                                 |     |        |                                              |                            |

| 1     NC     No connect     48     D1     MPU data, parallel input       9     NC     No connect     49     D0     I     MPU data, parallel input (LSB), serial data input (SSR) = 0)       10     NC     No connect     50     VDD     I     Power supply terminal: +SV       11     NC     No connect     51     NC     No connect     51       12     VDD     I     Power supply terminal: +SV     52     NC     No connect       13     SDO3     O     Digital audio serial data out, erossover output     53     NC     No connect       14     SDO2     O     Digital audio serial data out, erossover output     54     NC     No connect       15     SDO1     D Digital audio serial data out, full output     55     NC     No connect       16     LR0     O     Output left/right frame clock     59     NC     No connect       18     SDI     Input digital audio serial data     58     NC     No connect       21     VSS     I     Ground     61<                                                                                                          |         |         |     |                                                 |     |        |                                              |                            |

| 9     NC     No connect     49     D0     1     MPU data, parallel input (LSB), serial data input (SB) = 0)       10     NC     No connect     50     VDD     I     Nor connect       11     NC     No connect     51     NC     No connect       12     VDD     I     Power supply terminal: +5V     52     NC     No connect       13     SDO3     D bigital audio serial data out, crossover output     53     NC     No connect       14     SDO2     D Digital audio serial data out, crossover output     54     NC     No connect       15     SDO1     D Digital audio serial data out, crossover output     55     NC     No connect       16     LRD     O     Output digital audio serial data     56     VSS     I     Ground       17     SCKO     O utput digital audio serial data     58     NC     No connect       18     SD1     Input digital audio serial lock     60     NC     No connect       21     VSS     1     Ground     61     NC     <                                                                                                      |         |         |     | No connect                                      |     |        |                                              |                            |

| 9     NC     No connect     49     D0     1     (SER = 0)       10     NC     No connect     50     VDD     1     Power supply terminal: +5V       11     NC     No connect     51     NC     No connect       12     VDD     1     Power supply terminal: +5V     52     NC     No connect       13     SDO3     0     Digital audio serial data out, PCO output     53     NC     No connect       14     SDO2     0     Digital audio serial data out, PCO output     55     NC     No connect       15     SDO1     0     Digital audio serial data out, FCO output     55     NC     No connect       16     LRO     0     Output let/right frame clock     56     VSS     1     Ground       18     SDI     1     Input digital audio serial data     58     NC     No connect       20     SCK 10/0     Input digital audio serial clock     60     NC     No connect       21     VSS     1     Ground     62     N                                                                                                                                                 | 8       | NC      |     | No connect                                      | 48  | D1     |                                              |                            |

| 11     NC     No connect     51     NC     No connect       12     VDD     I     Power supply terminal: +5V     52     NC     No connect       13     SDO3     O     Digital audio serial data out, Crossover output     53     NC     No connect       14     SDO3     O     Digital audio serial data out, F2O output     55     NC     No connect       15     SDO1     O     Digital audio serial data out, full output     55     NC     No connect       16     LRO     O     Output leftright frame clock     56     VSS     I     Ground       17     SCKO     O utput leftright frame clock     59     NC     No connect       18     SDI     I     Input digital audio serial clock     60     NC     No connect       21     VSS     I     Ground     61     NC     No connect       22     RDY     I     Test pin, high for normal operation     62     NC     No connect       23     VSS     I     Ground     63                                                                                                                                              | 9       | NC      |     | No connect                                      |     |        | ļ                                            | (SEN = 0)                  |

| 12     VD0     1     Power supply terminal: +5V     52     NC     No connect       13     SD03     O     Digital audio serial data out, crossover output     53     NC     No connect       14     SD02     O     Digital audio serial data out, PEG output     54     NC     No connect       15     SD01     O     Digital audio serial data out, PEG output     55     VSS     1     Ground       16     LRO     O     Output digital audio serial clock     56     VSS     1     Ground       18     SD1     Input left/right frame clock     59     NC     No connect       20     SCKI     I/O     Input left/right rame clock     60     NC     No connect       21     VSS     1     Ground     61     NC     No connect       22     SCKI     I/O     Input left/right rame clock     64     VD0     No connect       23     VSS     1     Ground     63     CLIP     O     Clipping Indicator       24     PO <td< td=""><td>10</td><td>NC</td><td></td><td>No connect</td><td></td><td></td><td><u>                                     </u></td><td></td></td<> | 10      | NC      |     | No connect                                      |     |        | <u>                                     </u> |                            |

| 13     5003     0     Digital audio serial data out, crossover output     53     NC     No connect       14     SD02     0     Digital audio serial data out, PEQ output     54     NC     No connect       15     SD01     O     Digital audio serial data out, VEQ output     55     NC     No connect       16     LRO     O output left/right frame clock     55     NC     No connect       17     SCKO     O     Output left/right frame clock     57     NC     No connect       18     SD1     1     Input digital audio serial clock     57     NC     No connect       20     SCKI     10     input digital audio serial clock     60     NC     No connect       21     VSS     1     Ground     61     NC     No connect       23     VSS     1     Ground     63     CLIP     O     Clipping Indicator       24     PO     0     Test pin     64     VDD     1     Power supply terminal: +5V       25     ADSCK     0                                                                                                                                         | 11      | NC      |     | No connect                                      |     |        |                                              |                            |

| 13     SDC2     0     Digital studio serial data out, PEQ output     54     NC     No connect       15     SDC1     0     Digital studio serial data out, full output     55     NC     No connect       16     LRO     0     Output lefiftight frame clock     56     VSS     I     Ground       17     SCKO     0     Output digital audio serial clock     57     NC     No connect       18     SD1     I Input ieff/right frame clock     59     NC     No connect       20     SCKI     I/O     Input ieff/right frame clock     60     NC     No connect       21     VSS     I     Ground     61     NC     No connect       22     ROY     I     Test pin, high for normal operation     62     NC     No connect       23     VSS     I     Ground     63     CLIP     O     Clipping Indicator       24     PO     O     Test pin     ND, D/A converters     66     NC     No connect       25     ADSCK     O </td <td>12</td> <td>VDD</td> <td>1</td> <td>Power supply terminal: +5V</td> <td>52</td> <td></td> <td></td> <td>No connect</td>                  | 12      | VDD     | 1   | Power supply terminal: +5V                      | 52  |        |                                              | No connect                 |

| 15     SDC1     0     Digital audio serial data out, full output     55     NC     No connect       16     LRO     0     Output left/right frame clock     56     VSS     1     Ground       17     SCKO     0     Output digital audio serial clock     57     NC     No connect       18     SD1     1     Input digital audio serial clock     59     NC     No connect       20     SCKI     10     Input digital audio serial clock     60     NC     No connect       21     VSS     1     Ground     61     NC     No connect       22     RDV     1     Test pin, high for normal operation     62     NC     No connect       23     VSS     1     Ground     63     CLIP     O     Clipping Indicator       24     PO     0     Test pin     64     VDD     1     Power supply terminal: +5V       25     ADSCK     0     324Fs/26Fs master clock for A/D, D/A converters     66     NC     No connect       26     <                                                                                                                                             | 13      | SDO3    | 0   | Digital audio serial data out, crossover output | 53  | NC     | 1                                            | No connect                 |

| 16     LSPO     O     Diginal autoissing of the term       16     LSPO     O     Output left/right frame clock     56     VSS     1     Ground       17     SCKO     O     Output left/right frame clock     57     NC     No connect       18     SDI     1     Input digital audio serial clock     59     NC     No connect       20     SCKI     I/O Input digital audio serial clock     60     NC     No connect       21     VSS     1     Ground     61     NC     No connect       22     ROY     1     Test pin, high for normal operation     62     NC     No connect       24     PO     O     Test pin     64     VDD     1     Power supply terminal: +5V       25     ADSCK     O     32Fs/24Fs serial clock for A/D, D/A converters     65     NC     No connect       24     PO     O     Test pin, normally terminal: +5V     67     NC     No connect       25     ADSCK     O     32Fs/24Fs serial clock for A/D, D/A converters                                                                                                                       | 14      | SDO2    | 0   | Digital studio serial data out, PEQ output      | 54  | NC     |                                              | No connect                 |

| To     CRO     Output digital audio serial clock     57     NC     No connect       17     SCK     O     Output digital audio serial clock     57     NC     No connect       18     SDI     1     Input digital audio serial clock     59     NC     No connect       20     SCKI     I/O     Input digital audio serial clock     60     NC     No connect       21     VSS     1     Ground     61     NC     No connect       22     RDY     1     Test pin, high for normal operation     62     NC     No connect       23     VSS     1     Ground     63     CLIP     O     Clipping indicator       24     PO     O     Test pin     64     VDD     1     Power supply terminal: +5V       25     ADSCK     O     324Fs/S4Fs serial clock for A/D, D/A converters     66     NC     No connect       26     ADMCK     O     344Fs/S6Fs master clock for A/D, D/A converters     66     NC     No connect       28     VSS     1                                                                                                                                    | 15      | SDO1    | 0   | Digital audio serial data out, full output      | 55  | NC     |                                              | No connect                 |

| 18     SDI     1     Input digital audio serial data     58     NC     No connect       19     LRI     VO     Input digital audio serial clock     59     NC     No connect       20     SCKI     I/O     Input digital audio serial clock     60     NC     No connect       21     VSS     I     Ground     61     NC     No connect       22     RDV     I     Test pin. high for normal operation     62     NC     No connect       23     VSS     I     Ground     63     CLIP     O     Clipping Indicator       24     PO     O     Test pin. high for normal operation     63     CLIP     O     Clipping Indicator       25     ADSCK     O     32Fs/64Fs serial clock for A/D, D/A converters<br>(default 32Fs)     65     NC     No connect       26     ADMCK     O     384Fs/256Fs master clock for A/D, D/A converters<br>(default 32Fs)     67     NC     No connect       28     VSS     I     Ground     68     NC     No connect       2                                                                                                                 | 16      | LRO     | 0   | Output left/right frame clock                   | 56  | VSS    |                                              | Ground                     |

| 10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10<                                                                                                                                                                                                                                                                                                                                      | 17      | SCKO    | 0   | Output digital audio serial clock               | 57  | NC     |                                              | No connect                 |

| 13     14     Post of the strong management     60     NC     No connect       20     SCKI     I/O     Input digital audio serial clock     60     NC     No connect       21     VSS     I     Ground     61     NC     No connect       22     RDY     I     Test pin, high for normal operation     62     NC     No connect       23     VSS     I     Ground     63     CLIP     O     Clipping Indicator       24     PO     O     Test pin     64     VDD     I     Power supply terminal: +5V       25     ADSCK     O     25Fs/64Fs serial clock for A/D, D/A converters     65     NC     No connect       26     ADMCK     O     284Fs/256Fs master clock for A/D, D/A converters     66     NC     No connect       27     VDD     1     Power supply terminal: +5V     67     NC     No connect       28     VSS     1     Ground     68     NC     No connect       29     CGRES     1     Reset, must be hel                                                                                                                                                 | 18      | SDI     | 1   | Input digital audio serial data                 | 58  | NC     |                                              | No connect                 |

| 21USS1Ground61NCNo connect22RDY1Test pin, high for normal operation62NCNo connect23VSS1Ground63CLIPOClipping Indicator24PO0Test pin64VDD1Power supply terminal: +5V25ADSCK032Fs/64Fs serial clock for A/D, D/A converters<br>(default 32Fs)65NCNo connect26ADMCK0384Fs/256Fs master clock for A/D, D/A converters<br>(default 32Fs)66NCNo connect26ADMCK0384Fs/256Fs master clock for A/D, D/A converters<br>(default 32Fs)66NCNo connect27VDD1Power supply terminal: +5V67NCNo connect28VSS1Ground68NCNo connect29CGRES1Test pin, normally high69NCNo connect30RES1Reset, must be held low for at least two clock<br>cycles after power on<br>cycles after power on71NCNo connect31ENEXT1Test pin, normally low71NCNo connect32SEN1MPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A11Test pin. Low for normal operation73NCNo connect34A01Test pin. Low for normal operation74NCNo connect35VDD1Power sup                                                                                                                                         | 19      | LRI     | 1/0 | Input left/right frame clock                    | 59  | NC     | 1                                            | No connect                 |

| 111001Test pin, high for normal operation62NCNo connect23VSS1Test pin, high for normal operation63CLIPOClipping Indicator24POOTest pin64VDD1Power supply terminal: +5V25ADSCKO32Fs/64Fs serial clock for A/D, D/A converters65NCNo connect26ADMCKO33Fs/265Fs master clock for A/D, D/A converters66NCNo connect27VDD1Power supply terminal: +5V67NCNo connect28VSS1Ground68NCNo connect29CGRES1Test pin, normally high69NCNo connect30RES1Reset, must be held low for at least two clock<br>cycles after power on70VSS1Ground31ENEXT1Test pin, normally low71NCNo connect32SEN1MPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A11Test pin. Low for normal operation73NCNo connect34A01Test pin. Low for normal operation74NCNo connect35VDD1Power supply terminal: +5V75VDD1Power supply terminal: +5V36CS501Chip select, MPU interface enabled when CS0 = 076NCNo connect37CS11Chip select,                                                                                                                                                       | 20      | SCKI    | 1/0 | Input digital audio serial clock                | 60  | NC     |                                              | No connect                 |

| 11111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21      | VSS     | 1   | Ground                                          | 61  | NC     |                                              | No connect                 |

| 124PO0Test pin64VDD1Power supply terminal: +5V25ADSCK032Fs/64Fs serial clock for A/D, D/A converters<br>(default 32Fs)65NCNo connect26ADMCK0384Fs/256Fs master clock for A/D, D/A converters<br>(default 384Fs)66NCNo connect27VDD1Power supply terminal: +5V67NCNo connect28VSS1Ground68NCNo connect29CGRES1Test pin, normally high69NCNo connect29CGRES1Reset, must be held low for at least two clock<br>cycles after power on70VSS1Ground31ENEXT1Test pin, normally low71NCNo connect32SEN1MPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A11Test pin. Low for normal operation73NCNo connect34A01Test pin. Low for normal operation74NCNo connect35VDD1Power supply terminal: +5V75VDD1Power supply terminal: +5V36CS01Chip select, MPU Interface enabled when CS0 = 0<br>and CS1 = 176NCNo connect38SEL681MPU interface model: 68K = H, Z80 = L78NCNo connect39WR1Write Strobe (Z80), Write Enable (68K)79NCNo connect<                                                                                                                      | 22      | RDY     | 1   | Test pin, high for normal operation             | 62  | NC     |                                              | No connect                 |

| 25   ADSCK   0   32Fs/64Fs serial clock for A/D, D/A converters<br>(default 32Fs)   65   NC   No connect     26   ADMCK   0   384Fs/256Fs master clock for A/D, D/A converters<br>(default 384Fs)   66   NC   No connect     27   VDD   1   Power supply terminal: +5V   67   NC   No connect     28   VSS   1   Ground   68   NC   No connect     29   CGRES   1   Test pin, normally high   69   NC   No connect     30   RES   1   Reset, must be held low for at least two clock<br>cycles after power on   70   VSS   1   Ground     31   ENEXT   1   Test pin, normally low   71   NC   No connect     32   SEN   1   MPU serial interface enable. Serial = L, parallel =<br>H   72   NC   No connect     33   A1   1   Test pin. Low for normal operation   73   NC   No connect     34   A0   1   Test pin. Low for normal operation   74   NC   No connect     35   VDD   1   Power supply terminal: +5V <t< td=""><td>23</td><td>VSS</td><td>1</td><td>Ground</td><td>63</td><td>CLIP</td><td>0</td><td>Clipping Indicator</td></t<>                              | 23      | VSS     | 1   | Ground                                          | 63  | CLIP   | 0                                            | Clipping Indicator         |

| 25ADSCK0(default 32Fs)65NCNo connect26ADMCKO384Fs/256Fs master clock for A/D, D/A converters<br>(default 384Fs)66NCNo connect27VDD1Power supply terminal: +5V67NCNo connect28VSS1Ground68NCNo connect29CGRES1Test pin, normally high69NCNo connect30RESiReset, must be held low for at least two clock<br>cycles after power on70VSSIGround31ENEXT1Test pin, normally low71NCNo connect32SENIMPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A1ITest pin. Low for normal operation73NCNo connect34A0ITest pin. Low for normal operation74NCNo connect35VDDIPower supply terminal: +5V75VDDIPower supply terminal: +5V36CS0IChip select, MPU interface enabled when CS0 = 0<br>and CS1 = 177NCNo connect38SEL68IMPU interface mobile difference78NCNo connect39WRIWrite Strobe (Z80), Write Enable (68K)79NCNo connect                                                                                                                                                                                                                               | 24      | PO      | 0   | Test pin                                        | 64  | VDD    | 1                                            | Power supply terminal: +5V |

| 28ADMCK0(default 384Fs)30NCNCNo connect27VDD1Power supply terminal: $+5V$ 67NCNo connect28VSS1Ground68NCNo connect29CGRES1Test pin, normally high69NCNo connect30RES1Reset, must be held low for at least two clock<br>cycles after power on70VSS1Ground31ENEXT1Test pin, normally low71NCNo connect32SEN1MPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A11Test pin, Low for normal operation73NCNo connect34A01Test pin, Low for normal operation74NCNo connect35VDD1Power supply terminal: $+5V$ 75VDD1Power supply terminal: $+5V$ 36CS301Chip select, MPU interface enabled when CS0 = 0<br>and CS1 = 177NCNo connect38SEL681MPU interface enabled when CS0 = 0<br>and CS1 = 177NCNo connect39WR1Write Strobe (Z80), Write Enable (68K)79NCNo connect                                                                                                                                                                                                                                                                                         | 25      | ADSCK   | 0   |                                                 | 65  | NC     |                                              | No connect                 |

| 28VSS1Ground68NCNo connect29CGRES1Test pin, normally high69NCNo connect30RES1Reset, must be held low for at least two clock<br>cycles after power on70VSSIGround31ENEXT1Test pin, normally low71NCNo connect32SEN1MPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A11Test pin, Low for normal operation73NCNo connect34A01Test pin, Low for normal operation74NCNo connect35VDD1Power supply terminal: +5V75VDD1Power supply terminal: +5V36CS01Chip select, MPU interface enabled when CS0 = 0<br>and CS1 = 177NCNo connect38SEL681MPU interface mode: 68K = H, Z80 = L78NCNo connect39WR1Write Strobe (Z80), Write Enable (68K)79NCNo connect                                                                                                                                                                                                                                                                                                                                                                                                     | 26      | ADMCK   | 0   |                                                 | 66  | NC     |                                              | No connect                 |

| 29CGRES1Test pin, normally high69NCNo connect30RESiReset, must be held low for at least two clock<br>cycles after power on70VSSIGround31ENEXT1Test pin, normally low71NCNo connect32SEN1MPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A11Test pin. Low for normal operation73NCNo connect34A01Test pin. Low for normal operation74NCNo connect35VDD1Power supply terminal: +5V75VDD1Power supply terminal: +5V36CS01Chip select, MPU interface enabled when CS0 = 0<br>and CSI = 176NCNo connect38SEL681MPU interface mode: 68K = H, Z80 = L78NCNo connect39WR1Write Strobe (Z80), Write Enable (68K)79NCNo connect                                                                                                                                                                                                                                                                                                                                                                                                                               | 27      | VDD     | 1   | Power supply terminal: +5V                      | 67  | NC     |                                              | No connect                 |

| 25   Och Leb   1   Telop Jm, normally fingth   70   VSS   1   Ground     30   RES   1   Reset, must be held low for at least two clock<br>cycles after power on   70   VSS   1   Ground     31   ENEXT   1   Test pin, normally low   71   NC   No connect     32   SEN   1   MPU serial interface enable. Serial = L, parallel =<br>H   72   NC   No connect     33   A1   1   Test pin, Low for normal operation   73   NC   No connect     34   A0   1   Test pin, Low for normal operation   74   NC   No connect     35   VDD   1   Power supply terminal: +5V   75   VDD   1   Power supply terminal: +5V     36   CS0   1   Chip select, MPU interface enabled when CS0 = 0<br>and CS1 = 1   76   NC   No connect     37   CS1   1   Chip select, MPU interface enabled when CS0 = 0<br>and CS1 = 1   77   NC   No connect     38   SEL68   1   MPU interface mode: 68K = H, Z80 = L   78   NC   No connect     39   WR<                                                                                                                                             | 28      | VSS     | 1   | Ground                                          | 68  | NC     |                                              | No connect                 |

| 30HESIcycles after power on70VSSIChound31ENEXTITest pin, normally low71NCNo connect32SENIMPU serial interface enable. Serial = L, parallel =<br>H72NCNo connect33A1ITest pin. Low for normal operation73NCNo connect34A0ITest pin. Low for normal operation74NCNo connect35VDDIPower supply terminal: +5V75VDDIPower supply terminal: +5V36CS0IChip select, MPU interface enabled when CS0 = 0<br>and CSI = 176NCNo connect38SEL68IMPU interface mode: 68K = H, Z80 = L78NCNo connect39WRIWrite Strobe (Z80), Write Enable (68K)79NCNo connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29      | CGRES   | 1   | Test pin, normally high                         | 69  | NC     |                                              | No connect                 |

| 32   SEN   I   MPU serial interface enable. Serial = L, parallel =<br>H   72   NC   No connect     33   A1   I   Test pin. Low for normal operation   73   NC   No connect     34   A0   I   Test pin. Low for normal operation   74   NC   No connect     35   VDD   I   Power supply terminal: +5V   75   VDD   I   Power supply terminal: +5V     36   CS0   I   Chip select, MPU Interface enabled when CS0 = 0<br>and CSI = 1   76   NC   No connect     37   CS1   I   Chip select, MPU interface enabled when CS0 = 0<br>and CSI = 1   77   NC   No connect     38   SEL68   I   MPU interface mode: 68K = H, Z80 = L   78   NC   No connect     39   WR   I   Write Strobe (Z80), Write Enable (68K)   79   NC   No connect                                                                                                                                                                                                                                                                                                                                         | 30      | RES     | í   |                                                 | 70  | VSS    | 1                                            | Ground ,                   |

| 32   SEN   I   H   72   NC   No connect     33   A1   I   Test pin. Low for normal operation   73   NC   No connect     34   A0   I   Test pin. Low for normal operation   74   NC   No connect     35   VDD   I   Power supply terminal: +5V   75   VDD   I   Power supply terminal: +5V     36   CS0   1   Chip select, MPU interface enabled when CS0 = 0 and CSI = 1   76   NC   No connect     37   CS1   I   Chip select, MPU interface enabled when CS0 = 0 and CSI = 1   77   NC   No connect     38   SEL68   I   MPU interface mode: 68K = H, Z80 = L   78   NC   No connect     39   WR   I   Write Strobe (Z80), Write Enable (68K)   79   NC   No connect                                                                                                                                                                                                                                                                                                                                                                                                      | 31      | ENEXT   | 1   | Test pin, normally low                          | 71  | NC     |                                              | No connect                 |

| 34   A0   I   Test pin. Low for normal operation   74   NC   No connect     35   VDD   I   Power supply terminal: +5V   75   VDD   I   Power supply terminal: +5V     36   CS0   I   Chip select, MPU interface enabled when CS0 = 0<br>and CSI = 1   76   NC   No connect     37   CS1   I   Chip select, MPU interface enabled when CS0 = 0<br>and CSI = 1   77   NC   No connect     38   SEL68   I   MPU interface mode: 68K = H, Z80 = L   78   NC   No connect     39   WR   I   Write Strobe (Z80), Write Enable (68K)   79   NC   No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32      | SEN     | 1   |                                                 | 72  | NC     |                                              | No connect                 |

| 35   VDD   I   Power supply terminal: +5V   75   VDD   I   Power supply terminal: +5V     36   CS0   I   Chip select, MPU Interface enabled when CS0 = 0<br>and CSI = 1   76   NC   No connect     37   CS1   I   Chip select, MPU interface enabled when CS0 = 0<br>and CSI = 1   77   NC   No connect     38   SEL68   I   MPU interface mode: 68K = H, Z80 = L   78   NC   No connect     39   WR   I   Write Strobe (Z80), Write Enable (68K)   79   NC   No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33      | A1      | I   | Test pin. Low for normal operation              | 73  | NC     |                                              | No connect                 |

| 36   CS0   I   Chip select, MPU interface enabled when CS0 = 0 and CSI = 1   76   NC   No connect     37   CS1   I   Chip select, MPU interface enabled when CS0 = 0 and CSI = 1   77   NC   No connect     38   SEL68   I   MPU interface mode: 68K = H, Z80 = L   78   NC   No connect     39   WR   I   Write Strobe (Z80), Write Enable (68K)   79   NC   No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34      | AO      | I   | Test pin. Low for normal operation              | 74  | NC     |                                              | No connect                 |

| 36     CS0     1     and CSI = 1     70     NC     No connect       37     CS1     I     Chip select, MPU interface enabled when CS0 = 0<br>and CS1 = 1     77     NC     No connect       38     SEL58     I     MPU interface mode: 68K = H, Z80 = L     78     NC     No connect       39     WR     I     Write Strobe (Z80), Write Enable (68K)     79     NC     No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35      | VDD     | I   | Power supply terminal: +5V                      | 75  | . VDD  | 1                                            | Power supply terminal: +5V |

| S7     CS1     I     and CS1 = 1     II     III     IIII     IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36      | ರತರ     | 1   |                                                 | 76  | NC     |                                              | No connect                 |

| 39     WR     I     Write Strobe (Z80), Write Enable (68K)     79     NC     No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37      | CS1     | 1   |                                                 | 77  | NC     |                                              | No connect                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38      | SEL68   | T   | MPU interface mode: 68K = H, Z80 = L            | 78  | NC     |                                              | No connect                 |

| 40 DD L Write Stroke (SRK) 80 VSS L Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39      | WA      | T   | Write Strobe (Z80), Write Enable (68K)          | 79  | NC     |                                              | No connect                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40      | RD      | T   | Write Strobe (68K)                              | 80  | VSS    | 1                                            | Ground                     |

-New Japan Radio Co.,Ltd.-

# Specifications

Table 2 Absolute Maximum Ratings  $^{1}$  (V<sub>ss</sub> = 0 V)

| Parameter                                         | Symbol           | Minimum | Maximum               | Unit |

|---------------------------------------------------|------------------|---------|-----------------------|------|

| Supply Voltage (T <sub>A</sub> = 25°C)            | V <sub>DD</sub>  | -0.3    | 7                     | V    |

| Input, Output Pin Voltage (T <sub>A</sub> = 25°C) | V <sub>x</sub>   | -0.3    | V <sub>DD</sub> + 0.3 | V    |

| Operating Temperature                             | T <sub>OPR</sub> | -25     | 85                    | °C   |

| Storage Temperature                               | T <sub>STG</sub> | -55     | 150                   | °C   |

1. Absolute maximum ratings are stress ratings only, and functional operation beyond these limits is not guaranteed. Stress beyond the maximum rating may affect device reliability or cause permanent damage to the device.

# Table 3 Electrical Characteristics $(T_A = -20 \text{ C to } +70 \text{ C})$

| Parameter                    | Symbol           | Test Condition                    | Minimum               | Typical | Maximum              | Unit |

|------------------------------|------------------|-----------------------------------|-----------------------|---------|----------------------|------|

| Operating Voltage            | V <sub>DD</sub>  | V <sub>DD</sub> pins              | 4.75                  |         | 5.25                 | V    |

| Operating Current            | I <sub>DD</sub>  | f <sub>osc</sub> = 34 MHz         | -                     | · 90    | 125                  | mA   |

| High Level Input Voltage     | VIH              |                                   | 0.80 V <sub>DD</sub>  | 1       | V <sub>DD</sub>      | V    |

| Low Level Input Voltage      | VIL              |                                   | V <sub>SS</sub>       |         | 0.10 V <sub>DD</sub> | V    |

| High Level Input Current     | I <sub>IH</sub>  | $V_{IN} = V_{DD}$                 | -                     |         | 10                   | μA   |

| Low Level Input Current      | l <sub>IL</sub>  | V <sub>IN</sub> = V <sub>SS</sub> | -                     |         | 10                   | μA   |

| High Level Output Voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = 2 mA            | V <sub>DD</sub> - 1.0 |         | -                    | V    |

| Low Level Output Voltage     | V <sub>oL</sub>  | l <sub>oH</sub> = 2 mA            | -                     |         | 0.5                  | V    |

| Input Capacitance            | C <sub>IN</sub>  |                                   | -                     | 10      | 20                   | pF   |

| Clock Frequency <sup>1</sup> | f <sub>osc</sub> |                                   | 20                    |         | 34                   | MHz  |

| Ext. System Clock Duty Cycle | r <sub>EC</sub>  |                                   | 45                    |         | 55                   | %    |

1. For operation with 37 MHz clock frequency, contact factory.

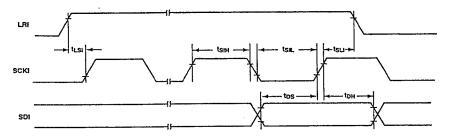

# Timing Parameters and Timing Diagrams

Table 4 Serial Data Input Timing P arameters ( $V_{DD}$  = 5V ± 5%,  $T_A$  = -20 °C to +70 °C,  $f_{CLK}$  = 34MHz)

| Parameter        | Symbol           | Minimum | Maximum | Unit |

|------------------|------------------|---------|---------|------|

| SCKI Period      |                  | 160     | -       | ns   |

| L Pulse Width    | t <sub>siL</sub> | 80      | -       | ns   |

| H Pulse Width    | t <sub>siH</sub> | 80      | -       | ns   |

| SCKI to LRI Time | t <sub>su</sub>  | 50      | •       | ns   |

| LRI to SCKI Time | t <sub>LSI</sub> | 75      | -       | ns   |

| Data Setup Time  | t <sub>DS</sub>  | 10      | -       | ns   |

| Data Hold Time   | t <sub>DH</sub>  | 10      |         | ns   |

,

Figure 6 Serial Data Input Timing

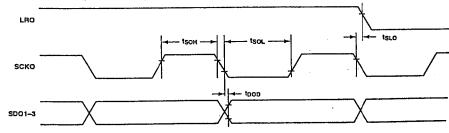

# Table 5 Serial Data Output Timing P arameter s ( $V_{DD}$ = 5V ± 5%, $T_A$ = -20 °C to +70 °C, $f_{CLK}$ = 34MHz, CL: LRO, SCKO, SDO = 5 pF)

| Parameter         | Symbol           | Minimum | Maximum | Unit |

|-------------------|------------------|---------|---------|------|

| SCKO Period       |                  | 160     | -       | ns   |

| L Pulse Width     | t <sub>SOL</sub> | . 80    | -       | ns   |

| H Pulse Width     | t <sub>son</sub> | 80      | -       | ns   |

| SCKO to LRO Time  | t <sub>SLO</sub> | -       | 5       | ns   |

| Data Output Delay | t <sub>DOD</sub> | -       | 5       | ns   |

# Figure 7 Serial Data Output Timing

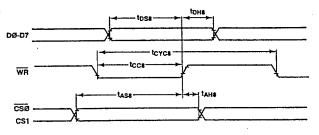

| Parameter              | Symbol           | Minimum | Maximum | Unit |

|------------------------|------------------|---------|---------|------|

| Address Setup Time     | t <sub>AS8</sub> | 100     | -       | · ns |

| Address Hold Time      | t <sub>AH8</sub> | 100     | -       | ns   |

| System Cycle Time      | tcycs            | 1,000   | •       | ns   |

| Read/Write Pulse Width | t <sub>ccs</sub> | 100     | -       | ns   |

| Write Data Setup Time  | t <sub>DS8</sub> | 10      | -       | ns   |

| Write Data Hold Time   | t <sub>DH8</sub> | 10      | -       | ns   |

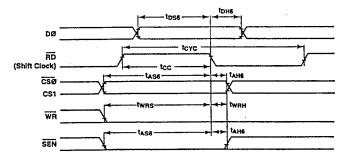

Table 6 Z80 Interface Timing P arameters ( $V_{DD}$  = 5V ± 5%,  $T_A$  = -20 °C to +70 °C,  $f_{CLK}$  = 34MHz)

Figure 8 Z80 Parallel Interface Timing (SEL68 Lo w)

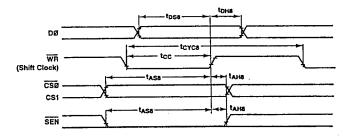

Figure 9 Z80 Serial Interface Timing (SEL68 Lo w)

4-222-

| Parameter                  | Symbol            | Minimum | Maximum | Unit |

|----------------------------|-------------------|---------|---------|------|

| Address Setup Time         | t <sub>AS6</sub>  | 100     | •       | ns   |

| Address Hold Time          | t <sub>AH6</sub>  | 100     | -       | ns   |

| System Cycle Time          | t <sub>CYC5</sub> | 1,000   | -       | ns   |

| Read/Write Pulse Width     | t <sub>CC5</sub>  | 100     | -       | ns   |

| Write Data Setup Time      | t <sub>DS6</sub>  | 10      | •       | ns   |

| Write Data Hold Time       | t <sub>DH6</sub>  | 10      | -       | ns   |

| Write-to-read Strobe Setup | twrs              | 100     | -       | ns   |

| Read-to-write Strobe Setup | t <sub>WRH</sub>  | 100     | -       | ns   |

| Table 7 68K Interface | Timing P arameter s (V <sub>p</sub> | $_{\rm D}$ = 5V ± 5%, T <sub>A</sub> = -20 °C to +70 °C, f <sub>CLK</sub> = 34MHz) |

|-----------------------|-------------------------------------|------------------------------------------------------------------------------------|

|-----------------------|-------------------------------------|------------------------------------------------------------------------------------|

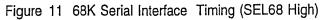

Figure 10 68K Parallel Interface Timing (SEL68 High)

-New Japan Radio Co.,Ltd.

# Functional Timing Diagrams

-New Japan Radio Co., Ltd.

# Functional Description

#### Spatializer N-2-2 Mode

Surround information from the audio source is extracted by the Dolby Pro Logic decoder processing in the NJU25019. Head Related Transfer Functions (HRTFs), based on the natural characteristics of the human hearing system, are used on both front and rear surround channels to synthesize virtual surround speakers to the side and rear of the listener. The Front HRTFs have frequency tailoring of the difference signals (L-R) to extend the sound image past the physical boundaries of the actual speakers. A different set of frequency coefficients are applied to

## Figure 17 Spatializ er N-2-2 Processing

the rear HRTFs that have much greater peak and valley differences. These coefficients are chosen so that the rear channels will virtualize behind the listener. The virtualized surround is then mixed into the left and right output. The center channel is also mixed into the left and right output. There is also a subwoofer output with low pass crossover filter that is active in all modes.

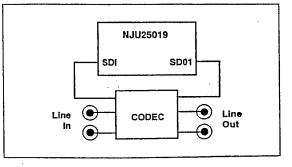

The NJU25019 initializes in N-2-2 mode with I<sup>2</sup>S audio data format for use with a codec (A/D+D/A) and does not require a microprocessor for 2channel 3D surround sound operation.

New Japan Radio Co., Ltd.

## Figure 19 2-Channel Surr ound System

## Dolby Pro Logic Mode

The NJU25019 can be switched from N-2-2 mode (2ch + optional subwoofer) to Dolby Pro Logic mode (5ch + optional subwoofer) using a microprocessor command. The NJU25019 has all the necessary controls to implement a complete Dolby Pro Logic system, including surround volume trim, surround delay using internal memory, noise sequencer, and center modes. Dolby 3 Stereo mode, Simulated Stereo mode for monophonic input sources, and Normal Stereo mode are also included in the chip.

Dolby Pro Logic processing with a DSP affords high performance with 24 bits of resolution and precise digital filtering for perfect matching between channels with exact consistency unit to unit. With the freedom to choose a wide variety of codecs, A/Ds, and D/As to fit the system cost and performance targets, the NJU25019 can be optimized for any market, from the most cost sensitive multimedia systems to audiophile equipment.

## Figure 20 Typical NJU25019 5.1-Channel Dolby Pro Logic System

# BBE<sup>®</sup>High Definition Audio

The BBE process is a proven method of improving the quality of any audio by restoring the transients lost in the dynamics of speakers, which create a progressively greater impedance with increasing frequencies. BBE compensates for the natural tendency of loudspeakers to add progressively longer delay times to the high frequencies. An equal and opposite delay curve of BBE for the low frequencies, delivers the high frequency transients first. At the same time, the digital process increases the amplitude of both high and low frequencies, resulting in boosted bass and treble. The result is a noticeable improvement in the presence and clarity of the audio, with the most accurate reproduction of live audio possible. Because BBE is a post virtualization audio enhancement, it does not alter the surround information or the 3D virtualization process. BBE's Lo Contour and Process can be adjusted by commands from the microprocessor, or it can be disabled entirely.

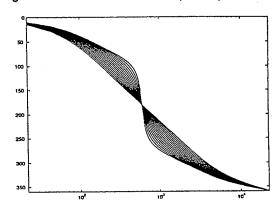

# Figure 21 BBE Gain vs. Frequency

Figure 22 BBE Phase vs.Frequenc y

#### Digital Audio Data Interface

New Japan Radio Co., Ltd.

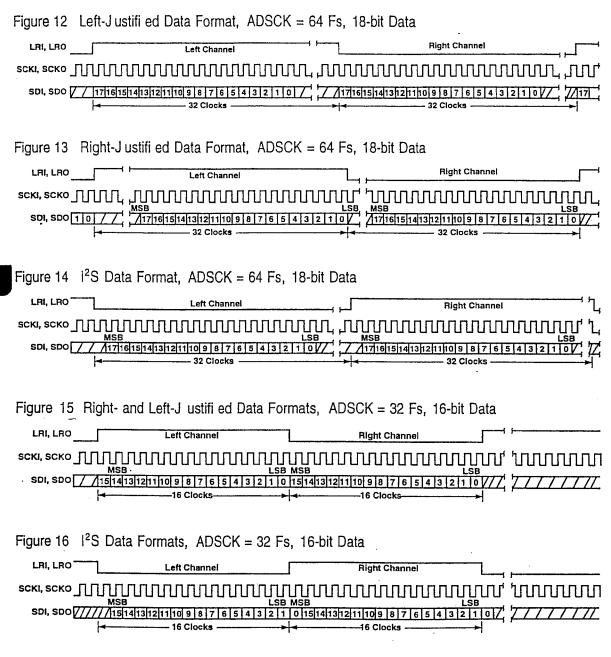

Three digital audio data formats are supported: left justified, right justified, and I<sup>2</sup>S. The data is always MSB first, 2's complement. Either 16-bit or 18-bit data can be accommodated. The polarities of the L/R clocks (LRI, LRO) are programmable, along with the active edge of the serial bit clocks (SCKI, SCKO). Master clock (ADMCK) and serial bit clock (ADSCK) outputs for the A/D and D/A converters are provided by an internal, programmable clock generator for synchronous operation with the DSP clock (768Fs). Asynchronous data rates are possible as long as the output is slaved to the input and it is close to the three supported sampling frequencies (32kHz, 44.1kHz, and 48kHz).

There is one stereo digital audio input and three stereo digital audio outputs for the L and R main channels, L and R surround

4-226-

channels, Center, and Subwoofer. All three serial data outputs must have identical data formats. In each data format mode, SCLK and LRCLK polarities are independently programmable for input and output. Audio data width (16/18 bits), SCK and MCK frequencies (32/64Fs, 256/384Fs, respectively) must be the same for both input and output.

#### **Clipping Indicator**

Each audio sample is examined for over-range condition on both the stereo input and on each output. Any time the audio data reaches full scale, a Clipping Indicator flag is set in the DSP, and is output on pin 63 as an active-High logic level, which can be used to turn on an LED through a transistor. The Clipping Indicator remains High for approximately 4,000 samples, or about 0.1s after clipping is first detected in order to be visible. When this period (0.1 s) has been exceeded without any clipping, the Clipping Indicator pin is returned to logic Low. The Clipping Indicator may also be monitored by a microprocessor, which can take other appropriate action.

#### Serial Data Formats

There are three serial data formats supported for interfacing an A/D and three D/As to the digital audio interface. Either Left

Justified, Right Justified, or I<sup>2</sup>S mode is selected by the FMT0 and FMT1 bits in the second byte of the four-byte System State Download Command. In Left Justified mode, the MSB is aligned to the edge of LRI or LRO. The data is positioned at the left or "front" side of the L/R pulse (see Figure 12). In Right Justified mode, the LSB is aligned to the LRI or LRO edge. The data is at the right or "rear" of the L/R pulse (see Figure 13). Sometimes this mode is called Japanese mode or EIAJ mode. The I<sup>2</sup>S mode is similar to Left Justified mode, except that the data Is delayed one SCLK period and the sense of LRI and LRO is inverted (see Figure 14). In I<sup>2</sup>S mode, LRI and LRO must be low for left channel data and high for right channel data, the opposite of other modes. The polarity of LRI and LRO can be inverted independently in any mode by the use of the LRI and LRO.

Normally, the serial data bits generated by a source change on the falling edge of the serial clock so that they can be easily clocked into a shift register on the rising clock edge. Considering an A/D as the source and the NJU25019 as a destination, the default setting is to clock the serial data input, SDI, in on the rising edge of SCKI. This can be changed to clock data in on the falling edge using the SCKI bit in the System Download Command.

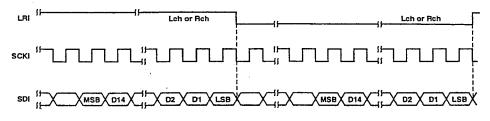

### Figure 23 Serial Data Input Format

New Japan Radio Co., Ltd.

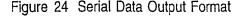

For the output serial data, the NJU25019 is considered the source and the D/As are considered the destination. The default interface setting is for data to be clocked out of SDO on the falling edge of SCKO so that the D/A clocks data in on the rising edge. This can be changed independently of the input and interface mode using the SCKO bit in the System Download Command.

The MS (Master/Slave) bit in the fourth System State Download Command byte selects either Master mode or Slave mode. In Right Justified mode, Master mode (MS = 0) is defined such that SCKO and LRO are generated from an internal divider derived from the 768Fs DSP clock (XI). In Slave mode (MS = 1) SCKO and LRO are the same as SCKI and LRI on the input. This mode should be used for asynchronous data rates, such as data from an S/PDIF receiver connected to the Digital Output from a laser disc player. The output D/A's must be synchronized to the input data by using the low jitter, recovered clock from the S/PDIF receiver to the D/A master clock. When an A/D is used, its master clock should be synchronous to the NJU25019 using ADMCK at 256Fs or 384Fs. In this case either Master mode or Slave mode will work. The default setting is Master mode (MS = 0).

In I<sup>2</sup>S mode, Master and Slave modes have slightly different meanings. Relative to the NJU25019, Slave mode (MS = 1) is

defined as LRI and SCKI being inputs from the A/D. This means that the A/D must be in Master mode with L/R and SCLK outputs. Conversely, when the NJU25019 is in Master mode (MS = 0), LRI and SCKI are outputs that drive the L/R and SCLK inputs of an A/D operating in slave mode. SCKO and LRO to the D/As are always outputs. The D/A converters can run only in Slave mode, receiving both the L/R and SCLK from the NJU25019 LRO and SCKO are derived from the 768Fs DSP clock. When slave mode is selected, LRO and SCKO are generated by the LRI and SCKI inputs. Slave mode should be used for asynchronous audio data.

When using a codec in slave mode and operating the NJU25019 in I<sup>2</sup>S Master mode, the LRO signal must be used to drive the L/R input of the codec. Although LRI is not used, it must be programmed with the opposite polarity. This is the default setting upon initialization after reset (LRI=0, LRO=1) for typical 2-channel applications. For more details, refer to the Demonstration Board User's Guide. In all other modes or when using separate A/D and D/A converters that use both LRI and LRO, respectively, the polarity should be the same for LRI and LRO.

in Left Justified mode, only Slave mode (MS = 0) is allowed. The A/D is required to be in Master mode and supplies LRI and

SCKI to the NJU25019 LRO and SCKO are generated from LRI and SCKI inputs.

For each data format, the serial clock frequency for SCKI and SCKO is selected using ADSCK in the System Download Command: either 32Fs (32-bit clocks per sample) or 64Fs (64-bit clocks per sample). SCKI and SCKO must be the same frequency. This clock is generated internally for the SCKI and SCKO in Master mode, but is also available as an output on the ADSCK pin. It is derived from the 768Fs Input Clock to the NJU25019

If SCKI and SCKO are selected to be 32Fs, the data length must be set to 16-bits (BIO = 0) because a stereo pair of 16-bit channels needs all 32 clocks per sample. In this case, both Left and Right Justified modes look exactly the same (see Figure 15), and either mode setting will work. In  $I^2S$  mode, the data bits appear shifted by one SCLK and the L/R is inverted (see Figure 16).

An output clock, ADMCK, is derived from the NJU25019 768Fs Input Clock for use as an A/D or D/A master clock. ADMCK is set to 256Fs or 384Fs using the ADMCK bit in the System Download Command.

#### Microcontroller Interface

There are two microprocessor interface modes that can be used to work with a variety of microcontrollers, including 68000, Z80, or 8031 type interfaces. The primary difference between modes is that data is latched on the rising edge of  $\overline{WR}$  in Z80 mode, while data is latched on the falling edge of  $\overline{RD}$  in 68K mode. For 68K mode, SEL68 is set high, and for Z80 it is set low. The interface may be configured for 8-bit serial data by a logic low on  $\overline{SEN}$ , and clocking the data in using  $\overline{WR}$  or  $\overline{RD}$  as the serial bit clock, depending on the mode, Z80 (rising edge) or 68K (falling edge), respectively.

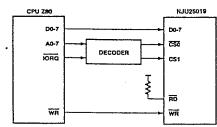

#### Figure 25 Z80 Interface

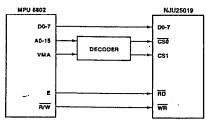

### Figure 26 68K Interface

All of the microprocessor commands in the NJU25019 consist of multiple bytes of data. After the last byte is received, the DSP may use the available time at the end of audio processing during each audio sample to calculate coefficients required for the new parameters. Each command may take a different amount of time, depending on the parametric data to be calculated. Therefore, the NJU25019 has a pin that can be used for a handshake protocol using pin 62, HSHK, for optimum data transfer from the host to the DSP. The NJU25019 can accept data without using the Handshake pin as long as the worst case processing time, 5ms, is inserted between bytes and commands.

The HSHK pin toggles after each byte is received, processed, and the DSP is ready to receive the next byte. The procedure for the microprocessor is to read the state of the pin before sending a command byte to the NJU25019 Before the next byte can be sent, the microprocessor must wait for the pin to change state. The only exception is the first byte after the NJU25019 has been reset, either by turning the power on or with a hardware reset on pin 30, RES. The microprocessor must not wait for a change of state before sending the first byte in this case. The initial state of HSHK is logic Low.

#### Parallel Interface—Z80 Mode

Writing commands to the NJU25019 from a Z80 type microprocessor is accomplished by setting SEL68 Low, placing data on the input data port, D0 to D7, setting the chip selects, and strobing  $\overline{WR}$  Low then High. Successive writes, as in the four-byte System Download Command, can be done without resetting the chip select(s). It is recommended to return the Chip Select to the inactive state as soon as the command is sent. The recommended sequence for writing parallel data to the NJU25019 is:

- 1. Read state of HSHK (if using handshake interface).

- 2. Set RD High (can be tied to Vcc).

- 3. Place data on the data port, D0:7.

- Assert chip selects, (CS0 = 0 and CS1 = 1). One can be permanently tied to its active state, while the other is controlled.

- 5. Strobe WR Low, then High.

- 6. Deactivate chip selects.

- Wait until HSHK changes state or 5 ms before sending next byte or command.

#### Parallel Interface-68K Mode

In 68K mode (SEL68 High)  $\overline{\text{RD}}$  acts as a strobe for both read and write operations.  $\overline{\text{WR}}$  defines whether a read or write is to be performed (L = write to NJU25019 H = there is no provision for reading fromNJU25019). Since only write operations are allowed,  $\overline{\text{WR}}$  can be tied Low. The recommended sequence to write parallel data to the NJU25019in this mode is:

- 1. Read state of HSHK (if using handshake interface).

- 2. Set WR Low (can be tied to GND).

- 3. Place data on the data port, D0:7.

- 4. Assert chip selects,  $(\overline{CS0} = 0 \text{ and } CS1 = 1)$ .

One can be permanently tied to its active state, while the other is controlled.

5. Strobe RD High, then Low.

New Japan Radio Co., Ltd.

#### Serial Interface

In serial interface mode ( $\overline{SEN} = 0$ ), D0 is used for the serial data input. Two types of interface modes are supported. In Z80 mode (SEL68 Low)  $\overline{WR}$  is used as a serial bit clock. In 68K mode (SEL68 High),  $\overline{RD}$  is used to clock the serial data. Data is clocked in 8 bits at a time with a maximum data rate of 1 MHz. As in Parallel mode above, after each byte (8 serial data bits), HSHK must change state or a wait time of 5 ms must occur before the next byte or command is sent.

#### Serial Interface—Z80 Mode

When using a microprocessor with a Z80 type interface, writing serial data to the NJU25019 is done by clocking the data in on rising edges of the  $\overline{WR}$ , with  $\overline{RD}$  held High (SEL68 = 0). The idle state of  $\overline{WR}$  must be High when  $\overline{CS0}$  and CS1 become active and return to inactive states. The recommended sequence is:

- 1. Read state of HSHK (if using handshake interface).

- 2. Set  $\overline{\text{SEN}} = 0$

- 3. Assert chip selects,  $(\overline{CS0} = 0 \text{ and } CS1 = 1)$ .

- 4. Set RD High.

- 5. Clock in serial data with WR (rising edge).

- 6. Deactivate chip selects.

- Wait until HSHK changes state or 5 ms before sending next byte or command.

### Serial Interface-68K Mode

For 68K type microprocessors, the function of  $\overline{RD}$  and  $\overline{WR}$  is opposite of the Z80. Writing serial data to the NJU25019is done by setting  $\overline{WR}$  Low and clocking the data in on rising edges of  $\overline{RD}$  (SEL68 = 1). The idle state of  $\overline{RD}$  must be Low when  $\overline{CS0}$ and CS1 become active and return to inactive states. The recommended sequence is:

- 1. Read state of HSHK (if using handshake interface).

- Set SEN = 0.

- 3. Assert chip selects,  $(\overline{CS0} = 0 \text{ and } CS1 = 1)$ .

- 4. Set WR Low.

- 5. Clock in serial data with RD (falling edge).

- 6. Deactivate chip selects.

- Wait until HSHK changes state or 5 ms before sending next byte or command.

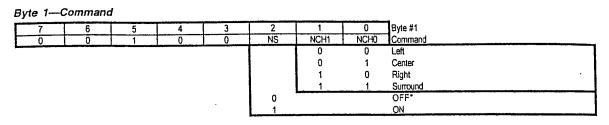

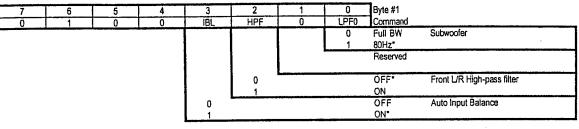

## Microcontroller Command Descriptions

In the following tables, \* indicates the default setting.

| Operating Mode                             | Spatializer N-2-2 (2.1 channel output)                                 |

|--------------------------------------------|------------------------------------------------------------------------|

| BBE Sound Enhancement                      | OFF                                                                    |

| Front Filter                               | OFF                                                                    |

| Subwooler Crossover                        | 80Hz                                                                   |

| Auto Input Balance                         | ON                                                                     |

| Noise Sequencer                            | OFF                                                                    |

| Noise Sequencer Channel                    | Left                                                                   |