# Clock Driver with 20 Clock Outputs

#### **Product Features**

- · Low-Noise Phase-Locked Loop Clock Distribution.

- Allows Clock Input to have Spread Spectrum modulation for EMI reduction. The clock outputs track the Clock Input modulation.

- Maximum clock frequency of 125 MHz.

- · Zero Input-to-Output delay.

- Low jitter: Cycle-to-Cycle jitter ±100ps max.

- · On-chip series damping resistor at clock output drivers for low noise and EMI reduction.

- Operates at 3.3V V<sub>CC</sub>.

- Output-to-Output skew less than 200ps.

- Package: Plastic 56-pin TSSOP (A).

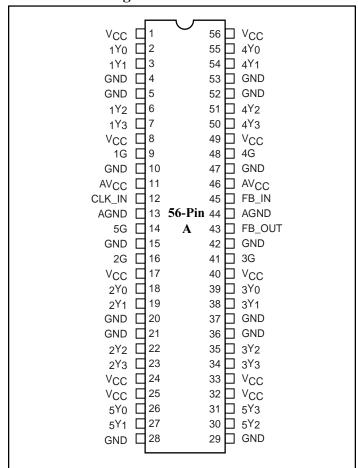

## **Product Pin Configuration**

### **Product Description**

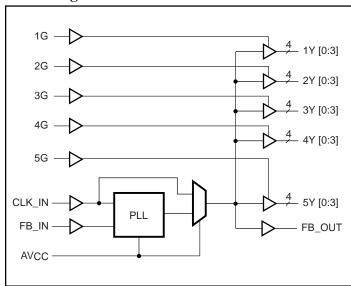

The PI6C2520 is a low-skew, low-jitter, phase-locked loop (PLL) clock driver, distributing low-noise clock signals for Networking Applications. By connecting the feedback FB OUT output to the feedback FB IN input, the propagation delay from the CLK IN input to any clock output will be nearly zero. This zero-delay feature allows the CLK IN input clock to be distributed, providing 5 banks of 4 clocks and an extra clock for feedback.

Low-Noise Phase-Locked Loop

For test purposes, the PLL can be bypassed by strapping AV<sub>CC</sub> to ground. The PI6C2520, which allows a Spread Spectrum clock input, operates at 3.3V V<sub>CC</sub> and provides integrated series-damping resistors that make it ideal for driving point-to-point loads. Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at the input clock.

Each bank of outputs can be enabled or disabled via the 1G, 2G, 3G, 4G, and 5G control inputs. When the G inputs are high, the outputs switch in phase and frequency with CLK IN. When the G inputs are low, the outputs are disabled to the logic low state.

## **Block Diagram**

PS8435B 07/25/00

## **Pin Functions**

| Pin Name Pin Number Type |                                             | Type   | Description                                                                                                                                                                                    |  |  |

|--------------------------|---------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK_IN                   | 12                                          | I      | Clock input. CLK allows spread spectrum.                                                                                                                                                       |  |  |

| FB_IN                    | 45                                          | Ι      | Feedback input. FB_IN provides the feedback signal to the internal PLL.                                                                                                                        |  |  |

| 1G                       | 9                                           | Ι      | Output bank enable. When 1G is LOW, outputs 1Y[0:3] are disabled to a logic low state. When 1G is HIGH, all outputs 1Y[0:3] are enabled.                                                       |  |  |

| 2G                       | 16                                          | Ι      | Output bank enable. When 2G is LOW, outputs 2Y[0:3] are disabled to a logic low state. When 2G is HIGH, all outputs 2Y[0:3] are enabled.                                                       |  |  |

| 3G                       | 41                                          | Ι      | Output bank enable. When 3G is LOW, outputs 3Y[0:3] are disabled to a logic low state. When 3G is HIGH, all outputs 3Y[0:3] are enabled.                                                       |  |  |

| 4G                       | 48                                          | Ι      | Output bank enable. When 4G is LOW, outputs 4Y[0:3] are disabled to a logic low state. When 4G is HIGH, all outputs 4Y[0:3] are enabled.                                                       |  |  |

| 5G                       | 14                                          | Ι      | Output bank enable. When 5G is LOW, outputs 5Y[0:3] are disabled to a logic low state. When 5G is HIGH, all outputs 5Y[0:3] are enabled.                                                       |  |  |

| FB_OUT                   | 43                                          | O      | Feedback output. FB_OUT is dedicated for external feedback. FB_OUT has an embedded series-damping resistor of the same value as the clock outputs 1Yx, 2Yx, 3Yx, 4Yx, and 5Yx.                 |  |  |

| 1Y[0:3]                  | 2,3,6,7                                     | О      | Clock outputs. These outputs provide low-skew copies of CLK. Each output has an embedded series-damping resistor.                                                                              |  |  |

| 2Y[0:3]                  | 18,19,22,23                                 | О      | Clock outputs. These outputs provide low-skew copies of CLK. Each output has an embedded series-damping resistor.                                                                              |  |  |

| 3Y[0:3]                  | 39,38,35,34                                 | О      | Clock outputs. These outputs provide low-skew copies of CLK. Each output has an embedded series-damping resistor.                                                                              |  |  |

| 4Y[0:3]                  | 55,54.51,50                                 | О      | Clock outputs. These outputs provide low-skew copies of CLK. Each output has an embedded series-damping resistor.                                                                              |  |  |

| 5Y[0:3]                  | 26,27,30,31                                 | О      | Clock outputs. These outputs provide low-skew copies of CLK. Each output has an embedded series-damping resistor.                                                                              |  |  |

| $AV_{CC}$                | 11,46                                       | Power  | Analog power supply. $AV_{CC}$ can be also used to bypass the PLL for test purposes. When $AV_{CC}$ is strapped to ground, PLL is bypassed and CLK is buffered directly to the device outputs. |  |  |

| AGND                     | 13,44                                       | Ground | Analog ground. AGND provides the ground reference for the analog circuitry                                                                                                                     |  |  |

| V <sub>CC</sub>          | 1,8,17,24,25,32,33,40,<br>49,56             | Power  | Power supply                                                                                                                                                                                   |  |  |

| GND                      | 4,5,10,15,20,21,28,29,<br>36,37,42,47,52,53 | Ground | Ground                                                                                                                                                                                         |  |  |

2

# **Absolute Maximum Ratings** (Over Operating Free-Air Temperature, unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                              | 0.5V to 4.6V                  |

|------------------------------------------------------------------------------------|-------------------------------|

| Input voltage range, V <sub>I</sub> (1)                                            | 0.5V to 6.5V                  |

| Voltage range applied to any output in the high or low state, $V_0^{(1,2)}$        | $-0.5$ V to $V_{CC}$ $+0.5$ V |

| Input clamp current, $I_{IK}(V_I \le 0)$                                           | 50mA                          |

| Output clamp current, $I_{OK}$ ( $V_O$ <0 or $V_O$ > $V_{CC}$ )                    | ±50mA                         |

| Continuous output current, I <sub>O</sub> (V <sub>O</sub> - 0 to V <sub>CC</sub> ) | ±50mA                         |

| Continuous current through each V <sub>CC</sub> or GND                             | ±100mA                        |

| Maximum power dissipation at $T_A = 55^{\circ}C$ (in still air) <sup>(3)</sup>     |                               |

| Storage Temperature Range, T <sub>stg</sub>                                        | -65°C to 150°C                |

<sup>†</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

#### Notes:

- 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. This value is limited to 4.6V maximum.

- 3. Maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

## **Recommended Operating Conditions**<sup>(4)</sup>

| Symbol          | Parameter                               | Min. | Max.            | Units     |  |

|-----------------|-----------------------------------------|------|-----------------|-----------|--|

| $V_{CC}$        | Supply voltage                          | 3    | 3.6             |           |  |

| V <sub>IH</sub> | High-level input voltage                | 2    |                 | $_{ m V}$ |  |

| V <sub>IL</sub> | V <sub>IL</sub> Low-level input voltage |      | 0.8             | V         |  |

| VI              | Input Voltage                           | 0    | V <sub>CC</sub> | 1         |  |

| I <sub>OH</sub> | High-level output current               |      | -12             | A         |  |

| I <sub>OL</sub> | Low-level output current                |      | 12              | mA        |  |

| TA              | Operating free-air temperature          | 0    | 70              | °C        |  |

#### Notes:

#### **Function Table**

| xG | CLK_IN | xY [0:3] | FB_OUT |

|----|--------|----------|--------|

| L  | L      | L        | L      |

| L  | Н      | L        | Н      |

| Н  | L      | L        | L      |

| Н  | Н      | Н        | Н      |

#### Note:

x is from 1 to 5

<sup>4.</sup> Unused inputs must be held high or low to prevent them from floating.

## Electrical Characteristics (Over Recommended Operating Free-air Temperature Range, unless otherwise noted)

| Symbol                                                                                                      | Test Condition                           | V <sub>CC</sub> | Min.                 | Тур.(1) | Max. | Units |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|----------------------|---------|------|-------|

| V <sub>IK</sub> , Input clamp voltage Input current at -18mA                                                |                                          | 3V              |                      | -0.79   | -1.2 |       |

|                                                                                                             | $I_{OH} = -100 \mu A$                    | Min. to Max.    | V <sub>CC</sub> -0.2 | 2.99    |      |       |

| $ m V_{OH}$                                                                                                 | $I_{OH} = -12mA$                         | 21/             | 2.1                  | 2.66    |      | V     |

|                                                                                                             | $I_{OH} = -6mA$                          | 3V              | 2.4                  | 2.83    |      |       |

|                                                                                                             | $I_{OL} = 100 \mu A$                     | Min. to Max.    |                      | 0.01    | 0.2  |       |

| $ m V_{OL}$                                                                                                 | $I_{OL} = 12mA$                          | 21/             |                      | 0.3     | 0.8  |       |

|                                                                                                             | $I_{OL} = 6mA$                           | 3V              |                      | 0.15    | 0.55 |       |

| I <sub>I,</sub> Input current                                                                               | Clock input voltage = $V_{CC}$ or GND    | 2.61/           |                      |         | ±5   |       |

| I <sub>CC</sub> , Analog supply current                                                                     | Clock input voltage = $V_{CC}$ or GND    | 3.6V            |                      |         | 20   | μA    |

| Ci                                                                                                          | Input voltage = $V_{CC}$ or GND          | 2.237           |                      | 4       | 3.5  | pF    |

| Co                                                                                                          | $C_{O}$ Output voltage = $V_{CC}$ or GND |                 |                      | 6       |      |       |

| $\Delta I_{CC} \qquad \qquad \text{One input @ $V_{CC}$ $-0.6$V,} \\ \text{other inputs @ $V_{CC}$ or GND}$ |                                          | 3.3V to 3.6V    |                      | 4.0     | 500  | μА    |

#### **Notes:**

## Timing Requirements (Over Recommended Ranges of Supply Voltage and Operating Free-Air Temperature).

| Symbol                     | Parameter                         | Min. | Max. | Units | Note |

|----------------------------|-----------------------------------|------|------|-------|------|

| $F_{CLK}$                  | Clock Frequency                   | 25   | 125  | MHz   | 1    |

| D <sub>CYI</sub>           | Input clock duty cycle            | 40   | 60   | %     |      |

| t <sub>Stabilization</sub> | Stabilization Time after power up |      | 1    | ms    |      |

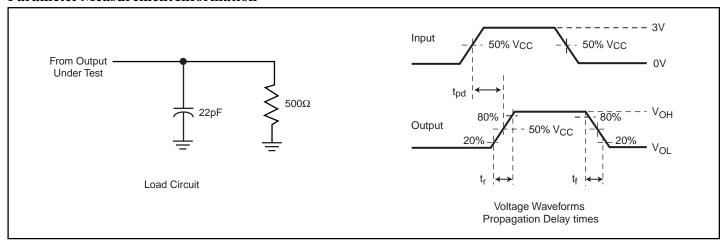

# Switching Characteristics (Over Recommended Ranges of Supply Voltage & Operating Free-Air Temperature, $C_L = 22 pF$ ) (1,3)

|                           |                              |                  | $V_{CC} = 3.3V \pm 0.3V$ |      |      |       |

|---------------------------|------------------------------|------------------|--------------------------|------|------|-------|

| Parameter                 | From (Input)                 | To (Output)      | Min.                     | Тур. | Max. | Units |

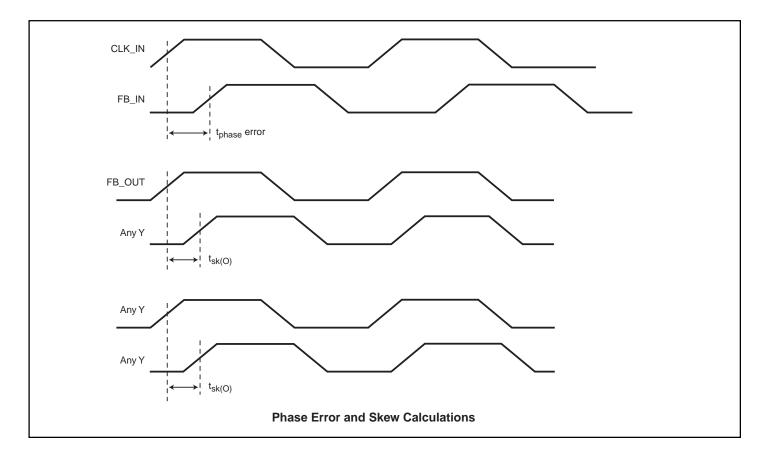

| t <sub>phase</sub> error  | CLK_IN↑ = 100MHz             | FB_IN↑           |                          | 170  |      |       |

| t <sub>sk(O)</sub> (2)    | Any Y or FBOUT               |                  |                          |      | 200  | ps    |

| Jitter <sub>(pk-pk)</sub> | F(CLK_IN> 66MHz)             |                  | -100                     |      | 100  |       |

| Dustry arvala             | F(CLK_IN ≤ 66MHz)            | Am. V on ED. OUT | 45                       |      | 55   | %     |

| Duty cycle                | F(CLK_IN > 66MHz)            | Any Y or FB_OUT  | 45                       |      | 55   | 70    |

| t <sub>r</sub>            | Management from 2007 to 9007 |                  | 0.7                      |      | 2.8  |       |

| $t_{\mathrm{f}}$          | Measured from 20% to 80%     |                  | 1.2                      |      | 2.8  | ns    |

#### **Notes:**

- 1. These parameters are not production tested.

- 2. The  $t_{sk(0)}$  specification is only valid for equal loading of all outputs.

- 3. The specifications for parameters in this table are applicable only after any appropriate stabilization time has elapsed.

4

PS8435B 07/25/00

<sup>1.</sup> For Min. or Max. conditions, use the appropriate value specified under recommended operating conditions.

#### **Parameter Measurement Information**

#### **Notes:**

- 1. C<sub>L</sub> includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: CLK\_IN  $\leq$  100MHz,  $Z_O = 50$  ohms,  $t_f \leq$  1.2ns,  $t_f \leq$  1.2ns.

- 3. The outputs are measured one at a time with one transition per measurement.

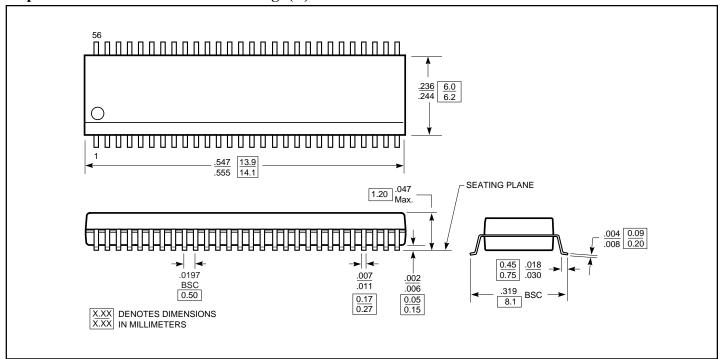

## 56-pin Thin Shrink Small-Outline Package (A)

## **Ordering Information**

| Part Number | Ordering P/N | Package      |

|-------------|--------------|--------------|

| PI6C2520    | PI6C2520A    | 56-Pin TSSOP |

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com