# SOFTWARE PROGRAMMABLE, 12-BIT, DATA ACQUISITION SYSTEM (DAS)

# **FEATURES**

- MUX, inst. amp, S/H, A/D in a compact 40-pin DIP

- Software programmable gain instrumentation amplifier (SPGIA)

- Input and output offset adjust

- 126 dB dynamic range

# **DESCRIPTION**

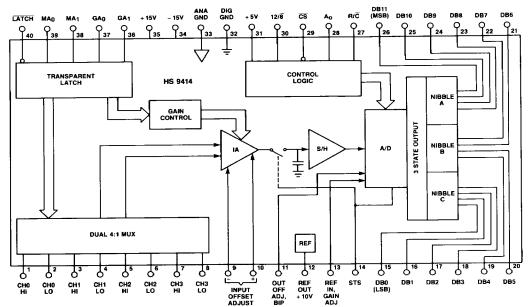

The HS9414 provides complete 12-bit data acquisition functionality in a 40-pin DIP. The HS9414 includes a 4-channel differential input multiplexer, a software programmable instrumentation amplifier, a sample and hold circuit and the HS574A, 12-bit,  $25\mu sec$  A/D converter. Specifications are guaranteed for the complete system instead of for each individual component.

The HS9414 is offered in a ceramic package for commercial (0°C to +70°C) and military (-55°C to +425°C) applications with processing available in full compliance with MIL-STD-883C.

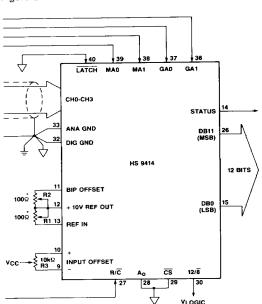

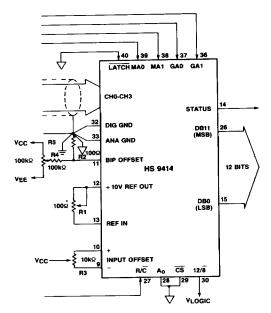

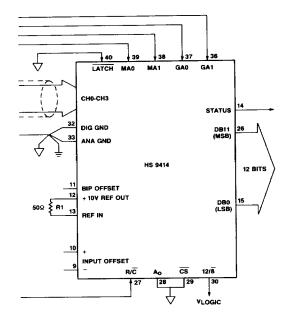

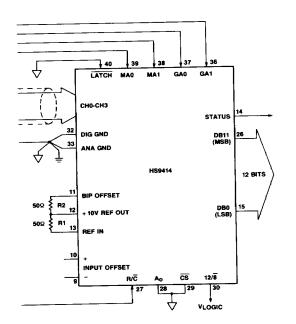

# **FUNCTIONAL DIAGRAM**

# **SPECIFICATIONS**

(Typical @ +25°C, V<sub>CC</sub> = +15V, V<sub>EE</sub> = -15V, V<sub>LOGIC</sub> = +5V unless otherwise specified)

| MODEL                                                                                                                                        | HS 9414                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| ANALOG INPUTS                                                                                                                                |                                                                                               |

| Number of Inputs                                                                                                                             | 4 Differential                                                                                |

| Normber of migrations (G = 1)* Unipolar ( - 1) Bipolar ( - 2)                                                                                |                                                                                               |

| Unipolar ( = 1)                                                                                                                              | 0 to + 10V or ±5V<br>± 10V                                                                    |

| Bipolar ( - 2)                                                                                                                               | $\pm 10V$<br>$\pm (11 - \frac{V_{IN} Diff \times Gain}{2})$                                   |

| Common Mode Voltage Range                                                                                                                    | 2                                                                                             |

| Differential Mode Voltage Range                                                                                                              | ±( 2(10 -  CMV ) )                                                                            |

| Input Offset Voltage (Unipolar) <sup>3</sup>                                                                                                 |                                                                                               |

| G = 1<br>G = 10<br>G = 100                                                                                                                   | ± 0.5 LSB                                                                                     |

| G = 10                                                                                                                                       | ± 100 µV<br>± 50 vV 250 vV max                                                                |

| G= 100<br>G= 500                                                                                                                             | ± 0.5 LSB<br>± 100 µV<br>± 50 µV, 250 µV max<br>± 50 µV, 250 µV max                           |

| Input CH to CH Offset Voltage                                                                                                                | ν ۷ 2                                                                                         |

| CMBR                                                                                                                                         |                                                                                               |

| G=1<br>G=10                                                                                                                                  | <ul> <li>80 dB typ, -76 dB max</li> <li>100 dB typ, -90 dB max</li> <li>120 dB typ</li> </ul> |

| G = 10<br>G = 100, G = 500                                                                                                                   | - 120 dB typ                                                                                  |

| Input Dynamic Range                                                                                                                          | 126 dB                                                                                        |

| Input Bias Current                                                                                                                           | 60 nA                                                                                         |

| Input Resistance                                                                                                                             | 1 GQ                                                                                          |

| Input Capacitance                                                                                                                            | 25 pF                                                                                         |

| Input Offset Current                                                                                                                         | 60 nA                                                                                         |

| input Noise Voltage                                                                                                                          | 2 <sub>μ</sub> V RMS, 10 μV p⋅p @G = 500                                                      |

| DIGITAL INPUTS                                                                                                                               | ,                                                                                             |

|                                                                                                                                              |                                                                                               |

| Logic Inputs<br>CS, R/C, A <sub>p</sub> , 12/8<br>Logic 11                                                                                   |                                                                                               |

| Logic 10                                                                                                                                     | + 2.0V min, + 5.5V max<br>- 0.5V min, + 0.8V max<br>±50 A max<br>5 pF                         |

| Logic 11"<br>Logic 10"<br>Current                                                                                                            | - 0.5V min, + 0.8V max                                                                        |

| Current<br>Capacitance                                                                                                                       | 5 pF                                                                                          |

| Control Input, 12/8                                                                                                                          | Hardwire to V <sub>LOGIC</sub> or DIG COM                                                     |

| Minimum Start Pulse                                                                                                                          | 200,0                                                                                         |

| CS-Negative<br>R/C-Negative                                                                                                                  | 120 nsec                                                                                      |

| R/C-Negative                                                                                                                                 | 120 nsec                                                                                      |

| LATCH                                                                                                                                        | 33 nsec                                                                                       |

| Data Set-Up Time<br>MA0, MA1, GA0, GA1                                                                                                       | 33 nsec                                                                                       |

|                                                                                                                                              | 1 TTL Load                                                                                    |

| Fan-Out                                                                                                                                      | TITE LOAD                                                                                     |

| SIGNAL DYNAMICS                                                                                                                              |                                                                                               |

| A/D Conversion Time                                                                                                                          | 25 µsec typ. 30 µsec max                                                                      |

| System Throughput Rate?                                                                                                                      | 00.0111                                                                                       |

| System Throughput Rate <sup>2</sup> G = 1, 10 (0.01½ Settling Accuracy) G = 100 (0.015½ Settling Accuracy) G = 500 (0.02½ Settling Accuracy) | 28 6 kHz max<br>17 kHz max                                                                    |

| G = 500 (0 02% Settling Accuracy)                                                                                                            | 10 kHz typ                                                                                    |

| Gain Switching Time and<br>IA Settling Time<br>G = 1.10<br>G = 100                                                                           |                                                                                               |

| IA Settling Time                                                                                                                             | 10 usec typ                                                                                   |

| G = 100                                                                                                                                      | 50 µsec typ                                                                                   |

| G = 500                                                                                                                                      | 10 µsec typ<br>50 µsec typ<br>90 µsec typ                                                     |

| Amplifier Bandwidth ( – 3 dB)                                                                                                                |                                                                                               |

| G = 10                                                                                                                                       | 3 mHz<br>2.5 mHz                                                                              |

| G = 1<br>G = 10<br>G = 100                                                                                                                   | 100 kHz                                                                                       |

| G = 500                                                                                                                                      | 20 kHz                                                                                        |

| S/H Acquisition Time to 0.01%                                                                                                                | 10 μsec max                                                                                   |

| S/H Aperture Jitler                                                                                                                          | 50 psec typ                                                                                   |

| S/H Feedthrough                                                                                                                              | 76 dB                                                                                         |

| Crosstalk (V <sub>IN</sub> = 20V p·p sine wave)                                                                                              | ~ 78 dB @40 kHz<br>- 90 dB @0.5 kHz                                                           |

|                                                                                                                                              | - 30 0D @ 0.5 N/12                                                                            |

| ACCURACY                                                                                                                                     |                                                                                               |

| Integral Linearity HS 9414C (0°C to +70°C) HS 9414B (0°C to +70°C) (fund to linearity)                                                       | + 1/2 I SB may                                                                                |

| HS 9414C (0°C to + 70°C)<br>HS 9414B (0°C to + 70°C)                                                                                         | ± 72 LSB max<br>+ 72 LSB max                                                                  |

|                                                                                                                                              | ± ½ LSB max<br>± ½ LSB max<br>± 1 LSB max                                                     |

| Differential Linearity HS 9414C (0°C to +70°C) HS 94148 (0°C to +70°C) (1 <sub>MN</sub> 10 1 <sub>MA</sub> x)                                |                                                                                               |

| HS 9414C (0°C to +70°C)                                                                                                                      | ± 1/4 LSB typ, ± 1 LSB max<br>± 1/4 LSB typ, ± 1 LSB max<br>± 1/4 LSB typ, ± 1 LSB max        |

| (tagini 10 taga v)                                                                                                                           | ± 1/4 LSB typ, ± 1 LSB max                                                                    |

| No Missing Codes                                                                                                                             |                                                                                               |

| 12-Bits<br>11-Bits                                                                                                                           | 0°C to 70°C<br>− 55°C to + 125°C                                                              |

|                                                                                                                                              |                                                                                               |

| Total Gain Error @G = 13  @other gains referred to G = 1                                                                                     | 0.1% typ, 0.3% max                                                                            |

| @other gains referred to G = 1<br>G = 10<br>G = 100                                                                                          | 0.02% typ, 0.1% max                                                                           |

| G = 100                                                                                                                                      | 0.02% typ, 0.1% max<br>0.03% typ, 0.1% max<br>0.05% typ                                       |

| G = 500                                                                                                                                      |                                                                                               |

| Bipolar Offset <sup>3</sup><br>t <sub>MIN</sub> to t <sub>MAX</sub>                                                                          | ± 1 LSB typ, ±3 LSB max<br>15 LSB max                                                         |

| 'MIN " 'MAX                                                                                                                                  | .o coo max                                                                                    |

| DRIFT                                                                                                                                        |                                                                                               |

| Integral Nonlinearity                                                                                                                        | ± 2 ppm/°C                                                                                    |

| Differential Nonlinearity                                                                                                                    | ± 2 ppm/°C                                                                                    |

| Unipolar Output Offset                                                                                                                       | ± 10 ppm/°C                                                                                   |

| Bipolar Output Offset                                                                                                                        | ± 10 ppm/°C                                                                                   |

| Gain Tempco G = 1                                                                                                                            | ± 25 ppm/°C                                                                                   |

| REFERENCE                                                                                                                                    |                                                                                               |

| Output Voltage                                                                                                                               | 10.00V nominal, ± 0.1V max                                                                    |

|                                                                                                                                              | ±30 ppm/°C typ. ±50 ppm/°C m                                                                  |

| 1empco                                                                                                                                       | ± 30 ppm C typ, ± 30 ppm C n                                                                  |

| MODEL                                   | HS 9414                                                            |

|-----------------------------------------|--------------------------------------------------------------------|

| POWER REQUIREMENTS                      |                                                                    |

| Power Supply Range                      | ± 15V. ± 5%                                                        |

| PSSR (All Supplies) %FSR/% Supply       | 0.002%/% typ, 0.005%/% max                                         |

| Current Drain<br>+ 15V<br>- 15V<br>+ 5V | 22 mA typ, 27 mA max<br>10 mA typ, 15 mA max<br>2 mA typ, 5 mA max |

| Power Dissipation                       | 490 mW typ, 655 mW max                                             |

| TEMPERATURE RANGE                       |                                                                    |

| Operating<br>9414C<br>9414B             | - 0°C to +70°C<br>-55°C to +125°C                                  |

| Storage                                 | − 65 °C to + 165 °C                                                |

#### NOTES:

- 1. Input range selected at factory.

HS 9414C-1 = 0 to + 10V or ±5V input

HS 9414C-2 = ±10V input

HS 9414B-1 = 0 to + 10V or ±5V input

HS 9414B-2 = ±10V input

- Assumes pipelining signal is applied to I.A., acquired by sample/hold and converted by A/D.

- 3. Externally adjustable to zero. See Applications Information.

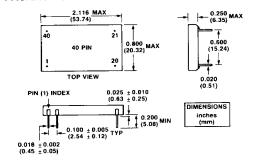

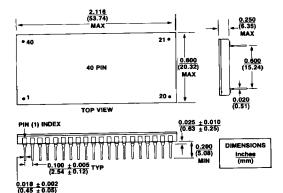

#### **PACKAGE OUTLINE**

# **PIN ASSIGNMENTS**

| PIN | FUNCTION                      | PIN | FUNCTION                 |

|-----|-------------------------------|-----|--------------------------|

| 1   | CH0 HI                        | 40  | LATCH                    |

| 2   | CH0 LO                        | 39  | MA0                      |

| 3   | CH1 HI                        | 38  | MA1                      |

| 4   | CH1 LO                        | 37  | GA0                      |

| 5   | CH2 HI                        | 36  | GA0                      |

| 6   | CH2 LO                        | 35  | V <sub>CC</sub> (+15V)   |

| 7   | СНЗ НІ                        | 34  | VEE ( - 15V)             |

| 8   | CH3 LO                        | 33  | Analog GND               |

| 9   | Input Offset Adjust –         | 32  | Digital GND              |

| 10  | Input Offset Adjust +         | 31  | V <sub>LOGIC</sub> (+5V) |

| 11  | Output Offset Adjust, Bipolar | 30  | 12/8                     |

| 12  | Ref Out (+ 10V)               | 29  | <u>cs</u>                |

| 13  | Ref In, Gain Adjust           | 28  | A <sub>0_</sub>          |

| 14  | Status                        | 27  | R/C                      |

| 15  | DB0 (LSB)                     | 26  | DB11 (MSB)               |

| 16  | DB1                           | 25  | DB10                     |

| 17  | DB2                           | 24  | DB9                      |

| 18  | DB3                           | 23  | DB8                      |

| 19  | DB4                           | 22  | DB7                      |

| 20  | DB5                           | 21  | DB6                      |

|     |                               |     |                          |

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to Digital Common                                                                     | 0 to + 16.5V                                     |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| VEE to Digital Common                                                                                 | 0 to - 16.5V                                     |

| V <sub>L</sub> OGIC to Digital Common                                                                 |                                                  |

| Analog Common to Digital Common                                                                       | ± 1V                                             |

| Control Inputs (CE, CS, A <sub>O</sub> , 12/8, R/C, LATCH, MAO, MA1, GAD, GA1) to Digital Common – 0. | .5V to V <sub>LOGIC</sub> + 0.5V                 |

| Analog Inputs (REF IN, BIP OFF, CH0-CH3) to<br>Analog Common                                          | ± 16.5V                                          |

| Input Offset Adjust Pins 9, 10                                                                        | V <sub>CC</sub> ± 1V                             |

| REF OUT to Analog or Digital GND to ±VDD                                                              | Indefinite short circuit<br>100 ms short circuit |

| Voltage on Digital Outputs in Tri-State Mode                                                          |                                                  |

| Lead Temperature, Soldering                                                                           | 300°C, 10 sec                                    |

# APPLICATIONS INFORMATION

# A/D CONTROL FUNCTIONS

The HS 9414 contains all control functions necessary to provide for complete microprocessor interface and also 'stand alone' operation including continuous conversions. All A/D control functions are defined in Table 1 and Table 2.

| FUNCTION       | DEFINITION    | FUNCTION                                                                                                                                                                                                                         |

|----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| €S             | Chip Select   | Typically the address pin when used with μP.     Must be low (0) for a conversion to start or read data at the output.     T⊥ transition may be used to initiate conversion.                                                     |

| R/C            | Read/Convert  | initiate conversion     initiate read                                                                                                                                                                                            |

| A <sub>a</sub> | Address       | Selects conversion mode. 12 Bits if low (0), 8 Bits if high (1).     In read mode A <sub>0</sub> selects the output format, if low (0) then 8 MSB's (high and middle byte) or if high (1) then only low byte and trailing zeros. |

| 12/8           | Output Format | 1. May be hard wired. 2. Normal 12-Bit format if high (1). 3. 8-Bit format as set by A <sub>O</sub> if low (0).                                                                                                                  |

Table 1. Defining A/D Control Functions

| CONTROL INPUTS |          | HS 9414 OPERATION |                |                                         |

|----------------|----------|-------------------|----------------|-----------------------------------------|

| CS             | R/C      | 12/8              | A <sub>O</sub> |                                         |

| 1              | ×        | х                 | Х              | No Operation                            |

| 0              | 7_       | Х                 | 0              | Initiates 12-Bit Conversion             |

| 0              | PL.      | Х                 | 1              | Initiates 8-Bit Conversion              |

| T.             | 0        | Х                 | 0              | Initiates 12-Bit Conversion             |

| 7.             | 0        | Х                 | 1              | Initiates 8-Bit Conversion              |

| 0              | <u>.</u> | Pin 31            | Х              | Enables 12-Bit Parallel<br>Output       |

| 0              | F        | Pin 32            | 0              | Enables 8 MSB's                         |

| 0              | <u>_</u> | Pin 32            | 1              | Enables 4 LSB's and<br>4 Trailing Zeros |

| 7.             | 1        | Pin 31            | Х              | Enables 12 Bit<br>Parallel Output       |

| J.             | 1        | Pin 32            | 0              | Enables 8 MSB's                         |

| J.             | 1        | Pin 32            | 1              | Enables 4 LSB's &<br>4 Trailing Zero's  |

NOTES 1 1 indicates logic HIGH.

2 0 indicates logic LOW

X indicates don I care.

4.

∫ indicates operation commences on low to high transition

5 MSB → XXXX XXXX XXXX → LSB

High Middle Low Byte Byte Byte 6 Not a common use of this function

Table 2. HS 9414 A/D Section Truth Table

# **SPGIA CONTROL FUNCTIONS**

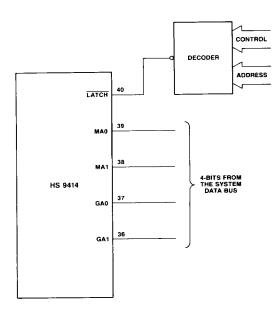

The HS 9414 has a 4-Bit transparent latch that selects input MUX channel as well as Gain. The SPGIA control functions are defined in Table 3.

| NAME     | DEFINITION          | FUNCTION                                                                                                    |

|----------|---------------------|-------------------------------------------------------------------------------------------------------------|

| LATCH    | MUX, Gain,<br>Clock | 1. Update input MUX & Gain 2. Hold input MUX & Gain 3. High (1) is hold mode 4. Low (0) is transparent mode |

| MA1, MA0 | MUX Address         | Select Input MUX Channel                                                                                    |

|          |                     | MAD MA1 CH                                                                                                  |

|          |                     |                                                                                                             |

|          | 1                   | 0 1 1                                                                                                       |

|          | i                   | 1 0 2                                                                                                       |

| Į.       | Į                   | 1 1 3                                                                                                       |

| GA1, GA0 | Gain Address        | Select Gain                                                                                                 |

|          |                     | GA1 GA0 Gain                                                                                                |

|          |                     | 0 0 0(x1)                                                                                                   |

| į.       | 1                   | 0 1 1(x10)                                                                                                  |

| l        |                     | 1 0 2(x100)                                                                                                 |

|          |                     | 1 1 3(x500)                                                                                                 |

Table 3. Defining the SPGIA Control Functions

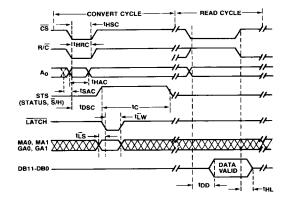

#### TIMING

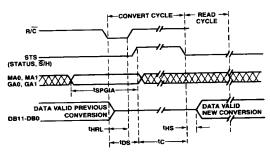

The timing diagrams are shown in Figure 1. Note that to start a conversion  $\overline{CS}$ , and  $R/\overline{C}$  must have an overlap time of 120 nS minimum.  $\overline{CS}$  and  $R/\overline{C}$  may be advanced or delayed if needed (by the application) but no specifications are given for this — only the coincidence of 120 nS must be met. Typically  $R/\overline{C}$  is used to initiate a conversion — however other lines may be used. See truth table (Table 2).

In the READ mode note the access time tpp is 125 nS typ, 150 nS max. This means that an entire conversion can be completed and read in 25.3  $\mu$ S typ, 30.35  $\mu$ S max including setup, conversion time and access time.

Figure 1a. HS 9414 Interface Timing

#### CONVERT CYCLE

| SYMBOL           | PARAMETER                                                                                     |                                              |

|------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------|

| t <sub>HSC</sub> | CS Pulse Width                                                                                | 120 nS min                                   |

| thec             | R/C LOW during CS LOW                                                                         | 120 nS min                                   |

| 1HAC             | Apvalid during CS LOW                                                                         | 120 nS min                                   |

| †SAC             | Maximum A <sub>O</sub> delay from CS<br>Set up as shown (negative<br>time wrt* CS) not needed | 60 nS max                                    |

| †DSC             | STS delay from CS                                                                             | 150 nS min                                   |

| tC               | Conversion time<br>8 Bit cycle<br>12 Bit cycle                                                | 15 μS typ, 25 μS max<br>25 μS typ, 30 μS max |

| t <sub>LS</sub>  | LATCH Setup Time                                                                              | 33 nS min                                    |

| tLW              | LATCH Pulse Width                                                                             | 33 nS min                                    |

|                  |                                                                                               | and the second second                        |

NOTE: No setup for  $\overline{\text{CS}}$ .  $R/\overline{\text{C}}$  or  $A_0$  is required. The only condition that must be satisfied is 120 nS coincidence, as shown.  $R/\overline{\text{C}}$ , or  $\overline{\text{CS}}$ , can be advanced or delayed as needed as long as this condition is met. Should  $A_0$  be delayed (t<sub>SAC</sub> 60 nS) then this must be added to  $\overline{\text{CS}}$  and  $R/\overline{\text{C}}$ . This condition not shown above.

# READ CYCLE

| ¹DD  | Access time from CS LOW | 125 nS typ, 150 nS max |

|------|-------------------------|------------------------|

| tui. | Output Float Delay      | 150 nS max             |

<sup>\*</sup>wrt = With Respect To.

Figure 1b. HS 9414 Interface Timing

# STAND-ALONE OPERATION

The HS 9414 can be used in a 'stand-alone' mode. Connections and timing for this mode are shown in Figure 2.

Figure 2a. Bipolar Stand-Alone Connections with Offset and Gain Adjustments

Figure 2b. Unipolar Stand-Alone Connections with Offset and Gain Adjustments

Figure 2c. No Trim Unipolar Connections

<sup>\*</sup>Trimpots can be 300Q for greater range adjustments.

Figure 2d. No Trim Bipolar Connections

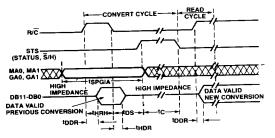

### R/C NEGATIVE PULSE

#### CONVERT CYCLE

| SYMBOL                                | PARAMETER                                                                                                                         |                       |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| ther.                                 | Low R/C Pulse Width                                                                                                               | 100 nS min            |

| tos                                   | STS Delay from R/C                                                                                                                | 200 nS ma:            |

| tC                                    | Conversion Time                                                                                                                   | 30 <sub>⊭</sub> S max |

| tus                                   | Data valid after STS low                                                                                                          | 70 nS max             |

| <sup>1</sup> HS<br><sup>1</sup> SPGIA | Software programmable gain<br>instrumentation ampilifier and S/H<br>settling time after input MUX, gain<br>or input signal change |                       |

#### READ CYCLE

1. Data always in read mode except during a conversion in which data lines revert to high impedance or when R/C goes low (0).

Output always valid after conversion is complete.

#### R/C POSITIVE PULSE

#### CONVERT CYCLE

| SYMBOL           | PARAMETER                                                                                                                        |            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|

| <sup>t</sup> HDR | Valid Data (Previous Conversion)<br>after R/C low                                                                                | 100 nS min |

| thrh             | High R/C Pulse Width                                                                                                             | 90 nS min  |

| t <sub>DS</sub>  | STS Delay from R/C                                                                                                               | 200 nS max |

| IDDR             | Data Access Time                                                                                                                 | 150 nS max |

| tC               | Conversion Time                                                                                                                  | 30 µS max  |

| tspgia           | Software programmable gain<br>instrumentation amplifier and S/H<br>settling time after input MUX, gain<br>or input signal change |            |

#### READ CYCLE

Converter output remains in high impedance state after conversion (STS goes low) until RIC goes high (to read data).

Figure 3. HS 9414 Stand-Alone Operation Top: Using Negative R/C Pulse Bottom: Using Positive R/C Pulse

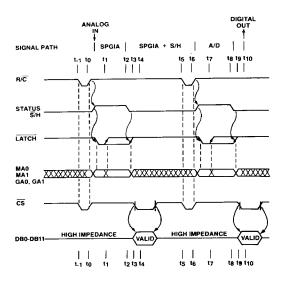

# INCREASING THROUGHPUT

To minimize added set-up delay, overlapping the multiplexer channels can significantly improve throughput. The technique involved is the same as normal operation; however, instead of waiting for the A/D to complete a conversion before selecting a new multiplexer channel, the new channel is selected at the start of the A/D conversion. By doing this, the A/D digitizes the analog voltage that is held in the sample and hold and the new multiplexer channel's voltage can start to settle through the multiplexer and intrumentation amplifier. An added 25 µS (A/D conversion time) can be saved from the front end settling time required by preselecting the new channel. After the A/D is finished converting, the sample and hold will switch back to sample to acquire the newly selected channel's voltage and the process repeated.

Figure 4. HS 9414 Pipeline Timing for Highest Throughput

- t\_1-to R/C pulse starts new conversion and sample and hold goes to hold mode.

- t<sub>0</sub>-t<sub>2</sub> New SPGIA gain, new input MUX channel and new input signal while the A/D is converting.

- t3-t6 Sample and hold samples the new input signal

- t3-t4 A/D data from the last signal is retrieved.

- t5-t6 RIC starts conversion of the new input signal.

- 16 Sample and hold holds the new signal

- t6-t7 Next SPGIA gain, next input MUX channel and next input signal

- ty-tg The new signal is converted.

- t<sub>10</sub> The new signal digital data is retrieved.

NOTE: Pipeline delay from t<sub>0</sub> to t<sub>10</sub>

Throughput is 1/t<sub>6</sub> to Hz

SPGIA settling time from t<sub>0</sub> to t<sub>6</sub>

S/H acquisition time from t<sub>2</sub> to t<sub>6</sub>

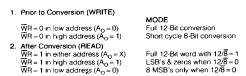

# USING THE AO LINE

The state of the  $A_O$  line at the start of a conversion places the HS 9414 in either a full 12-Bit conversion or in an 8-Bit 'short cycle' mode. During a READ at the end of a conversion the  $A_O$  line is used to format the data as follows:

| Prior to Conversion        | MODE                                                                              |

|----------------------------|-----------------------------------------------------------------------------------|

| $A_0 = 1$                  | Short cycle 8-Bit conversion                                                      |

| $A_{O} = 1$ $A_{O} = 0$    | Full 12-Bit conversion                                                            |

| 2. After Conversion (READ) |                                                                                   |

| A <sub>O</sub> = 1         | Data = Low Byte (LSB)                                                             |

| $A_{O} = 0$                | followed by zeros<br>Data = High Byte (MSB's)<br>followed by middle and low byte. |

In a  $\mu$ P application the A<sub>O</sub> line can be considered a pair of  $\overline{W}$ R locations as follows:

# INTERFACING THE HS 9414 WITH 8-BIT MICROPROCESSORS

The HS 9414 which has 12-Bit data can be used directly with popular 8-Bit microprocessors. The data however, must be multiplexed by setting the output mode select 12/8 pin to GND.

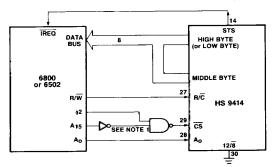

In the first case, a 6800 (or 6502) is used. See Figure 5.

NOTE 1. Decoding may be needed for a large system.

Figure 5. Interfacing the HS 9414 and a 6800 μP

The STATUS (STS) is tied directly to IREQ which is the interrupt line. When STS goes to 0 (at the end of a conversion) the 6800 may either service the interrupt or be timed for 30  $\mu$ S (since this IREQ is software maskable) the time required for a conversion.

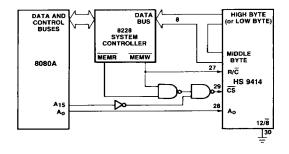

Figure 6 shows the 8080A  $\,\mu\text{P}$  as interfaced with the HS 9414. In this case, a 8228 controller is shown with gates to generate needed signals.

Figure 6. Interfacing the HS 9414 and 8080A  $_{\mu}P$

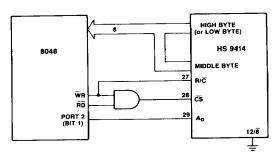

Figure 7 shows the HS 9414 connected with a 8048  $_{\mu}$ P. A single AND gate is used to generate  $\overline{\text{CS}}$ .

Figure 7. Interfacing the HS 9414 with a 8048 µP.

A summary of  $\mu P$  types and connections is in Table 4.

| MICRO-<br>PROCESSOR                               | HS 9414CONTROL INPUTS |                                 |                     |  |

|---------------------------------------------------|-----------------------|---------------------------------|---------------------|--|

|                                                   | R/C                   | CS                              | A <sub>Q</sub>      |  |

| 8080<br>MEMORY MAPPED<br>I/O<br>PROGRAMMED<br>I/O | (MEMR)                | DECODED<br>ADDRESS              | Ao                  |  |

| 6800                                              | R/W                   | DECODED<br>ADDRESS              | A <sub>o</sub>      |  |

| 6502                                              | R/W                   | DECODED<br>ADDRESS              | Ao                  |  |

| Z80<br>MEMORY MAPPED<br>I/O                       | (RD)                  | DECODED<br>ADDRESS<br>WITH MREQ | Ao                  |  |

| PROGRAMMED<br>I/O                                 | (RD)                  | DECODED<br>ADDRESS<br>WITH IOR  | Ao                  |  |

| 8048                                              | (RD)                  | PORT 2 <sub>0-3</sub> *         | PORT 2 <sub>0</sub> |  |

\*Port 2, Lines 0-3 can be used as a 4-Bit address bus. System address decoding requirements vary from no hardware to a fully latched 12-Bit address, depending on system complexity.

Table 4. Summary of HS 9414 Control Inputs with Various Microprocessors

# **ENABLING DATA IN 8-BIT OUTPUT MODE**

For an 8-bit system Figures 5, 6 and 7 show no direct connection of the low bytes. Hybrid Systems has provided internal multiplexing prior to the output tri-state drivers of the MSB's and LSB's. During the READ cycle when  $A_0 = 0$  the 8 MSB's are enabled and appear on pins 19-26. When  $A_0 = 1$  the LSB's are multiplexed onto pins 23-26, pins 20-23 to "0", and pins 15-18 float (High Z). The LSB's may be hardwired directly to the MSB's (23-26) with no loss in system performance but this will decrease the system versatility.

A recap of the output data in an 8-bit system is as follows:

#### CONDITIONS

- 1. 12/8 (pin 2) grounded or at "0"

- READ cycle.

|                      | 001901                  |                               |                   |  |

|----------------------|-------------------------|-------------------------------|-------------------|--|

| A <sub>O</sub> State | 23-26 (High)            | 19-22 (Middle)                | 15-18 (Low)       |  |

| 0                    | MSB Data<br>(Bits 1-4)  | Middle Bit Data<br>(Bits 5-8) | Float<br>(High Z) |  |

| 1                    | LSB Data<br>(Bits 9-12) | 0's                           | Float<br>(High Z) |  |

#### **USING THE LATCH LINE**

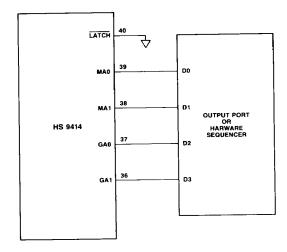

The LATCH line controls the internal 4-Bit transparent latch that holds the input MUX channel number (MAO, MA1) and the gain selection word (GAO, GA1). A low (0) on this line updates this latch and a high (1) holds the new word.

If the system where the HS 9414 is being used already has fully implemented output ports, then the LATCH line may be hardwired low so that an output port may control the timing of the input MUX and SPGIA gain directly. (See Figure 8).

Figure 8.

If the system does not have available output ports for the input MUX channel and gain selection, then 4-Bits from the system data bus can be directly tied to the MA0, MA1, GA0 and GA1 lines. Port address control decoding circuitry is connected to the LATCH line so that the 4-Bit data is grabbed from the system bus at the proper time. (See Figure 9).

Figure 9.

### OUTPUT OFFSET AND GAIN ADJUSTMENT AT GAIN = 1

The output offset and gain adjustments are used to calibrate the A/D section at a gain of one. The HS 9414 is normally used with external zero and gain calibration potentiometers. However, if maximum accuracy is not required, they may be omitted. If no trims are used, the gain of one calibration will be within approximately  $\pm 2$  LSB zero offset error, and  $\pm 12$  LSB maximum full scale error. See Figure 2c & 2d for connection with no trims. If gain and zero adjustment potentiometers are used, they should be connected as shown in Figure 2a & 2b. The zero control has a range of about  $\pm 20$  LSB, and the gain control has a range of about  $\pm 13$  LSB.

Proper gain and zero calibration requires great care and the use of extremely sensitive and accurate instruments. The voltage source used as a signal input must be very stable. It also should be capable of being set to within 1/10 LSB at both ends of its range.

The HS 9414's zero and gain adjustments are independent of each other if the zero (or offset) adjustment is made first.

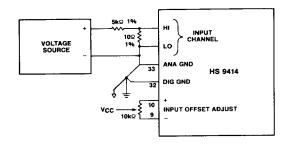

# SPGIA INPUT OFFSET ADJUSTMENT AT HIGH GAIN

The HS 9414 provides input offset adjustment to allow calibration of input offset errors to less than 5  $_{\mu}V$  ( < ½ LSB @G = 500) at high gains. The initial offset error before calibration is typically less than 50  $_{\mu}V$  or 250  $_{\mu}V$  maximum at G = 500. This input offset error may be adequate in some applications, and input offset adjustment may be omitted. See Figure 2 for the various adjustment options.

Proper use of the input and output offset adjustment pots results in an offset free system regardless of SPGIA gain setting or input channel. This can be achieved by calibrating the A/D section output offset and gain adjustments first and the input offset second. After the input offset is adjusted at G=500 the output offset at G=1 may need a minor adjustment.

#### A/D CALIBRATION

- 1. Center input offset pot if used.

- 2. Set SPGIA gain to one.

- Tie channel LO to analog ground (Pin 33) and apply the input voltage standard between HI and LO of that channel.

- Make sure that the voltage standard is grounded externally only at the input channel LO.

#### ZERO ADJUSTMENT PROCEDURE

- 1. For unipolar ranges:

- a) Set input voltage precisely to + 1/2 LSB.

- b) Adjust zero control until converter is switching from 0000000000000 to 000000000001.

- 2. For bipolar ranges:

- a) Set input voltage precisely to ½ LSB above - F.S.

- b) Adjust zero control until converter is switching from 000000000000 to 000000000001

#### GAIN ADJUSTMENT PROCEDURE

- Set input voltage precisely to ½ LSB less than "all bits on" ideal value. Note that this is 1½ LSB less than nominal full scale.

- 2. Adjust gain control until converter is switching from 111111111110 to 11111111111.

Table 5 summarizes the zero and gain adjustment procedure, and shows the proper input test voltages used in calibrating the HS 9414.

#### SPGIA OFFSET CALIBRATION PROCEDURE

- Calibrate the A/D section first.

- Set the SPGIA gain to 500.

- a) Apply ½ LSB to the input channel via a 500:1 attenuator as shown in Figure 10 or via the external front end circuitry. ½ LSB at gain of 500 is 4.8 μV for 20V range units (HS 9414X-2) and 2.4 μV for 10V range units (HS 9414X-1).

- b) Unipolar configuration:

Adjust input offset pot until converter is switching from 000000000000 to 000000000001

- Bipolar configuration:

Adjust input offset pot until converter is switcning from 100000000000 to 100000000001

|                  |      | ideal Input Voltage Value |           |                     |             | Adjust input to point where converter is just on the verge of switching between |  |

|------------------|------|---------------------------|-----------|---------------------|-------------|---------------------------------------------------------------------------------|--|

| Voltage<br>Range |      | GAIN = 1                  | GAIN = 10 | GAIN = 100          | GAIN = 500  | the two codes shown.1                                                           |  |

|                  | ZERO | 1.22mV                    | 0.122mV   | 12.2 <sub>µ</sub> V | 2.4µV       | 00000000000                                                                     |  |

| 0 to +10V        | GAIN | 9.9963V                   | 0.99963V  | 99.963mV            | 19.9926mV   | 111111111110                                                                    |  |

| ±5V              | ZERO | - 4.9988V                 | -0.49988V | - 49.988mV          | 9.9976mV    | 00000000000                                                                     |  |

|                  | GAIN | 4.9963V                   | 0.49963V  | 49.963mV            | - 9.9926mV  | 111111111110                                                                    |  |

|                  | ZERO | - 9.9976V                 | - 0.9976V | - 99.976mV          | – 19.9952mV | 00000000000                                                                     |  |

| ± 10V            | GAIN | 9.9927V                   | 0.99927V  | 99.927mV            | 19.99859mV  | 111111111110                                                                    |  |

NOTE 1. Codes shown are natural binary for unipolar input ranges and offset binary for bipolar ranges.

Table 5. Calibration Data

# **POWER SUPPLY CONSIDERATION**

Power supplies used for the HS 9414 should be selected for low noise operation. In particular they should be free of high frequency noise. Unstable output codes may result with noisy power sources. It is important to remember that 5  $\,\mu V$  is 1 LSB for a 10 volt range, at a gain of 500.

Decoupling capacitors are recommended on all power supply pins located as close to the converter as possible. Suitable decoupling capacitors are 10  $\mu$ F tantalum type in parallel with 0.1  $\mu$ F disc ceramic type.

# **GROUNDING CONSIDERATIONS**

To insure maximum accuracy, the HS 9414 has a separate analog and digital ground; these two grounds must be routed properly to prevent DC and transient errors.

DC errors can be caused by current flowing through a run resistance between the system ground reference

Figure 10. Suggested SPGIA Input Offset Calibration Circuit

and the DAS ground reference. (One mA through 2.52 will cause an LSB of error.) The best way to prevent this type of error is to connect the digital and analog grounds very close to the HS 9414 and use this point as the system ground. This can be done as a so-called "star ground" as shown in Figure 11. The single common ground reference insures no ground current or ground loop errors.

Figure 11.

### **ANALOG FRONT END**

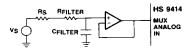

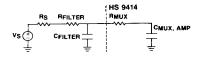

If the circuit is to be used at or near its maximum throughput rate, care must be used to prevent dynamic errors due to source impedance at the multiplexer inputs. If a low-pass anti-alias filter is used at the analog inputs (Figure 12a), it is suggested that a buffer be used (Figure 12b) to eliminate charge-transfer errors between CFILTER and CMUX.AMP (Figure 12c).

The term "O" is the transition between a logic 0 and a logic 1 state.

Figure 12a. (Not Recommended)

Figure 12b. (Recommended)

Figure 12c. (Equivalent Circuit of 12a)

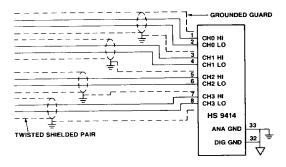

The HI and LOW inputs for each channel are adjacent to each other in the package. This simplifies layout of closely spaced HI and LO lines and eases connection of shielded and twisted pairs for each channel. (See Figure 13). These wiring consideration are particularly important at high SPGIA gain settings. The close proximity and similarity of the HI and LO conductors also reduces thermoelectric errors due to Seebeck effect.

Figure 13. Recommended Input Wiring Layout

#### DYNAMIC PERFORMANCE CONSIDERATIONS

The analog signal path in the HS 9414 has a characteristic settling time for each gain setting. If maximum accuracy is desired, enough settling time for each gain setting must be allowed. If not, each new conversion may have vestigial amounts of signal from the previous conversion. This phenomenon also manifests itself as poor crosstalk performance among successively converted channels or input signals.

Coherent noise coupling and input MUX crosstalk is more detrimental at certain time slots of the DAS pipeline (Figure 4) than others. System coherent noise spikes and adjacent channel dynamic swings will affect the signal that is being converted more severely if they happen in the last 1 to 10 µs before the status line goes high.

When switching the SPGIA to a higher gain it is important to make sure that the input MUX is not switched to the new low level signal later than the gain. Momentary saturation may occur while the signal presented to SPGIA is still high level and the new gain is high.

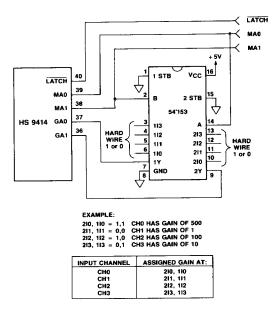

# FIXED GAIN ASSIGNMENT FOR EACH INPUT CHANNEL

The HS 9414 has four input channels and four independent gains. Any input channel can be software or hardware programmed for any gain in any sequence of DAS conversions. However, in some applications it suffices to preassign a fixed gain for each channel. This reduces the number of SPGIA control bits from four (MAO, MA1, GAO, GA1) to two (MAO, MA1). Figure 14 shows an implementation of this configuration using a dual 4-input multiplexer.

Figure 14. Input Channel Assigned Gain

# UNIPOLAR/BIPOLAR CONFIGURATION

The HS 9414-2 units are 20 volt range units which must be operated in bipolar configuration to give a  $\pm$  10V input signal range (for unity gain amplification). The HS 9414-1 units are 10 volt range units which can be operated in unipolar or bipolar modes. Refer to Figure 2 for various configurations.

# INPUT EXPANSION

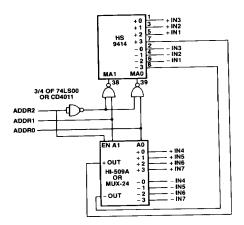

The DAS is configured with a 4-channel differential input. In the event the user wishes to increase the number of input channels, examples of input expansion are shown in Figure 15.

| ADDR2 | ADDR1 | ADDR0 | ACTIVE CHANNEL |

|-------|-------|-------|----------------|

| 0     | 0     | 0     | NONE           |

| 0     | 0     | 1     | ± IN1          |

| 0     | 1     | 0     | ± IN2          |

| 0     | 1     | 1     | ±IN3           |

| 1     | 0     | 0     | ±1N4           |

| 1     | 0     | 1     | ± IN5          |

| 1     | 1     | 0     | ±1N6           |

| 1     | 1     | 1     | ± IN7          |

Figure 15. Input Expansion for HS 9414 (From 4 to 7 Channels)

# ORDERING INFORMATION

| MODEL<br>NUMBER | INPUT<br>RANGE | TEMPERATURE<br>RANGE | SCREENING |

|-----------------|----------------|----------------------|-----------|

| HS 9414C-1      | 10V            | 0°C to +70°C         | -         |

| HS 9414C-2      | 20V            | 0°C to +70°C         | _         |

| HS 9414B-1      | 10V            | -55°C to +125°C      | 883C      |

| HS 9414B-2      | 20V            | - 55°C to + 125°C    | 883C      |