# PARADIGM

### 64K x 18 Fast CMOS Synchronous Static SRAM with Burst Counter

### **Features**

- ☐ Interfaces directly with the i486<sup>TM</sup>, Pentium<sup>TM</sup> processors (66.6, 60, 50, 40, 33.3 MHz)

- ☐ High Speed Access Times

Clock to data valid times:

9, 10, 12, 14, 18ns

- Cycle Times: 15, 16.6, 20. 25. 20 ns

- ☐ High Density 64Kx18 Architecture ☐ Choice of 5V or 3V ±10% Output Vcc for output level compatability

- ☐ High Output Drive: 85 pF at Rated Taa

- ☐ Asynchronous Output Enable

- ☐ Self Timed Write Cycle

- ☐ Byte Writeable via Dual Write Strobes

- ☐ Internal burst read/write address counter

- ☐ Internal write registers for Address, Data, Controls

- ☐ Packages: 52-pin PLCC

### **Description**

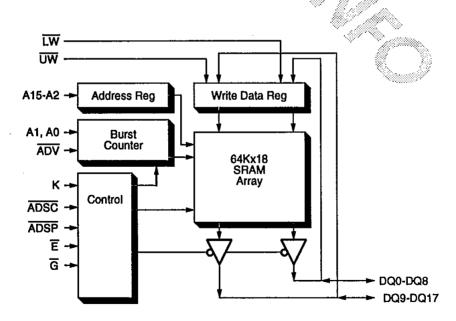

The PDM44018 is a 1,179,648 bit synchronous random access memory organized as 65,536 words by 18 bits. It has burst mode capability and interface controls designed to provide high performance in secondary cache designs for 486 and Pentium<sup>TM</sup> microprocessors. Addresses, write data and all control signals except output enable are controlled through positive edge triggered registers. cycles are self timed and are also initiated by the rising edge of the clock. Controls are provided to allow burst reads and writes of up to four words in length. A two-bit burst address counter controls the two least significant bits of the address during burst reads and writes. The burst address counter uses the 2-bit counting scheme required by the 486 and Pentium<sup>TM</sup> microprocessors. Individual write strobes provide byte write for the upper and lower 9-bit bytes of data. An asynchronous output enable simplifies interface to high speed buses. Separate output Vcc pins provide user controlled output levels of 5 or 3.3 volts, for 3.3 volt TTL compatibility.

# **Functional Block Diagram**

TM i486, Pentium are trademarks of Intel Corp.

# **Pin Assignment**

### **Pinout**

| Name VO Description |     | Description               | Name | 1/0 | Description                       |

|---------------------|-----|---------------------------|------|-----|-----------------------------------|

| Α                   | ı   | Address Inputs A15-A2     | ĽW   | T   | Low Byte Write Enable, DQ0-DQ8    |

| A1, A0              | ı   | Address Inputs A1 & A0    | υw   | 1   | Upper Byte Write Enable, DQ8-DQ17 |

| DQ0-DQ17            | I/O | Read/Write Data           | E    | 1   | Chip Enable                       |

| К                   | ı   | Clock                     | G    | 1   | Output Enable                     |

| ADV                 | ŀ   | Burst Counter Advance     | vcc  | -   | Power (+5)                        |

| ADSC                | ı   | Controller Address Status | vss  | _   | Ground                            |

| ADSP                | 1   | Processor Address Status  |      |     |                                   |

### **Asynchronous Truth Table**

| Operation  | Ğ | VO Status             |

|------------|---|-----------------------|

| Read       | L | Data Out              |

| Read       | Н | High-Z                |

| Write      | Х | High-Z: Write Data In |

| Deselected | × | High-Z                |

NOTE: 1. X means Don't Care.

2. For a write operation following a read operation, G must be high before the input data required setup time and held high through the input data hold time.

### **Burst Sequence Table**

| Sequence          | A15-A2 | <b>A</b> 1 | A0 |

|-------------------|--------|------------|----|

| Start Address     | AAAA   | В          | С  |

| 1st Burst Address | AAAA   | В          | C  |

| 2nd Burst Address | AAAA   | В          | С  |

| 3rd Burst Address | AAAA   | В          | С  |

### Synchronous Truth Table

| E | ADSP | ADSC | ADV | UW or LW | K | Address                            | Operation                   |  |

|---|------|------|-----|----------|---|------------------------------------|-----------------------------|--|

| Н | L.   | ×    | ×   | Х        | 1 | N/A                                | Deselected                  |  |

| Н | ×    | L    | ×   | X        | 1 | N/A                                | Deselected                  |  |

| L | L    | Х    | ×   | X        | 1 | External Read Cycle, Begin Burst   |                             |  |

| L | Н    | L    | X   | L        | 1 | External                           | Write Cycle, Begin Burst    |  |

| L | Н    | L    | ×   | Н        | 1 | External                           | Read Cycle, Begin Burst     |  |

| Х | Н    | Н    | L   | L.       | Ť | Next                               | Write Cycle, Continue Burst |  |

| X | Н    | Н    | L   | н        | Ť | Next                               | Read Cycle, Continue Burst  |  |

| X | Н    | Н    | Н   | L        | Ť | Current Write Cycle, Suspend Burst |                             |  |

| Х | Н    | Н    | Н   | н        | Ť | Current Read Cycle, Suspend Burst  |                             |  |

- NOTE: 1. X means Don't Care.

- 2. All inputs except G must meet setup and hold times relative low-to-high transition of clock, K.

- 3. Wait states are inserted by suspending burst.

### **Burst Mode Operation**

This is a synchronous part. All activities are initiated by the positive, low-to-high edge of the clock (K). This part can perform burst reads and writes with burst lengths of up to 4 words. The 4 word burst is created by using a burst counter to drive the two least significant bits of the internal RAM address. The burst counter is loaded at the start of the burst and is incremented for each word of the burst. The burst counter uses a modified binary sequence compatible with the cache line burst reload sequence of i486 microprocessors. This sequence is given in the Burst Sequence Table.

Burst transfers are initiated by the ADSC or ADSP signals. When the ADSP signal is sampled low, a read cycle is started (independent of W and ADSC), and prior burst activity is terminated. The address and the chip enable input (E) are sampled by the same edge that samples ADSP. Read data is valid at the output after the specified delay from the clock edge.

When ADSC is sampled low and ADSP is sampled high, a read or write cycle is started depending on the state of UW or LW. If UW and LW are both sampled high, a read cycle is started, as described above. If UW or LW is sampled low, a write cycle is begun. The address, write data, and the chip enable input (E) are sampled by the same edge that samples ADSC and UW or LW. The ADV line is held high for this clock edge to maintain the correct address for the internal write operation which will follow this second clock edge.

After the first cycle of the write burst, The state of UW and LW determines whether the next cycle is a read or write cycle, and ADV controls the advance of the address counter. The address counter is advanced by the ADV signal. This increments the address to the next available RAM address. You write the next word in the burst by taking ADV low and presenting the write data at the positive edge of the clock. If ADV is sampled low, the burst counter advances and the write data -- which is sampled by the same clock -- is written into the internal RAM during the time following the clock edge.

### **Absolute Maximum Ratings**

| Symbol            | Rating                               | Com'l.       | Mil.         | Unit |

|-------------------|--------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | V    |

| TA                | Operating Temperature                | 0 to +70     | -55 to +125  | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias               | -55 to +125  | -55 to +125  | *C   |

| T <sub>STG</sub>  | Storage Temperature                  | -55 to +125  | -65 to +135  | °C   |

| OUT               | DC Output Current                    | 50           | 50           | mA   |

NOTE: 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended DC Operating Conditions**

| Symbol          | Description         | Min. | Тур. | Max. | Unit |

|-----------------|---------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage      | 4.75 | 5.0  | 5.25 | V    |

| GND             | Supply Voltage      | 0    | 0    | 0    | v    |

| Military        | Ambient Temperature | -55  | 25   | 125  | °C   |

| Commercial      | Ambient Temperature | -0   | 25   | 70   | °C   |

# **DC Electrical Characteristics** ( $V_{CC} = 5.0V \pm 10\%$ , All Temperature Ranges)

| Symbol             | Description              | Test Conditions                                                   |                                       | Min.     | Max.     | Unit |  |

|--------------------|--------------------------|-------------------------------------------------------------------|---------------------------------------|----------|----------|------|--|

| IILI               | Input Leakage Current    | V <sub>CC</sub> = MAX., V <sub>IN</sub> = GND to V <sub>CC</sub>  |                                       |          | 10       | μА   |  |

| ll <sub>LO</sub> l | Output Leakage Current   | V <sub>CC</sub> = MAX., V <sub>OUT</sub> = GND to V <sub>CC</sub> |                                       | _        | 10       | μА   |  |

| V <sub>OL</sub>    | Output Low Voltage       | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8mA                     | · · · · · · · · · · · · · · · · · · · | 0.4      | -        | V    |  |

| V <sub>OH</sub>    | Output High Voltage      | V <sub>CC</sub> = Min., I <sub>OH</sub> = 12mA                    |                                       | 2.4      | _        | V    |  |

| lor                | Output Low Drive Current | V <sub>CC</sub> = Min., V <sub>OL</sub> = 2.0 Volts               |                                       | 50       | _        | mA   |  |

| R <sub>OUT</sub>   | Output Resistance        | ΔV <sub>OL</sub> /ΔI <sub>OL</sub> @ I <sub>OL</sub> = 8mA        | Mil<br>Com'l.                         | 21<br>24 | 38<br>35 | Ω    |  |

| V <sub>IH</sub>    | Input HIGH Voltage       |                                                                   |                                       | 2.2      | 6        | ٧    |  |

| V <sub>IL</sub>    | Input LOW Voltage        |                                                                   |                                       | -0.5     | 0.8      | ٧    |  |

NOTE: 1. Undershoots to -1.5 for 10 ns are allowed once per cycle.

# **Power Supply Characteristics**

| Symbol           | Description                                                     | Min.                                                                 | Max.          | Unit |          |          |

|------------------|-----------------------------------------------------------------|----------------------------------------------------------------------|---------------|------|----------|----------|

| l <sub>CC1</sub> | Active Supply Current:<br>Outputs Open                          | V <sub>CC</sub> = Max., F = 1/T <sub>CYC</sub> on Rclk & Wclk        | Mil<br>Com'l. |      | <br>360  | mA<br>mA |

| I <sub>SB1</sub> | Standby Current:<br>Inputs @ V <sub>CC</sub> - 0.2V             | V <sub>CC</sub> = Max., F = 1/T <sub>CYC</sub> , E = V <sub>IH</sub> | Mil<br>Com'l. | _    | <br>50   | mA<br>mA |

| I <sub>SB2</sub> | CMOS Standby Current:<br>Inputs <b>©</b> V <sub>CC</sub> - 0.2V | $V_{CC} = Max., F = 0, E = V_{CC} - 0.2V$                            | Mil<br>Com'l. | 1 1  | <u> </u> | mA<br>mA |

# Capacitance (T<sub>A</sub> = +25°C, f=1.0 Mhz)

| Symbol           | Parameter              | Conditions            | Max. | Unit |

|------------------|------------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance      | $V_{iN} = 0V$         | 5    | pF   |

| C <sub>OUT</sub> | Output Leakage Current | V <sub>OUT</sub> = 0V | 8    | ρF   |

NOTES: 1. Characterized values, not currently tested.

2. With output deselected.

#### 1 2 111 110 10

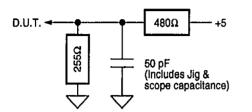

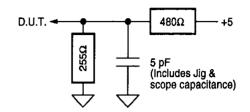

#### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input rise and fall times     | 3ns                 |

| Input timing reference levels | 1.5V                |

| Output reference levels       | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

Figure 1a. Output Load

Figure 1b. Output Disable Timing Load

# AC Electrical Characteristics ( $V_{CC}$ = 5V $\pm$ 10%, All Temperature Ranges)

| Parameter                               | Symbol           | -9  | -10  | -12 | -14 | -18 | Type | Units | Notes |

|-----------------------------------------|------------------|-----|------|-----|-----|-----|------|-------|-------|

| Clock Cycle time                        | t <sub>CYC</sub> | 15  | 16.6 | 20  | 25  | 30  | Min. | ns    |       |

| Clock to Data Valid                     | t <sub>CD</sub>  | 9   | 10   | 12  | 14  | 18  | Max. | ns    | 5     |

| Clock to Data Valid<br>(No Capacitance) |                  | 8   | 9    | 10  | 12  | 16  | Min. | ns    | 1     |

| Output Enable                           | toE              | 5   | 5    | 6   | 7   | 8   | Max. | ns    |       |

| Clock to Data Low-Z                     | t <sub>CLZ</sub> | 3   | 3    | 3   | 3   | 3   | Min. | ns    |       |

| Clock to Data Hold Time                 | t <sub>CH</sub>  | 3   | 3    | 3   | 3   | 3   | Min. | ns    |       |

| OE to Output Low Z <sup>(1)</sup>       | tolz             | 0   | 0    | 0   | 0   | 0   | Min. | ns    | 1     |

| OE to Output Hi Z <sup>(1)</sup>        | t <sub>OHZ</sub> | 5   | 5    | 6   | 7   | 8   | Max. | ns    | 1, 6  |

| Clock to Data High-Z                    | t <sub>CHZ</sub> | 6   | 6    | 7   | 8   | 9   | Max. | ns    | 1, 6  |

| Clock High/Low                          | tw               | 4   | 5    | 6   | 7   | 8   | Min. | ns    |       |

| Setup Time                              | ts               | 2.5 | 2.5  | 3   | 3   | 3   | Min. | ns    | 7     |

| Hold Time                               | t <sub>H</sub>   | 0.5 | 0.5  | 0.5 | 0.5 | 0.5 | Min. | ns    | 7     |

NOTES: 1. Values characterized and guaranteed by design, not currently tested.

- 2. A read cycle is defined by UW and LW high or ADSP low for the setup and hold times. A write cycle is defined by LW or UW low and ADSP high for the set up and hold times.

- 3. All read and write cycle timings are referenced from K or G.

- 4. G is a don't care when UW or LW is sampled low.

- 5. Maximum access times are guaranteed for all possible i486 external bus cycles.

- 6. Transition is measured ±500mV from steady-state voltage with load of Figure 1B. This parameter is sampled rather than 100% tested. At any given voltage and temperature, t<sub>CHZ</sub> max is less than t<sub>CLZ</sub> min for a given device and from device to device.

- 7. This is a synchronous device. All addresses must meet the specified setup and hold times for ALL rising edges of K whenever ADSP or ADSC is low, and the chip is enabled. Chip enable must be valid at each rising edge of clock for the device (when ADSP or ADSC is low) to remain enabled.

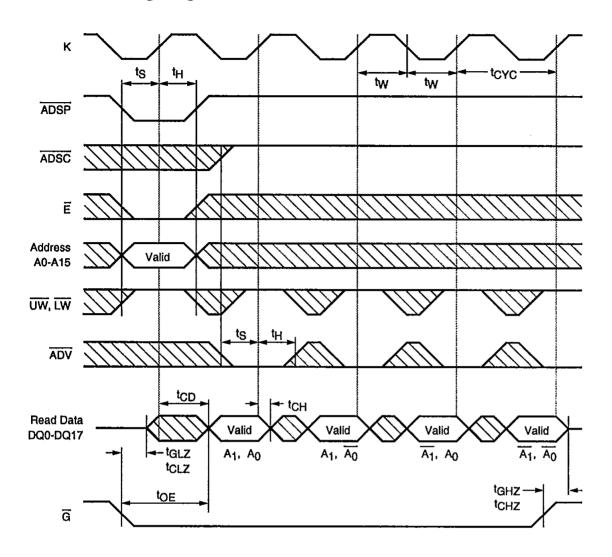

# **ADSP Read Timing Diagram**

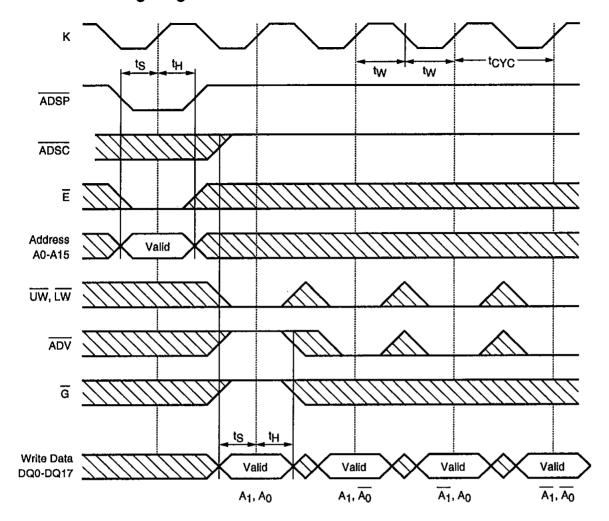

### **ADSP Write Timing Diagram**

NOTE: W is ignored for the first cycle when ADSP initiates the burst. ADSP active loads a new address into the address counter and forces the first cycle to be a read cycle.

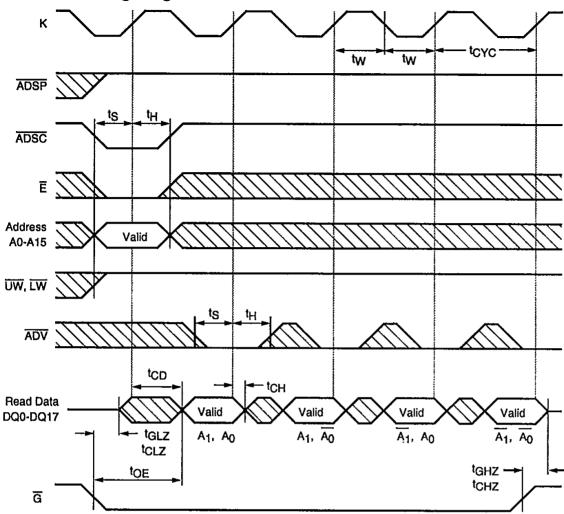

# **ADSC Read Timing Diagrams**

I Dillatoro

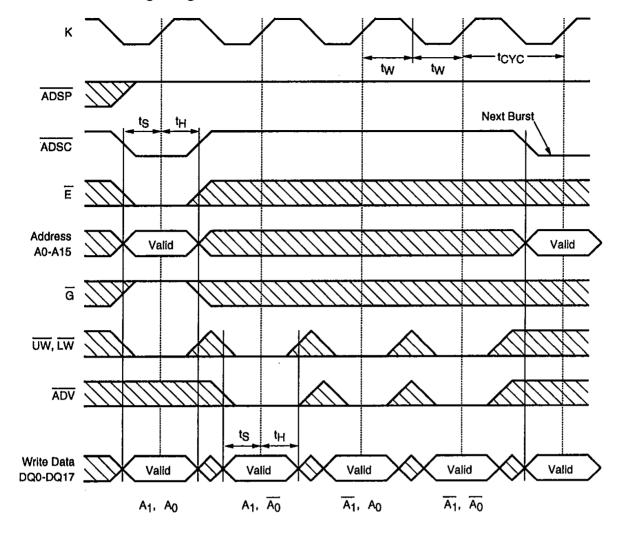

# **ADSC Write Timing Diagram**

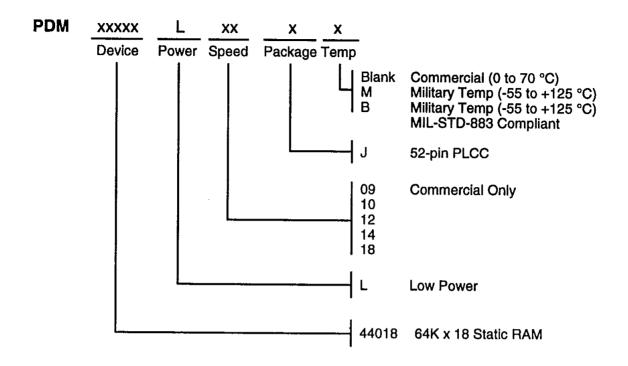

# **Ordering Information**