# IATC 2952 INTEGRATED LINE CARD CONTROLLER

- Provides Complete Backplane Interface for 8 to 16 Subscribers

- **■** Performs All Timeslot Assignments

- 2 Full-Duplex, Serial TDM Highways

- Serial, Bidirectional Packetized Highway for Signaling Control

- Standard MCS® μP Interface with Two Channel DMA and Interrupt

- Implements HDLC Protocol to Guarantee Integrity of All Signaling and Control Information

- Supports Four Control Options Local or Global Microprocessor Direct or Interleaved HDLC Control

- Designed for 24, 32, 48 or 64 Timeslot Systems

- Common Backplane Interface Supports ISDN Upgradability

The Intel iATC 2952 Line Card Controller (LCC) is a special purpose I/O controller optimized for use in all types of telecommunication switching systems. The 2952 is intended for use with up to sixteen subscriber devices in both analog and digital line circuits. It is also useful as a general purpose I/O controller for other applications.

The 2952 represents the continuation of a trend to intelligent flexible line cards. With its modular design, the 2952 provides a graceful upgrade path from analog line circuits to an all digital system. Analog line board density can be greatly increased using the LCC with the 29C51, 29C50A, or 29C48 Feature Control Combos. The 2952 handles the transfer of voice, data, feature control, and signaling information between the backplane and up to 8 29C51's, 16 29C50A's, or 16 29C48's. The 2952 will interface with and control all Intel SLD compatible slave devices. The 2952 emphasizes highly serial interfaces, thus reducing the number of digital interconnections both to the subscriber device and to the backplane.

Figure 1. Pin Configuration

270155-1

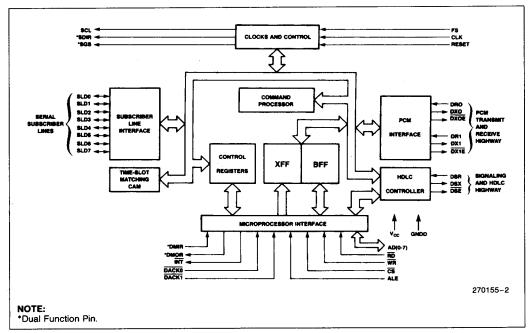

Figure 2. 2952 Block Diagram

**Table 1. Pin Description**

| Symbol    | Pin No.      | Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDD      | 20           | GROUND: 0V.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Vcc       | 31           | MOST POSITIVE SUPPLY: Input voltage is +5V ±5%.                                                                                                                                                                                                                                                                                                                                                                 |

| SLD0-7    | 37-40<br>1-4 | SUBSCRIBER DATA LINK: There are eight bidirectional pins that transfer serial information between the 2952 and the subscriber devices (e.g. 29C51).                                                                                                                                                                                                                                                             |

| SCL       | 12           | SUBSCRIBER CLOCK: This is a 512 KHz signal generated by the 2952 with 50% or 33% duty cycle clock. Can be connected up to 8 slave devices.                                                                                                                                                                                                                                                                      |

| SGS/DMIR  | 13           | SIGNALING STROBE: Can be used to strobe signaling bits or voice bytes for enabling external logic. In the DMA mode DMIR functions as DMA input request for HDLC.                                                                                                                                                                                                                                                |

| SDIR/DMOR | 14           | SUBSCRIBER DIRECTION: This is an 8 KHz signal generated by the 2952 to serve as both a direction indicator and a slave frame sync. When high, the SLD bus becomes an output and data is transferred from the 2952 to the slave. When low, the output buffer on the slave SLD pin is enabled and data is transferred from the slave to the 2952. In the DMA mode, DMOR functions as DMA output request for HDLC. |

Table 1. Pin Description (Continued)

| Symbol         | Pin No.  | Function                                                                                                                                                                                                                                                                                                          |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS             | 18       | CHIP SELECT: Enables $\overline{\text{RD}}$ or $\overline{\text{WR}}$ . A low level at this input allows the 2952 to accept commands or data from a microprocessor within a write cycle, or to transmit data during a read cycle. When no local $\mu\text{P}$ is connected, this pin should be connected to GNDD. |

| ALE            | 19       | ADDRESS LATCH ENABLE: (Active high input.) On falling edge of this input signal, data on AD(0-7) is latched into the selected register. When no local μP is connected, this pin should be connected to GNDD.                                                                                                      |

| RD             | 22       | <b>READ STROBE:</b> (Active low input.) When input is low, data is transferred from selected register on to $\mu$ P bus. When no local $\mu$ P is connected, this pin should be connected to GNDD.                                                                                                                |

| AD(0-7)        | 23-30    | ADDRESS/DATA PINS: Standard $\mu$ P bus used to transfer address and data between the $\mu$ P and internal registers of the 2952. When no local $\mu$ P is connected, the unique ID is hardwired on pins AD(0–7).                                                                                                 |

| WR             | 32       | <b>WRITE STROBE:</b> (Active low input.) When $\overline{WR}$ transitions from low to high, data on pins AD(0–7) are latched into the selected register. When no local $\mu P$ is connected, this pin should be connected to GNDD.                                                                                |

| DACKO<br>DACK1 | 33<br>34 | <b>DMA ACKNOWLEDGE:</b> DACKO is used to acknowledge the DMA output, and DACK1 is used for DMA input. When no local $\mu P$ is connected, these pins are used to hardwire mode information.                                                                                                                       |

| ĪNT            | 35       | INTERRUPT REQUEST: A standard μP interrupt, with active low output.                                                                                                                                                                                                                                               |

| DR1            | 5        | RECEIVE PCM HIGHWAY 1: Serial words are received on PCM highway 1 at this interface.                                                                                                                                                                                                                              |

| DR0            | 6        | RECEIVE PCM HIGHWAY 0: Serial words are received on PCM highway 0 at this interface.                                                                                                                                                                                                                              |

| DX1            | 7        | TRANSMIT PCM HIGHWAY 1: Serial words are transmitted onto PCM highway 1 at this interface.                                                                                                                                                                                                                        |

| DX1E           | 8        | TRANSMIT PCM HIGHWAY 1 ENABLE: Used to enable external tristate buffers to drive signals onto the PCM highway. The signal goes low while the 2952 is transmitting onto PCM highway 1.                                                                                                                             |

| DX0            | 9        | TRANSMIT PCM HIGHWAY 0: Serial words are transmitted onto PCM highway 0 at this interface.                                                                                                                                                                                                                        |

| DX0E           | 10       | TRANSMIT PCM HIGHWAY 0 ENABLE: Used to enable external tristate buffers to drive signals onto the PCM highway. The signal goes low while the 2952 is transmitting onto PCM highway 0.                                                                                                                             |

| DSX            | 15       | TRANSMIT SIGNALING HIGHWAY: Serial signaling and control data is transmitted on this dedicated HDLC highway.                                                                                                                                                                                                      |

| DSE            | 16       | <b>TRANSMIT SIGNALING HIGHWAY ENABLE:</b> Used to enable external tristate buffers to drive signals onto the transmit signaling highway. The signal goes low while the 2952 is transmitting an HDLC packet onto DSX.                                                                                              |

| DSR            | 17       | RECEIVE SIGNALING HIGHWAY: Serial signaling and control data is received on this dedicated HDLC highway.                                                                                                                                                                                                          |

| FS             | 11       | FRAME SYNCHRONIZATION: System sync pulse indicating beginning of a 125 μs frame.                                                                                                                                                                                                                                  |

|                |          |                                                                                                                                                                                                                                                                                                                   |

| Symbol | Pin No. | Function                                                                                                                                                                                                                                      |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK    | 21      | MASTER CLOCK: System input clock provides basic timing for the 2952 and is synchronous to the PCM clock. The clock rate determines the number of timeslots on the transmit and receive PCM highways, ranging from 24, 32, 48 or 64 per frame. |

| RESET  | 36      | RESET: (Active high input.) When high, 2952 internal circuitry is reset. Th                                                                                                                                                                   |

Table 1. Pin Description (Continued)

#### **FUNCTIONAL DESCRIPTION**

The 2952 is a highly integrated line card controller which concentrates and multiplexes all digital information that passes between a line card and the next switching or control level in a digital telecommunications system. It controls time switching functions between the individual subscriber line devices and the system backplane Time Division Multiplexed (TDM) highways. In addition, it manages the transfer of all signaling and control messages, either to an optional local microprocessor or to a central control processor. The 2952 implements all protocol control functions using the HDLC format for all information transmitted between the line card and the central processor.

#### **EXTERNAL INTERFACE**

The 2952 LCC supports interfaces for the subscriber line devices, an optional local microprocessor, and the backplane PCM and HDLC highways. Each is described briefly below.

#### Subscriber Line Interface

minimum reset pulse must be 16 complete CLK clock cycles wide.

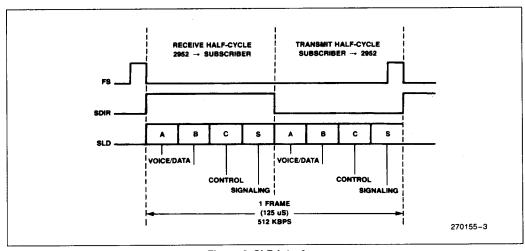

The LCC provides 8 serial, bidirectional ports for the digital transmission of voice, data, control, and signaling information to and from the subscriber. These leads, SLD0-SLD7, can be used to interface to both analog and digital line card subscribers (see Figure 3).

The Slave Clock SCL, is a fixed 512 KHz signal output used to transfer all signals between the subscriber device and the 2952. Data is received and transmitted upon the rising edge of SCL.

Data transmission direction is controlled by the Slave Direction clock, SDIR. This 8 KHz signal divides the frame transfer into transmit and receive halves referenced to the subscriber as shown in Figure 3. When SDIR is high, (RCV half-cycle), information is transmitted from the 2952 to the subscriber in four bytes consisting of voice, data, feature control, and signaling information. In the second half (XMIT-half cycle), the subscriber circuit sends four bytes of XMIT data back to the 2952.

Figure 3. SLD Interface

## **Backplane Interface**

The LCC supports dual TDM voice/data highways as well as a separate high speed serial highway for signaling and control information. This information is packetized and protected in HDLC format for transmission to a central processor.

The system clock (CLK) provides data rate transfers for both the TDM and HDLC links. The 2952 can operate in 24, 48, 32 or 64 timeslots systems. Any subscriber has access to any timeslot on either TDM highway. The 2952 allows the flexibility of programmable rising or falling edge latching of data onto the highways. Additionally, PCM highway delays can be compensated for by programming a phase shift in both transmit and receive timeslots as referenced to the frame synchronization pulse. The starting point of the bytes can be shifted up to 7 CLK clock cycles for both transmit and receive directions in half clock increments.

## Microprocessor Interface

The microprocessor interface provides a communication path for a local  $\mu P$  and the backplane and/or slave devices. The 2952 is designed to operate with standard Intel 8-bit parallel microprocessors, such as the MCS®-48, MCS®-51, MCS®-85, and iAPX-86 families. Interrupt capability, direct-memory-access request and acknowledge signals and a full feature multiplexed address data bus are incorporated into this interface.

Alternatively, the 2952 can operate in a stand alone mode on the line card in systems using a more centralized processing architecture. In this mode, the individual line board address and initialization information is hardwired onto the microprocessor interface pins.

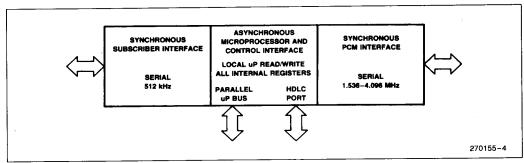

## 2952 BASE ARCHITECTURE

The 2952 can be partitioned into three functional blocks, according to the type of data transfers that each provides. The synchronous portion comprises the subscriber and PCM highway interfaces. Included in this section is also the Master Timing Unit, a CAM (Content Addressable Memory) for timeslot matching, a MODE register to configure the 2952 and for the determination of the type of HDLC data exchange, and the internal bus for a communication link between the various interfaces and registers. The PCM Interface Unit and the Subscriber Interface Unit with Last Look logic are also grouped into this segment. The Last Look logic monitors the status of signaling information received from each subscriber every frame. Any change of status is reported to the local µP or to the LCC bus control unit.

The asynchronous portion includes the local microprocessor interface and the serial HDLC signaling and control interface. The HDLC controller is compatible with ISO/CCITT recommendation X.25, and is designed for either point-to-multipoint configurations as a primary station, or in point-to-point as a secondary station. Each 2952 is accessed through an 8-bit address, allowing up to 255 secondaries to be addressed on one HDLC serial line. The logic level of the HDLC implementation and the distribution and compilation of the data packages are handled in a separate command unit contained in this portion.

The synchronous and asynchronous portions are linked to one another by a set of buffers and a control unit for the LCC internal bus. Two 16-byte by 8-bit FIFO's are used for intermediate storage of mesages. The XFF, or Transmit FIFO buffers data packages for transmission to the central processor through the HDLC interface. The type of data loaded is either from the Last Look logic or from the  $\mu P$  in package form with direct addressing to the 2952. The BFF, or bidirectional FIFO, is used for data exchange between the central controller (via the HDLC interface), the local microprocessor (via the  $\mu P$  bus), and the LCC (via the LCC bus).

## **MODES OF OPERATION**

The 2952 may operate in either a primary or secondary command mode within a single system. When instructed as a primary station, a local microprocessor must be used to instruct the 2952 and to generate control messages for other stations. This mode is used primarily by unit or group controllers to command secondary 2952's. When in the secondary mode, the 2952 executes received HDLC commands from the group controller. Additionally, a transparent command mode may be configured in which all HDLC messages received from the backplane are passed directly to the local microprocessor. This allows a secondary 2952 to execute user defined protocol and commands.

The 2952 can operate in one of two HDLC communication modes—dedicated HDLC or interleaved HDLC. In the dedicated configuration, HDLC messages are received on DSR and are transmitted on DSX. The interleaved mode reserves up to two timeslots per frame for transmission of signaling and control messages on the PCM highways. The HDLC packets are disassembled and interleaved into programmed timeslots on either of the two highways. Alternatively, the microprocessor can communicate directly to the central controller via a direct connection, bypassing the 2952 HDLC interface completely.

Figure 4. Architectural Diagram

## **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias 10°C to +8                         | 30°C |

|-----------------------------------------------------------|------|

| Storage Temperature65°C to +12                            | 25°C |

| All Input and Output Voltages with Respect to GNDD0.3V to | + 7V |

| Total Power Dissipation1                                  | .5W  |

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTICE: Specifications contained within the following tables are subject to change.

## D.C. CHARACTERISTICS

$T_A=0^{\circ}C$  to 70°C, V $_{CC}=+5V$   $\pm5\%,$  GNDD =0V Typical values are for  $T_A=25^{\circ}C$  and nominal power supply value

| Symbol          | Parameter                      | Min | Тур | Max  | Units | Test Conditions                |

|-----------------|--------------------------------|-----|-----|------|-------|--------------------------------|

| ارل             | Input Leakage Current          | -10 |     | +10  | μА    | $GND \leq V_{IN} \leq V_{CC}$  |

| loL             | Output Leakage Current         | -10 |     | +10  | μА    | $GND \leq V_{OUT} \leq V_{CC}$ |

| V <sub>IL</sub> | Input Low Voltage              |     |     | 0.8  | ٧     |                                |

| ViH             | Input High Voltage             | 2.0 |     |      | V     |                                |

| V <sub>OL</sub> | Output Low Voltage             |     |     | 0.45 | V     | $I_{OL} = +1.6 \text{ mA}$     |

| V <sub>OH</sub> | Output High Voltage            | 2.4 |     |      | ٧     | $I_{OH} = -400 \mu\text{A}$    |

| lcc             | V <sub>CC</sub> Supply Current |     | 85  | 120  | mA    | $V_{CC} = 5V$                  |

| P <sub>D1</sub> | Operating Power Dissipation    |     | 425 |      | mW    |                                |

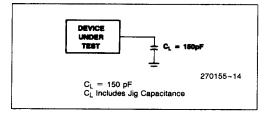

## CAPACITANCE TA = 25°C, VCC = GNDD = 0V

| Symbol           | Parameter                | Min | Тур | Max | Units | Test Conditions                  |

|------------------|--------------------------|-----|-----|-----|-------|----------------------------------|

| C <sub>IN</sub>  | Input Capacitance        |     | 5   | 10  | pF    | f <sub>C</sub> = 1 MHz           |

| CI/O             | Input/Output Capacitance |     | 10  | 20  | pF    |                                  |

| C <sub>OUT</sub> | Output Capacitance       |     | 8   | 15  | pF    | Unmeasured pins returned to GNDD |

# **A.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5V \pm 5\%$ , GNDD = 0V

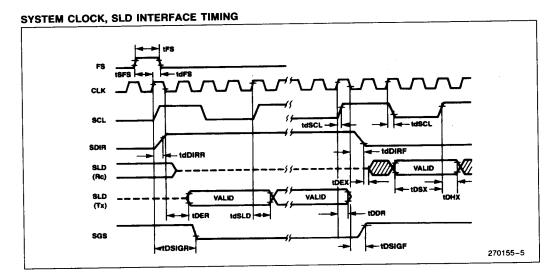

# SYSTEM CLOCK, SLD INTERFACE TIMING

| Symbol             | Parameter                                | Min                             | Max              | Units |  |

|--------------------|------------------------------------------|---------------------------------|------------------|-------|--|

| CLK                | System Backplane Clock Frequency         | 1                               |                  | MHz   |  |

|                    | CLK Duty Cycle                           | 45                              | 55               | %     |  |

|                    | CLK Rise, Fall Times                     |                                 | 10               | ns    |  |

| t <sub>SPP</sub>   | Frame Synchronization Pulse Period       | 125                             |                  | μs    |  |

| t <sub>FS</sub>    | Frame Synchronization Pulse Width        | 60                              | t <sub>CLK</sub> | ns    |  |

| t <sub>dFS</sub>   | Pulse Delay to CLK                       | 10                              |                  | ns    |  |

| t <sub>SFS</sub>   | Set-Up Time to CLK                       | 50                              |                  | ns    |  |

| SCL                | Slave Clock SCL Frequency                | 512                             | 512              | KHz   |  |

| tdSCL              | SCL Delay Time from CLK                  | 100                             | 165              | ns    |  |

| SDIR               | Slave Direction SDIR Frequency           | 8                               | 8                | KHz   |  |

| t <sub>dDIRR</sub> | SDIR Delay Time to CLK<br>(Rising Edge)  | 120                             | 190              | ns    |  |

| t <sub>dDIRF</sub> | SDIR Delay Time to CLK<br>(Falling Edge) | 30                              | 110              | ns    |  |

| tdSLD              | SLD Data Delay                           | 160                             | 300              | ns    |  |

| t <sub>DER</sub>   | Data Enable Receive                      | 100                             | 180              | ns    |  |

| t <sub>DDR</sub>   | Data Disable Receive                     | 100                             | 180              | ns    |  |

| t <sub>DEX</sub>   | Data Enable Transmit                     | 0                               |                  | ns    |  |

| t <sub>DHX</sub>   | Data Hold Transmit                       | 0                               |                  | ns    |  |

| t <sub>DSX</sub>   | Data Set-Up Transmit                     | $\frac{1}{2 \text{ CLK}} + 200$ |                  | ns    |  |

| <sup>t</sup> DSIGR | Signaling Strobe Delay<br>(Rising Edge)  | 110                             | 160              | ns    |  |

| t <sub>DSIGF</sub> | Signaling Strobe Delay<br>(Falling Edge) | 140                             | 220              | ns    |  |

# **A.C. CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC} = GNDD = 0V$

## MICROPROCESSOR INTERFACE

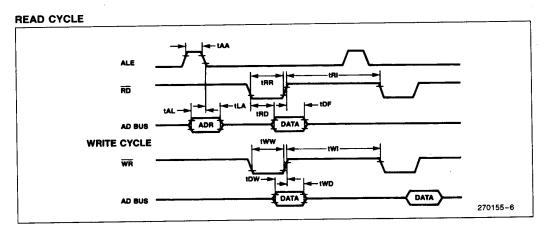

## **READ CYCLE**

| Symbol          | Parameter                          | Min                             | Max | Units |

|-----------------|------------------------------------|---------------------------------|-----|-------|

| t <sub>AL</sub> | Address Set-Up to ALE              | 30                              |     | ns    |

| t <sub>LA</sub> | Address Hold after ALE             | 20                              |     | ns    |

| t <sub>AA</sub> | ALE Pulse Width                    | 60                              |     | ns    |

| t <sub>RD</sub> | Data Delay from RD                 |                                 | 150 | ns    |

| tDF             | Data Float after RD                | 10                              | 50  | ns    |

| t <sub>RR</sub> | RD Pulse Width                     | 150                             |     | ns    |

| t <sub>RI</sub> | RD Control Interval <sup>(1)</sup> | $2 \times \frac{1}{\text{CLK}}$ |     | ns    |

| t <sub>RI</sub> | RD Control Interval(2)             | 100                             |     | ns    |

# WRITE CYCLE

| Symbol          | Parameter                          | Min                     | Max | Units |

|-----------------|------------------------------------|-------------------------|-----|-------|

| t <sub>DW</sub> | Data Set-Up to WR                  | 50                      |     | ns    |

| twp             | Data Hold after WR                 | 25                      |     | ns    |

| tww             | WR Pulse Width                     | 100                     |     | ns    |

| t <sub>WI</sub> | WR Control Interval <sup>(1)</sup> | $2 	imes \frac{1}{CLK}$ |     | ns    |

| t <sub>WI</sub> | WR Control Interval(2)             | 100                     |     | ns    |

## NOTES:

1. Read or Write of BFF and XFF.

2. Read or Write of all other registers.

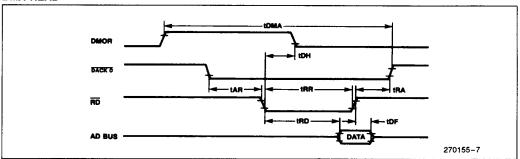

## **DMA READ**

| Symbol           | Parameter                | Min | Max                             | Units |

|------------------|--------------------------|-----|---------------------------------|-------|

| <sup>t</sup> DMA | DMA Read Time            |     | $7 \times \frac{1}{\text{CLK}}$ | ns    |

| t <sub>DH</sub>  | DMOR Hold Time           |     | 75                              | ns    |

| t <sub>AR</sub>  | Address Stable before RD | 0   |                                 | ns    |

| t <sub>RD</sub>  | Data Delay from RD       |     | 150                             | ns    |

| t <sub>DF</sub>  | Data Float after RD      | 10  | 50                              | ns    |

| t <sub>RA</sub>  | Address Hold after RD    | 0   |                                 | ns    |

| t <sub>RR</sub>  | RD Pulse Width           | 150 | 104                             | ns    |

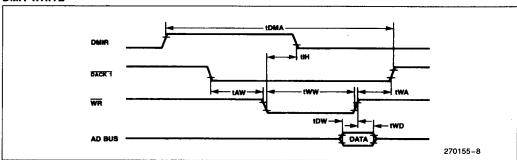

## **DMA WRITE**

| Symbol           | Parameter                | Min | Max                             | Units |

|------------------|--------------------------|-----|---------------------------------|-------|

| t <sub>DMA</sub> | DMA Write Time           |     | $7 \times \frac{1}{\text{CLK}}$ | ns    |

| tıH              | DMIR Hold Time           |     | 80                              | ns    |

| t <sub>AW</sub>  | Address Stable before WR | 0   |                                 | ns    |

| t <sub>WA</sub>  | Address Hold after WR    | 0   |                                 | ns    |

| t <sub>DW</sub>  | Data Set-Up to WR        | 30  |                                 | ns    |

| t <sub>WD</sub>  | Data Hold after WR       | 25  |                                 | ns    |

| tww              | WR Pulse Width           | 100 |                                 | ns    |

# **System Backplane Timing Parameters**

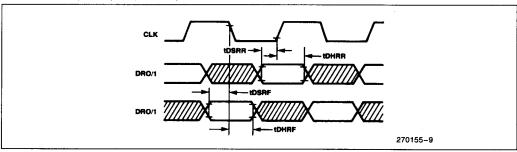

## PCM INTERFACE—RECEIVE TIMING

| Symbol            | Parameter                      | Min | Max | Units | Test Conditions            |

|-------------------|--------------------------------|-----|-----|-------|----------------------------|

| tDSRR             | Receive Data Set-Up DCR = 0(1) | 40  |     | ns    | 60 ns for Interleaved Mode |

| t <sub>DHRR</sub> | Receive Data Hold DCR = 0(1)   | 10  |     | ns    |                            |

| tDSRF             | Receive Data Set-Up DCR = 1(2) | 20  |     | ns    |                            |

| t <sub>DHRF</sub> | Receive Data Hold DCR = 1(2)   | 40  |     | ns    |                            |

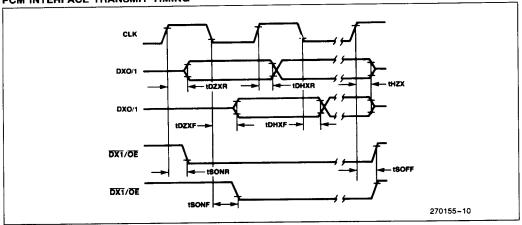

## PCM INTERFACE—TRANSMIT TIMING

| Symbol            | Parameter                    | Min | Max | Units | Test Conditions         |

|-------------------|------------------------------|-----|-----|-------|-------------------------|

| t <sub>DZXR</sub> | Data Enable DCX = 0          | 80  | 160 | ns    | C <sub>L</sub> = 200 pF |

| t <sub>DHXR</sub> | Data Hold Time DCX = 0       | 45  | 160 | ns    | C <sub>L</sub> = 200 pF |

| t <sub>DZXF</sub> | Data Enable DCX = 1          | 40  | 100 | ns    | C <sub>L</sub> = 200 pF |

| t <sub>DHXF</sub> | Data Hold Time DCX = 1       | 40  | 100 | ns    | C <sub>L</sub> = 200 pF |

| t <sub>HZX</sub>  | Data Float after CLK TS      | 35  | 80  | ns    | C <sub>L</sub> = 150 pF |

| tSONR             | Timeslot X to Enable DCX = 0 | 70  | 130 | ns    | C <sub>L</sub> = 150 pF |

| <sup>t</sup> SONF | Timeslot X to Enable DCX = 1 | 40  | 100 | ns    | C <sub>L</sub> = 150 pF |

| tsoff             | Timeslot X to Disable        | 40  | 100 | ns    | C <sub>L</sub> = 150 pF |

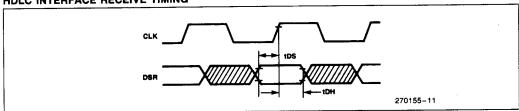

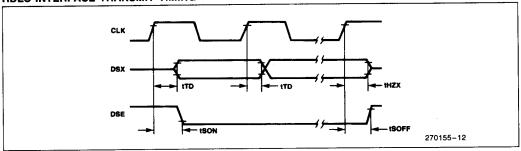

## HDLC INTERFACE TIMING

| Symbol           | Parameter             | Min | Max | Units | Test Conditions         |

|------------------|-----------------------|-----|-----|-------|-------------------------|

| t <sub>DS</sub>  | Receive Data Set Up   | 40  |     | ns    |                         |

| t <sub>DH</sub>  | Receive Data Hold     | 10  |     | ns    |                         |

| t <sub>TD</sub>  | Transmit Data Delay   | 40  | 100 | ns    | C <sub>L</sub> = 200 pF |

| t <sub>HZX</sub> | Data Float on TS Exit | 35  | 80  | ns    | C <sub>L</sub> = 200 pF |

| tson             | Timeslot X to Enable  | 40  | 95  | ns    | C <sub>L</sub> = 150 pF |

| tsoff            | Timeslot X to Enable  | 35  | 90  | ns    | $C_1 = 150  pF$         |

## NOTES:

1. DCR = 0 data latched on rising edge of CLK.

2. DCR = 1 data latched on falling edge of CLK.

# **WAVEFORMS**

# **Microprocessor Interface**

# **WAVEFORMS** (Continued)

# **DMA READ**

## **DMA WRITE**

## **PCM INTERFACE RECEIVE TIMING**

# **WAVEFORMS** (Continued)

# PCM INTERFACE TRANSMIT TIMING

## HDLC INTERFACE RECEIVE TIMING

# HDLC INTERFACE TRANSMIT TIMING

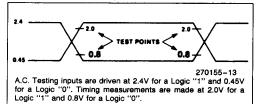

## A.C. TESTING INPUT, OUTPUT WAVEFORM

## A.C. TESTING LOAD CIRCUIT