# 1 DIGITAL Semiconductor 21340-AB Overview

The DIGITAL Semiconductor 21340-AB 10/100-Mb/s Buffered Port Switch (also called the 21340-AB) is an intelligent, multisegment, four-port buffered repeater building block. The 21340-AB can be used to build a variety of advanced Ethernet port switching architectures in both managed and nonmanaged configurations.

## **1.1 General Description**

The 21340-AB device is targeted for port switch applications, 10/100-Mb/s buffered repeater applications, and as a Fast Ethernet topology limitation solution.

When used in port switch applications, the 21340-AB device enables dynamic allocation of ports between four separate segments, supporting VLAN implementations. It offloads traffic from the forwarding switch engine by implementing an address filtering scheme between ports sharing the same segment. Intersegment packets are filtered out and are not presented to the switching engine.

The 21340-AB device enlarges the available bandwidth by enabling the filtering of fragment packets and preventing collisions from being propagated to other ports. The 21340-AB enables the use of a low-cost switch engine with a relatively small buffer size. In addition, it enables the setting of different priority schemes to different ports for bandwidth-hungry or time-bounded applications.

The 21340-AB allows a simple and low-cost migration path from a 10-Mb/s data rate network to a 100-Mb/s data rate network. Upgrading single or multiple end-stations from 10 Mb/s to 100 Mb/s does not require any hardware changes in a 21340-AB-based hub. The current hardware's value is maintained.

The 21340-AB allows the building of a Fast Ethernet network topology of unlimited length. Although the Fast Ethernet protocol scales the timing parameters along all network components, it creates some severe topological restrictions. Class II Fast Ethernet repeaters allow cascading of only two level of repeaters, reaching a maximum network length of 205 m. The 21340-AB-based port switch eliminates this network length restriction by transforming each of the connected ports into a distinct collision domain handled on the port switch side by a fully featured MAC with full-packet buffering capability.

1 October 1997

1

Conventions and Terminology

## **1.2 Conventions and Terminology**

This document uses the following subscript notation terminology:

| Subscript Notation | Description                                                                                                                                                                                                                    |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [i]                | Generic reference to one segment of the 21340-AB parallel bus. For example, <b>cntl[i]</b> refers to the control lines for one segment (out of 4) of the parallel bus.                                                         |  |

| { <b>j</b> }       | Generic reference to signals of a single 21340-AB port. For example, <b>gnt{j}</b> refers to the grant line of a 21340-AB port.                                                                                                |  |

| $\diamond$         | Numbers inside the angle brackets indicate specific bits of a register.<br>For example, <b>sts{j}&lt;5&gt;</b> is a generic reference to bit 5 in the STR register in any of the four 21340-AB ports. Bit 0 is always the LSB. |  |

### 1.3 Features

The 21340-AB has the following features:

- Offers four distinct standard MII/SYM interface ports, each connected to a separate collision domain.

- Supports CAT3 unshielded twisted-pair (UTP), CAT5 UTP, shielded twisted-pair (STP), or fiber cables. Multiple media types can be connected to a single 21340-AB simultaneously. With external PHY devices, each individual port can support multiple media connections.

- Contains Physical Coding Sublayer (PCS) functions per port to significantly reduce the cost of 100BASE-TX solutions.

- Offers unique inverse MII functionality<sup>1</sup> enabling direct connection to any MII PHY or MII MAC device without the need of a glue logic.

- Supports MII management functions.

- Supports 10-Mb/s or 100-Mb/s network ports.

- Receives and transmits at full wire speed.

- Implements partition, receive jabber, and carrier integrity isolation functions.

- Offers expansion ports that enable cascading up to 36 ports on one board.

- Supports up to 256 ports in a stackable configuration.

- Provides onchip round-robin and bursty round-robin with a priority arbitration scheme with no additional logic.

- Supports a wide range of external arbitration schemes.

- 2 DIGITAL Semiconductor 21340-AB Overview

Microarchitecture

- Provides dynamic allocation of ports to the four parallel bus segments supporting virtual LAN (VLAN) implementation.

- Supports half-duplex or full-duplex flow control between two 21340-AB ports.

- Provides filtering capability for one MAC address per port.

- Supports External Address Lookup Table logic unit.

- Ensures zero packet loss.

- Provides fragment packet filtering mode.

- Provides full RMON statistic group counters implementation.

- Provides full repeater MIB statistic counters implementation.

- Provides Ethernet-like MIB statistic counters implementation.

- Provides 21340-AB private MIB statistic counters implementation.

- Implements an interrupt pin for error notifications, isolation events, and statistic counter wrap-around notifications.

- Provides external and internal loopback capabilities.

- Supports JTAG boundary scan.

<sup>1</sup> DIGITAL Semiconductor patent pending.

#### **1.4 Microarchitecture**

The 21340-AB is an enhanced version of the 21340 device. It is fully backward-compatible to the 21340. To benefit from its advanced features and enhancements, connect the **emop** pin to **Vdd**. Connecting the **emop** pin to **Vss** will mask out all the 21340-AB features and the device will maintain the basic 21340 functionality.

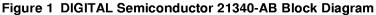

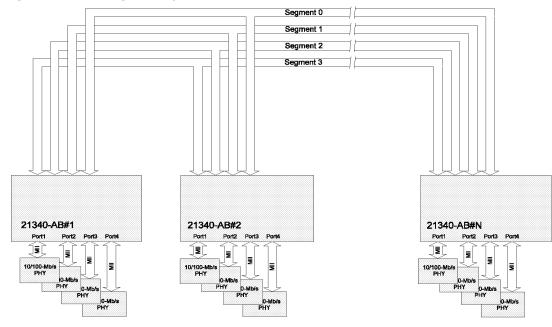

Figure 1 is a block diagram of the 21340-AB chip. The 21340-AB includes four independent ports. Each of the ports can be connected dynamically to any of the four segments of the 21340-AB parallel bus. Each segment of the parallel bus can be brought out as an expansion port to external devices such as additional 21340-AB units.

The 21340-AB contains four independent MAC-layer interfaces. These interfaces can connect directly to either an MII PHY device, an MII MAC device, or a SYM PHY device, allowing for 100BASE-TX cost optimization in the system solution.

1 October 1997

The MAC interfaces contain smart FIFO buffers that eliminate packet loss and enhance throughput. The buffer size (4KB receive FIFO and 2KB transmit FIFO) eliminates the need for additional onboard memory.

### 1.5 21340-AB Functional Description

This section describes the major functions of the 21340-AB and the data flow from one receiving port to all other transmitting ports.

### 1.5.1 Data Flow

A 21340-AB port can receive data packets when there is enough space in its receive FIFO (Rx\_FIFO). Each 21340-AB port uses various methods to ensure zero packet loss in case of Rx\_FIFO congestion. The method selected depends on the remote node's capabilities. When a 21340-AB port identifies its remote node as another 21340 node\*, the 21340 – 21340 credit-based flow-control (FCTL) method is

activated. When a 21340-AB port identifies its remote node as a non-21340 node\*, it uses a backpressure (BP) mechanism whenever the 21340-AB port's Rx\_FIFO is congested, holding off the remote node until the 21340-AB port is ready to receive a full packet.

\* This node can be either a 21340 or a 21340-AB remote node.

#### 1.5.1.1 Backpressure Mechanisms

The 21340-AB port uses two programmable backpressure mechanisms (BPM control bit in OPM $\{j\}$ ) to deliberately generate a carrier on the physical media to block the remote node's transmission. One mechanism causes the 21340-AB port to continuously send a special BP packet to the remote node. This makes the remote node suspend its attempt to transmit until the port is ready to receive a full packet. The other mechanism causes the 21340-AB port to collide with each carrier activity from the remote node by transmitting 96-bit JAM patterns. No additional packets are generated and spread throughout the network. In both mechanisms, other 21340-AB ports are not affected by the backpressure operation.

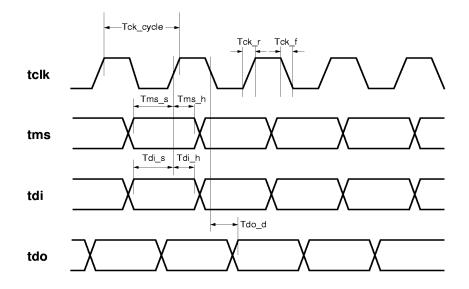

#### 1.5.1.2 Arbitration and Data Forwarding Functions

When a received packet starts loading into the Rx\_FIFO, the port asserts its request to ask the arbiter for permission to broadcast the packet on the parallel bus. The arbiter logic verifies that all target ports are ready to load the broadcast packet before granting the requesting port permission to broadcast.

The 21340-AB provides two internal onchip arbitration schemes that can be selected on a per-port basis:

- Round robin

- Bursty round robin

The internal onchip arbitration scheme, based on token passing, is expandable to support stackable configuration.

The 21340-AB can also support an external arbiter. The external arbiter uses the same 21340-AB pins as the internal arbitration scheme. See Sections 1.5.15 and 1.5.16 for a detailed description of the onchip internal and external arbitration schemes.

The granted port starts broadcasting the packet over the parallel bus segment [i]. First it drives a preamble octet, followed by a Start Frame Delimiter (SFD), on the **pdata[i]** lines while driving a *start frame* op-code on the **cntl[i]** lines. Next, the port transfers the received packet from its Rx\_FIFO to the **pdata[i]** lines while driving a

1 October 1997

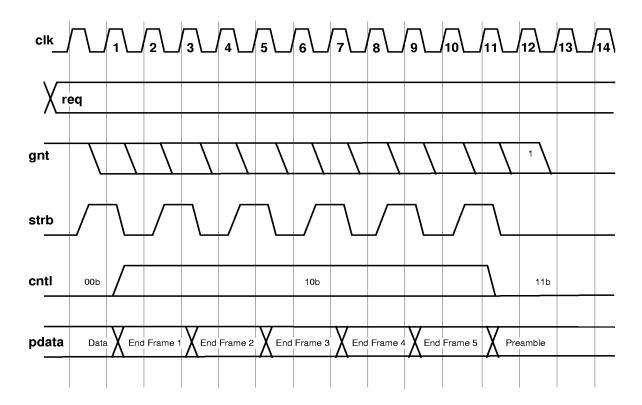

*data valid* op-code on **cntl[i]**. After the last data byte is transferred the granted port drives the chip\_id, port\_id, and received\_packet\_status bytes on **pdata[i]** while driving an *end frame* op-code on **cntl[i]**.

The broadcast packet is buffered in the target ports' transmit FIFOs (Tx\_FIFOs) while it is transmitted to the respective remote nodes through MII or SYM PHY devices, according to the IEEE 802.3 standard.

#### 1.5.2 Port Assignment to Segment and Data Rate Selection

Each 21340-AB port can be assigned dynamically to any of the four parallel bus segments. Each 21340-AB port can operate independently at either 10 Mb/s or 100 Mb/s, depending on the local PHY configuration. All ports allocated to the same parallel bus segment must be configured to the same data transfer rate.

Reassigning a port from one parallel bus segment to another, or changing the data rate, is software controlled. This can only be done when there is no packet being broadcast on the parallel bus and the arbiter is disabled.

### 1.5.3 Remote Node Flow-Control Autodetection Process

The purpose of the flow-control autodetection process is to check if the remote node is capable of running the 21340 credit-based flow-control scheme. The 21340-AB ports use the following two autodetection methods, based on the port's local and remote PHY device capabilities: Nway or Non-Nway.

#### 1.5.3.1 Nway-Supported Autodetection

If the local PHY is an MII PHY device, the management entity uses an Auto-Negotiation process to check the remote node capabilities.

If the remote node is not capable of running Auto-Negotiation, the management entity performs the non-Nway autodetection identification process as described in Section 1.5.3.2. If the remote node supports Auto-Negotiation and the flow-control operation, the management entity:

| e the 21340-AB port{j} to perform autodetection process. |

|----------------------------------------------------------|

|                                                          |

Based on the results of the Nway autodetection process, the port either:

| Asserts                              | То                                                                                                                                                                              |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCTL_on<br>in STR{j} register        | Notify the management entity that the link<br>supports credit-based flow control. The port<br>then operates according to the 21340<br>flow-control regime.                      |

|                                      | — or —                                                                                                                                                                          |

| FCTL_id_Failed<br>in STR{j} register | Notify the management entity that the link<br>does not support the 21340<br>flow-control regime. The link should be<br>initialized to work in half-duplex<br>21340-client mode. |

#### 1.5.3.2 Non-Nway FCTL Autodetection

If the local PHY device has a SYM interface, or if the remote node does not support Auto-Negotiation, the management entity:

| Sets                                          | То                                                                           |

|-----------------------------------------------|------------------------------------------------------------------------------|

| Enable_non_nway_link_id<br>in OPM{j} register | Configure the 21340-AB port{j} to perform the non-Nway autodetection process |

Based on the results of the non-Nway autodetection process, the port:

| Asserts            | То                                         |

|--------------------|--------------------------------------------|

| FCTL_on bit        | Notify the management entity that the link |

| in STR{j} register | supports credit-based flow control         |

The management entity, in turn, initializes the port to operate in the 21340 credit-based flow-control scheme.

If 21340 credit-based flow control has not been identified after a predefined period, the management entity initializes the port to operate in half-duplex 21340-client mode.

The user has the ability to manually set the link to a credit-based flow-control link, using the Force-FCTL control bit in the OPM{j} register. If the local and remote nodes do not use the same flow-control algorithm, the 21340-AB port's behavior will be UNPREDICTABLE and may lead to a system failure. See Section 1.7 for a description of the PHY hardware requirements needed to avoid false identifications.

1 October 1997

#### 1.5.4 Flow-Control Mechanism

Network performance enhancement is achieved by a unique credit-based flow-control (FCTL) mechanism optimized for the 21340-AB's Tx and Rx buffers. The mechanism is utilized whenever autodetection determines that a port's remote node is able to use the same FCTL mechanism.

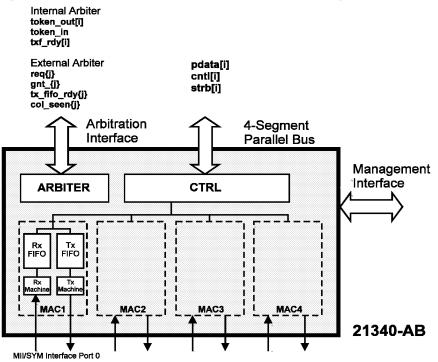

Each port supports credit-based FCTL in both directions. As a receiver, each port sends credits — the amount of free space that is available in its Rx\_FIFO — to its remote node. As a sender, each port traces the amount of free space in the remote node's Rx\_FIFO, using the credit value that has been transmitted by the remote node. The sender only transmits data packets to the remote node when it has enough credit. The received credit-based FCTL packets are filtered after the credit value is extracted from them.

Figure 2 illustrates the 21340-AB credit-based FCTL mechanism. In Figure 2, the 21340-AB#2 port is transmitting data to 21340-AB#1. The 21340-AB#1 port sends the amount of free space in its Rx\_FIFO (credit) to its remote node. The 21340-AB#2 port then decides, according to the credit value, whether or not it can send a packet.

#### Figure 2 Credit-Based FCTL Mechanism

#### 1.5.5 Address Filtering Scheme

To improve overall network performance, a 21340-AB port can filter out packets that are addressed to another port's remote node. The filtering level can be adjusted by the management entity.

When the internal address filtering mode is enabled, each 21340-AB port stores the last source address (SA) received from its remote node. This address is valid until the aging timer (T1) expires. The aging timer is set upon each packet reception.

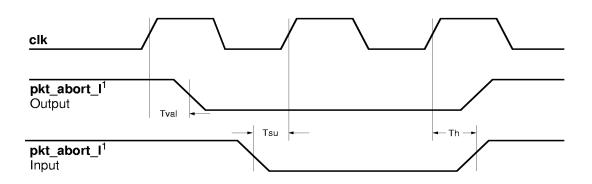

During T1, the valid bit (V\_bit) is set, and the port compares the broadcasted packet's destination address (DA) field with the stored address. If they match, the port asserts the **pkt\_abort\_l[i]** signal (active low), signaling other ports on the same parallel bus segment to filter out the packet.

On reception of a packet with a new SA, the port sets the T2 timer and the flood bit (F\_bit). Until T2 expires, the port transmits all broadcasted packets, unless the **pkt\_abort\_l[i]** signal was deasserted by another 21340-AB port. When T2 expires, and V\_bit is valid, the F\_bit is cleared and the port filters out all broadcasted packets with destination addresses (DAs) that do not match the stored address.

#### 1.5.5.1 Filtering Levels

The following three filtering levels can be applied using the F\_bit and V\_bit:

#### • Most aggressive level

When the 21340-AB port determines that only one remote node is connected to it; F\_bit is cleared and V\_bit is set. The port filters out all packets that are not destined to its remote node. The port notifies other ports to filter out packets destined to its remote node.

#### • Less aggressive level

When the port identifies at least one remote node, but is not certain about the existence of additional remote nodes; both the F\_bit and V\_bit are set. In this mode, the port filters out only packets that were identified as destined uniquely to one of the other ports. The port notifies other ports to filter out packets destined to its identified remote node. (The **pkt\_abort\_l[i]** signal was asserted for these packets.)

1 October 1997

9

#### • Least aggressive level

When no specific remote node has been identified by the port;  $F_bit$  is set and  $V_bit$  is cleared. In *flooding mode*, the 21340-AB port filters out only packets that are identified as uniquely destined to one of the other ports' remote nodes. This mode does not affect any other port's filtering operation.

Note: The state of having both F\_bit and V\_bit cleared is not allowed.

Multicast packets (addressed to a specific group of ports) are always transmitted to the remote node unless **pkt\_abort\_l[i]** assertion by an external device is detected. The **pkt\_abort\_l[i]** signal is shared among all ports connected to the same parallel bus segment [i].

The F\_BIT and C\_VBIT control bits in OPM{j} enable limiting the 21340-AB port address filtering level.

Table 1 summarizes the filtering levels available in a 21340-AB port.

| Aggression<br>Level | F_bit | V_bit | Filtering Operation                                                  | Notify Other Ports<br>(Asserts pkt_abort_I[i]) |

|---------------------|-------|-------|----------------------------------------------------------------------|------------------------------------------------|

| High                | 0     | 1     | Pass only packets destined to the remote node.                       | Yes                                            |

| Medium              | 1     | 1     | Filter out only packets for which <b>pkt_abort_l[i]</b> is asserted. | Yes                                            |

| Low                 | 1     | 0     | Filter out only packets for which <b>pkt_abort_l[i]</b> is asserted. | No                                             |

Table 1 Port Filtering Levels

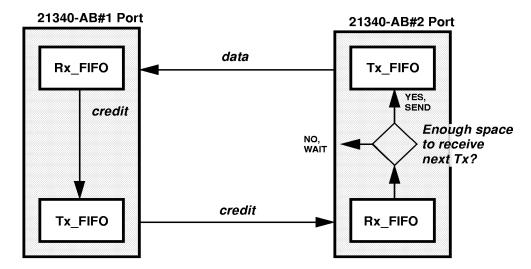

Figure 3 illustrates a network configuration in which one of the 21340-AB ports on a segment is connected to multiple nodes.

Figure 3 Internal Address Filtering with Multiple Nodes

Port0 and Port1 of device 21340-AB#1 are connected to single remote nodes, respectively. Port3 of device 21340-AB#1 is connected to multiple remote nodes.

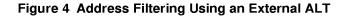

### 1.5.6 External Address Lookup Table

The 21340-AB allows the user to add an external Address Lookup Table (ALT) logic unit in order to further enhance system performance. When operating with an external ALT, the internal address filtering mechanism should be disabled (clear\_v\_bit control bit in the OPM{j} register is set), and the external ALT mode bit enabled (External\_ALT\_Enabled control bit in the MTC register is set).

In this mode, the ports' **pkt\_abort\_l{j}** signals are utilized as outputs from the ALT unit to all 21340-AB ports. The ALT decodes the destination address of the broadcast packet and compares it to the content of the address table it maintains. If a match occurs, the ALT asserts the **pkt\_abort\_l{j}** signal within the first loaded 16 bytes to ports that the broadcast packet is not addressed to.

1 October 1997

If the **pkt\_abort\_l{j}** signal assertion is detected after the first 16-byte time, the port ignores it and transmits the loaded packet.

Figure 4 shows a segment with an external ALT. The ALT recognizes the destination address and compares it to the remote nodes' addresses, which it maintains in its local lookup table. It then asserts the **pkt\_abort\_l{j}** signals of the ports that are not connected to the destination remote node.

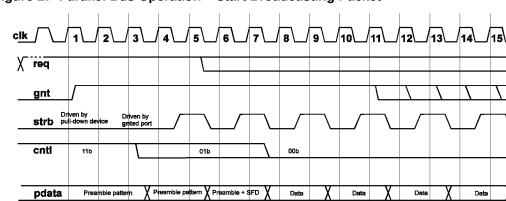

#### 1.5.7 MII Port Interface

Each of the 21340-AB ports implements a fully compliant IEEE 802.3u media-independent interface (MII), providing a direct connection to a PHY device located on the same board, or on a daughtercard, or to a cable (similar to an AUI connection).

In addition, each of the 21340-AB ports implements an inverse MII interface that enables a direct glueless connection to any 802.3u MII MAC device. When initialized to work in the inverse mode of operation, the 21340-AB device can be

used as a simple, low-cost, off-the-shelf component for directly connecting commercial MAC devices or switching cores to the 21340-AB parallel bus segments via a standard MII interface without requiring any glue logic or PHY device. See Figure 9.

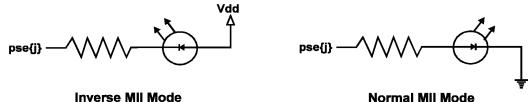

The 21340-AB port is set to the normal or inverse mode upon hardware reset, according to the configuration of the components connected to the **pse{j**} pins. When a resistor and an optional LED are connected between the pse{j} and Vdd, port{j} is initialized to work in the inverse MII mode of operation. When a register and an optional LED are connected between  $pse{j}$  and Vss, port{j} is initialized to work in the standard MII mode of operation.

A special internal circuit senses the polarity of **pse{j}** during hardware reset and adjusts the pse{j} LED driver accordingly. Figure 5 shows the pse{j} configurations for selecting normal and inverse MII modes.

#### Figure 5 pse{j} Normal and Inverse MII Mode

Normal MII Mode

While operating in the normal or Iinverse MII mode of operation, each of the 21340-AB ports can operate in either a 10-Mb/s or 100-Mb/s data transfer rate.

100-Mb/s Operation

The port's MII operates in nibble mode with a clock rate of 25 MHz.

10-Mb/s Operation

The port's MII operates in nibble mode with a clock rate of 2.5 MHz.

The port should be connected to a segment configured to operate at the same data transfer rate. Connecting a port to a segment operating in another data transfer rate may lead to UNPREDICTABLE behavior and data corruption.

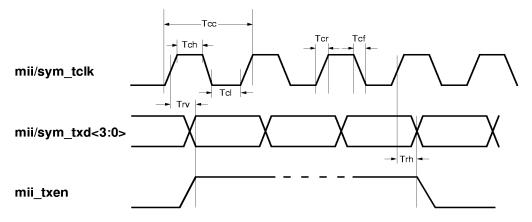

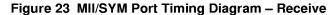

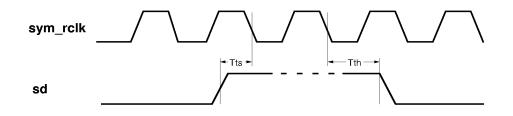

#### 1.5.8 100BASE-TX SYM Interface Mode of Operation

The 100BASE-TX SYM interface is an alternative to the standard MII interface between the MAC and the PHY device. It provides a lower-level interface and therefore enables the use of lower cost SYM PHY devices. The SYM interface

1 October 1997

provides a direct unframed 5-bit interface to the physical medium attachment (PMA) layer. Data is exchanged between the MAC and the PHY device at a 25-MHz clock rate. Since only one of the interfaces, SYM or MII, is active at a certain time, their pins are multiplexed.

The 100BASE-TX SYM interface is selected by setting the PCS control bit in JBR{j} register, and by setting the port to work at 100-Mb/s data transfer rate (setting the appropriate bits in MTC<31:28> register). The port should be connected to a segment operating at the same 100-Mb/s data transfer rate. Table 2 lists the mapping of the pins.

| MII Interface   | SYM Interface               |  |

|-----------------|-----------------------------|--|

| mii_cs_tclk     | sym_tclk                    |  |

| mii_cs_txen     | sym_txd<4>                  |  |

| mii_cs_txd<3:0> | sym_txd<3:0>                |  |

| mii_cs_rclk     | sym_rclk                    |  |

| mii_cs_rxd<3:0> | sym_rxd<3:0>                |  |

| mii_clsn        | sym_rxd<4>                  |  |

| mii_dv          | Status indicator LED        |  |

| mii_cs_errr     | Has no meaning in this mode |  |

| mii_crs         | sd                          |  |

Table 2 MII and SYM Interface Pin Mapping

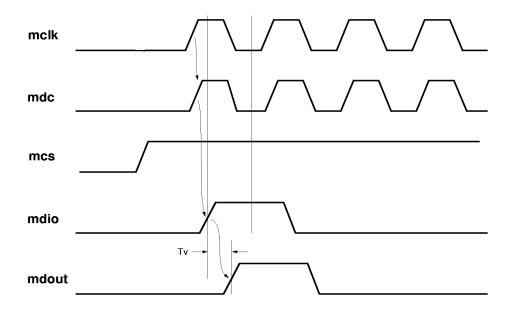

#### 1.5.9 Serial Management Interface

The serial management interface is used for control, status, and statistic registers access. It is also used for management access to an MII PHY device if one is connected to the port. The serial management interface is composed of the following four pins:

mclk

Used as a clock. All other management interface pins are synchronized to this pin. The **mclk** pin should be active during CSR access.

• mcs

A unique chip-select line for each 21340-AB in an application. It is used to choose which 21340-AB device is currently accessed.

#### • mdin

Data-in. The management entity drives the CSR's address and data on this pin.

• mdout Data-out. When reading a CSR, the 21340-AB drives the read data on this pin.

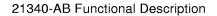

The mclk, mdin, and mdout signals can be shared by all 21340-AB devices. All 21340-AB devices in the system have these pins connected together in parallel, except the mcs signal. The mcs signal is unique for each 21340-AB device.

Figure 6 shows a typical configuration of the serial management interface signals.

#### Figure 6 Serial Management Interface Configuration

#### 1.5.9.1 Read and Write Operations

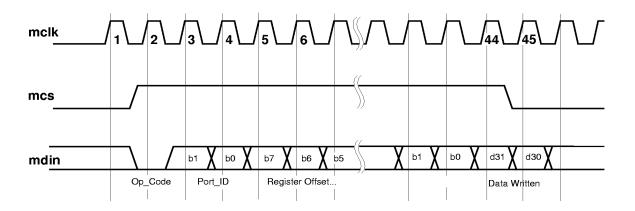

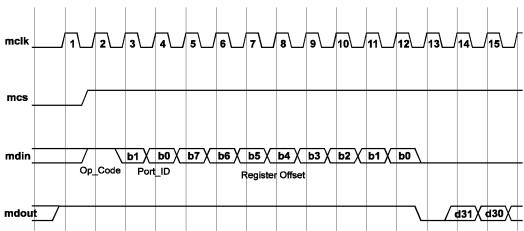

When the management entity wants to access a register in one of the 21340-AB devices, it activates **mclk**. After two clock cycles, the management entity asserts the **mcs** line and drives the following bits on **mdin**:

1 October 1997

**op\_code** — First bit driven. "0" indicates that the management entity is writing; "1" indicates that the management entity is reading.

**port\_id** — The number of the port that the accessed register is related to. Access to a register that is implemented only once in the 21340-AB should be done with port\_id set to 0.

Next, the management entity drives 8 bits of address, according to the accessed register's internal address, and then drives 32 bits of data. For a read operation, the management entity waits for a start bit 0 to be driven on the **mdout** line for one full **mclk** cycle. In the next cycle the 21340-AB will drive the data, read from the register, on **mdout**. For a write operation, the management entity drives 32 bits of data following the register offset field.

After the last bit is driven, the management deasserts **mcs** line and drives another two cycles of **mclk** before it may deactivate the clock. If the **mcs** line is deasserted in the middle of an access, the access is aborted. See Sections 3.5.3 to 3.5.5.

#### 1.5.9.2 MII PHY Device Access

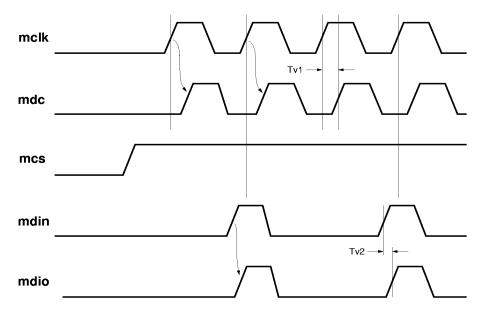

Management of the local PHY device is done through the **mdc** and **mdio** pins per port. The 21340-AB provides the management entity with two methods for accessing the MII PHY registers: an indirect access method and a direct access method.

The indirect access method of driving these pins is done through the MTC register. The management entity may access all four MII PHY devices connected to the same 21340-AB at the same time. The values of the appropriate bits of the MTC register are reflected over the MII management pins.

Table 3 describes the 4 bits per each MII PHY device in the MTC register.

| MTC Register  | Description                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------|

| Clock         | Directly connected to <b>mdc</b> pin.                                                         |

| I/O Direction | Determines <b>mdio</b> pin direction:<br>0 – output<br>1 – input                              |

| Data-In       | Samples <b>mdio</b> pin every <b>clk</b> cycle when <b>mdio</b> is set for input.             |

| Data-Out      | Drives data on the <b>mdio</b> pin every <b>clk</b> cycle when <b>mdio</b> is set for output. |

Table 3 MTC Register Functions

The direct access mode shortens the time required for accessing the MII PHY device registers. The **mdc** and **mdio** pins are connected directly to the **mclk**, **mdin**, and **mdout** pins. Setting this mode is done by setting the DAE control bit in the MTC register.

When direct access mode is enabled, the management entity performs the following tasks:

- Writes the DAD and DAP control bits in the MTC register with the direct access direction and the accessed port number

- Asserts the **mcs** pin while keeping the **mclk** pin at a 0 level for at least 40 ns

- Toggles the **mclk** pin and either drives data on **mdin**, or samples **mdout** according to the access direction

To complete accessing the MII PHY device registers, the management entity:

- Drives mclk to 0 for at least 60 ns

- Deasserts the **mcs** pin

- Holds mclk at 0 for at least 60 ns after deassertion of mcs

Deasserting the mcs pin will reset the DAE bit in the MTC register.

#### 1.5.10 Isolation Functions

The 21340-AB supports three defined repeater isolation functions of link unstable, partitioning, and receive jabber. When the 21340-AB port is in isolation, it ceases to receive and load packets. It resets the transmit path to flush the loaded packets and continues to monitor the line until the isolation is over. Each isolation function can be disabled by setting the appropriate control bits in the OPM{j}, JBR{j}, and CCC{j} registers.

Table 4 describes the 21340-AB isolation functions.

Table 4 21340-AB Isolation Functions

| Isolation Function | Description                                                                                                                                                                                                                                                                           |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link Unstable      | Occurs when the carrier-integrity-isolation is enabled and one of<br>the following conditions occur:<br>- Two consecutive false-carrier events<br>- A false-carrier event longer than 450–500 bit-times<br>- A link-failed event<br>- Hardware (HW) or software (SW) reset            |

|                    | The port does not receive or transmit any packets during the isolation. The isolation is over when the link is stable and the 21340-AB port detects either no activity of 33,000 bit-times or a valid carrier of at least 450 bit-times, preceded by an idle time of 64–84 bit-times. |

| Partitioning       | Occurs when the port attempts to transmit and the number of consecutive collisions, without any successful activity in between, exceeds the predefined limit. The isolation is over on a successful transmission or reception of more than 64 bytes.                                  |

| Receive Jabber     | Defined as a too long receive carrier (more than 40,960–45,056 bit-times). During isolation the port does not receive or transmit any packets. The isolation is over after the carrier drops.                                                                                         |

### 1.5.11 Management Support

The 21340-AB device presents network statistics, error and abnormal events directly, by using the 21340-AB onchip event flags and statistic counters, and indirectly, by appending the received packet's status information to the packet broadcasted on the parallel bus segment.

Each 21340-AB port has its own set of snapshot and event flags: flags that provide a snapshot of the 21340-AB current operation state and flags that provide an indication that an event has occurred.

| Flags                   | Description                                                                                                                                |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | Snapshot Flags                                                                                                                             |  |  |

| Auto partitioning       | Indicates whether a port is currently partitioned.                                                                                         |  |  |

| Jabber                  | Indicates whether a port is in jabber state.                                                                                               |  |  |

| Link unstable           | Indicates whether a port is in link unstable isolation state.                                                                              |  |  |

| Backpressure            | Indicates whether a port is in backpressure state.                                                                                         |  |  |

| Administration          | Indicates whether a port is in a stopped state.                                                                                            |  |  |

| Flow control            | Indicates whether a credit-based flow-control link has been identified.                                                                    |  |  |

| Scrambler lock          | Indicates that the descrambler is locked to the input data signal while the port is configured to work in SYM interface mode.              |  |  |

| Link failed             | Indicates that a link failed event is detected.                                                                                            |  |  |

| No grant                | Indicates that a grant was not issued to the port at least 0.33 seconds after the port's request for parallel bus segment ownership.       |  |  |

|                         | Event Flags                                                                                                                                |  |  |

| Auto partitioning       | Indicates that a port has been partitioned.                                                                                                |  |  |

| Jabber isolation        | Indicates that a port has been in jabber state.                                                                                            |  |  |

| Link unstable isolation | Indicates that a port has been in link unstable isolation.                                                                                 |  |  |

| Late collision          | Indicates that a transmit late collision event has been detected.<br>Late collision causes a packet abort (no retransmission<br>attempts). |  |  |

| Short carrier           | Indicates that a short carrier event has been detected.                                                                                    |  |  |

| Transmit underflow      | Indicates that an error in 21340-AB transmit operation has occurred. The Tx_FIFO has been emptied during transmission.                     |  |  |

| Receive underflow       | Indicates that an internal error has occurred in the 21340-AB port's receive operation. The Rx_FIFO has been full.                         |  |  |

| Link failed flag        | Indicates that a link-failed event has been detected.                                                                                      |  |  |

Table 5 lists the 21340-AB port snapshot and event flags with their functions.

Each port implements a complete set of the RMON Ethernet statistic group MIB, Repeater statistic MIB, and Ethernet-like MIB.

Table 6 lists the 21340-AB port statistic counters and their function.

| Register Description                | Mnemonic       |  |  |

|-------------------------------------|----------------|--|--|

| Statistic Counters <sup>1</sup>     |                |  |  |

| Overflow counter                    | ROVF[i]        |  |  |

| Total octet counter low             | ROCTL[i]       |  |  |

| Total octet counter high            | ROCTH[i]       |  |  |

| Broadcast packet counter            | RBCT[i]        |  |  |

| Multicast packet counter            | RMCT[i]        |  |  |

| Undersized packet counter           | RUSZ[i]        |  |  |

| Oversized packet counter            | ROSZ[i]        |  |  |

| Fragment counter                    | RFRG[i]        |  |  |

| Too long packets with CRC errors    | RJBR[i]        |  |  |

| Collision counter                   | RCOL[i]        |  |  |

| 64 octets packet counter            | R64[i]         |  |  |

| 65 – 127 octets packet counter      | R65TO127[i]    |  |  |

| 128 – 255 octets packet counter     | R128TO255[i]   |  |  |

| 256 – 511 octets packet counter     | R256TO511[i]   |  |  |

| 512 – 1023 octets packet counter    | R512TO1023[i]  |  |  |

| 1024 – 1518 octets packet counter   | R1024TO1518[i] |  |  |

| Alignment error packet counter      | MALI[i]        |  |  |

| CRC error packet counter            | MCRC[i]        |  |  |

| Single collision counter            | MSCOL[i]       |  |  |

| Multicollision counter              | MMCOL[i]       |  |  |

| Deferred transmission counter       | MDEF[i]        |  |  |

| Late collision counter              | MLCOL[i]       |  |  |

| Partition isolation counter         | MPAR[i]        |  |  |

| Carrier integrity isolation counter | MISO[i]        |  |  |

20 DIGITAL Semiconductor 21340-AB Overview

#### Table 6 21340-AB Statistic Counters (Sheet 2 of 2) **Register Description** Mnemonic Symbol error counter MSYE[i] Source address changed counter MSAC[i] Last source address low UAR1[i] Last source address high UAR2[i] MSHE[i] Short event counter Good octets counter low MOCTL[i] Good octets counter high MOCTH[i] Receive jabber counter MVLE[i] Control packet counter MCPKT[i] Total transmitted octets - low MTOCTL[i] Total transmitted octets - high MTOCTH[i] Total transmitted packets MTPKT[i] Total transmitted control packets MTCPKT[i] Total filtered packets in transmit MTFTR[i]

#### 21340-AB Functional Description

<sup>1</sup> Each statistic register has two addresses:

• Read-only address. Reading the register address does not affect the register's content.

• Clear-by-read address. Reading the register address clears the register's content.

Table 7 summarizes the 21340-AB counters, grouped according to function.

| Name                           | 21340-AB Registers                                                                                  |

|--------------------------------|-----------------------------------------------------------------------------------------------------|

| R                              | MON MIB Counters                                                                                    |

| etherStatsDropEvents           | ROVF                                                                                                |

| etherStatsOctets               | $ROCTH \times 100000000h + ROCTL$                                                                   |

| etherStatsPkts                 | RUSZ + RFGR + R64 + R65TO127 + R128TO255<br>+ R256TO511 + R512TO1023 + R1024TO1518 +<br>RJBR + ROSZ |

| etherStatsBroadcastPkts        | RBCT                                                                                                |

| etherStatsMulticastPkt         | RMCT                                                                                                |

| etherStatsCRCAlignErrors       | MALI + MCRC                                                                                         |

| etherStatsUndersizePkts        | RUSZ                                                                                                |

| etherStatsOversizePkts         | ROSZ                                                                                                |

| etherStatsFragments            | RFRG                                                                                                |

| etherStatsJabbers              | RJBR                                                                                                |

| etherStatsCollisions           | RCOL + MLCOL                                                                                        |

| etherStatsPkts64Octets         | R64                                                                                                 |

| etherStatsPkts65to127Octets    | R65TO127                                                                                            |

| etherStatsPkts128to255Octets   | R128TO255                                                                                           |

| etherStatsPkts256to511Octets   | R256TO511                                                                                           |

| etherStatsPkts512to1023Octets  | R512TO1023                                                                                          |

| etherStatsPkts1024to1518Octets | R1024TO1518                                                                                         |

| Repeate                        | r MIB Counters (RFC1516)                                                                            |

| rptrMonitorPortReadableFrames  | R64 + R65TO127 + R128TO255 + R256TO511 +<br>R512TO1023 + R1024TO1518 - MALI - MCRC                  |

| rptrMonitorPortReadableOctets  | $MOCTH \times 10000000h + MOCTL$                                                                    |

| rptrMonitorPortFCSErrors       | MCRC                                                                                                |

| rptrMonitorPortAlignmentErrors | MALI                                                                                                |

| rptrMonitorPortFrameTooLongs   | MJBR + MOSZ                                                                                         |

| rptrMonitorPortShortEvents     | MSHE                                                                                                |

| <b>Fable 7 21340-AB Counters Summary</b> (Sheet 2 of 4) |                                                    |

|---------------------------------------------------------|----------------------------------------------------|

| Name                                                    | 21340-AB Registers                                 |

| rptrMonitorPortRunts                                    | MFRG + RUSZ                                        |

| rptrMonitorPortCollisions                               | RCOL + MLCOL                                       |

| rptrMonitorPortLateEvents                               | MLCOL                                              |

| rptrMonitorPortVeryLongEvents                           | MVLE                                               |

| rptrMonitorPortDataRateMismatches                       | Not applicable                                     |

| rptrMonitorPortAutoPartitions                           | MPAR                                               |

| rptrMonitorPortTotalErrors                              | MCRC + MALI + ROSZ + RJBR + MSHE +<br>MLCOL + MVLE |

| rptrAddrTrackNewLastSrsAddress                          | UAR1, UAR2                                         |

| rptrAddrTrackSourceAddrChanges                          | MSAC                                               |

| Ethernet-Like                                           | e MIB Counters (RFC1643)                           |

| dot3StatsAlignmentErrors                                | MALI                                               |

| dot3StatsFCSErrors                                      | MCRC                                               |

| dot3StatsSingleCollisionFrames                          | MSCOL                                              |

| dot3StatsMultipleCollisionFrames                        | MMCOL                                              |

| dot3StatsSQETestErrors                                  | Not applicable                                     |

| dot3StatsDeferredTransmissions                          | MDEF                                               |

| dot3StatsLateCollisions                                 | MLCOL                                              |

| dot3StatsExcessiveCollisions                            | Not applicable                                     |

| dot3StatsInternalMACTransmitErrors                      | Not applicable                                     |

| dot3StatsCarrierSenseErrors                             | Not applicable                                     |

| dot3StatsFrameTooLongs                                  | RJBR+ROSZ                                          |

| dot3StatsInternalMACReceiveErrors                       | Not applicable                                     |

| MAC Entity Manag                                        | ed Object Class (IEEE Std 802.3)                   |

| aFrameTransmittedOK                                     | МТРКТ                                              |

| aSingleCollisionFrames                                  | MSCOL                                              |

| aMultipleCollisionFrames                                | MMCOL                                              |

|                                                         |                                                    |

| ( a a =                                                 |                                                    |

| Table 7 21340-AB Counters Summary         (Sheet 3 of 4) |                                                                                    |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Name                                                     | 21340-AB Registers                                                                 |  |

| aFrameReceivedOK                                         | R64 + R65T0127 + R128T0255 + R256T0511 +<br>R512T01023 + R1024T01518 - MALI - MCRC |  |

| aFrameCheckSequenceErrors                                | MCRC                                                                               |  |

| aAlignmentErrors                                         | MALI                                                                               |  |

| aOctetsTransmittedOK                                     | MTOCTH × 100000000h + MTOCTL                                                       |  |

| aFramesWithDeferredXmissions                             | MDEF                                                                               |  |

| aLateCollisions                                          | MLCOL                                                                              |  |

| aFrameAbortedDueToXSColls                                | Not applicable                                                                     |  |

| aFrameLostDueToIntMACXmitError                           | Not applicable                                                                     |  |

| aCarrierSenseError                                       | Not applicable                                                                     |  |

| aOctetsReceivedOK                                        | $MOCTH \times 10000000h + TOCTL$                                                   |  |

| aFrameLostDueToIntMACRcvError                            | Not applicable                                                                     |  |

| aMulticastFrameXmittedOK                                 | Not implemented                                                                    |  |

| aBroadcastFramesXmittedOK                                | Not implemented                                                                    |  |

| aFrameWithExcessiveDeferral                              | Not applicable                                                                     |  |

| aMulticastFrameReceivedOK                                | RMCT                                                                               |  |

| aBroadcastFrameReceivedOK                                | RBCT                                                                               |  |

| alnRangeLengthErrors                                     | Not implemented                                                                    |  |

| aOutOfRangeLengthField                                   | Not implemented                                                                    |  |

| aFrameTooLongErrors                                      | RJBR+BOSZ                                                                          |  |

| Repeater Manage                                          | d Object Class (IEEE Std 802.3)                                                    |  |

| aReadableFrames                                          | R64 + R65TO127 + R128TO255 + R256TO511 +<br>R512TO1023 + R1024TO1518 - MALI - MCRC |  |

| aReadableOctets                                          | $MOCTH \times 10000000h + MOCTL$                                                   |  |

| aFrameCheckSequenceErrors                                | MCRC                                                                               |  |

| aAlignmentErrors                                         | MALI                                                                               |  |

| aFrameTooLong                                            | ROSZ + RJBR                                                                        |  |

|                                                          |                                                                                    |  |

| Table 7 21340-AB Counters Summary         (Sheet 4 of |                    | (Sheet 4 of 4) |

|-------------------------------------------------------|--------------------|----------------|

| Name                                                  | 21340-AB Registers |                |

| aShortEvents                                          | MSHE               |                |

| aRunts                                                | RUSZ + RFRG        |                |

| aCollisions                                           | RCOL + MLCOL       |                |

| aLateEvents                                           | MLCOL              |                |

| aVeryLongEvents                                       | MVLE               |                |

| aDataRateMismatches                                   | Not applicable     |                |

| aAutoPartitions                                       | MPAR               |                |

| alsolates                                             | MISO               |                |

| aSymbolErrorDuringPacket                              | MSYE               |                |

| aLastSourceAddress                                    | UAR1, UAR2         |                |

| aSourceAddressChanges                                 | MSAC               |                |

#### Table 7 21340-AB Counters Summarv

The statistical information of each received packet is appended to it, following broadcast of the packet's data onto the parallel bus segment.

The statistical information is 5 bytes long and contains the following information about the packet:

- The receiving port identification number •

- The receiving 21340-AB chip identification number •

- The packet's length in bytes •

- Indications of:

- CRC error

- Alignment error \_

- MII or a SYM error

- Packet longer than the legal Ethernet packet

- Packet longer than 1600 bytes

- 802.3 or Ethernet packet

- Multicast or unicast packet

- Runt packet (shorter than the minimum valid packet) \_

### 1 October 1997

#### 1.5.11.1 Interrupt Mechanism

The 21340-AB is capable of informing the management entity about various events occurring during run time, using its interrupt mechanism.

The 21340-AB's interrupt is asserted whenever one or more unmasked interrupt events are asserted. It is deasserted when all unmasked interrupt events are deasserted.

Interrupt events are divided into three event groups based on their functionality:

- The error group includes the following events:

- Rx\_FIFO overflow condition

- Tx\_FIFO underflow condition

- Short carrier event

- Late collision event

- No grant issue to port

- Link change direction

- The informative group includes notification events:

- Carrier integrity isolation

- Receive jabber isolation

- Partitioning isolation

- Flow-control identification, process failed notification

- Flow-control identification, process succeeded

- The service group includes all statistic counters' overflow interrupt events

The 21340-AB device provides the management entity with a dedicated status register that enables quick identification of the interrupt source port and its nature. Following identification, the management entity can easily identify and handle the cause of the interrupt.

### 1.5.12 LED Status Indicators

The 21340-AB device supports three status LEDs. Table 8 describes the LEDs and their pin connections.

| LED                         | Pin Number           | Description                                                                                                                                                                                                                                                |

|-----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Activity<br>LED             | 120, 97<br>143, 166  | Turns on when either transmit or receive activity is<br>detected. This signal is stretched to ensure that a signal<br>activity event will be seen. If the activity is continuous,<br>the LED will appear permanently on.                                   |

| Link<br>Integrity LED       | 108, 83<br>150, 127  | Turns on when link integrity status is OK.                                                                                                                                                                                                                 |

| Isolation<br>Indication LED | 175, 176<br>177, 178 | Turns on when the 21340-AB isolates the network port.<br>Port isolation occurs when the port either enters into<br>partition state, detects link unstable or receive jabber<br>condition, performs remote node autodetection, or is in a<br>stopped state. |

Table 8 21340-AB LED Support

**Note:** The 21340-AB port MII interface mode provides only the isolation indication LED. Status indications for link integrity and link activity are provided by the MII PHY device.

#### 1.5.13 Reset Commands

The following commands are available to reset the 21340-AB:

#### • Hardware reset

Asserts the **rst** line for a minimum duration of 0.64  $\mu$ s (16 **clk** cycles) to initialize the hardware. After the reset command, the 21340-AB should be allowed to stabilize for at least 50 **clk** cycles before the first transaction.

Software reset

Sets the SWR{j} register through the 21340-AB management interface port to initiate a software reset. After a software reset, the management entity should poll the STR{j} register's STOP\_RX and STOP\_TX status bits before initiating a new write operation to that port.

For either reset command, the **clk** and **mii\_cs\_clk/sym\_tclk{j}** clocks should be operating normally. At the end of the reset sequence, both receive and transmit paths of the 21340-AB are halted. It is possible to issue successive reset commands.

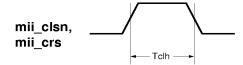

### 1.5.14 Joint Test Action Group Test Logic

This section describes the joint test action group (JTAG) test logic and associated registers (instruction, bypass, and boundary scan) as implemented in the 21340-AB.

**Note:** To understand the description of the 21340-AB JTAG test logic in this section, the reader should be familiar with the IEEE 1149.1 standard.

#### 1.5.14.1 Test Access Port Controller

The test access port (TAP) controller interprets IEEE 1149.1 protocols received on the 21340-AB's four test pins. The following table lists the 21340-AB test pins and their functions.

| Pin Name | Description                  |

|----------|------------------------------|

| tms      | Test mode select             |

| telk     | Test clock                   |

| tdi      | Test data and instruction in |

| tdo      | Test data out                |

All inputs and output data are synchronous to the test clock (tclk). The input signals (tdi, tms) are clocked into the test logic at the rising edge of tclk while the output signal (tdo) is clocked on the tclk falling edge.

The TAP controller interprets IEEE 1149.1 protocols received on the **tms**, **tclk** and **tdi** pins. It generates clocks and control signals to control the operation on the test logic. The control signals switch **tdi** and **tdo** between the instruction and test data registers.

#### 1.5.14.2 JTAG Test Registers

In the JTAG test logic, three registers are implemented through the 21340-AB's pads:

- Instruction register

- Bypass register

- Boundary-scan register

Table 9 describes the types of test instructions that are interpreted by the 21340-AB's JTAG test logic.

| Table 9 21340-AB JTAG Test Instruction |

|----------------------------------------|

|----------------------------------------|

| Instruction                   | Operation<br>Code | Description                                                                                                                                                                                     |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bypass<br>Instruction         | 111               | Used to provide a minimum length serial path between the <b>tdi</b> and <b>tdo</b> pins of the 21340-AB when the test logic in the 21340-AB is bypassed.                                        |

|                               |                   | When power is applied, JTAG test logic resets to bypass mode.                                                                                                                                   |

| Extest<br>Instruction         | 000               | Allows testing of the 21340-AB board-level<br>interconnections. Test data is shifted into the<br>boundary-scan register on the 21340-AB and then<br>transferred in parallel to the output pins. |

| Sample/Preload<br>Instruction | 001               | Allows scanning of the boundary-scan register without causing interference to the normal operation of the onchip system logic.                                                                  |

| Continuity<br>Instruction     | 110               | Allows checking of the connectivity of the 21340-AB pins<br>on the board. This instruction causes all output pins of the<br>21340-AB to drive the value 0.                                      |

| Tristate<br>Instruction       | 101               | Causes all output pins of the 21340-AB to be tristated.                                                                                                                                         |

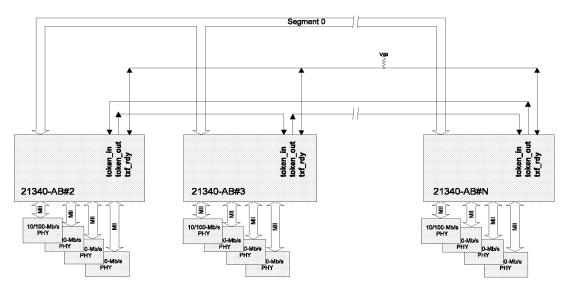

#### 1.5.15 Internal Arbitration Scheme Support

When the internal onchip arbiter function is enabled, a token is circulated between all ports sharing the same segment. When a 21340-AB port receives a token, it has the permission to broadcast its received packet(s) onto the parallel segment. If the port has stored packets in its Rx\_FIFO and it receives a token, it captures the token and broadcasts its stored packets until one of the following conditions occurs:

- The port broadcasted a full burst of packets, as defined by the its burst-size control bits.

- The port has no more packets stored in its Rx\_FIFO.

- The destination ports cannot load a new packet.

When a port completes its broadcast operation, or does not have any stored packets in its Rx\_FIFO, it passes the token on to the next inline port sharing the same segment [i].

Because the burst size can be defined separately for each of the 21340-AB ports, the user can initialize some of the 21340-AB ports with higher priority by programming them to have a larger allowed burst size.

Table 10 lists the interface provided for the internal arbitration scheme.

| Pin Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| token_out[i] | Together with the <b>token_in[i]</b> pin, creates a ring connectivity<br>between all ports sharing segment[i]. Grants the following<br>21340-AB port connected to segment[i] to broadcast a burst of<br>its received packets in its turn.                                                                                                                                                                                                        |

| token_in[i]  | Together with the <b>token_out</b> pin, creates a ring connectivity<br>between all ports sharing segment[i]. Grants the current<br>21340-AB port connected to segment[i] to broadcast a burst of<br>its received packets in its turn.<br>The port captures and holds the token while broadcasting.<br>When the port completes its broadcast operation, it passes the<br>token on to the next port connected to segment[i], through the           |

|              | token_out[i] pin.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| txf_rdy[i]   | Shared among all ports connected to segment[i]. Asserted by<br>the 21340-AB port to inform the broadcasted port that it does<br>not have enough space to load a new packet from the parallel<br>packet to its Tx_FIFO. When the broadcasting port detects the<br><b>txf_rdy[i]</b> signal assertion, it completes the current packet's<br>broadcast operation, and then passes the token on to the next<br>inline port sharing the same segment. |

| ext_arb      | Should be connected to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 10 Internal Arbiter Interface

Figure 7 shows the internal arbitration scheme connectivity for one segment.

#### Figure 7 Internal Arbitration Scheme Connectivity

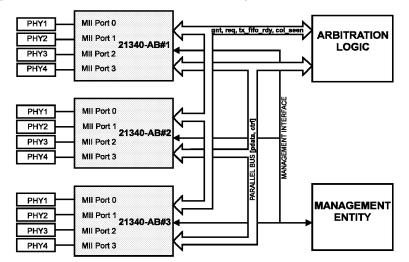

### 1.5.16 External Arbitration Scheme Support

When the external arbiter mode of operation is enabled, the arbitration scheme is performed by an external arbiter. It determines which of the ports on a parallel bus segment is granted the next opportunity to broadcast its received packet.

The arbitration scheme should avoid deadlocks. Table 11 lists the interface provided for the arbiter.

Table 11 External Arbiter Interface

| Pin Name       | Description                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_fifo_rdy{j} | Indicates that the 21340-AB port is able to load a new packet for transmission.                                                                                            |

| req{j}         | Indicates the 21340-AB port's request to broadcast a received packet.                                                                                                      |

| col_seen{j}    | When set, indicates that the port has experienced a collision during transmission when the $req{j}$ line was not asserted. (Optional for advanced arbitration algorithms.) |

| gnt{j}         | When asserted, notifies the 21340-AB port that it owns the <b>pdata[i]</b> , <b>cntl[i]</b> , and <b>strb[i]</b> lines, and may broadcast its received packet.             |

| ext_arb        | Should be connected to Vdd.                                                                                                                                                |

In addition to the hooks listed in Table 11, other factors must be considered:

- The arbiter should not grant a port unless all target ports' **tx\_fifo\_rdy** signals are asserted.

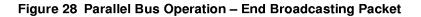

- The **gnt** signal should be set for at least 10 **clk** cycles during broadcast and deasserted no later than one **clk** cycle after termination of broadcast. (See Figure 28.)

In a segmented network, each network segment should have its own arbitration logic. Each arbiter should be notified of the ports grouped in its segment and update the ports dynamically. Figure 8 shows the external arbitration connectivity.

Figure 8 External Arbitration Connectivity

**Network Applications**

### **1.6 Network Applications**

This section describes the use of the 21340-AB in various network applications.

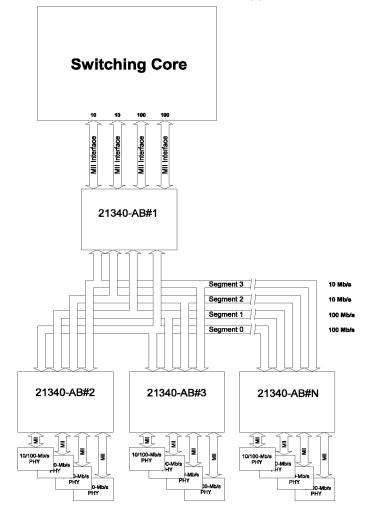

#### 1.6.1 21340-AB in Port Switch Applications

A port switch is a cost-optimized approach for addressing the need of additional network bandwidth while maintaining the flexibility of adding, removing or moving users between segments.

A port switch can balance a network by assigning the bandwidth-hungry users to a less utilized or even separate segment while assigning other users, with lower bandwidth requirements, to share a different segment. As network conditions change, users can be moved from one segment to another, thus balancing the network. A port switch also provides excellent support for workgroup security and VLAN-based applications. Users can share applications, data, and server without being interfered by users on other segments.

A 10/100-Mb/s dual-rate port enables the assignment of ports to segments, based on their data transfer rate and bandwidth allocation requirements. When a port is ready to migrate to 100 Mb/s, it is reallocated by a software command to a 100-Mb/s segment. No other modification in the wiring closet is required.

Features unique to the 21340-AB enable it to improve the performance of port switch applications, lower the solution cost, and reduce development time-to-market while maintaining the powerful features of the switching core.

Figure 9 shows how the 21340-AB building block can be configured in a port switch application. The switch engine in Figure 9 has four ports, each connected to the 21340-AB system's four independent segments using the 21340-AB#1 device. The 21340-AB#1, which is configured to work in the inverse mode of operation, provides a simple, low-cost, glueless connection between the switch MII interface and the 21340-AB parallel bus segments.

**Network Applications**

#### Figure 9 21340-AB in a 10/100-Mb/s Switch Application

The 21340-AB improves network throughput compared to a standard multisegment repeater. Collisions experienced on any of its ports do not propagate to other ports sharing the same segments and switching core. In addition, the 21340-AB filters out fragment packets, preventing them from being propagated in the network. The 21340-AB address filtering mechanism filters out intrasegment packets that otherwise would have been presented to the switching engine by a standard multisegment repeater.

**Network Applications**

The 21340 port's flow-control mechanism (backpressure or credit-based) ensures no packet loss. When the switch engine is congested, backpressure is applied only against the aggressive node. Other remote nodes in the network segment are not affected by the backpressure built-in operation.

The unique features of the 21340-AB (dual MII mode of operation, expandable and flexible internal arbitration scheme, and backpressure scheme) reduce port switch system cost and development time. In addition, the 21340-AB ports can be allocated to segments by a simple software command. This ability to move, add, or remove users from a segment, provides an excellent support for VLAN applications. Because ports can have different priorities by programming them to a larger packet's burst size while granted, there is greater flexibility in designing port switch-based applications.

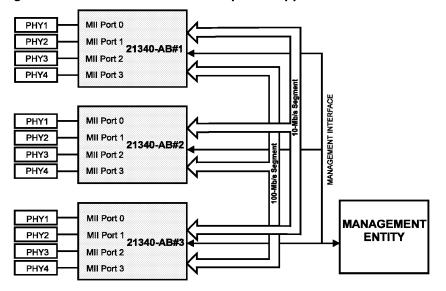

#### 1.6.2 21340-AB in 10/100 Dual-Rate Enhanced Repeater Applications

Figure 10 shows how 21340-AB building blocks can be configured in a non-SNMP-managed 10/100-Mb/s dual-rate enhanced repeater system. The management entity detects the local and remote PHY capabilities, initializes the 21340-AB ports' modes of operation appropriately, and then enables the ports.

Figure 10 21340-AB in Enhanced Repeater Application

#### Limitations

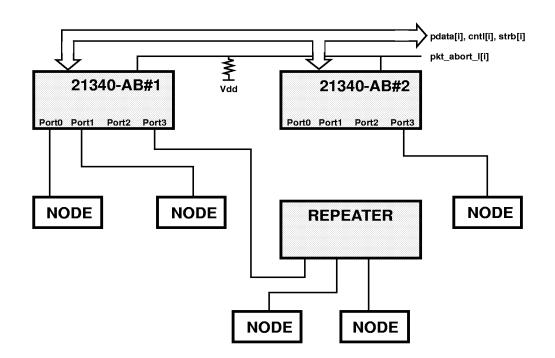

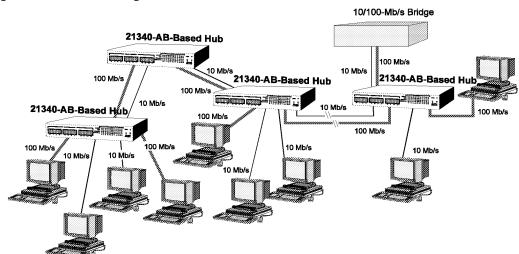

Figure 11 shows a network of 10/100-Mb/s dual-rate enhanced repeater systems that use 21340-AB building blocks. The network includes two segments: one operates at 10 Mb/s and the other operates at 100 Mb/s. A 10/100-Mb/s bridge device is used in order to connect between the 10-Mb/s and the 100-Mb/s segments.

When a remote node is changed from 10 Mb/s to 100 Mb/s, the management entity identifies the change through Auto-Negotiation. Based on this information, the management entity reassigns the port to the segment with the matching data transfer rate of 100 Mb/s. Upgrading remote nodes can occur gradually without changing the hardware.

#### Figure 11 Low-Cost Migration from 10 Mb/s to 100 Mb/s

#### 1.7 Limitations

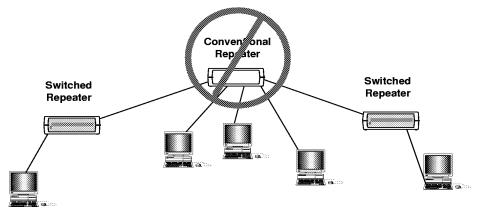

It is not recommended to create a topology with conventional repeaters interleaved between 21340-AB-based repeaters because this may lead to degradation in performance. Figure 12 shows an example of the unrecommended topology.

**Recommended PHY Devices**

#### Figure 12 Unrecommended Network Topology

#### **1.8 Recommended PHY Devices**

The 21340-AB implements a remote node autodetection scheme that detects if the remote node connected to a 21340-AB port is capable of using the 21340-AB flow-control scheme. Table 12 lists the capability requirements for the PHY devices.

| Protocol                  | Interface | Capability                                |

|---------------------------|-----------|-------------------------------------------|

| 10BASE-T or<br>100BASE-TX | MII       | Full-duplex support with Auto-Negotiation |

| 100BASE-TX                | SYM PHY   | Full-duplex with <b>txen</b> pin          |

| 10BASE-T or<br>100BASE-T4 | MII       | Auto-Negotiation                          |

| Table 12 | PHY Device | Capability | Requirements |

|----------|------------|------------|--------------|

|----------|------------|------------|--------------|

Other PHY devices may require manual programming to establish 21340-AB-21340-AB flow-control connections.

**Related Documents**

#### **1.9 Related Documents**

The 21340-AB design criteria meets the following specifications:

- IEEE Standard 802.3u–1995 Supplement to ISO/IEC 8802-3:1993

- IETF Remote Network Monitoring (RMON) MIB (RFC 1757)

- *IETF Repeater Device MIB (RFC 1516)*

- IETF Ethernet-Like MIB (RFC 1643)

- IEEE Standard 1149.1 Test Access Port and Boundary Scan Architecture

## 2 Pinout

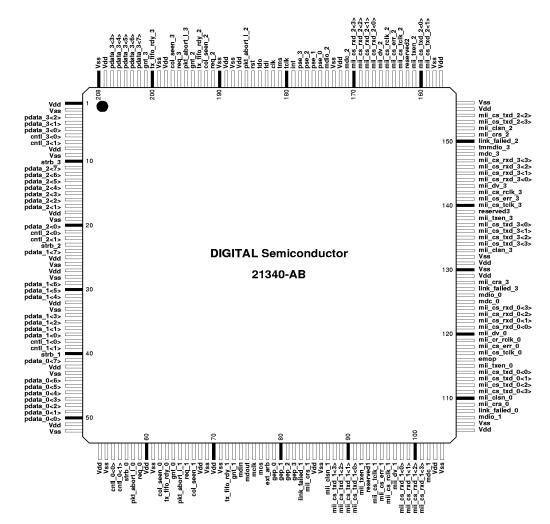

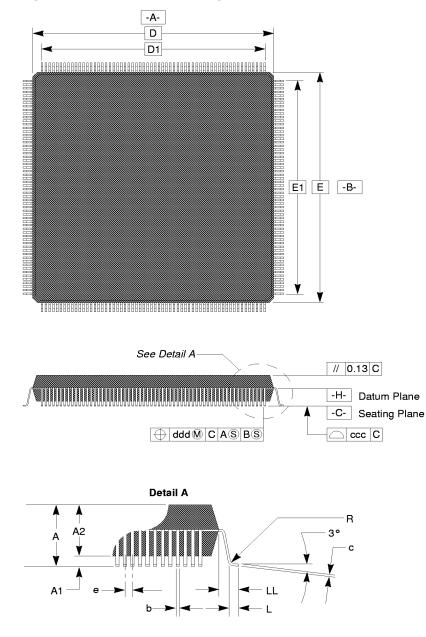

The 21340-AB is packaged in a 208-pin plastic quad flat pack (PQFP). Figure 13 shows the 21340-AB pinout.

Signal List

## 2.1 Signal List

Table 13 lists the 21340-AB's external signals and their associated pins.

| Tabla | 12 | Din/Gianal List |

|-------|----|-----------------|

| Iable | 13 | Pin/Signal List |

(Sheet 1 of 3)

| Signal          | Pin<br>Number | Signal        | Pin<br>Number | Signal          | Pin<br>Number |

|-----------------|---------------|---------------|---------------|-----------------|---------------|

| ext_arb         | 78            | link_failed_1 | 83            | mii_cs_err_0    | 118           |

| clk             | 182           | link_failed_2 | 150           | mii_cs_err_1    | 95            |

| cntl_0<0>       | 55            | link_failed_3 | 127           | mii_cs_err_2    | 164           |

| cntl_0<1>       | 56            | mclk          | 76            | mii_cs_err_3    | 141           |

| cntl_1<0>       | 38            | mcs           | 77            | mii_cs_rclk_0   | 119           |

| cntl_1<1>       | 39            | mdc_0         | 125           | mii_cs_rclk_1   | 96            |

| cntl_2<0>       | 21            | mdc_1         | 102           | mii_cs_rclk_2   | 165           |

| cntl_2<1>       | 22            | mdc_2         | 171           | mii_cs_rclk_3   | 142           |

| cntl_3<0>       | 6             | mdc_3         | 148           | mii_cs_rxd_0<0> | 121           |

| cntl_3<1>       | 7             | mdin          | 74            | mii_cs_rxd_0<1> | 122           |

| col_seen_0      | 62            | mdio_0        | 126           | mii_cs_rxd_0<2> | 123           |

| col_seen_1      | 67            | mdio_1        | 107           | mii_cs_rxd_0<3> | 124           |

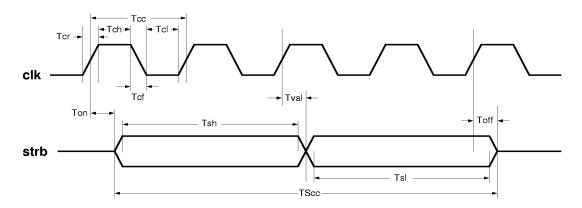

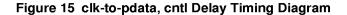

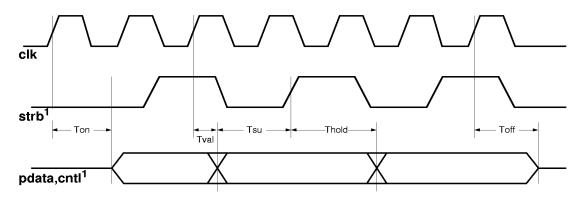

| col_seen_2      | 192           | mdio_2        | 174           | mii_cs_rxd_1<0> | 98            |

| col_seen_3      | 197           | mdio_3        | 149           | mii_cs_rxd_1<1> | 99            |

| gep_0           | 79            | mdout         | 75            | mii_cs_rxd_1<2> | 100           |

| gep_1           | 80            | mii_clsn_0    | 110           | mii_cs_rxd_1<3> | 101           |

| gep_2           | 81            | mii_clsn_1    | 87            | mii_cs_rxd_2<0> | 167           |

| gep_3           | 82            | mii_clsn_2    | 152           | mii_cs_rxd_2<1> | 168           |

| gnt_0           | 64            | mii_clsn_3    | 133           | mii_cs_rxd_2<2> | 169           |

| gnt_1           | 73            | mii_crs_0     | 109           | mii_cs_rxd_2<3> | 170           |

| gnt_2           | 194           | mii_crs_1     | 84            | mii_cs_rxd_3<0> | 144           |

| gnt_3           | 201           | mii_crs_2     | 151           | mii_cs_rxd_3<1> | 145           |

| link_failed_0   | 108           | mii_crs_3     | 128           | mii_cs_rxd_3<2> | 146           |

| mii_cs_rxd_3<3> | 147           | mii_txen_3    | 138           | pdata_3<3>      | 206           |

42 Pinout

#### Signal List

#### Table 13 Pin/Signal List

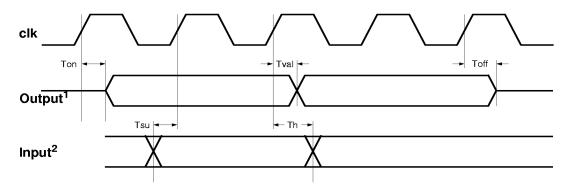

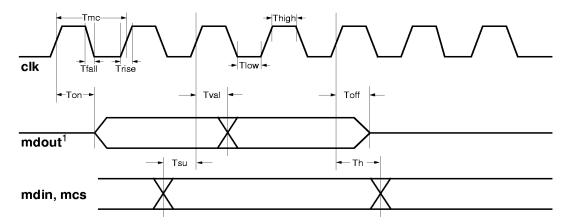

| Signal          | Pin<br>Number | Signal     | Pin<br>Number | Signal        | Pin<br>Number |