# UNISONIC TECHNOLOGIES CO., LTD

**Preliminary**

## LINEAR INTEGRATED CIRCUIT

# MONOLITHIC IC 82XX SERIES

#### DESCRIPTION

The normal operation of the UTC 82XX is that while the power is turned on or interrupted, detect power supply voltage and then reset the system accurately.

The internal circuits of the UTC 82XX include a built-in fixed delay time generating circuit. With a counter timer using an analog/digital hybrid circuit, the UTC 82XX as new low reset type system reset ICs expands the delay time series.

These ICs can be used in a variety of CPU systems and other logic systems.

#### **FEATURES**

- \* Internal Fixed Delay Time Setting by Counter Timer

- \* Grate Delay Time Temperature Characteristics:±800ppm/°C

- \* Operating Limit Voltage as 0.65V(Typ.)

- \* Hysteresis Voltage Provided: 50mV(Typ.)

- \* Circuit Current While On I<sub>CCL</sub>=300µA(Typ.)

- \* Circuit Current While Off I<sub>CCH</sub>=200µA(Typ.)

1 of 8

#### ORDERING INFORMATION

| Ordering Number | Package | Packing   |

|-----------------|---------|-----------|

| 82XXG-x-AF5-R   | SOT-25  | Tape Reel |

Notes: xx: Output Voltage, refer to Marking Information.

x: Delay Time, refer to Electrical Characteristics of "H" Transport Delay Time

www.unisonic.com.tw QW-R502-326.c

<sup>\*</sup> Halogen Free

## **MARKING INFORMATION**

| PACKAGE | VOLTAGE CODE                   | MARKING                                          |

|---------|--------------------------------|--------------------------------------------------|

| SOT-25  | 25:2.5V<br>27:2.7V<br>2K:2.93V | Month ✓ XXXX V. L: Lead Free G: Halogen Free 4 5 |

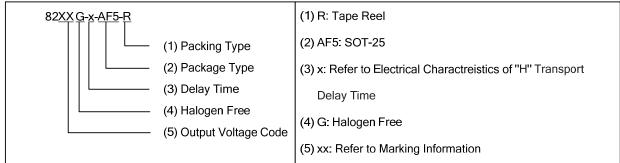

# **■ PIN CONFIGURATION**

# **■ PIN DESCRIPTION**

| PIN NO. | PIN NAME  | DESCRIPTION       |

|---------|-----------|-------------------|

| 1       | $V_{OUT}$ | Output pin        |

| 2       | NC        | Connected nothing |

| 3       | RESET     | Reset control pin |

| 4       | Vcc       | Supply voltage    |

| 5       | GND       | Ground            |

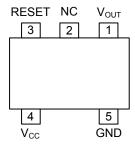

# **■ BLOCK DIAGRAM**

## ■ ABSOLUTE MAXIMUM RATING (Ta=25°C)

| PARAMETER                  | SYMBOL           | RATINGS  | UNIT |

|----------------------------|------------------|----------|------|

| Power Supply Voltage       | V <sub>CC</sub>  | -0.3~+10 | V    |

| Manual Reset Input Voltage | $V_{RESET}$      | -0.3~+10 | V    |

| Power Dissipation          | $P_D$            | 400      | mW   |

| Operating Temperature      | T <sub>OPR</sub> | -20~+75  | °C   |

| Storage Temperature        | T <sub>STG</sub> | -40~+125 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## ■ ELECTRICAL CHARACTERISTICS (Ta=25°C, Unless otherwise specified)

#### V<sub>S</sub>=2.5V~2.93V

| PARAMETER                                 |              | SYMBOL                  | TEST CONDITIONS                                                                            |                                                                      | MIN                      | TYP  | MAX                      | UNIT |    |

|-------------------------------------------|--------------|-------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------|------|--------------------------|------|----|

| Detection Voltage                         |              | Vs                      | $V_{OL} \le 0.4V$ , $V_{CC} = H \rightarrow L$ , $R_L = 470\Omega$<br>(See Test Circuit 1) |                                                                      | V <sub>S</sub><br>-0.15V | Vs   | V <sub>S</sub><br>+0.15V | V    |    |

| Low-Level Output Voltage                  |              | V <sub>OL</sub>         | $V_{CC}=V_{S(min)}$ -0.05V, $R_L$ =470 $\Omega$ (See Test Circuit 1)                       |                                                                      | 0.1                      | 0.4  | V                        |      |    |

| Operating Pow                             | er Supply Vo | Itage                   | V <sub>OPL</sub>                                                                           | $R_L=4.7k\Omega$ , $V_{OL}\leq0.4V$                                  |                          | 0.65 | 0.85                     | V    |    |

| Hysteresis Voltage                        |              | ΔVs                     | $V_{CC}=L \rightarrow H \rightarrow L$ , $R_L=470\Omega$<br>(See Test Circuit 1)           | 30                                                                   | 50                       | 100  | mV                       |      |    |

| Detection Voltage Temperature Coefficient |              | <u>VS</u><br>ΔT         | R <sub>L</sub> =470Ω, Ta=-20°C~+75°C<br>(See Test Circuit 1)                               |                                                                      | ±0.01                    |      | %/°C                     |      |    |

| Output Leakag                             | e Current    |                         | I <sub>OH</sub>                                                                            | V <sub>CC</sub> =10V (See Test Circuit 1)                            |                          |      | ±0.1                     | μΑ   |    |

| 0: 110                                    |              | On                      | I <sub>CCL</sub>                                                                           | $V_{CC} = V_{S(min)}$ -0.05V, $R_L = \infty$<br>(See Test Circuit 1) |                          |      | 300                      | 600  | μΑ |

| Circuit Current                           |              | Off                     | Іссн                                                                                       | $V_{CC}=V_{S(Typ)}/0.85V$ , $R_L=\infty$<br>(See Test Circuit 1)     |                          |      | 200                      | 350  | μΑ |

|                                           |              |                         |                                                                                            |                                                                      | Р                        | 30   | 50                       | 75   | mS |

|                                           |              |                         |                                                                                            | D =4.7KO C =400DE (Note 1)                                           | Q                        | 60   | 100                      | 150  | mS |

| "H" Transport [                           | Delay Time   |                         | $t_{PLH}$                                                                                  | $R_L$ =4.7K $\Omega$ , $C_L$ =100PF (Note 1) (See Test Circuit 2)    | R                        | 120  | 200                      | 300  | mS |

|                                           |              |                         |                                                                                            | (See Test Gircuit 2)                                                 | S                        | 240  | 400                      | 600  | mS |

|                                           |              |                         |                                                                                            |                                                                      | Τ                        | 480  | 800                      | 1200 | mS |

| "L" Transport Delay Time                  |              | t <sub>PHL</sub>        | $R_L$ =4.7k $\Omega$ , $C_L$ =100PF (Note 1)<br>(See Test Circuit 2)                       |                                                                      |                          | 10   |                          | μS   |    |

| Output Current While on 1                 |              | I <sub>OL1</sub>        | $V_{CC}$ =VS min0.05V, $R_L$ =0 $\Omega$<br>(See Test Circuit 1)                           |                                                                      | 8                        |      |                          | mA   |    |

| Output Current While on 2                 |              | I <sub>OL2</sub>        | Ta=-20°C ~+75°C, $R_L$ =0 $\Omega$ (Note 2)<br>(See Test Circuit 1)                        |                                                                      | 6                        |      |                          | mA   |    |

| Pin                                       | Input High \ | oltage/                 | $V_{RESH}$                                                                                 |                                                                      |                          | 2.0  |                          |      | V  |

|                                           | Input High C | Input High Current IRES |                                                                                            | V <sub>RESET</sub> =2V                                               |                          |      |                          | 80   | μA |

|                                           | Input Low V  | oltage                  | V <sub>RESL</sub>                                                                          |                                                                      |                          |      |                          | 0.8  | V  |

Notes: 1.  $t_{PLH}$ :  $V_{CC}$ =  $(V_{S(TYP)}$ -0.4V) $\rightarrow$   $(V_{S(TYP)}$ +0.4V)  $t_{PHL}$ :  $V_{CC}$ =  $(V_{S(TYP)}$ +0.4V) $\rightarrow$   $(V_{S(TYP)}$ -0.4V)

- 2. V<sub>CC</sub>=V<sub>S(MIN)</sub>-0.15V

- 3.  $V_{\text{OUT}}$  pin is low when manual reset pin is high.  $V_{\text{OUT}}$  pin is high when manual reset pin is low.

#### **■ TEST CIRCUITS**

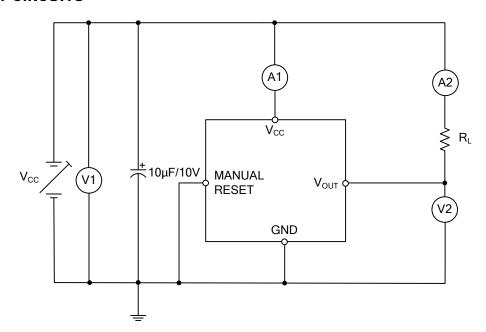

**Test Circuit 1**

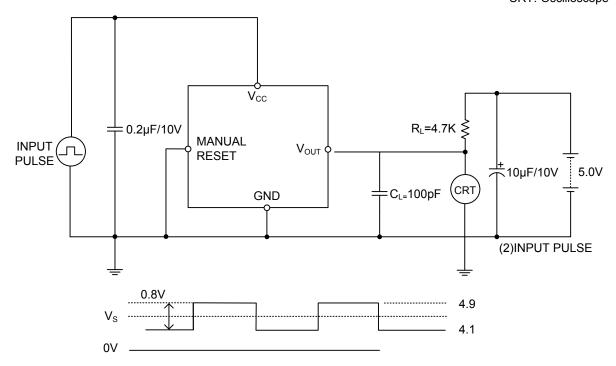

A: DC ammeter V: DC voltmeter CRT: Oscilloscope

Note Input model is an example for 82XX

**Test Circuit 2**

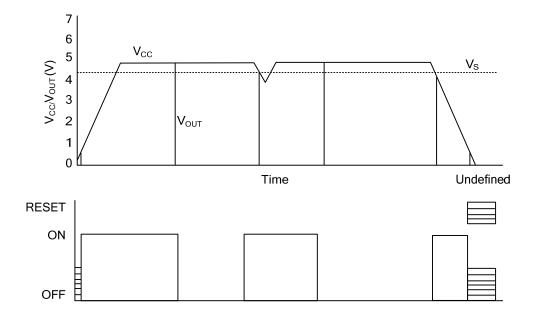

## **■ TIMING CHART**

#### **■ TYPICAL APPLICATION CIRCUITS**

**Preliminary**

#### 1. Normal hard reset

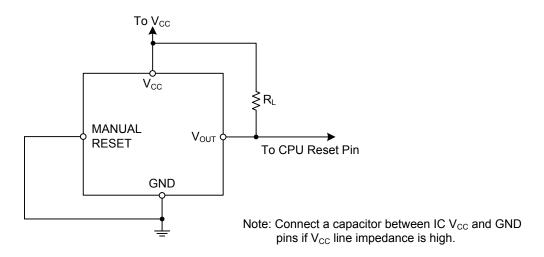

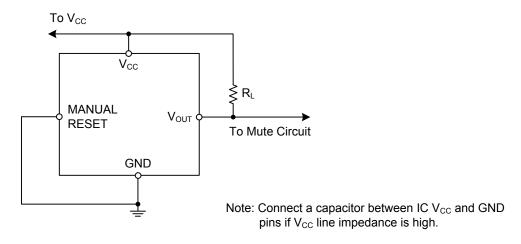

#### 2. Manual reset

Note: Connect a capacitor between IC  $V_{\text{CC}}$  and GND pins if  $V_{\text{CC}}$  line impedance is high.

#### 3. Mute circuit

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.