# Single Air-Core Gauge Driver

# Description

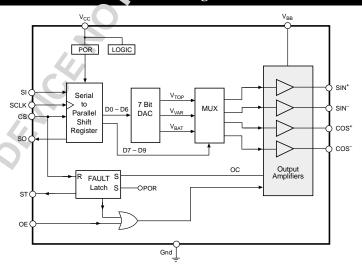

The CS4172 is a monolithic BiCMOS integrated circuit used to translate a digital 10-bit word from a microprocessor/microcontroller to complementary DC outputs. The DC outputs drive an air-core meter commonly used in vehicle instrument panels. The 10 bits of data are used to linearly control the quadrature coils of the meter directly with a 0.35° resolution and ±1.0° accuracy over the full 360° range of the gauge. The interface from the microcontroller is by a Serial Peripheral Interface (SPI) compatible serial connection using up to a 2MHz shift clock rate.

The digital code, which is directly proportional to the desired gauge pointer deflection, is shifted into a DAC and multiplexer. These two blocks provide a tangential conversion function to change the digital data into the appropriate DC coil voltage for the angle demanded. The tangential algorithm creates approximately 40% more torque in the meter movement than does a sin-cos algorithm at 45°, 135°,

225°, and 315° angles. This increased torque reduces the error due to pointer droop at these critical angles.

Each output buffer is capable of supplying up to 80mA per coil and are controlled by a common enable pin. When OE is low the output buffers are turned off but the logic portion of the chip remains powered and continues to operate normally.

The Serial Gauge Driver is self-protected against output short circuit conditions. The output drivers are disabled anytime the on-chip protection circuitry detects a short circuit condition. The outputs remain off until a falling edge is presented on CS. If the short circuit is still present the output drivers automatically disable themselves again. A thermal protection circuit limits the junction temperature to approximately 160°C for conditions of high supply voltage and high ambient temperature.

The status pin (ST) reflects the state of the outputs and is low whenever the outputs are disabled.

## **Features**

- Serial Input Bus

- 2MHz Operating Frequency

- Tangential Drive Algorithm

- 80mA Drive Circuits

- 0.5° Accuracy (Typ.)

- Power-On-Reset

- Protection Features

Output Short Circuit

Overtemperature

# **Package Options**

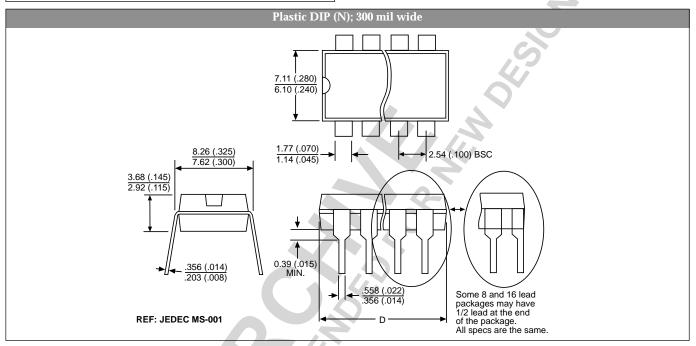

#### 16 Lead PDIP

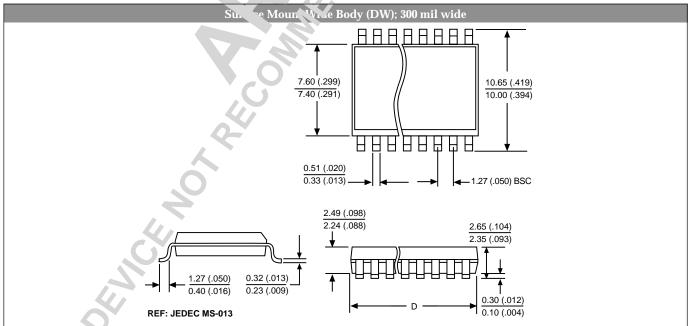

## 16 Lead SO Wide

#### Block Diagram

ON

ON Semiconductor 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885–3600 Fax: (401)885–5786 N. American Technical Support: 800-282-9855 Web Site: www.cherry-semi.com

## **Absolute Maximum Ratings**

| $\mathfrak S$                                    |                         |

|--------------------------------------------------|-------------------------|

| Supply Voltage                                   |                         |

| $ m V_{BB}$                                      |                         |

| V <sub>CC</sub><br>Digital Inputs                |                         |

| Digital Inputs                                   |                         |

| Ground Potential Difference (  AGnd-DGnd  )      | 0.5V                    |

| Steady State Output Current                      | ±100mA                  |

| Forced Injection Current (Inputs and Supply)     |                         |

| Operating Junction Temperature (T <sub>J</sub> ) | 150°C                   |

| Storage Temperature Range                        | 65°C to 150°C           |

| Lead Temperature Soldering                       |                         |

| Wave Solder (through hole styles only)           | 10 sec. max, 260°C peak |

| Reflow (SMD styles only)                         |                         |

| ESD Susceptibility (Human Body Model)            | 2kV                     |

|                                                  |                         |

| PARAMETER                          | TEST CONDITIONS                                                                                                           | MIN                     | TYP                  | MAX                 | UNI |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|---------------------|-----|

| <b>Supply Voltages and Current</b> | is                                                                                                                        |                         |                      |                     |     |

| V <sub>BB</sub> Quiescent Current  | Output disabled (OE = 0V) $ [R_{COS}, R_{SIN} = R_{L(MIN)}] @ 45^{\circ} $ $ (code = X'080) V_{BB} = 14V $                |                         | 1                    | 5<br>175            | m/  |

| V <sub>CC</sub> Quiescent Current  | $\begin{aligned} \text{OE} &= \text{high, V}_{\text{BB}} = \text{0V} \\ \text{SCLK} &= 2.0 \text{MHz} \end{aligned}$      |                         |                      | 1                   | m   |

| Digital Inputs and Outputs         |                                                                                                                           |                         |                      |                     |     |

| Output High Voltage                | SO, I <sub>OH</sub> = 0.8mA                                                                                               | V <sub>CC</sub> - 0.8   |                      |                     |     |

| Output Low Voltage                 | SO, $I_{OL} = 0.8 \text{mA}$<br>ST, $I_{OL} = 2.5 \text{mA}$                                                              |                         |                      | 0.4<br>0.8          | 7   |

| Output High Current                | ST, $V_{CC} = 5.0V$                                                                                                       |                         |                      | 25                  | μ   |

| Input High Voltage                 | CS, SCLK, SI, OE                                                                                                          | $0.7 \times V_{\rm CC}$ |                      |                     | 7   |

| Input Low Voltage                  | CS, SCLK, SI, OE                                                                                                          |                         |                      | $0.3 \times V_{CC}$ | 1   |

| Input High Current                 | CS, SCLK, SI, OE; $V_{IN} = 0.7 \times V_{CC}$                                                                            |                         |                      | 1                   | μ   |

| Input Low Current                  | CS, SCLK, SI, OE; $V_{IN} = 0.3 \times V_{CC}$                                                                            |                         |                      | 1                   | μ   |

| Analog Outputs                     |                                                                                                                           |                         |                      |                     |     |

| Output Function Accuracy           |                                                                                                                           | -1.2                    |                      | +1.2                | de  |

| Output Shutdown Current,<br>Source | $V_{BB} = 14.0V$                                                                                                          | 70                      |                      | 250                 | m   |

| Output Shutdown Current,<br>Sink   | $V_{BB} = 14.0V$                                                                                                          | 70                      |                      | 250                 | m   |

| Output Shutdown Current,<br>Source | $V_{BB} = 7.5V$                                                                                                           | 43                      |                      | 250                 | m   |

| Output Shutdown Current,<br>Sink   | $V_{BB} = 7.5V$                                                                                                           | 43                      |                      | 250                 | m   |

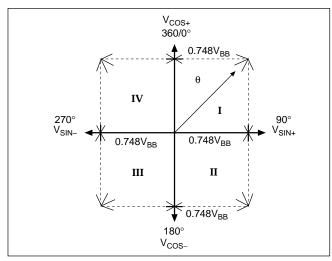

| Coil Drive Output Voltage          |                                                                                                                           |                         | $0.748\times V_{BB}$ |                     | 1   |

| Minimum Load Resistance            | $T_{\mathrm{A}} = 105^{\circ}\mathrm{C}$ $T_{\mathrm{A}} = 25^{\circ}\mathrm{C}$ $T_{\mathrm{A}} = -40^{\circ}\mathrm{C}$ |                         | 229<br>171<br>150    |                     | 2   |

# $Electrical\ Characteristics: -40^{\circ}C \leq T_{A} \leq 105^{\circ}C; \ 7.5V \leq V_{BB} \leq 14V; \ 4.5V \leq V_{CC} \leq 5.5V; \ unless\ otherwise\ specified.$

| PARAMETER             | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------|-----|-----|-----|------|

| Shift Clock Frequency |                                           |     |     | 2.0 | MHz  |

| SCLK High Time        |                                           | 175 |     |     | ns   |

| SCLK Low Time         |                                           | 175 |     |     | ns   |

| SO Rise Time          | $0.75V$ to $V_{CC} - 1.2V$ ; $C_L = 90pF$ |     |     | 150 | ns   |

| SO Fall Time          | $0.75V$ to $V_{CC} - 1.2V$ ; $C_L = 90pF$ |     |     | 150 | ns   |

| SO Delay Time         | $C_L = 90pF$                              |     |     | 150 | ns   |

| SI Setup Time         |                                           | 75  |     |     | ns   |

| SI Hold Time          |                                           | 75  |     |     | ns   |

| CS Setup Time         |                                           | 0   |     |     | ns   |

| CS Hold Time          |                                           | 75  |     |     | ns   |

| Package Pin Description |              |                  |                                                                                                                                                                                                                                                                                                             |  |

|-------------------------|--------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PACKAC                  | GE PIN#      | PIN SYMBOL       | FUNCTION                                                                                                                                                                                                                                                                                                    |  |

| 16 Lead SO Wide         | 16 Lead PDIP |                  |                                                                                                                                                                                                                                                                                                             |  |

| 1                       | 1            | SIN-             | Negative output for SINE coil.                                                                                                                                                                                                                                                                              |  |

| 2                       | 2            | SIN <sup>+</sup> | Positive output for SINE coil.                                                                                                                                                                                                                                                                              |  |

| 3                       | 4            | $ m V_{BB}$      | Analog supply. Nominally 13.5V.                                                                                                                                                                                                                                                                             |  |

| 4,5,12,13               | 3,13,14      | Gnd              | Ground.                                                                                                                                                                                                                                                                                                     |  |

| 6                       | 6            | SI               | Serial data input. Data present at the rising edge of the clock signal is shifted into the internal shift register.                                                                                                                                                                                         |  |

| 7                       | 7            | $V_{CC}$         | 5V logic supply. The internal registers and latches are reset by a POR generated by the rising edge of the voltage on this pin.                                                                                                                                                                             |  |

| 8                       | 8            | OE               | Controls the state of the output buffers. A logic low on this pin turns them off.                                                                                                                                                                                                                           |  |

| 9                       | 9            | SCLK             | Serial clock for shifting in/out of data. Rising edge shifts data on SI into the shift register and the falling edge changes the data on SO.                                                                                                                                                                |  |

| 10                      | 10           | CS               | When high allows data at SI to be shifted into part with<br>the rising edges of SCLK. The falling edge transfers the<br>shift register contents into the DAC and multiplexer to<br>update the output buffers. The falling edge also re-enables<br>the output drivers if they have been disabled by a fault. |  |

| 11                      | 11           | ST               | STATUS reflects the state of the outputs and is low any-<br>time the outputs are disabled, either by OE or the internal<br>protection circuitry. Requires external pull-up resistor.                                                                                                                        |  |

| 14                      | 5            | SO               | Serial data output. Existing 10-bit data is shifted out when<br>new data is shifted in. Allows cascading of multiple<br>devices on common serial port.                                                                                                                                                      |  |

| 15                      | 15           | COS-             | Negative output for COSINE coil.                                                                                                                                                                                                                                                                            |  |

| 16                      | 16           | COS+             | Positive output for COSINE coil.                                                                                                                                                                                                                                                                            |  |

|                         | 12           | NC               | No connection.                                                                                                                                                                                                                                                                                              |  |

## **Applications Information**

## **Theory of Operation**

The SACD is for interfacing between a microcontroller or microprocessor and air-core meter movements commonly used in automotive vehicles for speedometers and tachometers. These movements are built using 2 coils placed at a 90° orientation to each other. A magnetized disc floats in the middle of the coils and responds to the magnetic field generated by each coil. The disc has a shaft attached to it that protrudes out of the assembly. A pointer indicator is attached to this shaft and in conjunction with a separate printed scale displays the vehicle's speed or the engine's speed.

The disc (and pointer) respond to the vector sum of the voltages applied to the coils. Ideally, this relationship fol-

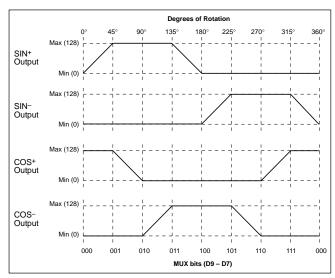

lows a cosine equation. Since this is a transcendental and non-linear function, devices of this type use an approximation for this relationship. The SACD uses a tangential algorithm as shown in Figure 1. Only 1 output varies in any 45 degree range.

Figure 1. Major gauge outputs.

#### Quadrant I

$$\theta = Tan^{-1} \left[ \begin{array}{c} V_{SIN+} - V_{SIN-} \\ V_{COS+} - V_{COS-} \end{array} \right]$$

For  $\theta = 0.176^{\circ}$  to  $44.824^{\circ}$ :

$$V_{SIN} = Tan\theta \times 0.748 \times V_{BB}$$

$V_{COS} = 0.748 \times V_{BB} \label{eq:VCOS}$

For  $\theta = 45.176^{\circ}$  to  $89.824^{\circ}$ :

$$V_{SIN} = 0.748 \times V_{BB}$$

$$V_{COS} = Tan(90^{\circ} - \theta) \times 0.748 \times V_{BB}$$

#### **Quadrant II**

$$\theta = 180^{\circ} - Tan^{-1} \left[ \frac{V_{SIN+} - V_{SIN-}}{V_{COS+} - V_{COS-}} \right]$$

For  $\theta = 90.176^{\circ}$  to  $134.824^{\circ}$ :

$$V_{SIN} = 0.748 \times V_{BB}$$

$$V_{COS} = -Tan(\theta - 90^{\circ}) \times 0.748 \times V_{BB}$$

For  $\theta = 135.176^{\circ}$  to  $179.824^{\circ}$ :

$$V_{SIN} = Tan(180^{\circ} - \theta) \times 0.748 \times V_{BB}$$

$$V_{COS} = -0.748 \times V_{BB}$$

#### **Quadrant III**

$$\theta = 180^{\circ} + Tan^{-1} \left[ \frac{V_{SIN+} - V_{SIN-}}{V_{COS+} - V_{COS-}} \right]$$

For  $\theta = 180.176^{\circ}$  to 224.824°:

$$V_{SIN} = -Tan(\theta - 180^{\circ}) \times 0.748 \times V_{BB}$$

$$V_{COS} = -0.748 \times V_{BB}$$

For  $\theta = 225.176^{\circ} - 269.824^{\circ}$ :

$$V_{SIN} = -0.748 \times V_{BB}$$

$$V_{COS} = -Tan(270^{\circ} - \theta) \times 0.748 \times V_{BB}$$

#### **Quadrant IV**

$$\theta = 360^{\circ} - Tan^{-1} \left[ \frac{V_{SIN+} - V_{SIN-}}{V_{COS+} - V_{COS-}} \right]$$

For  $\theta = 270.176^{\circ}$  to  $314.824^{\circ}$ :

$$V_{SIN} = -0.748 \times V_{BB}$$

$$V_{COS} = Tan(\theta - 270^{\circ}) \times 0.748 \times V_{BB}$$

For

$$\theta = 315.176^{\circ} - 359.824^{\circ}$$

:

$$V_{SIN} = -Tan(360^{\circ} - \theta) \times 0.748 \times V_{BB}$$

$$V_{COS} = 0.748 \times V_{BB}$$

Graph 1. Major gauge response.

## **Applications Information: continued**

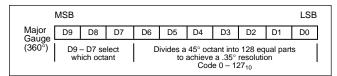

To drive the gauge's pointer to a particular angle, the microcontroller sends a 10-bit digital word into the serial port. These 10 bits are divided as shown in Figure 2. However, from a software programmers viewpoint, a 360° circle is divided into 1024 equal parts of .35° each. Table 1 shows the data associated with the 45° divisions of the 360° driver.

Figure 2. Definition of serial word.

| Input Code<br>(Decimal) | Ideal<br>Degrees | Nominal<br>Degrees | V <sub>SIN</sub> (V) | V <sub>COS</sub> (V) |

|-------------------------|------------------|--------------------|----------------------|----------------------|

| 0                       | 0                | 0.176              | 0.032                | 10.476               |

| 128                     | 45               | 45.176             | 10.476               | 10.412               |

| 256                     | 90               | 90.176             | 10.476               | -0.032               |

| 384                     | 135              | 135.176            | 10.412               | -10.476              |

| 512                     | 180              | 180.176            | -0.032               | -10.476              |

| 640                     | 225              | 225.176            | -10.476              | -10.412              |

| 768                     | 270              | 270.176            | -10.476              | 0.032                |

| 896                     | 315              | 315.176            | -10.476              | 10.412               |

| 1023                    | 359.65           | 359.826            | -0.032               | 10.476               |

Table 1. Nominal output for major gauge ( $V_{BB} = 14V$ ).

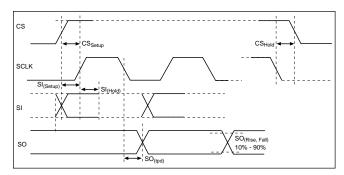

The 10 bits are shifted into the device's shift register MSB first using an SPI compatible scheme. This method is shown in Figure 3. The CS must be high and remain high for SCLK to be enabled. Data on SI is shifted in on the rising edge of the synchronous clock signal. Data in the shift

register changes at SO on the falling edge of SCLK. This arrangement allows the cascading of devices. SO is always enabled. Data shifts through without affecting the outputs until CS is brought low. At this time the internal DAC is updated and the outputs change accordingly.

Figure 3. Serial data timing diagram.

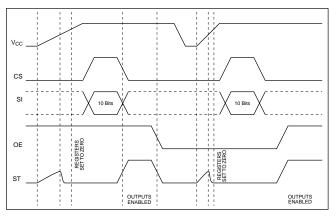

Figure 4. Power-up sequence.

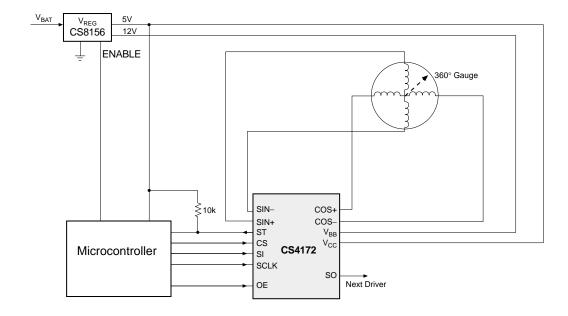

#### **Application Diagram**

## **Package Specification**

## PACKAGE DIMENSIONS IN mm (INCHES)

|                  | D     |       |      |      |

|------------------|-------|-------|------|------|

| Lead Count       | Met   | ric   | Eng  | lish |

|                  | Max   | Min   | Max  | Min  |

| 16 Lead PDIP     | 19.69 | 18.67 | .775 | .735 |

| 16 Lead SO Wide* | 10.50 | 10.10 | .413 | .398 |

| PACKAGE I HERMAL DATA   |                 |                     |      |  |  |

|-------------------------|-----------------|---------------------|------|--|--|

| Thermal<br>Data         | 16 Lead<br>PDIP | 16 Lead<br>SO Wide* |      |  |  |

| $R_{\Theta JC}$ typ     | 42              | 18                  | °C/W |  |  |

| R <sub>OJA</sub> typ 80 |                 | 75                  | °C/W |  |  |

DACKACE THEDMAL DATA

| Ord | orin  | 101 | Im | i o r | ma  | н  | Ωľ | а |

|-----|-------|-----|----|-------|-----|----|----|---|

| Olu | GIIII | ۱ĕ  |    | w     | HIE | 44 | ш  | ч |

| Part Number   | Description                    |

|---------------|--------------------------------|

| CS4172XN16    | 16 Lead PDIP                   |

| CS4172XDWF16  | 16 Lead SO Wide*               |

| CS4172XDWFR16 | 16 Lead SO Wide* (tape & reel) |

\*Internally Fused Leads

ON Semiconductor and the ON Logo are trademarks of Semiconductor Components Industries, LLC (SCILLC). ON Semiconductor reserves the right to make changes without further notice to any products herein. For additional information and the latest available information, please contact your local ON Semiconductor representative.