# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

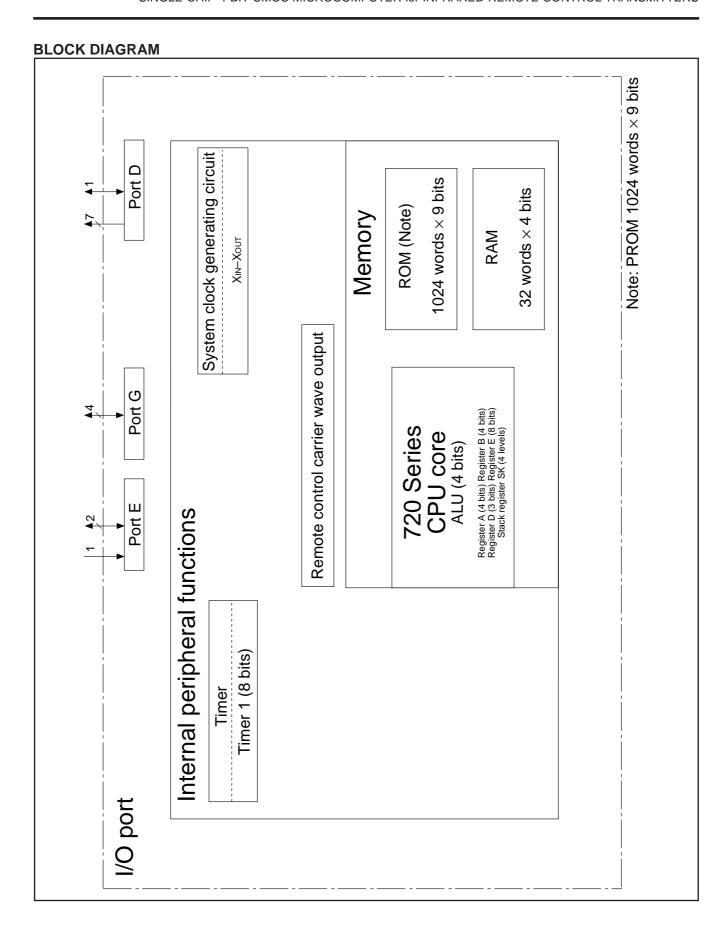

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS

#### **DESCRIPTION**

The 4280 Group is a 4-bit single-chip microcomputer designed with CMOS technology for remote control transmitters. The 4280 Group has 7 carrier waves and enables fabrication of  $8\times7$  key matrix.

## **FEATURES**

- Carrier wave output function (port CARR) f(XIN), f(XIN)/4, f(XIN)/8, f(XIN)/12 f(XIN)/64, f(XIN)/96, "H" output fixed

- Logic operation function (XOR, OR, AND)

- · RAM back-up function

- Oscillation circuit ...... Ceramic resonance

- · Watchdog timer

- · Power-on reset circuit

- Voltage drop detection circuit ...... Typical:1.50 V

### **APPLICATION**

Various remote control transmitters

| Product        | ROM (PROM) size<br>(× 9 bits) | RAM size<br>(× 4 bits) | Package   | ROM type      |

|----------------|-------------------------------|------------------------|-----------|---------------|

| M34280M1-XXXFP | 1024 words                    | 32 words               | 20P2N-A   | Mask ROM      |

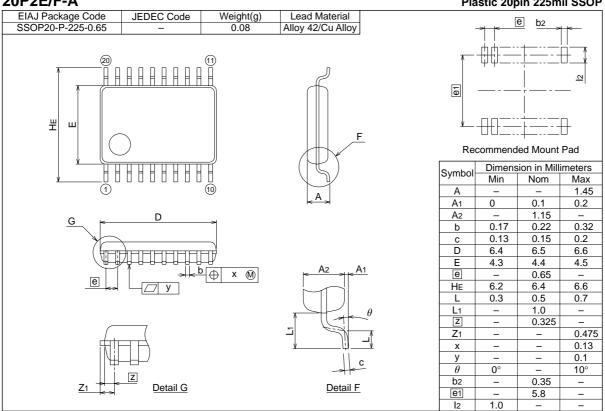

| M34280M1-XXXGP | 1024 words                    | 32 words               | 20P2E/F-A | Mask ROM      |

| M34280E1FP     | 1024 words                    | 32 words               | 20P2N-A   | One Time PROM |

| M34280E1GP     | 1024 words                    | 32 words               | 20P2E/F-A | One Time PROM |

# **PERFORMANCE OVERVIEW**

| Pa                                 | arameter                               |                                           | Function                                                                              |  |  |  |

|------------------------------------|----------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Number of bas                      | ic instruct                            | tions                                     | 62                                                                                    |  |  |  |

| Minimum instruction execution time |                                        | cution time                               | 8.0 μs (at 4.0 MHz system clock frequency)                                            |  |  |  |

|                                    |                                        |                                           | (f(XIN) = 4.0  MHz,  system clock = f(XIN)/8, VDD = 3 V)                              |  |  |  |

| Memory sizes                       | ROM                                    | M34280M1/                                 | 1024 words X 9 bits                                                                   |  |  |  |

|                                    | RAM                                    | E1                                        | 32 words X 4 bits                                                                     |  |  |  |

| Input/Output                       | D0-D6                                  | Output                                    | Seven independent output ports                                                        |  |  |  |

| ports                              | D <sub>7</sub>                         | I/O                                       | 1-bit I/O port with the pull-down function                                            |  |  |  |

|                                    | E0-E2                                  | Input                                     | 3-bit input port with the pull-down function                                          |  |  |  |

|                                    | E <sub>0</sub> , E <sub>1</sub> Output |                                           | 2-bit output port (E <sub>0</sub> , E <sub>1</sub> )                                  |  |  |  |

|                                    | G0-G3 I/O                              |                                           | 4-bit I/O port with the pull-down function                                            |  |  |  |

|                                    | CARR                                   | ARR Output 1-bit output port; CMOS output |                                                                                       |  |  |  |

| Timer 1                            |                                        |                                           | 8-bit timer with a reload register                                                    |  |  |  |

| Subroutine nes                     | sting                                  |                                           | 4 levels (However, only 3 levels can be used when the TABP p instruction is executed) |  |  |  |

| Device structur                    | re                                     |                                           | CMOS silicon gate                                                                     |  |  |  |

| Package                            |                                        |                                           | 20-pin plastic molded SOP (20P2N-A)/SSOP (20P2E/F-A)                                  |  |  |  |

| Operating temp                     | perature r                             | ange                                      | −20 °C to 85 °C                                                                       |  |  |  |

| Supply voltage                     |                                        |                                           | 1.8 V to 3.6 V                                                                        |  |  |  |

| Power Active mode                  |                                        | ode                                       | 400 μΑ                                                                                |  |  |  |

| dissipation                        |                                        |                                           | (f(XIN) = 4.0  MHz,  system clock = f(XIN)/8, VDD = 3  V)                             |  |  |  |

| (typical value)                    | RAM bad                                | ck-up mode                                | 0.1 $\mu$ A (at room temperature, V <sub>DD</sub> = 3 V)                              |  |  |  |

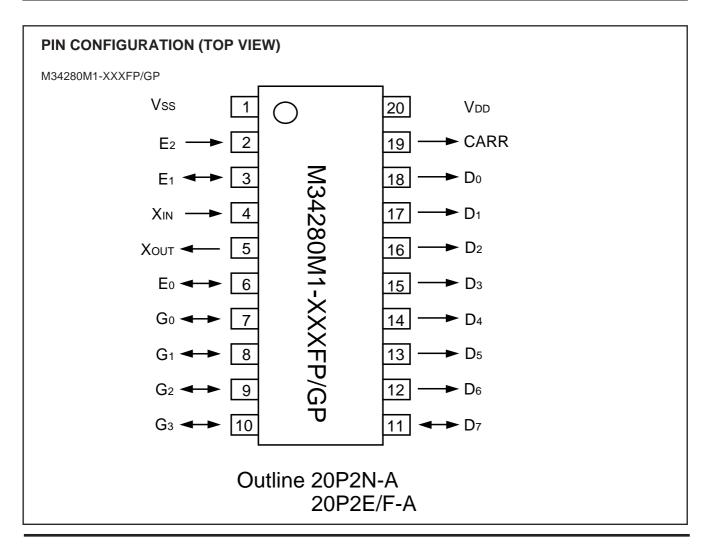

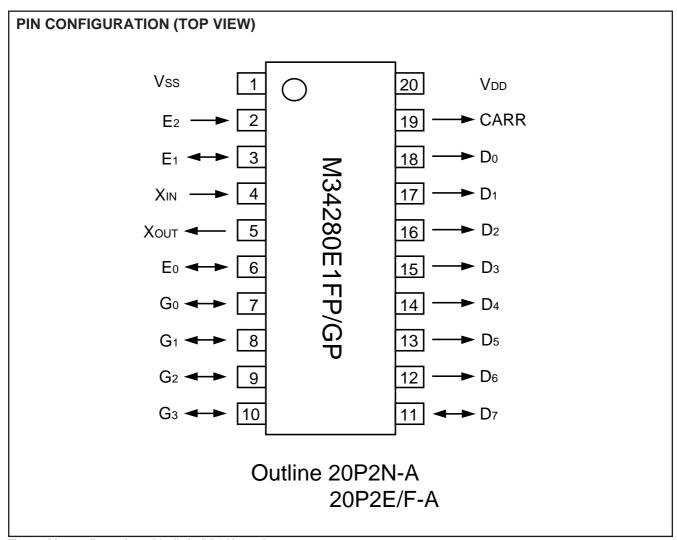

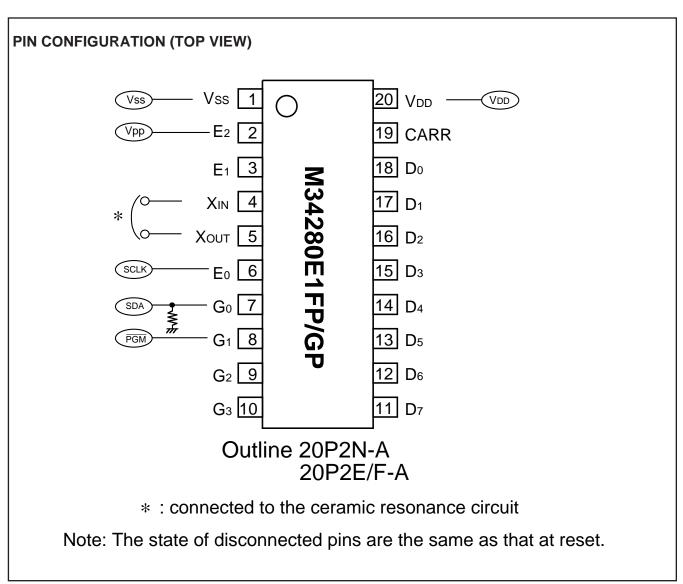

# **PIN DESCRIPTION**

| Pin            | Name                                   | Input/Output | Function                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD            | Power supply                           | _            | Connected to a plus power supply.                                                                                                                                                                                                                                                                                                                                 |

| Vss            | Ground                                 | _            | Connected to a 0 V power supply.                                                                                                                                                                                                                                                                                                                                  |

| XIN            | System clock input                     | Input        | I/O pins of the system clock generating circuit. Connect a ceramic resonator                                                                                                                                                                                                                                                                                      |

| Хоит           | System clock output                    | Output       | between pins XIN and XOUT. The feedback resistor is built-in between pins XIN and XOUT.                                                                                                                                                                                                                                                                           |

| D0-D6          | Output port D                          | Output       | Each pin of port D has an independent 1-bit wide output function. The output structure is P-channel open-drain.                                                                                                                                                                                                                                                   |

| D <sub>7</sub> | I/O port D                             | I/O          | 1-bit I/O port. For input use, turn on the built-in pull-down transistor and set the latch of the specified bit to "0." In addition, key-on wakeup function using "H" level sense becomes valid. The output structure is P-channel open-drain.                                                                                                                    |

| E0-E2          | I/O port E                             | Output       | 2-bit (E <sub>0</sub> , E <sub>1</sub> ) output port. The output structure is P-channel open-drain.                                                                                                                                                                                                                                                               |

|                |                                        | Input        | 3-bit input port. For input use (E <sub>0</sub> , E <sub>1</sub> ), turn on the built-in pull-down transistor and set the latch of the specified bit to "0." In addition, key-on wakeup function using "H" level sense becomes valid. Port E <sub>2</sub> has an input-only port and has a key-on wakeup function using "H" level sense and pull-down transistor. |

| G0-G3          | I/O port G                             | I/O          | 4-bit I/O port. For input use, set the latch of the specified bit to "0." The output structure is P-channel open-drain. Port G has a key-on wakeup function using "H" level sense and pull-down transistor.                                                                                                                                                       |

| CARR           | Carrier wave output for remote control | Output       | Carrier wave output pin for remote control. The output structure is CMOS circuit.                                                                                                                                                                                                                                                                                 |

#### **CONNECTIONS OF UNUSED PINS**

| Pin            | Connection                               |

|----------------|------------------------------------------|

| D0-D7          | Open or connect to VDD pin (Note 1).     |

| E0, E1         | Set the output latch to "1" and open, or |

|                | connect to VDD pin (Note 2).             |

| E <sub>2</sub> | Open or connect to Vss pin.              |

| G0-G3          | Set the output latch to "0" and open, or |

|                | connect to Vss pin.                      |

Notes 1: Port D7: Set the bit 2 (PU02) of the pull-down control register PU0 to "0" by software and turn the pull-down transistor OFF.

2: Set the corresponding bits (PU0<sub>0</sub>, PU0<sub>1</sub>) of the pull-down control register PU0 to "0" by software and turn the pull-down transistor OFF.

(Note in order to set the output latch to "0" to make pins open)

- After system is released from reset, a port is in a high-impedance state until the output latch of the port is set to "0" by software. Accordingly, the voltage level of pins is undefined and the excess of the supply current may occur.

- To set the output latch periodically is recommended because the value of output latch may change by noise or a program run away (caused by noise).

(Note when connecting to Vss and VDD)

• Connect the unused pins to Vss or Vpp at the shortest distance and use the thick wire against noise.

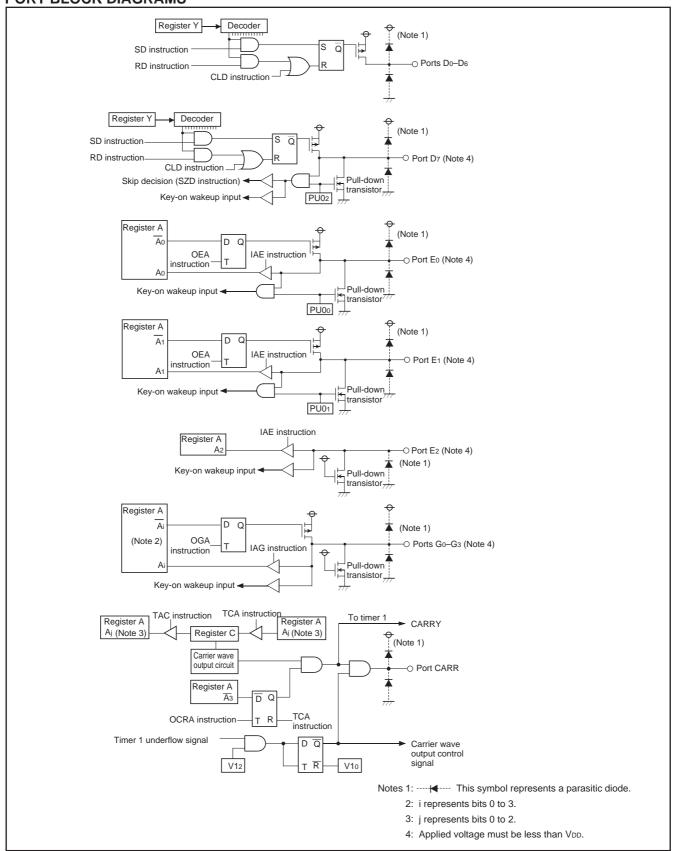

#### PORT FUNCTION

| Port      | Din            | Input/ | Output atmosture     | Control | Control      | Control   | Domonik                       |  |

|-----------|----------------|--------|----------------------|---------|--------------|-----------|-------------------------------|--|

| Fort      | Pin            | Output | Output structure     | bits    | instructions | registers | Remark                        |  |

| Port D    | D0-D6          | Output | P-channel open-drain | 1 bit   | SD           |           |                               |  |

|           |                | (7)    |                      |         | RD           |           |                               |  |

|           |                |        |                      |         | CLD          |           |                               |  |

|           | D <sub>7</sub> | I/O    |                      |         | SD           | PU0       | Pull-down function and key-on |  |

|           |                | (1)    |                      |         | RD           |           | wakeup function               |  |

|           |                |        |                      |         | CLD          |           | (programmable)                |  |

|           |                |        |                      |         | SZD          |           |                               |  |

| Port E    | E <sub>0</sub> | I/O    | P-channel open-drain | Output: | OEA          | PU0       | Pull-down function and key-on |  |

|           | E1             | (2)    |                      | 2 bits  | IAE          |           | wakeup function               |  |

|           |                |        |                      | Input:  |              |           | (programmable)                |  |

|           | E <sub>2</sub> | Input  |                      | 3 bits  | IAE          |           |                               |  |

|           |                | (1)    |                      |         |              |           |                               |  |

| Port G    | G0-G3          | I/O    | P-channel open-drain | 4 bits  | OGA          |           | Pull-down function and key-on |  |

|           |                | (4)    |                      |         | IAG          |           | wakeup function               |  |

|           |                |        |                      |         |              |           |                               |  |

| Port CARR | CARR           | Output | CMOS                 | 1 bit   | OCRA         | С         |                               |  |

|           |                | (1)    |                      |         |              |           |                               |  |

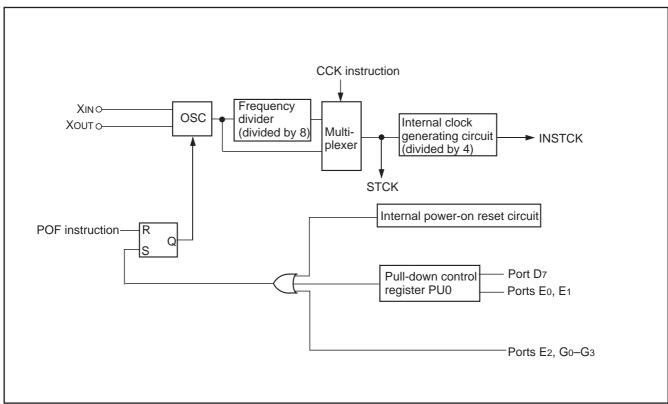

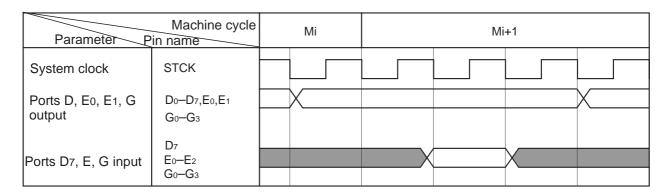

## **DEFINITION OF CLOCK AND CYCLE**

• System clock (STCK)

The system clock is the source clock for controlling this product. It can be selected as shown below whether to use the CCK instruction.

| CCK instruction | System clock | Instruction clock |  |

|-----------------|--------------|-------------------|--|

| When not using  | f(XIN)/8     | f(XIN)/32         |  |

| When using      | f(XIN)       | f(XIN)/4          |  |

• Instruction clock (INSTCK)

The instruction clock is a signal derived by dividing the system clock by 4, and is the basic clock for controlling CPU. The one instruction clock cycle is equivalent to one machine cycle.

• Machine cycle

The machine cycle is the cycle required to execute the instruction.

# **PORT BLOCK DIAGRAMS**

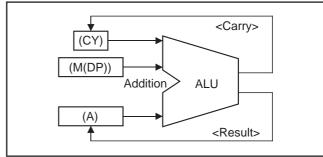

# FUNCTION BLOCK OPERATIONS CPU

## (1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as 4-bit data addition, comparison, and bit manipulation.

#### (2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer, exchange, and I/O operation.

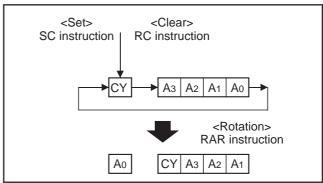

Carry flag CY is a 1-bit flag that is set to "1" when there is a carry with the AMC instruction (Figure 1).

It is unchanged with both A n instruction and AM instruction. The value of Ao is stored in carry flag CY with the RAR instruction (Figure 2).

Carry flag CY can be set to "1" with the SC instruction and cleared to "0" with the RC instruction.

#### (3) Registers B and E

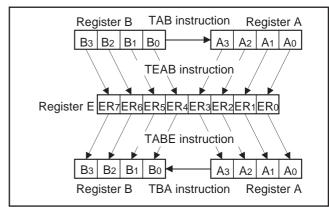

Register B is a 4-bit register used for temporary storage of 4-bit data, and for 8-bit data transfer together with register A. Register E is an 8-bit register. It can be used for 8-bit data transfer with register B used as the high-order 4 bits and register A as the low-order 4 bits (Figure 3).

## (4) Register D

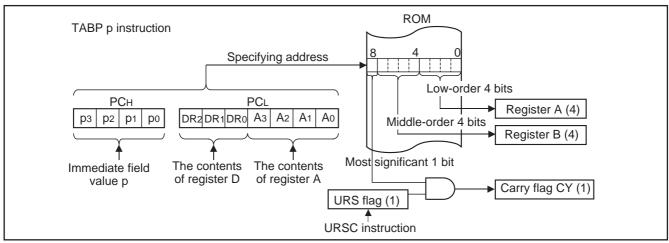

Register D is a 3-bit register.

It is used to store a 7-bit ROM address together with register A and is used as a pointer within the specified page when the TABP p, BLA p, or BMLA p instruction is executed (Figure 4).

Fig. 1 AMC instruction execution example

Fig. 2 RAR instruction execution example

Fig. 3 Registers A, B and register E

Fig. 4 TABP p instruction execution example

#### (5) Most significant ROM code reference enable flag (URS)

URS flag controls whether to refer to the contents of the most significant 1 bit (bit 8) of ROM code when executing the TABP p instruction. If URS flag is "0," the contents of the most significant 1 bit of ROM code is not referred even when executing the TABP p instruction. However, if URS flag is "1," the contents of the most significant 1 bit of ROM code is set to flag CY when executing the TABP p instruction (Figure 4). URS flag is "0" after system is released from reset and returned from RAM back-up mode. It can be set to "1" with the URSC instruction, but cannot be cleared to "0."

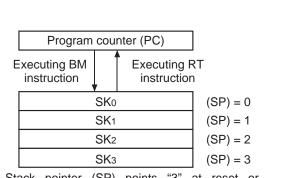

#### (6) Stack registers (SKs) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents of program counter (PC) just before branching until returning to the original routine when;

- · performing a subroutine call, or

- executing the table reference instruction (TABP p).

Stack registers (SKs) are four identical registers, so that subroutines can be nested up to 4 levels. However, one of stack registers is used when executing a table reference instruction. Accordingly, be careful not to over the stack. The contents of registers SKs are destroyed when 4 levels are exceeded.

The register SK nesting level is pointed automatically by 2-bit stack pointer (SP).

Figure 5 shows the stack registers (SKs) structure.

Figure 6 shows the example of operation at subroutine call.

# (7) Skip flag

Skip flag controls skip decision for the conditional skip instructions and continuous described skip instructions.

Note: The 4280 Group just invalidates the next instruction when a skip is performed. The contents of program counter is not increased by 2. Accordingly, the number of cycles does not change even if skip is not performed. However, the cycle count becomes "1" if the TABP p, RT, or RTS instruction is skipped.

Stack pointer (SP) points "3" at reset or returning from RAM back-up mode. It points "0" by executing the first BM instruction, and the contents of program counter is stored in SKo. When the BM instruction is executed after four stack registers are used ((SP) = 3), (SP) = 0 and the contents of SKo is destroyed.

Fig. 5 Stack registers (SKs) structure

Fig. 6 Example of operation at subroutine call

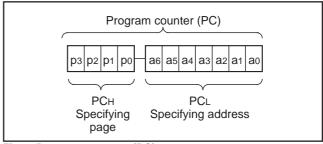

#### (8) Program counter (PC)

Program counter (PC) is used to specify a ROM address (page and address). It determines a sequence in which instructions stored in ROM are read. It is a binary counter that increments the number of instruction bytes each time an instruction is executed. However, the value changes to a specified address when branch instructions, subroutine call instructions, return instructions, or the table reference instruction (TABP p) is executed.

Program counter consists of PC<sub>H</sub> (most significant bit to bit 7) which specifies to a ROM page and PC<sub>L</sub> (bits 6 to 0) which specifies an address within a page. After it reaches the last address (address 127) of a page, it specifies address 0 of the next page (Figure 7).

Make sure that the PC ${\rm H}$  does not exceed after the last page of the built-in ROM.

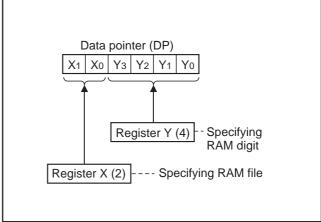

#### (9) Data pointer (DP)

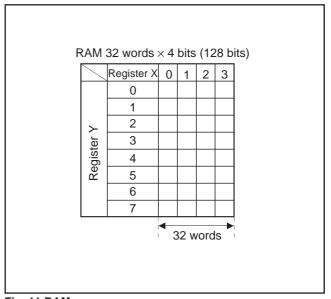

Data pointer (DP) is used to specify a RAM address and consists of registers X and Y. Register X specifies a file and register Y specifies a RAM digit (Figure 8).

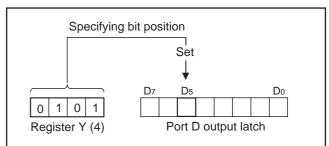

Register Y is also used to specify the port D bit position. When using port D, set the port D bit position to register Y certainly and execute the SD, RD, or SZD instruction (Figure 9).

Fig. 7 Program counter (PC) structure

Fig. 8 Data pointer (DP) structure

Fig. 9 SD instruction execution example

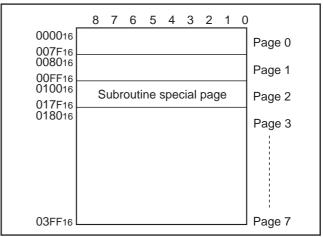

### PROGRAM MEMORY (ROM)

The program memory is a mask ROM. 1 word of ROM is composed of 9 bits. ROM is separated every 128 words by the unit of page (addresses 0 to 127).

Table 1 ROM size and pages

| Product  | ROM size (X 9 bits) | Pages      |  |

|----------|---------------------|------------|--|

| M34280M1 | 1004 words          | 0 (0 to 7) |  |

| M34280E1 | 1024 words          | 8 (0 to 7) |  |

Page 2 (addresses  $0100_{16}$  to  $017F_{16}$ ) is the special page for subroutine calls. Subroutines written in this page can be called from any page with the 1-word instruction (BM). Subroutines extending from page 2 to another page can also be called with the BM instruction when it starts on page 2.

ROM pattern of all addresses can be used as data areas with the TABP p instruction.

# **DATA MEMORY (RAM)**

1 word of RAM is composed of 4 bits, but 1-bit manipulation (with the SB j, RB j, and SZB j instructions) is enabled for the entire memory area. A RAM address is specified by a data pointer. The data pointer consists of registers X and Y. Set a value to the data pointer certainly when executing an instruction to access RAM.

Table 2 shows the RAM size. Figure 12 shows the RAM map.

Table 2 RAM size

| Product  | RAM size                     |

|----------|------------------------------|

| M34280M1 | 22 words V 4 bits (129 bits) |

| M34280E1 | 32 words X 4 bits (128 bits) |

Fig. 10 ROM map of M34280M1

Fig. 11 RAM map

# **TIMERS**

The 4280 Group has the programmable timer.

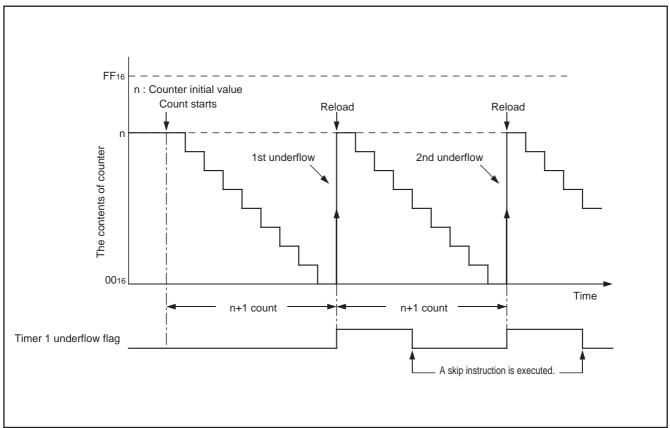

• Programmable timer

The programmable timer has a reload register and enables the frequency dividing ratio to be set. It is decremented from a setting value n. When it underflows (count to n+1), a timer 1 underflow flag is set to "1," new data is loaded from the reload register, and count continues (auto-reload function).

Fig. 12 Auto-reload function

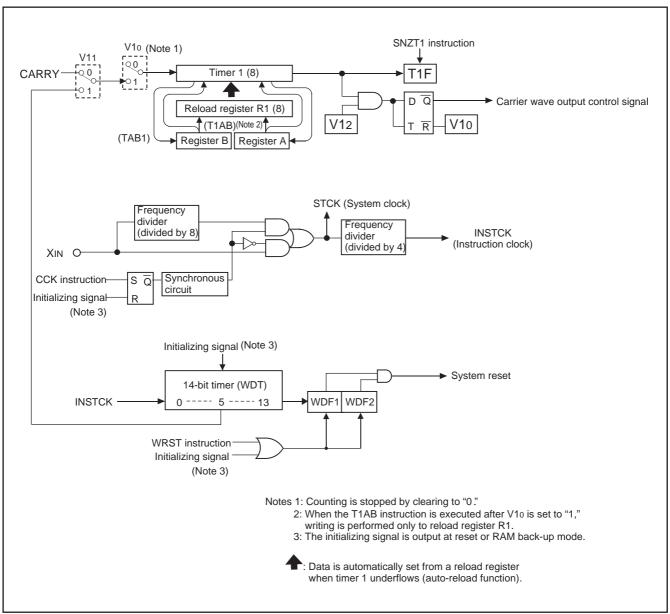

The 4280 Group timer consists of the following circuit.

• Timer 1: 8-bit programmable timer

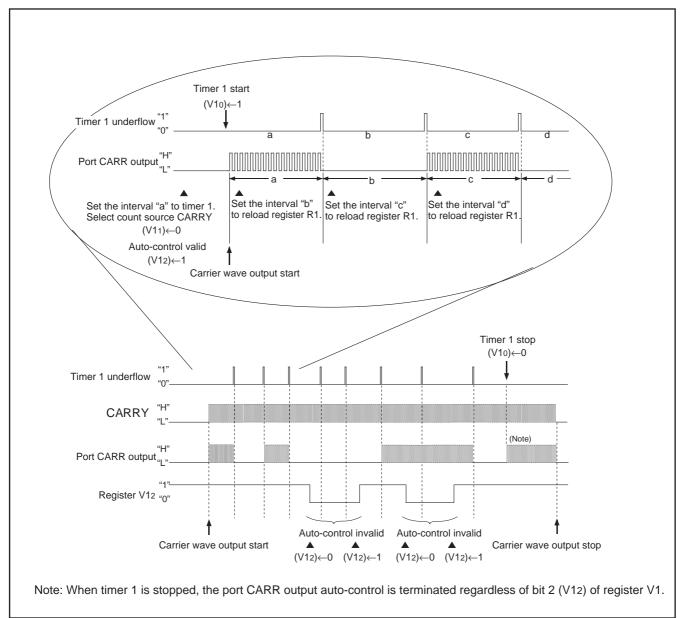

This timer can be controlled with the timer control register V1.

Timer 1 function is described below.

Table 3 Function related timer

| Circuit | Structure           | Count source               | Frequency dividing ratio | Use of output signal        | Control register |

|---------|---------------------|----------------------------|--------------------------|-----------------------------|------------------|

| Timer 1 | 8-bit programmable  | Carrier generating circuit | 1 to 256                 | Carrier wave output control | V1               |

|         | binary down counter | output (CARRY)             |                          |                             |                  |

|         |                     | Bit 5 of watchdog timer    |                          |                             |                  |

Fig. 13 Timers structure

#### Table 4 Control registers related to timer

| Timer control register V1        |                                          | at reset : 0002 |                                           | at RAM back-up : 0002 | W |  |  |

|----------------------------------|------------------------------------------|-----------------|-------------------------------------------|-----------------------|---|--|--|

| VA. Coming output output and hit |                                          | 0               | Auto-control output by timer 1 is invalid |                       |   |  |  |

| V 12                             | V12 Carrier wave output auto-control bit |                 | Auto-control output                       | by timer 1 is valid   |   |  |  |

| \/1.                             | V11 Timer 1 count source selection bit   |                 | Carrier output (CAF                       | RRY)                  |   |  |  |

| V 11                             |                                          |                 | Bit 5 of watchdog ti                      | mer (WDT)             |   |  |  |

| 1/4                              | Timer 4 control bit                      | 0               | Stop (Timer 1 state                       | retained)             |   |  |  |

| V10                              | Timer 1 control bit                      | 1               | Operating                                 |                       |   |  |  |

Note: "W" represents write enabled.

#### (1) Control register related to timer

· Timer control register V1

Register V1 controls the timer 1 count source and autocontrol function of carrier wave output from port CARR by timer 1. Set the contents of this register through register A with the TV1A instruction.

#### (2) Precautions

Note the following for the use of timers.

· Count source

Stop timer 1 counting to change its count source.

· Watchdog timer

Be sure that the timing to execute the WRST instruction in order to operate WDT efficiently.

· Writing to reload register R1

When writing data to reload register R1 while timer 1 is operating, avoid a timing when timer 1 underflows.

### (3) Timer 1

Timer 1 is an 8-bit binary down counter with the timer 1 reload register (R1).

When timer is stopped, data can be set simultaneously in timer 1 and the reload register (R1) with the T1AB instruction.

When timer is operating, data can be set to only reload register R1 with the T1AB instruction.

When setting the next count data to reload register R1 at operating, set data before timer 1 underflows.

Timer 1 starts counting after the following process;

- ① set data in timer 1,

- 2 select the count source with the bit 1 of register V1, and

- 3 set the bit 0 of register V1 to "1."

Once count is started, when timer 1 underflows (the next count pulse is input after the contents of timer 1 becomes "0"), the timer 1 underflow flag (T1F) is set to "1," new data is loaded from reload register R1, and count continues (auto-reload function).

When a value set in reload register R1 is n, timer 1 divides the count source signal by n + 1 (n = 0 to 255).

Data can be read from timer 1 to registers A and B. When reading the data, stop the counter and then execute the TAB1 instruction.

#### (4) Timer 1 underflow flag (T1F)

Timer 1 underflow flag is set to "1" when the timer 1 underflows. The state of this flag can be examined with the skip instruction (SNZT1).

T1F flag is cleared to "0" when the next instruction is skipped with a skip instruction.

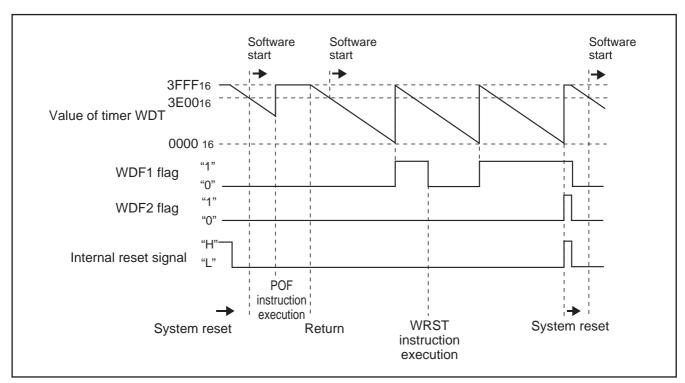

## **WATCHDOG TIMER**

Watchdog timer provides a method to reset and restart the system when a program runs wild. Watchdog timer consists of 14-bit timer (WDT) and watchdog timer flags (WDF1, WDF2).

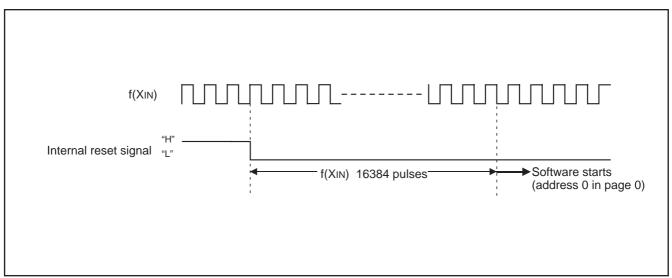

Watchdog timer downcounts the instruction clock (INSTCK) as the count source. When the timer WDT count value becomes 000016 and underflow occurs, the WDF1 flag is set to "1." Then, when the WRST instruction is not executed before the timer WDT counts 16383, WDF2 flag is set to "1" and internal reset signal is generated and system reset is performed.

When using the watchdog timer, execute the WRST instruction at period of 16383 machine cycle or less to keep the microcomputer operation normal.

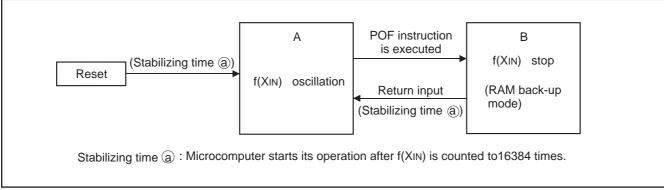

Timer WDT is also used for generation of oscillation stabilization time. When system is returned from reset and from RAM back-up mode by key-input, software starts after the stabilization oscillation time until timer WDT downcounts to 3E0016 elapses.

Fig. 14 Watchdog timer function

#### **CARRIER GENERATING CIRCUIT**

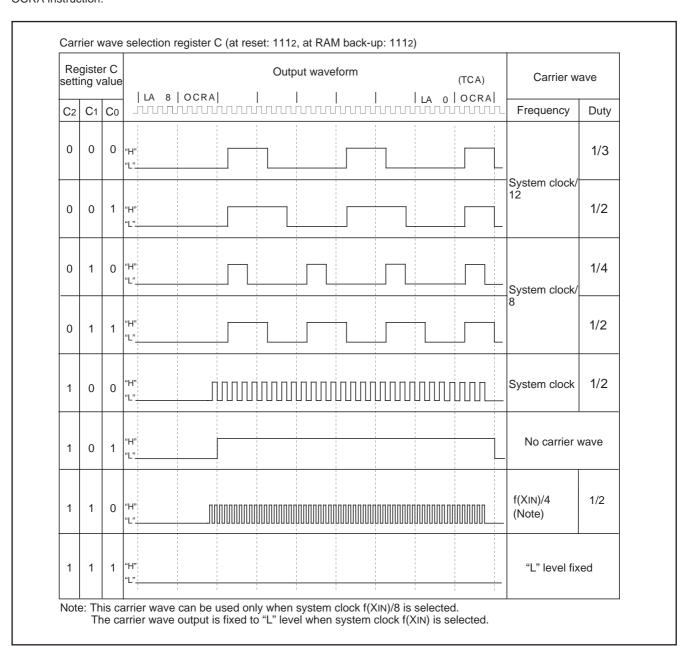

The 4280 Group can output the various carrier waveforms by the carrier wave selection register C.

Set the contents of this register through register A with the TCA instruction. The TAC instruction can be used to transfer the contents of register C to register A. When the TCA instruction is executed, the output latch of port CARR is cleared to "0."

The carrier waveform selected by setting register C can be output from port CARR by setting port CARR output latch to "1." When the CARR output latch is cleared to "0," carrier wave output is stopped and port CARR output is fixed to "L" level. The CARR output latch can be set through bit 3 (A<sub>3</sub>) of register A with the OCRA instruction.

The relationship between the setting value of register C and selected waveform is described below.

Also, timer 1 can auto-control the carrier wave output from port CARR by setting the timer control register V1.

Fig. 15 Carrier wave selection register

Fig. 16 Port CARR output auto-control by timer 1

# **LOGIC OPERATION FUNCTION**

The 4280 Group has the 4-bit logic operation function. The logic operation between the contents of register A and the low-order 4 bits of register E is performed and its result is stored in register A.

Each logic operation can be selected by setting logic operation selection register LO.

Set the contents of this register through register A with the TLOA instruction. The logic operation selected by register LO is executed with the LGOP instruction.

Table 5 shows the logic operation selection register LO.

Table 5 Logic operation selection register LO

| Logic operation selection register LO |                                |   | а               | t reset : 002                      | at RAM back-up : 002     | W |  |

|---------------------------------------|--------------------------------|---|-----------------|------------------------------------|--------------------------|---|--|

|                                       |                                |   | LO <sub>0</sub> |                                    | Logic operation function |   |  |

| LO <sub>1</sub>                       |                                | 0 | 0               | Exclusive logic OR operation (XOR) |                          |   |  |

|                                       | Logic operation selection bits | 0 | 1               | OR operation (OR)                  |                          |   |  |

| LO <sub>0</sub>                       | Do                             |   | 0               | AND operation (AN                  | D)                       |   |  |

|                                       |                                | 1 | 1               | Not available                      |                          |   |  |

Note: "W" represents write enabled.

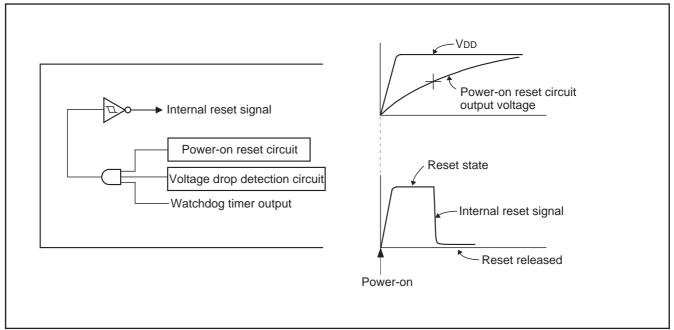

## **RESET FUNCTION**

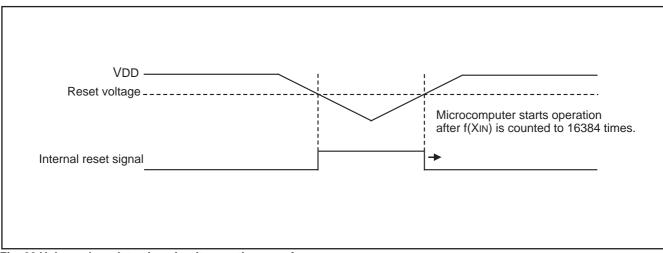

The 4280 Group has the power-on reset circuit, though it does not have  $\overline{\text{RESET}}$  pin. System reset is performed automatically at power-on, and software starts program from address 0 in page 0.

In order to make the built-in power-on reset circuit operate efficiently, set the voltage rising time until VDD=0 to 2.2 V is obtained at power-on 1ms or less.

Fig. 17 Reset release timing

Fig. 18 Power-on reset circuit example

#### (1) Internal state at reset

Table 6 shows port state at reset, and Figure 19 shows internal state at reset (they are retained after system is released from reset).

The contents of timers, registers, flags and RAM except shown in Figure 19 are undefined, so set the initial value to them.

| Program counter (PC)                                  |

|-------------------------------------------------------|

| Address 0 in page 0 is set to program counter.        |

| • Power down flag (P)                                 |

| • Timer 1 underflow flag (T1F)0                       |

| Timer control register V1                             |

| Carrier wave selection register C                     |

| Pull-down control register PU0                        |

| Logic operation selection register LO                 |

| Most significant ROM code reference enable flag (URS) |

| • Carry flag (CY)                                     |

| • Register A                                          |

| • Register B                                          |

| Stack pointer (SP)                                    |

Fig. 19 Internal state at reset

#### Table 6 Port state at reset

| Name           | State at reset                               | State after system is released from reset    |

|----------------|----------------------------------------------|----------------------------------------------|

| D0-D6          | "H" output                                   | High impedance state                         |

| D <sub>7</sub> | "H" output                                   | Input circuit OFF (Pull-down transistor OFF) |

| G0-G3, E2      | Input port (Pull-down transistor ON)         | Input port (Pull-down transistor ON)         |

| E0, E1         | Input circuit OFF (Pull-down transistor OFF) | Input port (Pull-down transistor OFF)        |

Note: The contents of all output latch is initialized to "0."

# **VOLTAGE DROP DETECTION CIRCUIT**

The built-in drop detection circuit is designed to detect a drop in voltage at operating and to reset the microcomputer if the supply voltage drops below the specified value (Typ. 1.50 V) or less.

The voltage drop detection circuit is stopped and power dissipation is reduced at the RAM back-up mode, when the functions except the RAM and pull-down control register (PU0) are initialized.

Fig. 20 Voltage drop detection circuit operation waveform

## **RAM BACK-UP MODE**

The 4280 Group has the RAM back-up mode.

When the POF instruction is executed, system enters the RAM back-up state.

As oscillation stops retaining RAM, the function of reset circuit and states at RAM back-up mode, power dissipation can be reduced without losing the contents of RAM. Table 7 shows the function and states retained at RAM back-up. Figure 21 shows the state transition.

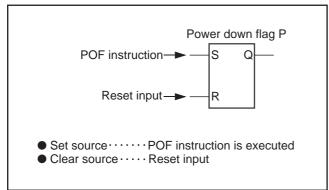

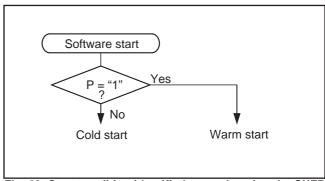

## (1) Identification of the start condition

Warm start (return from the RAM back-up state) or cold start (return from the normal reset state) can be identified by examining the state of the power down flag (P) with the SNZP instruction.

#### (2) Warm start condition

When the external wakeup signal is input after the system enters the RAM back-up state by executing the POF instruction, the CPU starts executing the software from address 0 in page 0. In this case, the P flag is "1."

#### (3) Cold start condition

The CPU starts executing the software from address 0 in page 0 when any of the following conditions is satisfied.

- reset by power-on reset circuit is performed

- reset by watchdog timer is performed

- reset by voltage drop detection circuit is performed In this case, the P flag is "0."

Table 7 Functions and states retained at RAM back-up

| Functi                                        | RAM back-up                    |                   |  |  |

|-----------------------------------------------|--------------------------------|-------------------|--|--|

| Program counter (PC), r                       | ×                              |                   |  |  |

| carry flag (CY), stack po                     | inter (SP) (Note 2)            | ^                 |  |  |

| Contents of RAM                               |                                | 0                 |  |  |

| Ports D <sub>0</sub> -D <sub>6</sub> (Note 3) |                                | X ("H" output)    |  |  |

| Port D <sub>7</sub>                           | (PU02)=0 (Note 3)              | X ("H" output)    |  |  |

| T OIL D7                                      | (PU0 <sub>2</sub> )=1          | X (input)         |  |  |

| Port E <sub>0</sub>                           | (PU0 <sub>0</sub> )=0 (Note 4) | X (input cut-off) |  |  |

| I OIL EO                                      | (PU0 <sub>0</sub> )=1          | X (input)         |  |  |

| Port E <sub>1</sub>                           | (PU01)=0 (Note 4)              | X (input cut-off) |  |  |

| POIL ET                                       | (PU0 <sub>1</sub> )=1          | X (input)         |  |  |

| Port G                                        |                                | X (input)         |  |  |

| Timer control register V                      | 1                              | ×                 |  |  |

| Pull-down control registe                     | er PU0                         | 0                 |  |  |

| Logic operation selection                     | n register LO                  | ×                 |  |  |

| Timer 1 function                              |                                | ×                 |  |  |

| Timer 1 underflow flag (                      | T1F)                           | ×                 |  |  |

| Watchdog timer (WDT)                          | ×                              |                   |  |  |

| Watchdog timer flag 1 (\                      | ×                              |                   |  |  |

| Watchdog timer flag 2 (\                      | ×                              |                   |  |  |

| Most significant ROM code ref                 | erence enable flag (URS)       | X                 |  |  |

- Notes 1: "O" represents that the function can be retained, and "X" represents that the function is initialized.

Registers and flags other than the above are undefined at RAM back-up, and set an initial value after returning.

- 2:The stack pointer (SP) points the level of the stack register and is initialized to "112" at RAM back-up.

- 3: The contents of port output latch is initialized to "0." However, port continues to output "H" level.

- 4: The state of this bit is equal to the state at reset.

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS

#### (4) Return signal

An external wakeup signal is used to return from the RAM back-up mode. Table 8 shows the return condition for each return source.

Table 8 Return source and return condition

| . Return source         | Return condition                | Remarks                                                               |

|-------------------------|---------------------------------|-----------------------------------------------------------------------|

| Ports D7, E0, E1        | Return by an external "H" level | Only key-on wakeup function of the port whose pull-down transistor is |

|                         | input.                          | turned ON is valid.                                                   |

| Ports G, E <sub>2</sub> | Return by an external "H" level | Key-on wakeup function is always valid.                               |

|                         | input.                          |                                                                       |

#### (5) Pull-down control register PU0

Pull-down control register PU0

Register PU0 controls the ON/OFF of pull-down transistor, input, key-on wakeup function of ports E<sub>0</sub>, E<sub>1</sub> and D<sub>7</sub>.

Set the contents of this register through register A with the TPU0A instruction.

Table 9 Pull-down control register

|                  | Pull-down control register PU0            | a | t reset : 0002                                                 | at RAM back-up : state retained       | W          |  |  |  |

|------------------|-------------------------------------------|---|----------------------------------------------------------------|---------------------------------------|------------|--|--|--|

| PU0 <sub>2</sub> | Port D7 pull-down control bit             | 0 | Pull-down transisto                                            | r OFF, input circuit OFF, key-on wake | up invalid |  |  |  |

| PU02             | Port D7 pail-down control bit             | 1 | Pull-down transistor ON, input circuit ON, key-on wakeup valid |                                       |            |  |  |  |

| PU0 <sub>1</sub> | Port E <sub>1</sub> pull-down control bit | 0 | Pull-down transisto                                            | r OFF, key-on wakeup invalid          |            |  |  |  |

| 1001             | Port Er pail-down control bit             | 1 | Pull-down transistor ON, key-on wakeup valid                   |                                       |            |  |  |  |

| PU0 <sub>0</sub> | Port E₀ pull-down control bit             | 0 | Pull-down transisto                                            | r OFF, key-on wakeup invalid          |            |  |  |  |

| 1000             | Port E0 pull-down control bit             | 1 | Pull-down transisto                                            | r ON, key-on wakeup valid             |            |  |  |  |

Note: "W" represents write enabled.

Fig. 21 State transition

Fig. 22 Set source and clear source of the P flag

Fig. 23 Start condition identified example using the SNZP instruction

## **CLOCK CONTROL**

The clock control circuit consists of the following circuits.

- · System clock generating circuit

- · Control circuit to stop the clock oscillation

- Control circuit to return from the RAM back-up state

Fig. 24 Clock control circuit structure

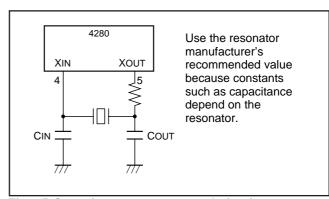

Clock signal f(XIN) is obtained by externally connecting a ceramic resonator. Connect this external circuit to pins XIN and XOUT at the shortest distance as shown Figure 26.

A feedback resistor is built-in between XIN pin and XOUT pin.

## **ROM ORDERING METHOD**

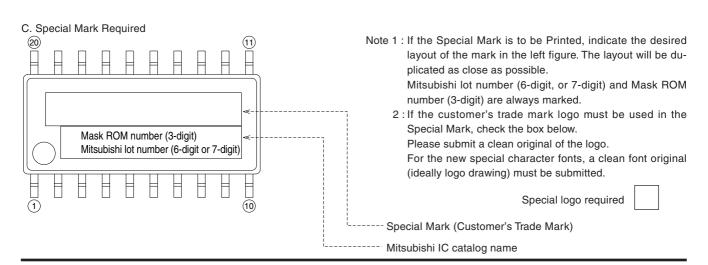

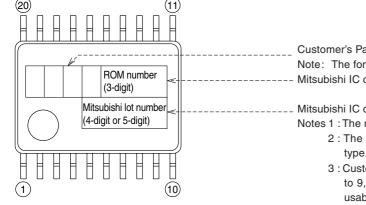

Please submit the information described below when ordering Mask ROM.

- (3) Mark Specification Form ...... 1

Fig. 25 Ceramic resonator external circuit

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS

# **LIST OF PRECAUTIONS**

## Noise and latch-up prevention

Connect a capacitor on the following condition to prevent noise and latch-up;

- connect a bypass capacitor (approx. 0.01 μF) between pins Vpd and Vss at the shortest distance,

- · equalize its wiring in width and length, and

- · use the thickest wire.

In the One Time PROM version, port E2 is also used as VPP pin. Connect this pin to Vss through the resistor about 5 k $\Omega$  which is assigned to E2/VPP pin as close as possible at the shortest distance.

# ② Notes on unused pins

(Note in order to set the output latch to "0" to make pins open)

- After system is released from reset, a port is in a highimpedance state until the output latch of the port is set to "0" by software.

- Accordingly, the voltage level of pins is undefined and the excess of the supply current may occur.

- To set the output latch periodically is recommended because the value of output latch may change by noise or a program run away (caused by noise).

(Note when connecting to Vss and VDD)

Connect the unused pins to Vss and VDD at the shortest distance and use the thick wire against noise.

## 3 Timer

- Count source

- Stop timer 1 counting to change its count source.

- · Watchdog timer

- Be sure that the timing to execute the WRST instruction in order to operate WDT efficiently.

- Writing to reload register R1

When writing data to reload register R1 while timer 1 is operating, avoid a timing when timer 1 underflows.

# Program counter

Make sure that the program counter does not specify after the last page of the built-in ROM.

# **SYMBOL**

The symbols shown below are used in the following list of instruction function and the machine instructions.

| Symbol | Contents                                        | Symbol            | Contents                                      |

|--------|-------------------------------------------------|-------------------|-----------------------------------------------|

| Α      | Register A (4 bits)                             | D                 | Port D (8 bits)                               |

| В      | Register B (4 bits)                             | E                 | Port E (3 bits)                               |

| DR     | Register D (3 bits)                             | G                 | Port G (4 bits)                               |

| ER     | Register E (8 bits)                             | CARR              | Port CARR (1 bit)                             |

| С      | Carrier wave selection register C (3 bits)      |                   |                                               |

| V1     | Timer control register V1 (3 bits)              | x                 | Hexadecimal variable                          |

| PU0    | Pull-down control register PU0 (3 bits)         | у                 | Hexadecimal variable                          |

| LO     | Logic operation selection register LO (2 bits)  | р                 | Hexadecimal variable                          |

|        |                                                 | n                 | Hexadecimal constant which represents the     |

| X      | Register X (2 bits)                             |                   | immediate value                               |

| Υ      | Register Y (4 bits)                             | j                 | Hexadecimal constant which represents the     |

| DP     | Data pointer (6 bits)                           |                   | immediate value                               |

|        | (It consists of registers X and Y)              | A3A2A1A0          | Binary notation of hexadecimal variable A     |

| PC     | Program counter (10 bits)                       |                   | (same for others)                             |

| РСн    | High-order 3 bits of program counter            |                   |                                               |

| PC∟    | Low-order 7 bits of program counter             | ←                 | Direction of data movement                    |

| SK     | Stack register (10 bits X 4)                    | $\leftrightarrow$ | Data exchange between a register and memory   |

| SP     | Stack pointer (2 bits)                          | ?                 | Decision of state shown before "?"            |

| CY     | Carry flag                                      | ( )               | Contents of registers and memories            |

| R1     | Timer 1 reload register                         |                   | Negate, Flag unchanged after executing        |

| T1     | Timer 1                                         |                   | instruction                                   |

| T1F    | Timer 1 underflow flag                          | M(DP)             | RAM address pointed by the data pointer       |

| WDT    | Watchdog timer                                  | а                 | Label indicating address a6 a5 a4 a3 a2 a1 a0 |

| WDF1   | Watchdog timer flag 1                           | р, а              | Label indicating address a6 a5 a4 a3 a2 a1 a0 |

| WDF2   | Watchdog timer flag 2                           |                   | in page p3 p2 p1 p0                           |

| URS    | Most significant ROM code reference enable flag | С                 | Hex. number C + Hex. number x (also same for  |

| Р      | Power down flag                                 | +                 | others)                                       |

| STCK   | System clock                                    | x                 |                                               |

| INSTCK | Instruction clock                               |                   |                                               |

|        |                                                 |                   |                                               |

Note: The 4280 Group just invalidates the next instruction when a skip is performed. The contents of program counter is not increased by 2. Accordingly, the number of cycles does not change even if skip is not performed. However, the cycle count becomes "1" if the TABP p, RT, or RTS instruction is skipped.

# LIST OF INSTRUCTION FUNCTION

| Grouping                      | Mnemonic | Function                                                                          | Grouping             | Mnemonic | Function                                                                                                               | Grouping             | Mnemonic       | Function                                                                      |

|-------------------------------|----------|-----------------------------------------------------------------------------------|----------------------|----------|------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-------------------------------------------------------------------------------|

|                               | TAB      | (A) ← (B)                                                                         |                      | LA n     | (A) ← n                                                                                                                | L C                  | SEAM           | (A) = (M(DP)) ?                                                               |

|                               | ТВА      | (B) ← (A)                                                                         |                      |          | n = 0 to 15                                                                                                            | Comparison operation | SEA n          | (A) = n ?                                                                     |

| nsfer                         | TAY      | $(A) \leftarrow (Y)$                                                              |                      | TABP p   | $(SP) \leftarrow (SP) + 1$<br>$(SK(SP)) \leftarrow (PC)$                                                               | Cor                  | P.o.           | n = 0 to 15                                                                   |

| ster tra                      | TYA      | $(Y) \leftarrow (A)$                                                              |                      |          | $(PCH) \leftarrow p p=0 \text{ to } 7$<br>$(PCL) \leftarrow (DR_2-DR_0, A_3-A_0)$                                      |                      | B a<br>BL p, a | (PCL) ← a6–a0<br>(PCH) ← p                                                    |

| to regi                       | TEAB     | $(ER_7-ER_4) \leftarrow (B)$<br>$(ER_3-ER_0) \leftarrow (A)$                      |                      |          | When URS=0 (B) $\leftarrow$ (ROM(PC))7 to 4                                                                            | eration              | ъс р, а        | (PCL) ← a6–a0                                                                 |

| Register to register transfer | TABE     | $(B) \leftarrow (ER7-ER4)$                                                        |                      |          | $(A) \leftarrow (ROM(PC))3 to 0$<br>When URS=1                                                                         | Branch operation     | BA a           | (PCL) ← (a6–a4, A3–A0)                                                        |

|                               | TDA      | $(A) \leftarrow (ER_3 - ER_0)$ $(DR_2 - DR_0) \leftarrow (A_2 - A_0)$             |                      |          | $(CY) \leftarrow (ROM(PC))8$<br>$(B) \leftarrow (ROM(PC))7 \text{ to } 4$<br>$(A) \leftarrow (ROM(PC))3 \text{ to } 0$ |                      | BLA p, a       | (PCH) ← p<br>(PCL) ← (a6-a4, A3-A0)                                           |

|                               | LXY x, y | $(X) \leftarrow x, x = 0 \text{ to } 3$                                           | ration               |          | $(PC) \leftarrow (SK(SP))$<br>$(SP) \leftarrow (SP) - 1$                                                               |                      | ВМа            | $(SP) \leftarrow (SP) + 1$<br>$(SK(SP)) \leftarrow (PC)$                      |

| esses                         |          | $(Y) \leftarrow y, y = 0 \text{ to } 15$                                          | Arithmetic operation | AM       | $(A) \leftarrow (A) + (M(DP))$                                                                                         |                      |                | $(PCH) \leftarrow 2$<br>$(PCL) \leftarrow a_6-a_0$                            |

| RAM addresses                 | INY      | (Y) ← (Y) + 1                                                                     | \rithme              | AMC      | $(A) \leftarrow (A) + (M(DP))$                                                                                         | ation                | BML p, a       | (SP) ← (SP) + 1                                                               |

| RAI                           | DEY      | (Y) ← (Y) − 1                                                                     |                      |          | + (CY)<br>(CY) ← Carry                                                                                                 | Subroutine operation | • *            | (SK(SP)) ← (PC)<br>(PCH) ← p p= 0 to 7                                        |

|                               | ТАМ ј    | $(A) \leftarrow (M(DP))$<br>$(X) \leftarrow (X) EXOR(j)$                          |                      | A n      | $(A) \leftarrow (A) + n$                                                                                               | routir               |                | (PCL) ← a6–a0                                                                 |

|                               |          | j = 0  to  3                                                                      |                      | /        | n = 0 to 15                                                                                                            | Sub                  | BMLA p,        | $(SP) \leftarrow (SP) + 1$<br>$(SK(SP)) \leftarrow (PC)$                      |

|                               | XAM j    | $(A) \longleftrightarrow (M(DP))$<br>$(X) \leftarrow (X) EXOR(j)$                 |                      | sc       | (CY) ← 1                                                                                                               |                      |                | $(PCH) \leftarrow p p = 0 \text{ to } 7$<br>$(PCL) \leftarrow (a6-a4, A3-A0)$ |

|                               |          | j = 0 to 3                                                                        |                      | RC       | (CY) ← 0                                                                                                               | Ľ                    | RT             | $(PC) \leftarrow (SK(SP))$                                                    |

|                               | XAMD j   | $(A) \longleftrightarrow (M(DP))$ $(X) \longleftrightarrow (X) \to X$ $(X) \to X$ |                      | szc      | (CY) = 0 ?                                                                                                             | operation            |                | (SP) ← (SP) – 1                                                               |

| transfe                       |          | j = 0 to 3<br>$(Y) \leftarrow (Y) - 1$                                            |                      | СМА      | $(A) \leftarrow (\overline{A})$                                                                                        | Return o             | RTS            | $(PC) \leftarrow (SK(SP))$<br>$(SP) \leftarrow (SP) - 1$                      |

| egister                       | XAMI j   | $(A) \longleftrightarrow (M(DP))$                                                 |                      | RAR      |                                                                                                                        | <u>«</u>             |                |                                                                               |

| RAM to register transfer      |          | $(X) \leftarrow (X) \text{ EXOR}(j)$<br>j = 0  to  3<br>$(Y) \leftarrow (Y) + 1$  |                      | LGOP     | Logic operation<br>instruction<br>XOR, OR, AND                                                                         |                      |                |                                                                               |

|                               |          |                                                                                   | u.                   | SB j     | $(Mj(DP)) \leftarrow 1$<br>j = 0  to  3                                                                                |                      |                |                                                                               |

|                               |          |                                                                                   | Bit operation        | RB j     | $(Mj(DP)) \leftarrow 0$<br>j = 0  to  3                                                                                |                      |                |                                                                               |

|                               |          |                                                                                   | Ш                    | SZB j    | (Mj(DP)) = 0 ?<br>j = 0 to 3                                                                                           |                      |                |                                                                               |

# LIST OF INSTRUCTION FUNCTION (CONTINUED)

| Grouping                       | Mnemonic | Function                                                                             | Grouping        | Mnemonic | Function                             |

|--------------------------------|----------|--------------------------------------------------------------------------------------|-----------------|----------|--------------------------------------|

|                                | TV1A     | $(V12-V10) \leftarrow (A2-A0)$                                                       |                 | NOP      | (PC) ← (PC) + 1                      |

|                                | TAB1     | $(B) \leftarrow (T17-T14)$ $(A) \leftarrow (T13-T10)$                                |                 | POF      | RAM back-up                          |

|                                | T4 A D   |                                                                                      |                 | SNZP     | (P) = 1 ?                            |

|                                | T1AB     | at timer 1 stop (V10=0):<br>$(R17-R14) \leftarrow (B)$<br>$(T17-T14) \leftarrow (B)$ | ation           | ССК      | STCK changes to f(XIN)               |

| eration                        |          | $(R13-R10) \leftarrow (A)$ $(R13-R10) \leftarrow (A)$ $(T13-T10) \leftarrow (A)$     | Other operation | TLOA     | $(LO_1, LO_0) \leftarrow (A_1, A_0)$ |

| Timer operation                |          | at timer 1 operating: (V10=1)                                                        | Oth             | URSC     | (URS) ← 1                            |

| F                              |          | $(R17-R14) \leftarrow (B)$ $(R13-R10) \leftarrow (A)$                                |                 | TPU0A    | (PU02−PU00) ← (A2−A0)                |

|                                |          |                                                                                      |                 | WRST     | (WDF1) ← 0                           |

|                                | SNZ1     | (T1F) = 1 ? After skipping the next                                                  |                 |          |                                      |

|                                |          | instruction                                                                          |                 |          |                                      |

|                                |          | (T1F) ← 0                                                                            |                 |          |                                      |

|                                |          | (0.0)                                                                                |                 |          |                                      |

| l u                            | TCA      | $(C_2-C_0) \leftarrow (A_2-A_0)$<br>$(CARR) \leftarrow 0$                            |                 |          |                                      |

| vave<br>erati                  |          | (Ortital) ( O                                                                        |                 |          |                                      |

| Carrier wave control operation | TAC      | $(A_2-A_0) \leftarrow (C_2-C_0)$                                                     |                 |          |                                      |

| Son                            | OCRA     | $(CARR) \leftarrow (A_3)$                                                            |                 |          |                                      |

|                                | CLD      | (D) ← 1                                                                              |                 |          |                                      |

|                                | RD       | (D(Y)) ← 0                                                                           |                 |          |                                      |

|                                |          | (Y) = 0  to  7                                                                       |                 |          |                                      |

|                                | SD       | (D(Y)) ← 1                                                                           |                 |          |                                      |

| tion                           |          | (Y) = 0  to  7                                                                       |                 |          |                                      |

| pera                           | SZD      | (D(Y)) = 0?                                                                          |                 |          |                                      |

| tput o                         |          | (Y) = 7                                                                              |                 |          |                                      |

| Input/Output operation         | OEA      | $(E_1,E_0) \leftarrow (A_1,A_0)$                                                     |                 |          |                                      |

| =                              | IAE      | $(A_2-A_0) \leftarrow (E_2-E_0)$                                                     |                 |          |                                      |

|                                | OGA      | $(G) \leftarrow (A)$                                                                 |                 |          |                                      |

|                                | IAG      | $(A) \leftarrow (G)$                                                                 |                 |          |                                      |

|                                |          |                                                                                      |                 |          |                                      |

# **INSTRUCTION CODE TABLE**

|           | D8-D4 | 00000 | 00001 | 00010    | 00011 | 00100   | 00101   | 00110     | 00111 | 01000 | 01001     | 01010   | 01011    | 01100       | 01101       | 01110       | 01111       | 10000<br>10111 | 11000<br>11111 |

|-----------|-------|-------|-------|----------|-------|---------|---------|-----------|-------|-------|-----------|---------|----------|-------------|-------------|-------------|-------------|----------------|----------------|

| D3-<br>D0 | Hex.  | 00    | 01    | 02       | 03    | 04      | 05      | 06        | 07    | 08    | 09        | 0A      | 0B       | 0C          | 0D          | 0E          | 0F          | 10–17          | 18–1F          |

| 0000      | 0     | NOP   | BLA   | SZB<br>0 | BL    | TAC     | BMLA    | XAM<br>0  | BML   | OGA   | TABP<br>0 | A<br>0  | LA<br>0  | LXY<br>0,0  | LXY<br>1,0  | LXY<br>2,0  | LXY<br>3,0  | ВМ             | В              |

| 0001      | 1     | ВА    | CLD   | SZB<br>1 | BL    | LGOP    | _       | XAM<br>1  | BML   | _     | TABP<br>1 | A<br>1  | LA<br>1  | LXY<br>0,1  | LXY<br>1,1  | LXY<br>2,1  | LXY<br>3,1  | ВМ             | В              |

| 0010      | 2     | _     | l     | SZB<br>2 | BL    | SNZT1   | _       | XAM<br>2  | BML   | URSC  | TABP<br>2 | A<br>2  | LA<br>2  | LXY<br>0,2  | LXY<br>1,2  | LXY<br>2,2  | LXY<br>3,2  | ВМ             | В              |

| 0011      | 3     | SNZP  | INY   | SZB<br>3 | BL    | -       | _       | XAM<br>3  | BML   | -     | TABP<br>3 | A<br>3  | LA<br>3  | LXY<br>0,3  | LXY<br>1,3  | LXY<br>2,3  | LXY<br>3,3  | ВМ             | В              |

| 0100      | 4     | _     | RD    | SZD      | BL    | RT      | _       | TAM<br>0  | BML   | OEA   | TABP<br>4 | A<br>4  | LA<br>4  | LXY<br>0,4  | LXY<br>1,4  | LXY<br>2,4  | LXY<br>3,4  | ВМ             | В              |

| 0101      | 5     | _     | SD    | SEAn     | BL    | RTS     | _       | TAM<br>1  | BML   |       | TABP<br>5 | A<br>5  | LA<br>5  | LXY<br>0,5  | LXY<br>1,5  | LXY<br>2,5  | LXY<br>3,5  | BM             | В              |

| 0110      | 6     | RC    | -     | SEAM     | BL    | ı       | IAE     | TAM<br>2  | BML   | OCRA  | TABP<br>6 | A<br>6  | LA<br>6  | LXY<br>0,6  | LXY<br>1,6  | LXY<br>2,6  | LXY<br>3,6  | ВМ             | В              |

| 0111      | 7     | sc    | DEY   |          | BL    | T1AB    | TAB1    | TAM<br>3  | BML   | _     | TABP<br>7 | A<br>7  | LA<br>7  | LXY<br>0,7  | LXY<br>1,7  | LXY<br>2,7  | LXY<br>3,7  | ВМ             | В              |

| 1000      | 8     |       | _     | IAG      |       |         | TLOA    | XAMI<br>0 | 1     | _     | _         | A<br>8  | LA<br>8  | LXY<br>0,8  | LXY<br>1,8  | LXY<br>2,8  | LXY<br>3,8  | ВМ             | В              |

| 1001      | 9     |       |       | TDA      |       |         | ССК     | XAMI<br>1 |       | _     | _         | A<br>9  | LA<br>9  | LXY<br>0,9  | LXY<br>1,9  | LXY<br>2,9  | LXY<br>3,9  | ВМ             | В              |

| 1010      | А     | AM    | TEAB  | TABE     |       | l       | TCA     | XAMI<br>2 | 1     | ı     | _         | A<br>10 | LA<br>10 | LXY<br>0,10 | LXY<br>1,10 | LXY<br>2,10 | LXY<br>3,10 | ВМ             | В              |

| 1011      | В     | AMC   |       | _        |       | ı       | TV1A    | XAMI<br>3 |       | _     | _         | A<br>11 | LA<br>11 | LXY<br>011  | LXY<br>1,11 | LXY 2,11    | LXY<br>3,11 | ВМ             | В              |

| 1100      | С     | TYA   | СМА   |          |       | RB<br>0 | SB<br>0 | XAMD<br>0 | _     | _     |           | A<br>12 | LA<br>12 | LXY<br>0,12 | LXY<br>1,12 | LXY<br>2,12 | LXY<br>3,12 | ВМ             | В              |

| 1101      | D     | POF   | RAR   | _        |       | RB<br>1 | SB<br>1 | XAMD<br>1 |       | _     |           | A<br>13 | LA<br>13 | LXY<br>0,13 | LXY<br>1,13 | LXY<br>2,13 | LXY<br>3,13 | ВМ             | В              |

| 1110      | Е     | TBA   | TAB   | _        | _     | RB<br>2 | SB<br>2 | XAMD<br>2 |       |       | _         | A<br>14 | LA<br>14 | LXY<br>0,14 | LXY<br>1,14 | LXY<br>2,14 | LXY<br>3,14 | ВМ             | В              |

| 1111      | F     | WRST  | TAY   | SZC      |       | RB<br>3 | SB<br>3 | XAMD<br>3 |       | TPU0A | _         | A<br>15 | LA<br>15 | LXY<br>0,15 | LXY<br>1,15 | LXY<br>2,15 | LXY<br>3,15 | ВМ             | В              |

The above table shows the relationship between machine language codes and machine language instructions. D3–D0 show the low-order 4 bits of the machine language code, and D8–D4 show the high-order 5 bits of the machine language code. The hexadecimal representation of the code is also provided. There are one-word instructions and two-word instructions, but only the first word of each instruction is shown. Do not use the code marked "–."

The codes for the second word of a two-word instruction are described below.

|      |   | The second | word |

|------|---|------------|------|

| BL   | 1 | 1 a a a    | aaaa |

| BML  | 1 | 0 a a a    | aaaa |

| ВА   | 1 | 1 a a a    | aaaa |

| BLA  | 1 | 1 a a a    | Оррр |

| BMLA | 1 | 0 a a a    | Оррр |

| SEA  | 0 | 1011       | nnnn |

| SZD  | 0 | 0010       | 1011 |

**4280 Group**

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS

# MACHINE INSTRUCTIONS

| Parameter                     |          |    |    |                |                | Ir         | nstru      | ıctio          | n co       | de             |   |              |             | o t                | o o o            |                                                                                                                                 |

|-------------------------------|----------|----|----|----------------|----------------|------------|------------|----------------|------------|----------------|---|--------------|-------------|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Type of instructions          | Mnemonic | D8 | D7 | D <sub>6</sub> | D <sub>5</sub> | D4         | Dз         | D <sub>2</sub> | D1         | D <sub>0</sub> |   | ade<br>otati | oimal<br>on | Number of<br>words | Number of cycles | Function                                                                                                                        |

|                               | TAB      | 0  | 0  | 0              | 0              | 1          | 1          | 1              | 1          | 0              | 0 | 1            | Е           | 1                  | 1                | $(A) \leftarrow (B)$                                                                                                            |

| E.                            | ТВА      | 0  | 0  | 0              | 0              | 0          | 1          | 1              | 1          | 0              | 0 | 0            | Е           | 1                  | 1                | (B) ← (A)                                                                                                                       |

| r transf                      | TAY      | 0  | 0  | 0              | 0              | 1          | 1          | 1              | 1          | 1              | 0 | 1            | F           | 1                  | 1                | $(A) \leftarrow (Y)$                                                                                                            |

| egisteı                       | TYA      | 0  | 0  | 0              | 0              | 0          | 1          | 1              | 0          | 0              | 0 | 0            | С           | 1                  | 1                | $(Y) \leftarrow (A)$                                                                                                            |

| Register to register transfer | TEAB     | 0  | 0  | 0              | 0              | 1          | 1          | 0              | 1          | 0              | 0 | 1            | Α           | 1                  | 1                | $(ER_7 - ER_4) \leftarrow (B) \; (ER_3 - ER_0) \leftarrow (A)$                                                                  |

| Regis                         | TABE     | 0  | 0  | 0              | 1              | 0          | 1          | 0              | 1          | 0              | 0 | 2            | Α           | 1                  | 1                | $(B) \leftarrow (ER7-ER4) (A) \leftarrow (ER3-ER0)$                                                                             |

|                               | TDA      | 0  | 0  | 0              | 1              | 0          | 1          | 0              | 0          | 1              | 0 | 2            | 9           | 1                  | 1                | $(DR_2-DR_0) \leftarrow (A_2-A_0)$                                                                                              |

|                               | LXY x, y | 0  | 1  | 1              | <b>X</b> 1     | <b>X</b> 0 | <b>у</b> з | <b>y</b> 2     | <b>y</b> 1 | y <sub>0</sub> | 0 | C<br>+x      |             | 1                  | 1                | $(X) \leftarrow x, x = 0 \text{ to } 3$<br>$(Y) \leftarrow y, y = 0 \text{ to } 15$                                             |

| RAM addresses                 | INY      | 0  | 0  | 0              | 0              | 1          | 0          | 0              | 1          | 1              | 0 | 1            | 3           | 1                  | 1                | (Y) ← (Y) + 1                                                                                                                   |

|                               | DEY      | 0  | 0  | 0              | 0              | 1          | 0          | 1              | 1          | 1              | 0 | 1            | 7           | 1                  | 1                | $(Y) \leftarrow (Y) - 1$                                                                                                        |

|                               | ТАМ ј    | 0  | 0  | 1              | 1              | 0          | 0          | 1              | j1         | jo             | 0 | 6            | 4<br>+j     | 1                  | 1                | $(A) \leftarrow (M(DP))$<br>$(X) \leftarrow (X) EXOR(j)$<br>j = 0  to  3                                                        |

| transfer                      | XAM j    | 0  | 0  | 1              | 1              | 0          | 0          | 0              | j1         | jo             | 0 | 6            | j           | 1                  | 1                | $ \begin{array}{l} (A) \longleftrightarrow (M(DP)) \\ (X) \longleftrightarrow (X) \ EXOR(j) \\ j = 0 \ to \ 3 \end{array} $     |

| RAM to register transfer      | XAMD j   | 0  | 0  | 1              | 1              | 0          | 1          | 1              | j1         | jo             | 0 | 6            | C<br>+j     | 1                  | 1                | $(A) \longleftrightarrow (M(DP))$ $(X) \longleftrightarrow (X) EXOR(j)$ $j = 0 \text{ to } 3$ $(Y) \longleftrightarrow (Y) - 1$ |