# Am100480

16,384 x 1 IMOXTM ECL Bipolar RAM

#### **PRELIMINARY**

### DISTINCTIVE CHARACTERISTICS

- Fast access time (15 ns) improves system cycle speeds.

- Enhanced output voltage level compensation providing 6X (improvement in) V<sub>OL</sub> and V<sub>OH</sub> stability over supply and temperature ranges.

- Internally voltage and temperature compensated providing flat AC performance.

- Fully compatible with 100K series ECL logic no board changes required.

- Emitter follower outputs easy wire-ORing

- Power dissipation decreases with increasing temperature.

## GENERAL DESCRIPTION

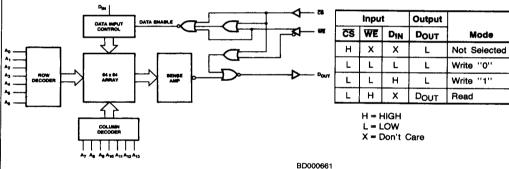

The Am100480-15 and Am100480-25 are fully decoded 16,384-bit ECL RAMs organized 16,384 words by one bit. Bit selection is achieved by means of a 14-bit address,  $A_0$  through  $A_{13}$ . Easy memory expansion is provided by an active LOW chip select ( $\overline{\text{CS}}$ ) input and an unterminated OR tieable emitter follower output.

An active LOW write enable (WE) controls the write/read operation of the memory. When the chip select and write

enable lines are LOW, the data input ( $D_{\mbox{\scriptsize IN}}$ ) is written into the addressed memory word.

Reading is performed with the chip select line LOW and the write enable line HIGH. The information stored in the addressed bit is read out on the noninverting output (DOUT).

During the writing operation, or when the chip select line is HIGH, the output of the memory goes to a LOW state.

## **MODE SELECT TABLE**

#### PRODUCT SELECTOR GUIDE

## Highlights of Key Performance Parameters (Commercial)

| Part Number                                                                                                         | Am 100480-15 | Am100480-25 |

|---------------------------------------------------------------------------------------------------------------------|--------------|-------------|

| Address Access Time (t <sub>AA</sub> )                                                                              | 15 ns        | 25 ns       |

| Write Pulse Width (tw)                                                                                              | 15 ns        | 25 ns       |

| Write Recovery (twn)                                                                                                | 18 ns        | 20 ns       |

| Chip Select Access/<br>Recovery and Write Disable<br>Times (t <sub>ACS</sub> , t <sub>RCS</sub> , t <sub>WS</sub> ) | 8 ns         | 10 ns       |

| Power Supply (I <sub>EE</sub> )                                                                                     | 220 mA       | 200 mA      |

IMOX is a tradement of Advanced Micro Devices, Inc.

Publication # Rev. Amendment

06875 B /0

Issue Date: May 1986

3-49

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65 to +150°C                 |

|-------------------------------------------------|

| Case Temperature with                           |

| Power Applied55 to +125°C                       |

| VEE Pin Potential to GND Pin7.0 V to +0.5 V     |

| Input Voltage (DC)VEE to +0.5 V                 |

| Output Current (DC Output HIGH)30 mA to +0.1 mA |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices (Note 2) |    |        |

|---------------------------------|----|--------|

| Temperature 0                   | to | +85°C  |

| Supply Voltage5.7 V             | to | -4.2 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS V<sub>EE</sub> = -4.5 V, V<sub>CC</sub> = GND (Note 2)

| Parameter<br>Symbol | Parameter<br>Description           | Test Conditions (Note 2)            |                       | B<br>(Note 3) | Typ.<br>(Note 1) | A<br>(Note 3) | Units |

|---------------------|------------------------------------|-------------------------------------|-----------------------|---------------|------------------|---------------|-------|

| Voн                 | Output Voltage HIGH                | VIN = VIHA OF VILB                  | IN # VILLA OF VILD    |               | -955             | -880          | mV    |

| VOL                 | Output Voltage LOW                 | THE THE O' TILB                     | Loading is            | - 1810        | -1715            | - 1620        | mV    |

| Vонс                | Output Voltage HIGH                | VIN = VIHB OF VILA                  | 50 Ω to -2.0 V        | -1035         |                  |               | mV    |

| Volc                | Output Voltage LOW                 | TIN TINE OF TILA                    |                       | - 6           |                  | -1610         | mV    |

| VIH                 | Input Voltage HIGH                 | Guaranteed Input Voltag<br>(Note 4) | e HIGH for All Inputs | -1165         |                  | -880          | mV    |

| VIL                 | Input Voltage LOW                  | Guaranteed Input Veltag<br>(Note 4) |                       | -1810         |                  | -1475         | mV    |

| lн                  | Input Current HIGH                 | Vin WVIHA                           |                       | 1             |                  | 220           | μΑ    |

| L                   | Input Current LOW Chip Select (CS) | V <sub>IN</sub> = V <sub>ILB</sub>  |                       | 0.5           |                  | 170           |       |

| հ <b>ե</b>          | All Other Inputs                   |                                     |                       | -50           |                  |               | μΑ    |

| lee                 | Power Supply                       | All Inputs and                      | Am100480-15           | -220          |                  |               |       |

| JEE .               | Current (Pin 10)                   | Outputs Open                        | Am100480-25           | -200          | -                |               | mA    |

Notes: 1. Typical values are:

- Typical values are:

VEC = -4.5 V, VCC = GND, T<sub>A</sub> = 25°C

Output Load = 50 Ω and 30 pF to -2.0 V, T<sub>A</sub> = 0 to +85°C for DIPs. Guaranteed with transverse air flow exceeding 400 linear F.P.M. and 2-minute warm-up period. Approximate resistance values of the package are:  $\theta_{\rm JA}$  (Junction-to-Ambient) = 90°C/Watt (still air)

- θ<sub>JA</sub> (Junction-to-Ambient) = 50°C/Watt (at 400 F.P.M. air flow)

- TC = 0 to +85°C for Flatpak and LCC packages

θ<sub>JC</sub> (Junction-to-Case) = 25°C/Watt

- Definition of symbols and terms used in this product specification: The relative values of the specified conditions and limits will be referenced to an algebraic scale. The extremities of the scale are: "A" the value closest to positive infinity, "B" the value closest to negative infinity.

These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

|                        |                                         |                                                              |                                                                          | A        | m100480-         | 15       | А           | m100480-         | 25       |       |

|------------------------|-----------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|----------|------------------|----------|-------------|------------------|----------|-------|

| No.                    | Parameter<br>Symbol                     | Parameter<br>Description                                     | Test Conditions                                                          | Min.     | Typ.<br>(Note 1) | Max.     | Min.        | Typ.<br>(Note 1) | Max.     | Unite |

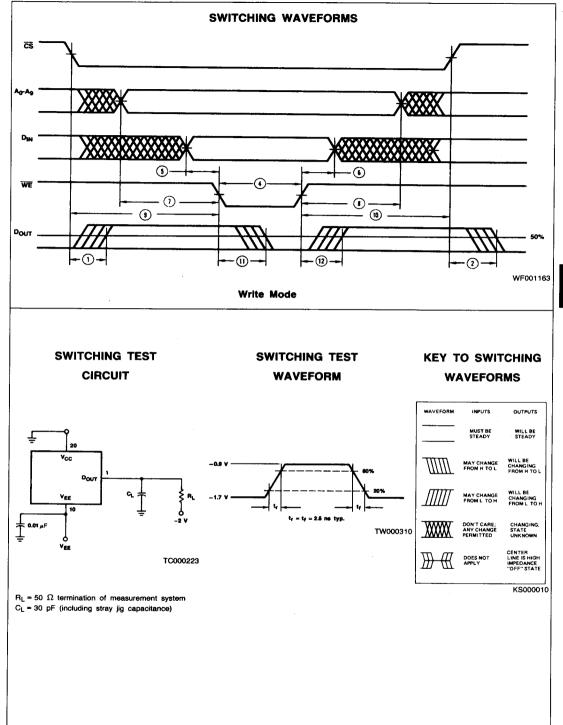

| REA                    | MODE                                    |                                                              |                                                                          |          |                  |          |             |                  |          |       |

| 1                      | t <sub>ACS</sub>                        | Chip Select Access Time                                      | Manager of EON of                                                        |          |                  | 8        |             |                  | 10       |       |

| 2                      | tRCS                                    | Chip Select Recovery Time                                    | Measured at 50% of input to 50% of output                                | ļ        |                  | 8        | ্ৰক্টেপ্টিল | - 107<br>- 107   | 10<br>25 | ns    |

| 3                      | taa                                     | Address Access Time                                          |                                                                          | <u> </u> |                  |          |             |                  |          | ш     |

| VRIT                   | E MODE                                  | 1 D. 1                                                       | ·                                                                        | T        |                  | 100 G    | p. 63636303 | -                | т —      |       |

| 4                      | tw                                      | Write Pulse Width (to Guarantee Writing)                     | twsa = twsa (Min.)                                                       | 15       |                  |          | 25          |                  |          | ns    |

| 5                      | twsp                                    | Data Setup Time<br>Prior to Write                            |                                                                          | 2.       | 4 2 4            | ,        | 5           |                  |          | ns    |

| 6                      | twHD                                    | Data Hold Time<br>After Write                                |                                                                          | .3       |                  |          | 5           |                  |          | ns    |

| 7                      | twsa                                    | Address Setup Time Prior to Write                            | tw = tw (Min.)                                                           | 2        |                  |          | 5           |                  |          | ns    |

| 8                      | twha                                    | Address Hold Time<br>After Write                             |                                                                          | 3        |                  |          | 5           | -                |          | ns    |

| 9                      | twscs                                   | Chip Select Setup Time                                       |                                                                          | 2        |                  |          | 5           |                  |          | ns    |

| 10                     |                                         | Prior to Write Chip Select Hold Time                         | Measured at 50% of                                                       | 3        | -                |          | 5           |                  | <b></b>  | ns    |

|                        | twics                                   | After Write Write Disable Time                               | input to 50% of output                                                   | <u> </u> | <del> </del>     | В        | $\vdash$    |                  | 10       | ns    |

| 11                     | tws                                     | Write Recovery Time                                          | 4                                                                        |          | -                | 18       |             | <del> </del>     | 20       | ns    |

|                        | TIME AND                                |                                                              |                                                                          | I        | <u> </u>         |          |             | I                | <u> </u> |       |

| IISE                   | t <sub>r</sub>                          | Output Rise Time                                             | Measured between                                                         |          | 2.5              | <u> </u> | T .         | 2.5              |          |       |

| 12                     |                                         | Output The Time                                              | 20% and 80% points                                                       |          | <del></del>      |          |             | 2.5              |          | ns    |

|                        |                                         | Output Fall Time                                             | 20% and 60% points                                                       | 1        | 1 2.5            | }        |             |                  |          |       |

| _                      | t <sub>f</sub>                          | Output Fall Time                                             | 20% and 80% points                                                       | l        | 2.5              | l        |             | 2.0              | <u> </u> |       |

| 14<br>CAP              | t <sub>f</sub><br>ACITANCE              |                                                              |                                                                          | I        | ·                |          | <u> </u>    |                  |          |       |

| 14<br>CAP/<br>15       | t <sub>f</sub>                          | Input Pin Capacitance Output Pin Capacitance                 | Measure with a pulse technique on sample basis  TCHING WAVEFO            | DRMS     | 7                | .)       |             | 4 7              |          | pF    |

| 14<br>CAP/<br>15<br>16 | ti ACITANCE CIN COUT                    | Input Pin Capacitance Output Pin Capacitance                 | Measure with a pulse technique on sample basis                           | DRMS     | 7                |          | PORESS L    | 4 7              |          | pF    |

| 14<br>CAP/<br>15<br>16 | tr<br>ACITANCE<br>Cin<br>COUT           | Input Pin Capacitance Output Pin Capacitance SWI             | Measure with a pulse technique on sample basis                           | DRMS     | 7                |          | DORESS L    | 4 7              |          |       |

| 14<br>CAP/<br>15<br>16 | tr ACITANCE CIN COUT  DDRESS AgrAs      | Input Pin Capacitance Output Pin Capacitance SWI             | Measure with a pulse technique on sample basis                           | DRMS     | 7                |          | DORESS      | 4 7              |          | 50%   |

| 14<br>CAP/<br>15<br>16 | ty ACITANCE CIN COUT  COUT  COUT  COUT  | Input Pin Capacitance Output Pin Capacitance  SWI            | Measure with a pulse technique on sample basis  TCHING WAVEFO            | DRMS     | (Cont'd          |          | DORESS L    | 4 7              |          | 50%   |

| 14<br>CAP/<br>15<br>16 | CIN COUT                                | Input Pin Capacitance Output Pin Capacitance  SWI  ADDRESS J | Measure with a pulse technique on sample basis  TCHING WAVEFO  ADDRESS K | DRMS     | (Cont'd          | AC       | DORESS L    | 4 7              |          | 50%   |

| 14<br>CAP/<br>15<br>16 | CS CITANCE  CIN  COUT  COUT  CS  CS  CS | Input Pin Capacitance Output Pin Capacitance  SWI            | Measure with a pulse technique on sample basis  TCHING WAVEFO            | DRMS     | (Cont'd          |          | DORESS L    | 4 7              | ĒΟ       | 50%   |