# Programmable Precision Current Source for Tunable Laser

# **Preliminary Technical Data**

**ADN8810**

**FEATURES**

High Precision 12-Bit Current Source

Low Noise

Long Term Stability

Current Output from 0 mA to 300 mA

Output Fault Indication

Low Drift

Programmable Maximum Current

4 mm × 4 mm Lead Frame Chip Scale Package

3-Wire Serial Interface

APPLICATIONS

Turnable Laser Current Source

Programmable High Output Current Source

### **GENERAL DESCRIPTION**

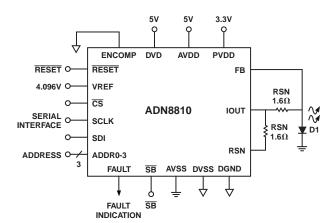

The ADN8810 is a tunable laser controller that provides high precision, low noise current sources and all other control signals needed for tunable laser devices.

The ADN8810 tunable laser controller can drive the Laser section, the Laser Front Mirror, Back Mirror, Phase, Gain or amplification. It interfaces to the host system over a serial interface. The host controls the operation of the controller.

Resolution and accuracy are 12-bits with  $\pm 3$  LSB INL and  $\pm$  LSB DNL. Noise and digital feed through are kept low to ensure low jitter operation. Full scale and scaled output currents are given in Equations 1 and 2, respectively.

$$I_{FS} \approx \frac{V_{REF}}{10 \times R_{SN}}$$

(1)

$$I_{OUT} = Code \times \frac{V_{REF}}{4096} \times \frac{1}{R_{SN}} \times \left(\frac{R_{SN}}{15k} + 0.1\right)$$

(2)

### FUNCTIONAL BLOCK DIAGRAM

\*Protected by U.S.Patent No. 5,969,657; other patents pending.

REV. PrC

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2003

## PRELIMINARY TECHNICAL DATA

# ADN8810-SPECIFICATIONS

# **ELECTRICAL CHARACTERISTICS** (AVDD = DVDD = 5 V, PVDD = 3.3 V, AVSS = DVSS = DGND = 0 V, T<sub>A</sub>= 25°C, covering IOUT from 2% IFS to 100% IFS unless otherwise noted.)

| Parameter                                                                                                                  | Symbol                                                                                         | Condition                                                                    | Min                     | Тур                                  | Max                         | Unit                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------|--------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------|

| DC PERFORMANCE Resolution Relative Accuracy Differential Nonlinearity Offset Offset Gain Error                             | N<br>INL<br>DNL                                                                                |                                                                              |                         | 12<br>4                              | ±3<br>±0.5<br>8<br>15<br>1% | Bit<br>LSB<br>LSB<br>LSB<br>ppm/°C<br>FS                                                                    |

| REFERENCE INPUT Reference Input Voltage Input Impedance Bandwidth                                                          | VREF<br>BWref                                                                                  |                                                                              | 3.9<br>500              | 4.096                                | 4.3<br>2                    | V<br>kΩ<br>MHz                                                                                              |

| ANALOG OUTPUT Output Current Change vs. Output Voltage Change Max Output Current Capacitive Load Output Compliance Voltage | $\begin{array}{c} \Delta I_{OUT}/\Delta V_{OUT} \\ I_{MAX} \\ C_{LFB} \\ V_{COMP} \end{array}$ | $V_{OUT}$ = 0.7 V to 2.0 V $R_{SN1} = R_{SN2} = 1.6 \; \Omega$               | 100                     | 2.5                                  | 250<br>250                  | ppm/V<br>mA<br>pF<br>V                                                                                      |

| AC PERFORMANCE Settling Time Bandwidth Current Noise Density @10 KHz                                                       | τ <sub>S</sub><br>BW<br>i <sub>N</sub>                                                         | $I_{FS} = 250 \text{ mA}$ $I_{FS} = 100 \text{ mA}$ $I_{FS} = 50 \text{ mA}$ |                         | 3<br>5<br>7.5<br>2.5<br>1.25         |                             | $\begin{array}{c} \mu s \\ MHz \\ nA/\sqrt{Hz} \\ nA/\sqrt{Hz} \\ nA/\sqrt{Hz} \\ nA/\sqrt{Hz} \end{array}$ |

| Shutdown Recovery                                                                                                          |                                                                                                |                                                                              |                         | 6                                    |                             | μs                                                                                                          |

| POWER SUPPLY <sup>1</sup> Power Supply Voltage  Power Supply Rejection Ratio Supply Current                                | DVDD<br>AVDD<br>PVDD<br>PSRR<br>I <sub>DVDD</sub><br>I <sub>AVDD</sub><br>I <sub>PVDD</sub>    | $AVDD; PVDD \\ I_O = 0 mA \\ I_O = 0 mA \\ I_O = 0 mA$                       | 3.0<br>4.5<br>3.0<br>60 | 5<br>5<br>3.3<br>80<br>1<br>1.5<br>3 | 5.5<br>5.5<br>3.6           | V<br>V<br>V<br>dB<br>mA<br>mA                                                                               |

| FAULT DETECTION Load Open Threshold Load Short Threshold FAULT Logic Output                                                | $V_{ m OH}$ $V_{ m OL}$                                                                        | DVDD = 5.0 V<br>DVDD = 5.0 V                                                 | 4.5                     | PVDD<br>AVSS+                        |                             | V<br>V<br>V                                                                                                 |

| LOGIC INPUTS Input Leakage Current Input Low Voltage Input High Voltage                                                    | I <sub>IL</sub> V <sub>IL</sub>                                                                | DVDD = 3.0 V<br>DVDD = 5 V<br>DVDD = 3.0 V<br>DVDD = 5 V                     | 2.4                     |                                      | ±1<br>0.5<br>0.8            | μΑ<br>V<br>V<br>V                                                                                           |

| INTERFACE TIMING <sup>2</sup> Clock Frequency RESET Pulse Width                                                            | f <sub>CLK</sub> t <sub>11</sub>                                                               |                                                                              | 20                      |                                      | 25                          | MHz<br>ns                                                                                                   |

NOTES

$^{1}$ With respect to AVSS.

-2- REV. PrC

<sup>&</sup>lt;sup>2</sup>See Timing Characteristics section for timing specifications.

## **ADN8810**

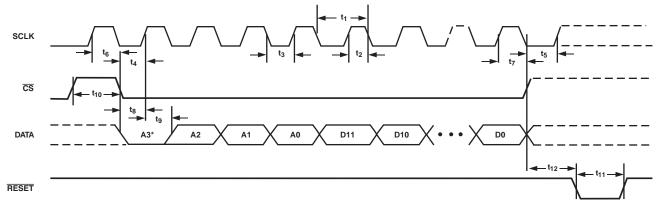

## TIMING CHARACTERISTICS<sup>1,2</sup>

| Parameter       | Description                | Min | Тур | Max | Unit |

|-----------------|----------------------------|-----|-----|-----|------|

| $f_{CLK}$       | SCLK Frequency             |     |     | 25  | MHz  |

| $t_1$           | SCLK Cycle Time            | 40  |     |     | ns   |

| $t_2$           | SCLK Width High            | 20  |     |     | ns   |

| $t_3$           | SCLK Width Low             | 20  |     |     | ns   |

| $t_4$           | CS Low to SCLK High Setup  | 15  |     |     | ns   |

| $t_5$           | CS High to SCLK High Setup | 15  |     |     | ns   |

| $t_6$           | SCLK High to CS Low Hold   | 35  |     |     | ns   |

| $t_7$           | SCLK High to CS High Hold  | 20  |     |     | ns   |

| t <sub>8</sub>  | Data Setup                 | 15  |     |     | ns   |

| $t_9$           | Data Hold                  | 2   |     |     | ns   |

| $t_{10}$        | CS High Pulsewidth         | 30  |     |     | ns   |

| t <sub>11</sub> | RESET Pulsewidth           | 20  |     |     | ns   |

| $t_{12}$        | CS High to RESET Low Hold  | 30  |     |     | ns   |

### NOTES

Specifications subject to change without notice.

Figure 1. Timing Diagram

REV. PrC –3–

<sup>&</sup>lt;sup>1</sup>Guaranteed by design. Not production tested.

<sup>&</sup>lt;sup>2</sup>Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are measured with tr = tf = 5 ns (10% to 90% of DVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

### PRELIMINARY TECHNICAL DATA

### **ADN8810**

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage 6V                               |

|-------------------------------------------------|

| Input Voltage GND to $V_S$ + 0.3V               |

| Output Short-Circuit Duration to GND Indefinite |

| Storage Temperature Range65°C to +150°C         |

| Operating Temperature Range 0°C to +85°C        |

| Junction Temperature Range                      |

| CP Packages                                     |

| Lead Temperature Range (Soldering, 10 sec) TBD  |

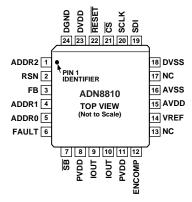

### PIN CONFIGURATION

NC = NO CONNECT

### **ORDERING GUIDE**

| Model      | Temperature Range | Package Description | Package Option |

|------------|-------------------|---------------------|----------------|

| ADN8810ACP | 0°C to +85°C      | 24LEAD LFCSP        | CP-24          |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADN8810 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-4-

## PRELIMINARY TECHNICAL DATA

# ADN8810

### **ADN8810 PIN FUNCTIONS**

| Pin | Name   | Туре           | Description                                                                      |

|-----|--------|----------------|----------------------------------------------------------------------------------|

| 1   | ADDR2  | Digital Input  | Chip address, Bit 2                                                              |

| 2   | RSN    | Analog Input   | Sense resistor RS2 feedback                                                      |

| 3   | FB     | Analog Input   | Sense resistor RS1 feedback                                                      |

| 4   | ADDR1  | Digital Input  | Chip address, Bit 1                                                              |

| 5   | ADDR0  | Digital Input  | Chip address, Bit 0                                                              |

| 6   | FAULT  | Digital Output | Load open/short indication                                                       |

| 7   | SB     | Digital Input  | Active low deactivates output stage (high output impedance state)                |

| 8   | PVDD   | Power          | Power supply for IOUT (3.3V recommended)                                         |

| 9   | IOUT   | Analog Output  | Current output                                                                   |

| 10  | IOUT   | Analog Output  | Current output                                                                   |

| 11  | PVDD   | Power          | Power supply for IOUT (3.3V recommended)                                         |

| 12  | ENCOMP | Digital Input  | Connect to PVDD to enable internal compensation, otherwise connect to AVSS       |

| 13  | NC     |                | No connection                                                                    |

| 14  | VREF   | Analog Input   | Input for high accuracy external reference voltage (ADR292ER)                    |

| 15  | AVDD   | Power          | Power supply for DAC                                                             |

| 16  | AVSS   | Ground         | Connect to analog ground or most negative potential in dual supply applications  |

| 17  | NC     |                | No connection                                                                    |

| 18  | DVSS   | Ground         | Connect to digital ground or most negative potential in dual supply applications |

| 19  | SDI    | Digital Input  | Serial data input                                                                |

| 20  | SCLK   | Digital Input  | Serial clock input                                                               |

| 21  | CS     | Digital Input  | Chip select; active low                                                          |

| 22  | RESET  | Digital Input  | Asynchronous reset to return DAC output to code zero; active low                 |

| 23  | DVDD   | Power          | Power supply for digital interface                                               |

| 24  | DGND   | Ground         | Digital ground                                                                   |

REV. PrC –5–