# MOTOROLA SEMICONDUCTOR EXECUTION TECHNICAL DATA

## Designer's Data Sheet

## **Power Field Effect Transistor**

## N-Channel Enhancement Mode Silicon Gate TMOS

These TMOS Power FETs are designed for high current, high speed power switching applications such as switching regulators, converters, and motor controls.

- IDSS, VDS(on), SOA and VGS(th) Specified at Elevated Temperature

- Rugged -- SOA is Power Dissipation Limited

- High di/dt Capability

- Silicon Gate for Fast Switching Speeds

- Multi-chip Construction

- Gates Internally Decoupled

MTE50N45 MTE50N50 MTE60N35 MTE60N40

TMOS POWER FETS 50 and 60 AMPERES rDS(on) = 0.075 OHM 350 and 400 VOLTS rDS(on) = 0.100 OHM 450 and 500 VOLTS

#### **MAXIMUM RATINGS**

|                                                                   | eet4U.com            |       | M        | TE                      |          | Data!         |

|-------------------------------------------------------------------|----------------------|-------|----------|-------------------------|----------|---------------|

| Rating                                                            | Symbol               | 60N35 | 60N40    | 50N45                   | 45 50N50 | Onit          |

| Drain-Source Voltage                                              | V <sub>DSS</sub>     | 350   | 400      | 450                     | 500      | Vdc           |

| Drain-Gate Voltage (RGS = 1 M $\Omega$ )                          | V <sub>DGR</sub>     | 350   | 400      | 450                     | 500      | Vdc           |

| Gate-Source Voltage                                               | V <sub>GS</sub>      |       | ±        | 20                      |          | Vdc           |

| Drain Current Continuous Pulsed                                   | I <sub>D</sub>       | 1     | 30<br>00 |                         | 50<br>40 | Adc           |

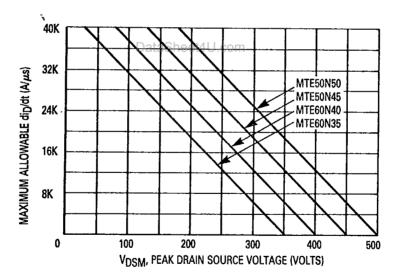

| Turn-Off Rate of Change                                           | di <sub>D</sub> /dt  | Se    |          | and Figure<br>derations | 15       | A/μs          |

| Gate Current — Pulsed                                             | IGM                  |       |          | 2                       |          | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C | PD                   |       | _        | 00<br><b>4</b>          |          | Watts<br>W/°C |

| Operating and Storage Temperature Range                           | TJ, T <sub>stg</sub> | 1     | -65      | to 150                  |          | · °C          |

| Mounting Torque (To heat sink with 10-32 screw)(1)                | τ(m)                 |       |          | 20                      |          | in-lb         |

| Lead Torque (Lead to bus with 1/4-20 screw)(2)                    | τ(Ι)                 |       | :        | 20                      |          | in-lb         |

| Per Unit Weight                                                   | W                    |       | 1        | 20                      |          | grams         |

THERMAL CHARACTERISTICS

| Thermal Resistance Junction to Case        | R <sub>θ</sub> JC | 0.25 | °C/W |

|--------------------------------------------|-------------------|------|------|

| Maximum Lead Temp. for Soldering Purposes, | Tı                | 275  | °C   |

| 1/8" from case for 5 seconds               | '-                |      |      |

1. A Belleville washer of 0.472" O.D., 0.205" I.D., 0.024" thick and 150 pounds flat is recommended.

2. The maximum penetration of the screw should be limited to 0.75".

TMOS and Designers are trademarks of Motorola Inc.

### WWW ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                     |                                                                         | Symbol               | Min                                   | Max                    | Unit        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------|---------------------------------------|------------------------|-------------|--|

| OFF CHARACTERISTICS                                                                                                                                |                                                                         |                      |                                       |                        |             |  |

| Drain-Source Breakdown Volta<br>(VGS = 0, ID = 5 mA)                                                                                               | age<br>MTE60N35<br>MTE60N40<br>MTE50N45<br>MTE50N50                     | V <sub>(BR)DSS</sub> | 350<br>400<br>450<br>500              | _<br>_<br>_            | Vdc         |  |

| Zero Gate Voltage Drain Curre<br>(VDS = 0.85 Rated VDSS, V<br>(TJ = 100°C)                                                                         |                                                                         | IDSS                 | _                                     | 0.25<br>2.5            | mAdc        |  |

| Gate-Body Leakage Current (VGS = 20 Vdc, VDS = 0)                                                                                                  |                                                                         | IGSS                 | <del>_</del>                          | 500                    | nAdc        |  |

| N CHARACTERISTICS*                                                                                                                                 |                                                                         |                      |                                       |                        | <del></del> |  |

| Gate Threshold Voltage<br>(ID = 1 mA, VDS = VGS)<br>(TJ = 100°C)                                                                                   |                                                                         | V <sub>GS(th)</sub>  | 2<br>1.5                              | 4.5<br>4               | Vdc         |  |

| Static Drain-Source On-Resista<br>$(V_{GS} = 10 \text{ Vdc}, I_D = 30 \text{ Ad}$<br>$(V_{GS} = 10 \text{ Vdc}, I_D = 25 \text{ Ad}$               | c) MTE60N35/40                                                          | rDS(on)              | <u> </u>                              | 0.075<br>0.100         | Ohms        |  |

| Drain-Source On-Voltage (VGS ( $I_D = 60$ Adc) ( $I_D = 30$ Adc, $T_J = 100^{\circ}$ C) ( $I_D = 50$ Adc) ( $I_D = 25$ Adc, $T_J = 100^{\circ}$ C) | MTE60N35/40<br>MTE60N35/40<br>MTE60N35/40<br>MTE50N45/50<br>MTE50N45/50 | V <sub>DS(on)</sub>  | _<br>_<br>_<br>_                      | 4.5<br>3.5<br>5.2<br>5 | Vdc         |  |

| Forward Transconductance ( $V_{DS} = 15 \text{ V}$ , $I_{D} = 30 \text{ A}$ ) ( $V_{DS} = 15 \text{ V}$ , $I_{D} = 25 \text{ A}$ )                 | MTE60N35/40<br>MTE50N45/50                                              | 9fs                  | 16<br>20                              |                        | mhos        |  |

| OYNAMIC CHARACTERISTICS                                                                                                                            |                                                                         |                      |                                       |                        |             |  |

| Input Capacitance                                                                                                                                  |                                                                         | Ciss                 | _                                     | 12,000                 | pF          |  |

| Output Capacitance                                                                                                                                 | (V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0efa=11eMHz).o               | <del></del>          | _                                     | 2,000                  | Data        |  |

| Reverse Transfer Capacitance                                                                                                                       |                                                                         | C <sub>rss</sub>     |                                       | 800                    |             |  |

| SWITCHING CHARACTERISTICS                                                                                                                          | * (T <sub>J</sub> = 100°C)                                              |                      |                                       |                        |             |  |

| Inductive Load, Clamped — M                                                                                                                        | TE60N35 and MTE60N40                                                    |                      |                                       |                        |             |  |

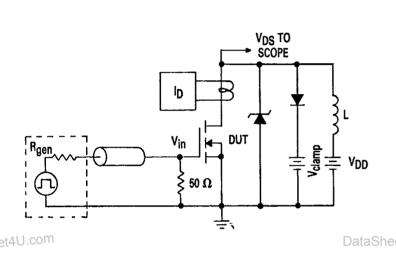

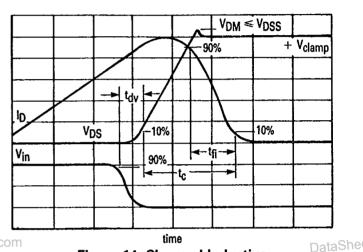

| Turn-Off Delay Time                                                                                                                                | (V <sub>clamp</sub> = 200 Vdc, I <sub>D</sub> = 30 Adc,                 | tdv                  | · · · · · · · · · · · · · · · · · · · | 1,300                  | ns          |  |

| Crossover Time                                                                                                                                     | $L = 25 \mu H, V_{in} = 10 \text{ Vdc}$                                 | t <sub>c</sub> —     |                                       | 325                    |             |  |

| Current Fall Time                                                                                                                                  | $R_{gen} = 50 \Omega$ ) See Figures 13 and 14                           | t <sub>fi</sub>      |                                       | 200                    |             |  |

| Inductive Load, Clamped — M                                                                                                                        | TE50N45 and MTE50N50                                                    |                      |                                       |                        |             |  |

| Turn-Off Delay Time                                                                                                                                | (V <sub>clamp</sub> = 250 Vdc, I <sub>D</sub> = 25, Adc,                | t <sub>dv</sub>      | _                                     | 1,300                  | ns          |  |

| Crossover Time                                                                                                                                     | $L = 25 \mu H, V_{in} = 10 \text{ Vdc}$                                 | t <sub>C</sub>       |                                       | 300                    |             |  |

|                                                                                                                                                    |                                                                         |                      |                                       |                        |             |  |

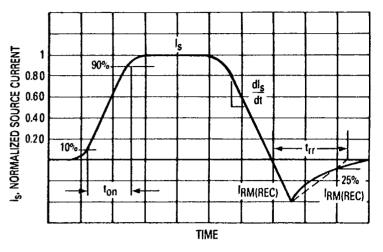

Reverse Recovery Time \*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2%.

**SOURCE-DRAIN DIODE CHARACTERISTICS\***

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc is an Equal Employment Opportunity/ Affirmative Action Employer.

$R_{gen} = 50 \Omega$ ) See Figures 13 and 14

(Is = Rated ID,  $V_{GS} = 0$ )

See Figures 15 and 16.

tfi

**Symbol**

**VSD**

ton

trr

**Current Fall Time**

Forward On-Voltage

Forward Turn-On Time

200

**Typical**

2

350

2,000

Unit

Vdc

ns

ns

et4U

#### TYPICAL CHARACTERISTICS

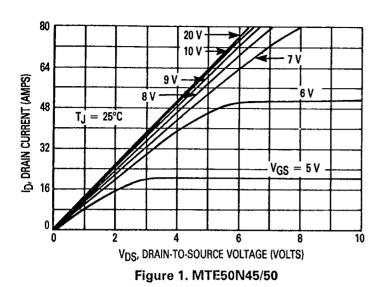

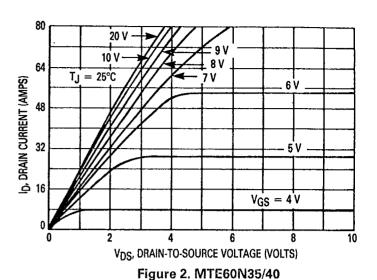

#### **ON-REGION CHARACTERISTICS**

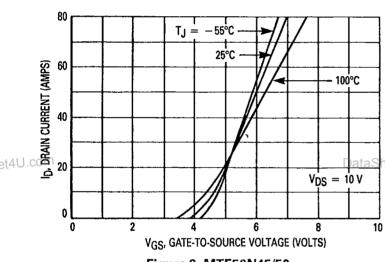

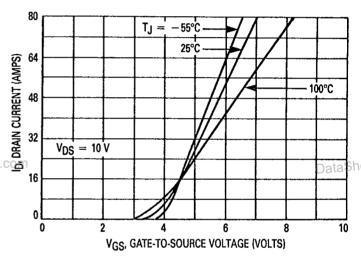

#### TRANSFER CHARACTERISTICS

Figure 3. MTE50N45/50

Figure 4. MTE60N35/40

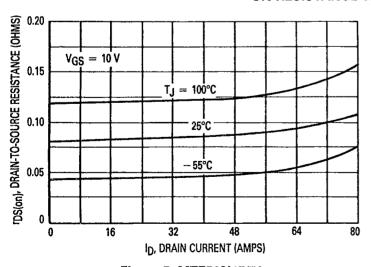

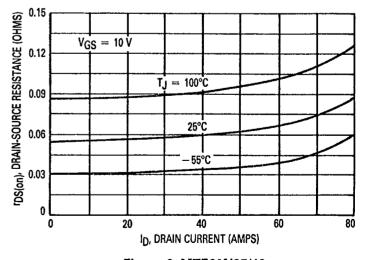

#### **ON-RESISTANCE versus DRAIN CURRENT**

Figure 5. MTE50N45/50

Figure 6. MTE60N35/40

#### TYPICAL CHARACTERISTICS

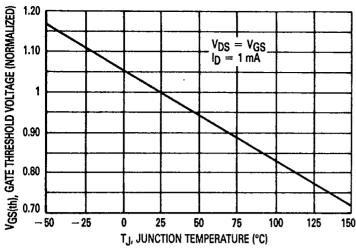

Figure 7. Gate-Threshold Voltage Variation with Temperature

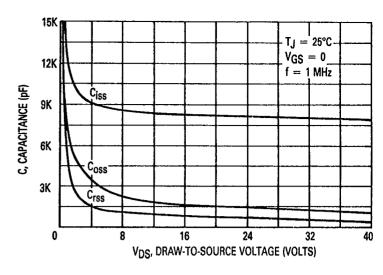

Figure 8. Capacitance Variation

#### SAFE OPERATING AREA INFORMATION

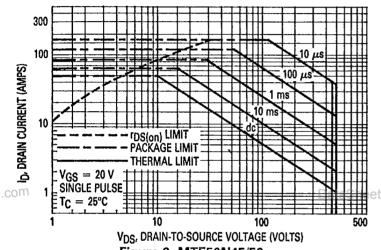

Figure 9. MTE50N45/50

Maximum Rated Forward Biased

Safe Operating Area

V<sub>DS</sub>, DRAIN-TO-SOURCE VOLTAGE (VOLTS)

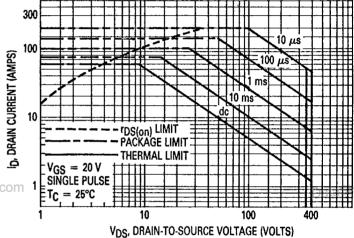

Figure 10. MTE60N35/40

Maximum Rated Forward Biased

Safe Operating Area

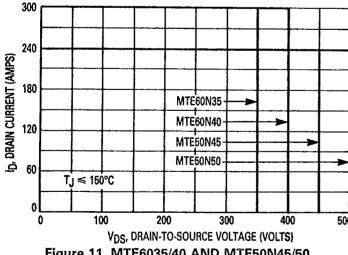

Figure 11. MTE6035/40 AND MTE50N45/50 Maximum Rated Switching Safe Operating Area

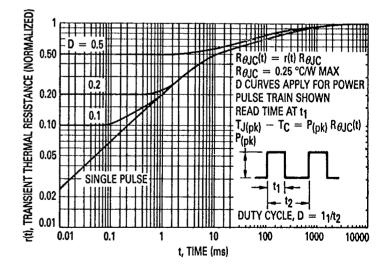

Figure 12. Thermal Response

MTE50N45 • MTE50N50 • MTE60N351 & MTE60N401

#### **GUARANTEED SAFE OPERATING AREA**

The dc data presented in Figures 9 and 10 is for a single pulse, applied while maintaining the case temperature T<sub>C</sub> at 25°C. For multiple pulses and case temperatures other than 25°C, the dc drain current at a case temperature of 25°C should be de-rated as follows:

$$I_D(T) = I_D (25^\circ) \left[ \frac{150 - T_C}{P_D \cdot R_{\theta JC} \cdot r(t)} \right]$$

where P<sub>D</sub> is the maximum power rating at 25°C, R<sub>BJC</sub> is the junction-to case thermal resistance, and r(t) is the normalized thermal response from Figure 15, corresponding to the appropriate pulse width and duty cycle.

EXAMPLE: Determine the maximum allowable drain current for an MTE50N50 at 25 volts drain voltage, with a pulse width of 10 ms and duty cycle of 50%, at a case temperature of 80°C.

From Figure 9, the dc drain current at  $V_{DS}=25$  volts is 20 A. For a 10 ms pulse and duty cycle of 50%, Figure 12 gives an r(t) of 0.6; then, with  $P_{D}=500$  watts at 25°C and  $R_{\theta JC}=0.5$ °C/W.

$$I_D = 20 \times \frac{150 - 80}{500 \times 0.25 \times 0.6} = 18.6 \text{ A}$$

The switching safe operating area in Figure 11 is the boundary that the load line may traverse without incurring damage to the device. The fundamental limits are the maximum rated peak drain current I<sub>DM</sub>, the minimum drain-to-source breakdown voltage V<sub>BR(DSS)</sub> and the maximum rated junction temperature. The boundaries are applicable for both turn-on and turn-off of the devices for rise and fall times of less than one microsecond.

Figure 13. Inductive Load Switching Circuit

Figure 14. Clamped Inductive Load Switching Waveforms

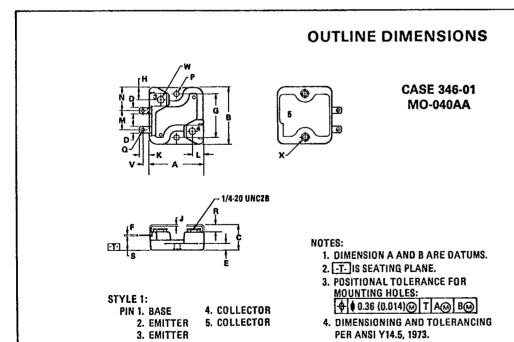

|     | MILLIMETERS |       | INCHES    |       |  |

|-----|-------------|-------|-----------|-------|--|

| DIM | MIN         | MAX   | MIN       | MAX   |  |

| Α   | 53.09       | 53.84 | 2.090     | 2.120 |  |

| В   | 55.37       | 56.39 | 2.180     | 2.220 |  |

| C   |             | 26.67 | -         | 1.050 |  |

| D   | 6.10        | 6.60  | 0.240     | 0.260 |  |

| E   | 6.60        | 7.11  | 0.260     | 0.280 |  |

| F   | 0.71        | 0.81  | 0.028     | 0.032 |  |

| G   | 43.31       | BSC   | 1.705 BSC |       |  |

| H   | 12.57       | 12.82 | 0.495     | 0.505 |  |

| J   | 1.52        | 1.62  | 0.060     | 0.064 |  |

| K   | 9.50        | 9.75  | 0.374     | 0.384 |  |

| اد  | 10.21       | 10.46 | 0.402     | 0.412 |  |

| М   | 18.92       | 19.18 | 0.745     | 0.755 |  |

| N   | 23.67       | 23.93 | 0.932     | 0.942 |  |

| P   | 5.08        | 5.21  | 0.200     | 0.205 |  |

| Q   | 3.53        | 3.78  | 0.139     | 0.149 |  |

| R   | 6.76        | 7.26  | 0.266     | 0.286 |  |

| S   | 14.73       | 15.24 | 0.580     | 0.600 |  |

| V   | 5.33        | 5.84  | 0.210     | 0.230 |  |

| W   | 6.40        | 6.65  | 0.252     | 0.262 |  |

| X   | 7.37        | 7.87  | 0.290     | 0.310 |  |

ww.DataSheet4U.cor

## CONSIDERATION IN DESIGNING WITH POWER MOSFETS

Depending on the frequency of operation, certain precautions must be taken to insure optimum reliability. When switching near the device maximum frequency, the high current and very fast switching capability of this device necessitates the use of the following protective measures:

- Note 1 As in any wideband circuit, good RF layout techniques must be maintained, i.e., short lead lengths, adequate ground planes and decoupled power supplies.

- Note 2 All overvoltage protection circuitry free wheeling diodes, zeners, MOVs, snubber networks—should be placed directly between the drain-source or between the drain and a good, low inductance ac ground.

- Note 3 Since most "real world" loads are inductive, the fast turn-off peak flyback voltage (e = L di/dt) must not exceed the VBR(DSS) rating, an instantaneous voltage limit. The protective circuitry, including parasitics, must have response times commensurate with the Power MOSFET switching speed, e.g., rectifiers must have very short recovery times. The forward

- recovery time  $t_{fr}$ , overshoot voltage  $V_{FM}(DYN)$  and reverse recovery time  $t_{rr}$  should be low to minimize the switching stress on the transistor.

- Note 4 Even with good RF layout and ideal clamping below the maximum V(BR)DSS of the device, significant potentials may be generated across the package drain and source parasitic inductances during rapid turn off of a large magnitude of current. These induced voltages which are internal to the package add to the clamp voltage. Therefore, to protect the chips from excessive voltage, the dip/dt must be limited in accordance to the peak voltage seen across the terminals of the device. The MAXIMUM ALLOWABLE dip/dt must be limited in accordance to the peak VDS appearing at the device terminals as shown in Figure 15.

For applications requiring slower switching speeds, increasing the gate drive impedance will increase the switching times. This can be accomplished by adding a resistor in series with the gate.

et4U.com

Figure 15. Maximum Allowable dip/dt versus Drain Source Voltage

DataShe

www.DataSheet4U.com

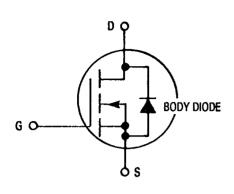

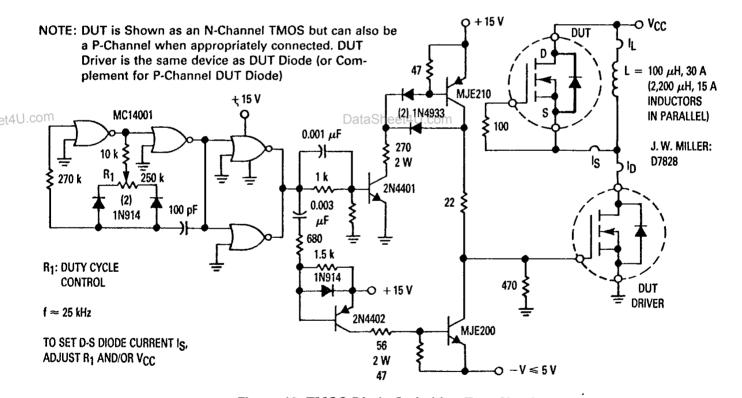

#### TMOS SOURCE-TO-DRAIN CHARACTERISTICS

In the fabrication of a TMOS FET, a diode is formed across the source-to-drain terminals as shown in Figure 16. Reversal of the drain voltage will cause current flow in the reverse direction. This diode may be used in circuits

requiring external fast recovery diodes, therefore, typical characteristics of the on voltage, forward turnon and reverse recovery times are given.

Figure 16. TMOS FET With Source-To-Drain Diode

Figure 17. Diode Switching Waveform

Figure 18. TMOS Diode Switching Test Circuit

www.DataSheet4U.com

DataSheet4U.com