#### **FEATURES**

- Access time as low as 150 ns max

- Cycle time as low as 350 ns max

- Static—no refresh required

- TTL Compatible Inputs/Outputs

- On Chip Address Register

- 1Kx4 Organization Ideal for Microprocessor Applications

- Low Operating Power 450 mw typ

- Low Standby Power 35mw typ

- Data Retention Mode, V<sub>DD</sub>= 4V; V<sub>BB</sub> = -4V

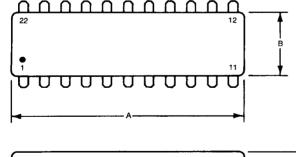

- Standard 22 pin dip

- Non-inverted Data Output

- Voltage Compatible with Popular Microprocessors

Name of the state of the state

#### **GENERAL DESCRIPTION**

The SEMI 4104

is an N-Channel MOS Random Access Memory,

organized as 1024 words by four bits. It uses a fully static memory cell which eliminates the need for any refresh or charge pump circuitry. All inputs can be driven by standard TTL devices and the three state data output can directly drive one TTL load of any type.

The Chip Select input provides for simple memory expansion and low system power, by putting unselected devices into a high output impedance and low power state. For additional power savings VDD and VBB can be reduced significantly, thus allowing data to be retained economically under battery power.

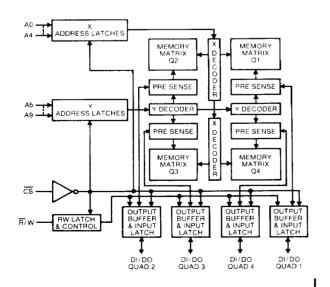

#### **BLOCK DIAGRAM**

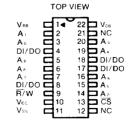

#### PIN CONFIGURATION

| Αn       | Address Inputs         |

|----------|------------------------|

| DI/DO    | Data Input/Data Output |

| <u> </u> | Chip Select Input      |

| R/W      | Read/Write Input       |

| N/C      | No Internal Connection |

| Vss      | Ground                 |

| $V_{BB}$ | Supply Voltage (-5V)   |

| Vcc      | Supply Voltage (+5V)   |

| $V_{DD}$ | Supply Voltage (+12V)  |

|          |                        |

## RECOMMENDED OPERATING CONDITIONS TAMB == 0°C to 70°C

| PARAMETER                | SYMBOL | MIN  | NOM  | MAX  | UNIT |

|--------------------------|--------|------|------|------|------|

| Supply Voltage           | σαν    | 11.4 | 12.0 | 12.6 | Vdc  |

| Output Reference Voltage | Vcc    | 4.75 | 5.0  | 5.25 | Vdc  |

| Substrate Voltage        | VBB    | 4.5  | -5   | -5.5 | Vdc  |

| Input High Level         | ViH    | 2.4  |      | 5.25 | Vdc  |

| Input Low Level          | VIL    | 0.1  | -    | 0.7  | Vdc  |

| Chip Select High Level   | VcH    | 8    | 12   | 15   | Vdc  |

| Chip Select Low Level    | VcL    | 1    | _    | 0.5  | Vdc  |

## DC ELECTRICAL CHARACTERISTICS (Full Operating Voltage and Temperature Range Unless Otherwise Noted)

|                                |                                   |        | 410 | 4A    | 410 | 4B                 |      |                                                                     |

|--------------------------------|-----------------------------------|--------|-----|-------|-----|--------------------|------|---------------------------------------------------------------------|

| CHARACTER                      | RISTICS                           | SYMBOL | MIN | MAX   | MIN | MAX                | UNIT | CONDITIONS                                                          |

| Input Current                  |                                   | lin    | -20 | -⊦20  | -20 | - <del>-</del> -20 | μA   | $V_{iN} = 0.7V \text{ or } 5V$                                      |

| Chip Select Input              | Current                           | Ics    | -20 | -∣-20 | -20 | +20                | μA   | $V_{CS} = 0.5V \text{ or } 12V$                                     |

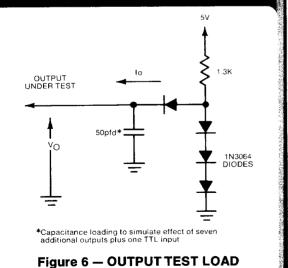

| Output "Low" Vol               | itage                             | Vol    | _   | 0.5   |     | 0.5                | Vdc  | I <sub>OL</sub> = 2.0 mA Fig. 5                                     |

| Output "High" Vo               | Itage                             | Vон    | 2.7 |       | 2.7 |                    | Vdc  | I <sub>OH</sub> = 500 µA Fig. 5                                     |

| Output Current (U              | Inselected)                       | IDO    | -20 | -≟-20 | 20  | +20                | μA   | V <sub>OUT</sub> = 2.7V, V <sub>CS</sub> = 12V                      |

| Supply Current (Saveraged over | one cycle)<br>4104B<br>150<br>300 | IDD    |     | 50    | _   | 55                 | mA   | TAMB == 25°C<br>Vpp == 12V<br>Vcc == 5V<br>VBB == -5V<br>Vcs == 12V |

| Supply Current                 | T <sub>AMB</sub> = 25°C           | IDD    |     | 5     | _   | 5                  | mA   | $V_{DD} = 12V$                                                      |

| (Unselected)                   | Т <sub>АМВ</sub> = 70°С7          | IDD    |     | 15    | _   | 15                 | mA   | V <sub>CC</sub> =5V                                                 |

| Substrate Curren               | t                                 | Іва    |     | -3    |     | 3                  | mA   | V <sub>BB</sub> = -5V                                               |

| Reference Supply               | Current                           | Icc    | _   | 100   |     | 100                | μA   | Vcs = 12V                                                           |

| Standby Current                | T <sub>AMB</sub> = 25°C           | lops   | _   | 2     | _   | 2                  | mA   | V <sub>CS</sub> = 4V to 15V<br>V <sub>DD</sub> = 4V                 |

| at Reduced<br>Voltages         | T <sub>AMB</sub> = 70°C           | I DDS  | _   | 6     | _   | 6                  | mA   | V <sub>BB</sub> = -4V<br>V <sub>CC</sub> = OV                       |

#### READ CYCLE - AC CHARACTERISTICS

|                                 |          | 4104A |          | 4104B |     |      |             |

|---------------------------------|----------|-------|----------|-------|-----|------|-------------|

| CHARACTERISTICS                 | SYMBOL   | MIN   | MAX      | MIN   | MAX | UNIT | CONDITIONS  |

| Chip Select Read Pulse Width    | Tosa     | 200   | <b>—</b> | 150   |     | ns   |             |

| Chip Select Rise and Fall Time* | Ton, Tor | _     | 100      | _     | 100 | ns   | FULL        |

| Set Up Time                     | ТР       | 0     | -        | 0     |     | ns   | OPERATING   |

| Access Time                     | TA       |       | 200      | -     | 150 | ns   | VOLTAGE     |

| Cycle Time,Tcn=Tcr = 10ns       | Tc       | 350   |          | 300   |     | ns   | AND         |

| Data Hold Time                  | Тн       | 100   | _        | 100   |     | ns   | TEMPERATURE |

| Output Recovery Time            | Tor      | 10    | _        | 10    |     | ns   | RANGE       |

| Read Recovery Time              | TCRR     | 125   | _        | 125   | T - | ns   |             |

#### WRITE CYCLE - AC CHARACTERISTICS

|                                                       |          | 4104A |          | 4104B |     |      |             |  |

|-------------------------------------------------------|----------|-------|----------|-------|-----|------|-------------|--|

| CHARACTERISTICS                                       | SYMBOL   | MIN   | MAX      | MIN   | MAX | UNIT | CONDITIONS  |  |

| Chip Select Write Pulse Width                         | Tcsw     | 200   | -        | 150   |     | ns   | FULL        |  |

| Chip Select Rise and Fall Time*                       | Tcr, Tcr |       | 100      | _     | 100 | ns   | OPERATING   |  |

| Set Up Time                                           | Tp       | 0     | <u> </u> | 0     |     | ns   | VOLTAGE     |  |

| Cycle Time, T <sub>CR</sub> = T <sub>CF</sub> = 10 ns | Tc       | 350   | _        | 300   | _   | ns   | AND         |  |

| Data Hold Time                                        | Тн       | 100   |          | 100   |     | ns   | TEMPERATURE |  |

| Write Recovery Time                                   | Town     | 125   |          | 125   | _   | ns   | RANGE       |  |

<sup>\*</sup>Typical Chip Select Rise and Fall Time (TcR and Tcr) is 10 ns For Read and Write Cycle

CAPACITANCE (Over Full Temperature Range and Worst Case Voltage Conditions)

| CHARACTERISTICS                        | SYMBOL | MIN | TYP | MAX | UNIT | CONDITIONS                      |

|----------------------------------------|--------|-----|-----|-----|------|---------------------------------|

| Input Capacitance (Except Chip Select) | Cin    | =   | 4   | 6   | pF   | Vin 2.4V                        |

| Input Capacitance Chip Select          | Ccs    | _   | 6   | 10  | pF   | Vcs = 12V or 0V                 |

| Output Capacitance                     | Со     | _   | 6   | 8   | pF   | V <sub>O</sub> 2.7V<br>V cs 12V |

# ABSOLUTE MAXIMUM RATINGS (See Note 1) (Referenced to GND)

| RATING                                          | SYMBOL | VALUE                 | UNIT |

|-------------------------------------------------|--------|-----------------------|------|

|                                                 | Vpp    | 5 to ⊡18              | Vdc  |

| Supply Voltages                                 | Vcc    | 5 to ⅓ 7              | Vdc  |

|                                                 | Vвв    | : .5 to ─18           | Vdc  |

| Input & Output Voltages<br>(Except Chip Select) | Vı, Vo | V <sub>BB</sub> to 15 | Vdc  |

| Chip Select Input Voltage                       | Vcs    | VBB to 15             | Vdc  |

| Power Dissipation                               | PD     | 1.6 (Note 2)          | W    |

| Operating Ambient<br>Temperature Range          | Тамв   | 0 to + 70             | °C   |

| Storage Temperature Range                       |        | 65 to +150            | °C_  |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

NOTE 1: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended or maximum voltages for extended periods of time could affect device reliability.

NOTE 2: At 25°C ambient. Derate 13.5mw/°C.

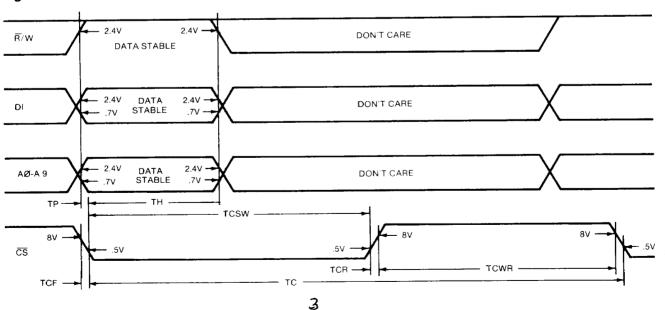

Figure 1 — READ CYCLE

Figure 2 — WRITE CYCLE

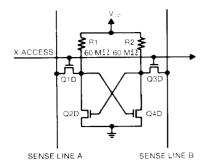

Figure 3 — MEMORY CELL

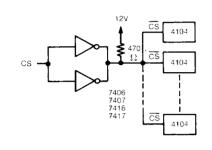

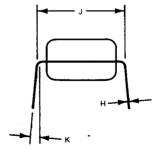

Figure 4 — TYPICAL CHIP SELECT DRIVER

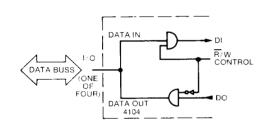

Figure 5 — COMMON DATA I/O

#### **FUNCTIONAL DESCRIPTION**

EMM/SEMI 4104 is a 4096 bit static RAM with memory cells organized in four arrays of 32 rows by 32 columns (1024 words x 4 bits). Each four bit word is addressed by simultaneously decoding the X addresses (Aothrough A4) for the rows and the Y addresses (A5 through A9) for the columns. Data is written or read in parallel on four common input/output pins (DI/DO). The operation of the memory is controlled by chip select (CS) and read/write (R/W).

When  $\overline{CS}$  is high, all pins are in an inoperative high impedance state, and power is supplied only to the memory elements.

When  $\overline{CS}$  is low, the memory is enabled for reading or writing.

The negative going edge of  $\overline{CS}$  begins timing for a read cycle. Data on  $\overline{R}/W$  and address pins (A<sub>N</sub>) must be stable for time T<sub>H</sub>.  $\overline{R}/W$  and A<sub>N</sub> will then have been latched into D type flip flops and no longer need to be held stable. Output data will be presented on the four output pins (DI/DO) within time T<sub>A</sub> and will remain until time T<sub>DR</sub> after  $\overline{CS}$  goes high. Data will then be invalid. After time T<sub>C</sub> another read or write cycle can be initiated.

The negative going edge of  $\overline{CS}$  also begins timing for a write cycle.  $\overline{R}/W$ ,  $A_N$  and DI must be held stable for time  $T_H$ . These inputs will then have been latched and DI will be entered within time  $T_{CSW}$ . Another read or write cycle can be initiated after time  $T_C$ .

The memory cells (because they are cross coupled high impedance static cells) will retain data down to  $V_{DD}\!=\!4V$ ,  $V_{BB}\!=\!-4V$ .

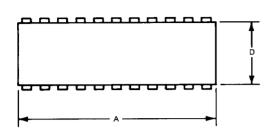

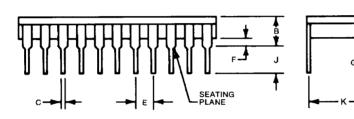

## **CERAMIC PACKAGE DIMENSIONS**

| [   | MILLIM | ETERS     | INCHES  |       |  |

|-----|--------|-----------|---------|-------|--|

| DIM | MIN    | MAX       | MIN     | MAX   |  |

| A   | 27.1   | 27.8      | 1.065   | 1.095 |  |

| В   | i – i  | 3.56      | _       | 0.140 |  |

| С   | 0.38   | 38 0.53 0 |         | 0.023 |  |

| D   | 8.64   | 10.8      | 0.340   | 0.425 |  |

| E   | 2.29   | 2.79      | 0.090   | 0.110 |  |

| F   | 0.64   | 1.65      | 0.025   | 0.065 |  |

| G   | 0.20   | 0.30      | 0.008   | 0.012 |  |

| J   | 2.54   | 3.81      | 0.100   | 0.150 |  |

| К   | 10.2   | REF       | 0.4 REF |       |  |

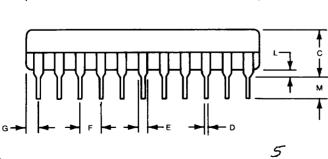

## PLASTIC PACKAGE DIMENSIONS

|     | MILLIN | IETERS | INC   | HES  |  |  |  |

|-----|--------|--------|-------|------|--|--|--|

| DIM | MIN    | MAX    | MIN   | MAX  |  |  |  |

| A   | 27.9   | 29.72  | 1.100 | 1.17 |  |  |  |

| В   | 8.64   | 9.14   | .340  | .360 |  |  |  |

| С   | 4.32   | 5.08   | .170  | .200 |  |  |  |

| D   | .36    | 36 .56 |       | .022 |  |  |  |

| E   | .76    | 1.52   | .030  | .060 |  |  |  |

| F   | 2.41   | 2.67   | .095  | .105 |  |  |  |

| G   | 1.02   | 2.03   | .040  | .080 |  |  |  |

| Н   | .20    | .31    | .008  | .012 |  |  |  |

| J   | 9.65   | 10.16  | .380  | .400 |  |  |  |

| K   | 0°     | 15°    | 0°    | 15°  |  |  |  |

| L   | .51    | 1.02   | .020  | .040 |  |  |  |

| М   | 2.54   | 3.56   | .100  | .140 |  |  |  |

#### **ORDERING INFORMATION**

|             | Spe    | ed    |         |                   |

|-------------|--------|-------|---------|-------------------|

| Part Number | Access | Cycle | Package | Temperature Range |

| 4104ACC     | 200    | 350   | Ceramic | 0°C to +70°C      |

| 4104ACP     | 200    | 350   | Plastic | 0°C to +70°C      |

| 4104BCC     | 150    | 300   | Ceramic | 0°C to +70°C      |

| 4104BCP     | 150    | 300   | Plastic | 0°C to +70°C      |

#### **WARNING:**

## MOS CIRCUITS ARE SUBJECT TO DAMAGE FROM STATIC DISCHARGE

Internal static discharge circuits are provided to minimize part damage due to environmental static electrical charge build-ups. Industry established recommendations for handling MOS circuits include:

- 1. Ship and store product in conductive shipping tubes or in conductive foam plastic. Never ship or store product in non-conductive plastic containers or non-conductive plastic foam material.

- 2. Handle MOS parts only at conductive work stations.

- 3. Ground all assembly and repair tools.

| Represented | in | Your | Area | By: |

|-------------|----|------|------|-----|

|             |    |      |      |     |

A Subsidiary of Electronic Memories & Magnetics Corporation 3883 North 28th Avenue, Phoenix, Arizona 85017 Telephone (602) 263-0202 • TWX 910-951-1383

6