February 1990

#### Distinctive Features

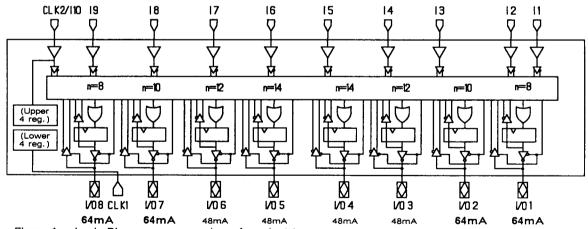

- Eight high current programmable I/Os and 11 inputs with logic architecture similar to industry standard PLDs.

- Integrated 64mA and 48mA drivers programmable to open collector or three-state configurations

- Buried register and combinatorial feedback capability

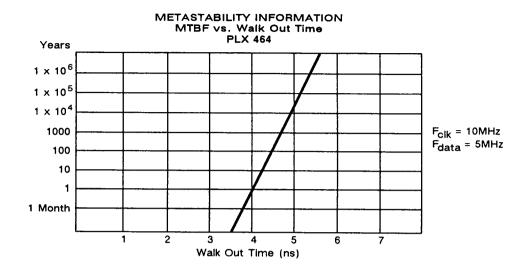

- Metastable hardened registers

- Two independent clock inputs

- On board drivers and Schmitt triggers allow direct connection to noisy backplanes

- Military temperature and reliability tested parts available in DIP and surface mountable packages

## Applications\_\_\_\_

- Bus Control Logic

- Bus Master and Slave Controllers

- Intelligent Transceivers

- Interrupt Generators and Handlers

- Bus Arbiters

- General purpose high density, high drive current logic

## General Description

The PLX 464 Is a CMOS, UV erasable programmable logic device that can be easily programmed with industry standard hardware and software. With its on-board high current drivers and Schmitt triggers, metastable hardened registers and input hysteresis, it is ideally suited for designs in which direct connection to a bus backplane or other noisy environment is required. The high current drivers meet the specifications of VME, VSB, MBI\*, MBII\*, Micro Channel\*\*, NuBus\*\*\* and other leading bus signal specifications. In addition, the PLX 464 has dynamic, bi-directional I/Os, buried register capability for building state machines and two clock inputs to handle asynchronous inputs.

Figure 1. Logic Diagram. n = number of product terms.

- Patent No. 4,833,349

- \* Multibus I and Multibus II are registered trademarks of Intel Corporation

- \*\* Micro Channel is a registered trademark of IBM Corporation

- \*\*\* NuBus is a registered trademark of Texas Instruments, Inc.

# Detailed Description\_\_\_\_\_

#### Programmable Output Macrocell

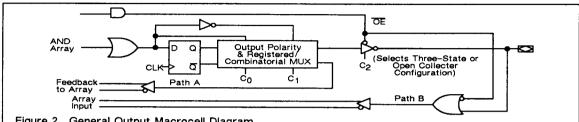

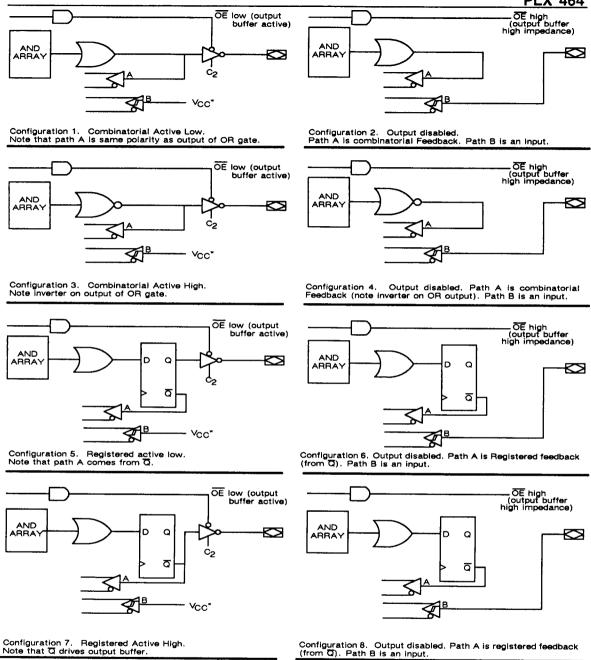

The PLX 464 programmable output macrocell configuration is determined by the architecture bits  $C_0$ ,  $C_1$ ,  $C_2$  and the output enable  $(\overline{OE})$  product term (see Figures 2, 3 and table below).

The user can program each macrocell to a registered or combinatorial configuration with bit  $\mathbf{C}_{o}$ .

$C_1$  determines the output polarity (Active High or Active Low).

With C<sub>2</sub> the user can individually program the 64mA outputs (I/O 1, 2, 7, 8) to open collector or three-state configurations. (Continued on page 4.)

Figure 2. General Output Macrocell Diagram. Applies to macrocells with 64mA outputs. 48mA output macrocells are three-state regardless of the state of  $C_2$ .

# Architecture Bit and OE Term Definitions

| Sign | al Na    | me |                   | Definition                                                                                      | Signal Name           | Defin                                                         | ition                                                                                                                     |

|------|----------|----|-------------------|-------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|      | CO<br>C1 |    | High is<br>combin | high Impedance, low is active. registered mode, low is activel. active high, low is active low. | C2                    | C2 is high and OE is open collector. If C2 then the output is | ate of 64mA outputs. If<br>s low then the output is<br>t s low and OE is low,<br>otem-pole. NOTE:<br>ways totem-pole when |

| CO   | C1       | C2 | ŌĒ                | Configuration D                                                                                 | escription            |                                                               | Schematic                                                                                                                 |

| 0    | 0        | 0  | 0                 | Combinatorial, active low, tot                                                                  | em pole output ena    | bled                                                          | Configuration 1                                                                                                           |

| 0    | 0        | 0  | 1                 | Combinatorial, active low, tot                                                                  | em pole output disa   | bled                                                          | Configuration 2                                                                                                           |

| 0    | 0        | 1  | 0                 | Combinatorial, active low, op                                                                   | en collector output e | enabled                                                       | Configuration 1                                                                                                           |

| 0    | 0        | 1  | 1                 | Combinatorial, active low, op-                                                                  | en collector output o | lisabled                                                      | Configuration 2                                                                                                           |

| 0    | 1        | 0  | 0                 | Combinatorial, active high, to                                                                  | tem pole output ena   | bled                                                          | Configuration 3                                                                                                           |

| 0    | 1        | 0  | 1                 | Combinatorial, active high, to                                                                  | tem pole output dis   | abled                                                         | Configuration 4                                                                                                           |

| 0    | 1        | 1  | 0                 | Combinatorial, active high, op                                                                  | en collector output   | enabled                                                       | Configuration 3                                                                                                           |

| 0    | . 1      | 1  | 1                 | Combinatorial, active high, op-                                                                 | en collector output   | disabled                                                      | Configuration 4                                                                                                           |

| 1    | 0        | 0  | 0                 | Registered, active low, totem                                                                   | pole output enabled   |                                                               | Configuration 5                                                                                                           |

| 1    | 0        | 0  | 1                 | Registered, active low, totem                                                                   | pole output disable   | <b>d</b>                                                      | Configuration 6                                                                                                           |

| 1    | 0        | 1  | 0                 | Registered, active low, open                                                                    | collector output ena  | bled                                                          | Configuration 5                                                                                                           |

| 1    | 0        | 1  | 1                 | Registered, active low, open                                                                    | collector output disa | bled                                                          | Configuration 6                                                                                                           |

| 1    | 1        | 0  | 0                 | Registered, active high, totem                                                                  | pole output enable    | d                                                             | Configuration 7                                                                                                           |

| 1    | 1        | 0  | 1                 | Registered, active high, totem                                                                  | pole output disable   | d                                                             | Configuration 8                                                                                                           |

| 1    | 1        | 1  | 0                 | Registered, active high, open                                                                   | collector output ena  | bled                                                          | Configuration 7                                                                                                           |

| 1    | 1        | 1  | 1                 | Registered, active high, open                                                                   | collector output disa | bled                                                          | Configuration 8                                                                                                           |

Figure 3. Specific Output Macrocell Configurations.

64 mA pins may be configured to open collector mode by programming C<sub>2</sub>

\* When  $\overline{\text{OE}}$  is enabled, Path B input becomes logical level high (goes to VCC)

#### Programmable Output Macrocell (Continued)

The  $\overline{OE}$  disables and enables both the output buffer and the input path (path B). When one is enabled, the other is disabled and vice versa. The  $\overline{OE}$  state may be selected permanently or dynamically. The operation of the output buffer and the path B buffer are similar to that of a bi-directional transceiver.

When  $\overline{OE}$  is low, the output buffer is enabled and the path B input is disconnected from the I/O pin and driven to  $V_{CC}$  (logic one).

When  $\overline{OE}$  is high, the output buffer is disabled and the path B input is connected to the I/O pin acting as an input to the array.

In a typical application, the user can monitor  $\overline{\text{OE}}$  to determine if path B is enabled or tied to  $V_{CC}$ . If the user wishes to monitor an I/O pin which can be driven by the macrocell output or another device (open collector or three state signal), the user can monitor both the internal feedback (Path A) and the input path (Path B).

Note that the output is enabled by the logical OR of the inputs to the  $\overline{OE}$  product term.

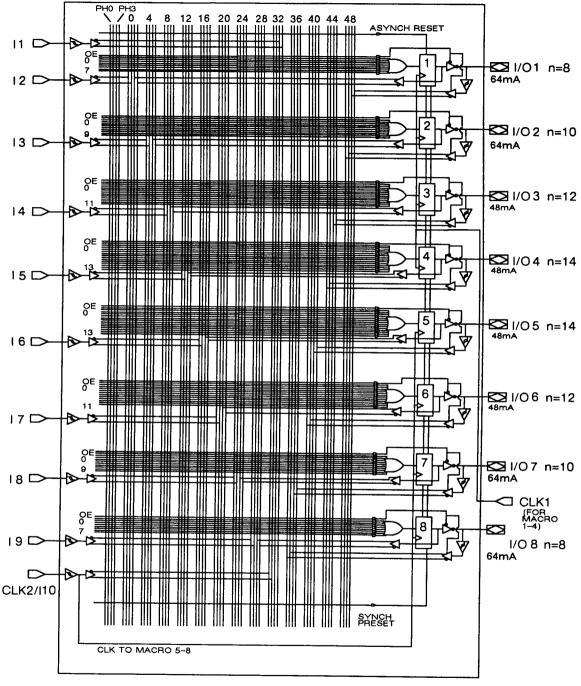

#### Preset and Reset

The PLX 464 includes synchronous preset and asynchronous reset product terms which are common to all output macrocells (see Figure 4.) The device automatically resets on power up. ("Preset" means Q output at register is set to 1. "Reset" means Q is set to 0.)

#### Testing

PLX 100 percent tests the windowed devices for full AC specifications before shipment. After test they are erased by exposure to Ultraviolet Light.

PLX tests the non-windowed one time programmable (OTP) devices for full AC specifications through the phantom array (Ph0-Ph3) and top test and bottom test

rows. The device can be tested at incoming inspection the same way. Programmed devices can be tested by using preload to load initial values into the registers. Contact PLX for detailed programming information.

#### Clocks

The PLX 464 has two clock inputs. The dedicated clock pin clocks the registers in macrocells 1-4. The shared clock/input pin clocks registers in macrocells 5-8 (see Figure 4.)

#### Erasure

To erase the device, apply a minimum dose of 2537 Angstroms, 1800 mW  $\times$  min/cm<sup>2</sup>, (20 minutes under direct UV light, typically).

#### Metastability

Registers in the device have been specifically designed to minimize the metastable recovery time. For example, an MTBF requirement of 10 years at a clock frequency of 10MHz and a data frequency of 5MHz requires only 4ns of recovery time. (See page 11.) A detailed report on metastability is available from PLX on request.

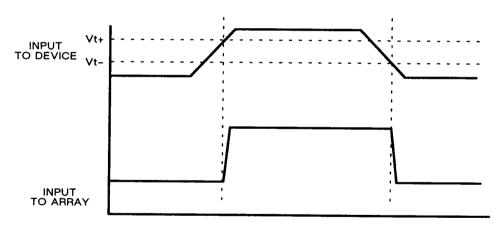

#### **Hysteresis**

All inputs, including output macrocell inputs, have 200 mV typical hysteresis. (See pages 7 and 11.)

#### **Ground Bounce**

Three ground pins are provided to ensure minimal ground bounce in the device. I/O1-4 grounds are electrically isolated from I/O5-8 grounds. All I/O grounds are isolated from the internal logic ground. A detailed report on ground bounce and other bus specific device characteristics is available from PLX on request.

#### **Device Programming**

The following PLD programming software and hardware supports the PLX 448 device. Designers may use the software products below to edit source files, perform simulations and create JEDEC fuse map files.

| Manufacturer (Software)                                                                                       | Product                                              | Phone No. (in U.S.)                                                                     |  |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| Data I/O, Redmond, WA<br>Logical Devices, Fort Lauderdale, FL                                                 | ABEL <sup>™</sup> (version 3.0)<br>CUPL <sup>™</sup> | 1-800-247-5700<br>(305-974-0967 FL)                                                     |  |

| PistoHI™ Tools, Cupertino, CA —Others are in development; contact PLX for ar                                  | PET100 <sup>™</sup><br>n update.                     | 1-800-274-7864                                                                          |  |

| Manufacturer (Programmers)                                                                                    | Model No.                                            | Phone No. (in U.S.)                                                                     |  |

| Advin Systems, Sunnyvale, CA<br>Data I/O, Redmond, WA<br>Data I/O<br>Digelec, Canoga Park, CA                 | Sallor-PAL<br>29B<br>Unisite 40 <sup>™</sup><br>860  | 408-736-1622<br>1-800-247-5700<br>1-800-247-5700<br>1-800-367-8750<br>(818-887-3755 CA) |  |

| InLab, Broomfield, CO                                                                                         | 28 A/U                                               | 1-800-237-6759<br>(303-460-0103 CO)                                                     |  |

| Logical Devices, Fort Lauderdale, FL                                                                          | Allpro™                                              | (305-974-0967 FL)<br>1-800-331-7766                                                     |  |

| OAE, Giendale, CA                                                                                             | (Omni 28, 40, 64 in development)                     | 1-800-828-0080,<br>(1-800-423-8874 CA)                                                  |  |

| PistoHI <sup>™</sup> Tools, Cupertino, CA                                                                     | PET100 <sup>™</sup>                                  | 408-255-2422                                                                            |  |

| Stag Microsystems, Santa Clara, CA<br>Sunrise, Glendora, CA<br>—Others in Development; contact PLX for an upo | All Models<br>ZL1000B, Z2500B<br>date.               | 408-988-1118<br>818-914-1926                                                            |  |

Figure 4. Logic Diagram (n = # of product terms)

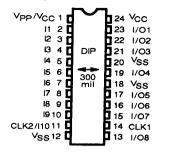

# Packages and Connection Diagrams

Pin Description (DIP and LCC Packages)

| Pin No.   |      | Description                                                      | Pin No.               |                       | Description                           |  |

|-----------|------|------------------------------------------------------------------|-----------------------|-----------------------|---------------------------------------|--|

| LCC       | DIP  |                                                                  | LCC                   | DIP                   |                                       |  |

| 28        | 24   | Vcc                                                              | 14, 21, 24            | 12, 18, 20            | Vss (Ground)                          |  |

| 3-7, 9-12 | 2-10 | Dedicated Inputs                                                 | 16, 18, 19            | 13, 15,16,            | Bidirectional                         |  |

| 13        | 11   | Dedicated Input and/or<br>Clock input to registers<br>4-8 (CLK2) | 20, 23, 25,<br>26, 27 | 17, 19, 21,<br>22, 23 | Input/Output pins                     |  |

| 17        | 14   | Clock input to registers<br>1-4 (CLK1)                           | 1, 8, 15,<br>22       |                       | No Connect                            |  |

| 2         | 1    | VPP /VCC                                                         |                       |                       | · · · · · · · · · · · · · · · · · · · |  |

Operating Ranges

Commercial (C)

Military (M)

**Ambient**

Temperature

0°C to +70°C

-55°C to +125°C

Supply Voltage

(Vcc)

$5V \pm 5\%$

5V ± 10%

# Absolute Maximum Ratings\_\_\_\_\_\_ Storage Temperature .....-65°C to +150°C Ambient Temperature with

Power Applied ..........-55°C to +125°C Supply Voltage to Ground ..... -0.5V to +7.0V

DC Voltage to Outputs in

High Z State .................-0.5V to +7.0V

Electrical Characteristics Tested over Operating Range

| Parameter                              | Description                  | Te                                                                             | est Conditions                                  | Min | Max | Units |

|----------------------------------------|------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|-------|

| Voн                                    | Output HIGH Voltage          | V <sub>CC</sub> = Min,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OH</sub> = -3.0mA                        | 2.4 |     | V     |

|                                        |                              |                                                                                | I/O3, 4, 5, 6<br>I <sub>OL</sub> = 48mA (Com'l) |     | 0.5 | v     |

| <b>V</b> OL                            | Output LOW Voltage           | VCC = Min,                                                                     | I <sub>OL</sub> = 48mA (MIL)                    |     | 0.6 | V     |

| -OL                                    | Output LOW Voltage           | VIN = VIH or VIL                                                               | I/O1, 2, 7, 8<br>I <sub>OL</sub> = 64mA (Com'I) |     | 0.5 | V     |

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                              |                                                                                | IOL = 64mA (MIL)                                |     | 0.6 | V     |

| <u> Ун</u>                             | Input HIGH Level             |                                                                                |                                                 | 2.0 |     | V     |

| YIL.                                   | Input LOW Level              |                                                                                |                                                 |     | 0.8 | V     |

| l <sub>l</sub> X                       | Input Leakage Current        | V <sub>SS</sub> <= V <sub>IN</sub> <=\                                         | CC, VCC= Max                                    | -10 | 10  | μА    |

| loz                                    | Output Leakage Current       |                                                                                | SS <= YOUT <= VCC                               | -40 | 40  | μΑ    |

| Isc                                    | Output Short Circuit Current | VCC = Max, VC                                                                  | OUT = 0.5V                                      | -30 | -90 |       |

|                                        |                              | 99 7 901 111                                                                   |                                                 |     |     | mA    |

| lcc                                    | Power Supply Current         | VCC = Max, VIN = GND Outputs Open (Com'I)                                      |                                                 |     | 80  | mΑ    |

|                                        |                              | VCC= Max, V <sub>N</sub> =                                                     | GND Outputs Open (MIL)                          |     | 90  | mA    |

6

# Capacitance (sample tested only) Hysteresis

| Parameter | Test Conditions                   | Pins             | Тур | Units |

|-----------|-----------------------------------|------------------|-----|-------|

| CiN       | V <sub>IN</sub> = 2.0V @ f = 1MHz | inputs &<br>CLK1 | 5   | рF    |

|           |                                   | I/Os             | 10  | рF    |

| COUT      | V <sub>IN</sub> = 2.0V @ f = 1MHz | I/Os             | 10  | pF    |

| Parameter<br>Symbol | Description                                     | Тур | Units    |

|---------------------|-------------------------------------------------|-----|----------|

| V <sub>T+</sub>     | Positive-going threshold                        | 1.5 | <b>V</b> |

| V <sub>T</sub> _    | Negative-going threshold                        | 1.3 | V        |

| n∨⊤                 | Hysteresis (V <sub>T+</sub> - V <sub>T-</sub> ) | 0.2 | V        |

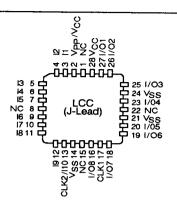

# Switching Waveform\_\_\_\_

# Switching Characteristics (Commercial Temperature Range)\_\_\_

|     | Parameter       |                                   |      | 15  |       |

|-----|-----------------|-----------------------------------|------|-----|-------|

|     | Symbol          | Description                       | Min  | Max | Units |

| 1.  | t <sub>PD</sub> | Input/feedback to nonreg. output  |      | 45  | ns    |

| 2.  | t <sub>EA</sub> | Input to Output Enable            |      | 45  | ns    |

| 3.  | t <sub>ER</sub> | Input to Output Disable           |      | 45  | ns    |

| 4.  | tco             | Clock to Output                   |      | 30  | ns    |

| 5.  | tp              | Clock Period (tg+ tCO)            | 60   |     | ns    |

| 6.  | t <sub>W</sub>  | Clock Width                       | 35   |     | ns    |

| 7.  | ts              | Setup time (input or feedback)    | 30   |     | ns    |

| 8.  | t <sub>H</sub>  | Hold time                         | 0    |     | ns    |

| 9.  | tAW             | Asynchronous reset width          | 45   |     | ns    |

| 10. | t <sub>AR</sub> | Recovery time, Asynch, reset      | 45   |     | ns    |

| 11. | t <sub>AP</sub> | Asynch reset to reg. output reset | 45   |     | ns    |

| 12. | fMAX            | Maximum frequency                 | 16.7 |     | MHz   |

Note: Devices are tested with a 50 pF load. De-rate speed by 10ns for a 300 pF load.

# Switching Characteristics (Military Temperature Range)\_\_\_\_\_

|     | Parameter        |                                   | N    | 1–65 |       |

|-----|------------------|-----------------------------------|------|------|-------|

|     | Symbol           | Description                       | Min  | Max  | Units |

| 1.  | t <sub>PD</sub>  | Input/feedback to nonreg. output  |      | 65   | ns    |

| 2.  | <sup>t</sup> EA  | Input to Output Enable            |      | 65   | ns    |

| 3.  | <sup>t</sup> ER  | Input to Output Disable           |      | 65   | ns    |

| 4.  | <sup>t</sup> co  | Clock to Output                   |      | 50   | ns    |

| 5.  | t₽               | Clock Period (ts+ tCO)            | 90   |      | ns    |

| 6.  | t <sub>W</sub>   | Clock Width                       | 35   |      | ns    |

| 7.  | t <sub>S</sub>   | Setup time (input or feedback)    | 40   |      | ns    |

| 8.  | t <sub>H</sub>   | Hold time                         | 0    |      | ns    |

| 9.  | t <sub>AW</sub>  | Asynchronous reset width          | 65   |      | ns    |

| 10. | t <sub>AR</sub>  | Recovery time, Asynch. reset      | 65   |      | ns    |

| 11. | t <sub>AP</sub>  | Asynch reset to reg. output reset | 65   |      | ns    |

| 12. | <sup>f</sup> MAX | Maximum frequency                 | 11.1 |      | MHz   |

Note: Devices are tested with a 50 pF load. De-rate speed by 10ns for a 300 pF load.

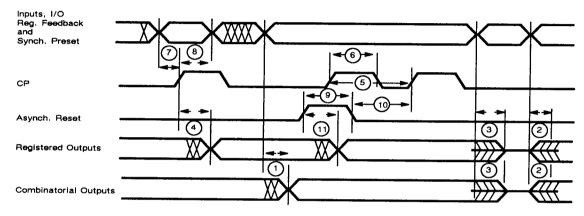

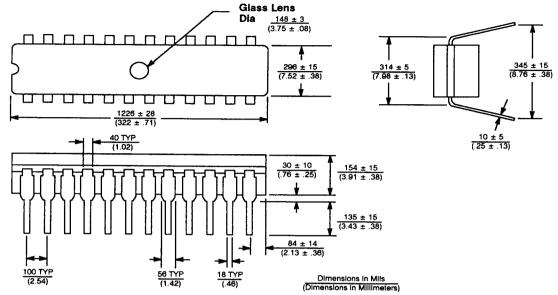

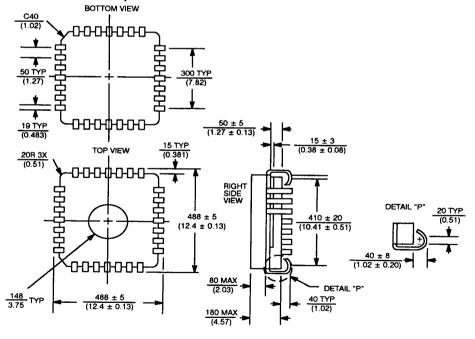

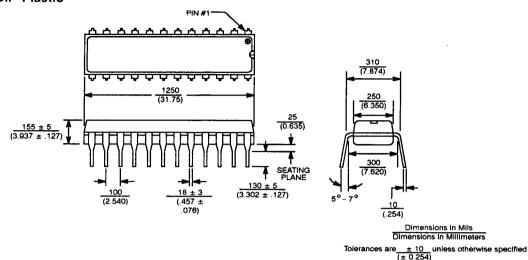

# 24-Lead Ceramic Dual In-line Package (CERDIP)

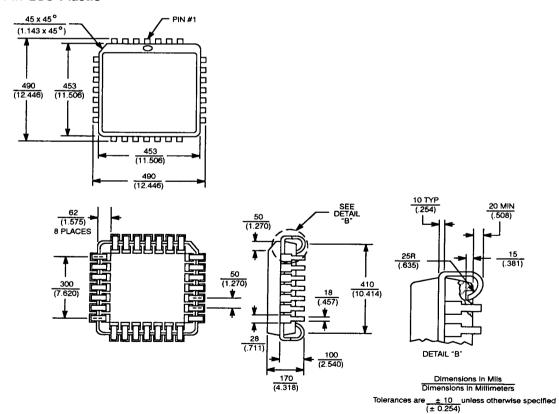

# 28-Pin J Lead Ceramic Chip Carrier

# 24-Pin DIP Plastic

# 28-Pin LCC Plastic

# INPUT HYSTERESIS (SCHMITT TRIGGER INPUTS)

# Ordering Information\_

|                    | Temperature Range  |                    |  |

|--------------------|--------------------|--------------------|--|

| Package            | Commercial         | Military           |  |

|                    | 0°C to +70°C       | -55°C to +125°C    |  |

| Package Material   | Ceramic/Plastic    | Ceramic            |  |

| ackage Type        | 24 Pin 300mil DIP  | 24 Pin 300mil DIP  |  |

|                    | 28 Pin J-Lead LCC  | 28 Pin J-Lead LCC  |  |

| rive Current (IOL) | 4 @ 64mA, 4 @ 48mA | 4 @ 64mA, 4 @ 48mA |  |

# Part Number Designations

**PLX 464** XXX-YY

Speed Category -45 or -65

Package Type D = 24 Pin, windowed ceramic DIP, 300mil

P = 24 Pin, plastic DIP, 300mil

WJC = 28 Pin, windowed J-lead ceramic LCC

JC = 28 Pin, J-lead ceramic LCC

JP = 28 Pin, J-lead plastic LCC

HR = 24 Pin, windowed ceramic DIP, 300mil, High Reliability Tested

M = 24 Pin, windowed ceramic DIP, 300mil, Military Temperature (-55°C to +125°C)

PLX reserves the right to make changes in its products without notice. For further information on specifications, contact PLX directly.

© PLX Technology Corporation, 1990

o36889 ₹ \_