# Si3220/25 Si3200/02

# DUAL PROSLIC<sup>®</sup> PROGRAMMABLE CMOS SLIC/CODEC

#### **Features**

- Performs all BORSCHT functions

- Ideal for applications up to 18 kft

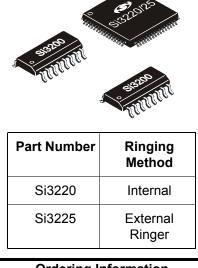

- Internal balanced and unbalanced ringing (Si3220)

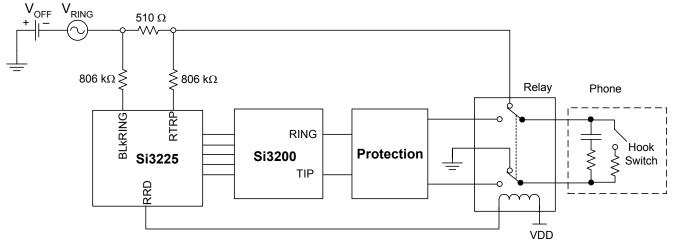

- External bulk ringer support (Si3225)

- Software-programmable parameters:

- Ringing frequency, amplitude, cadence, and waveshape (Si3220)

- Two-wire ac impedance

- Transhybrid balance

- DC current loop feed

- · Loop closure and ring trip thresholds

- Ground key detect threshold

- Automatic switching of up to three battery supplies

- On-hook transmission

#### Applications

- **Digital loop carriers**

- Central Office telephony

- Pair gain remote terminals

- Wireless local loop

#### Description

Loop or ground start operation with smooth/abrupt polarity reversal Modem/fax tone detection

- DTMF generation/decoding

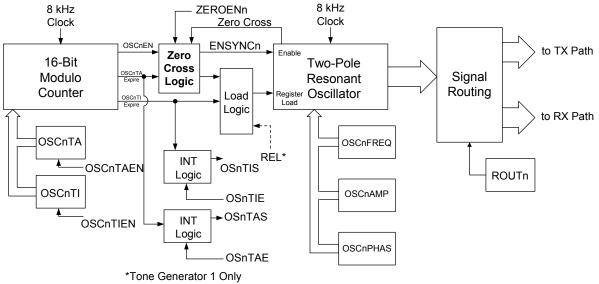

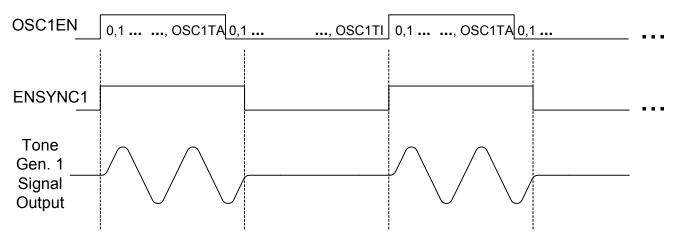

- Dual tone generators

- A-Law/u-Law. linear PCM companding

- PCM and SPI bus digital interfaces with programmable interrupts

- GCI mode support

- 3.3 or 5 V operation

- GR-909 loop diagnostics

- Audio diagnostics with loopback

- 12 kHz/16 kHz pulse metering (Si3220)

- FSK caller ID generation

- Lead-free/RoHS-compliant

- Private Branch Exchange (PBX) systems

- Voice over IP/voice over DSL

- ISDN terminal adapters

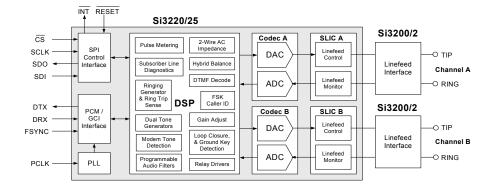

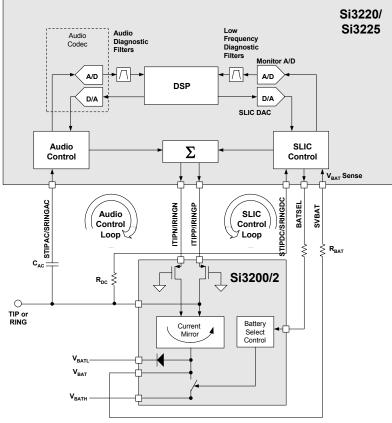

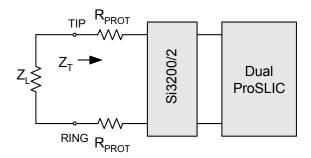

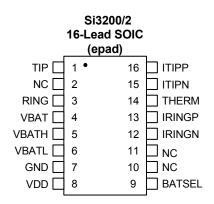

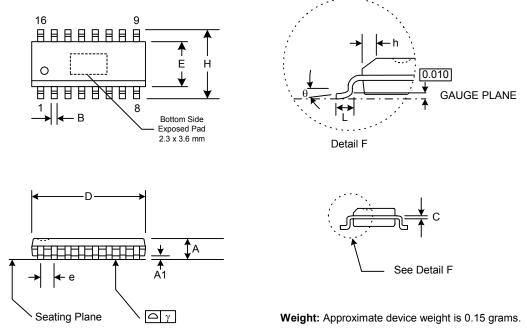

The Dual ProSLIC<sup>®</sup> is a series of low-voltage CMOS devices that integrate both SLIC and codec functionality into a single IC to provide a complete dual-channel analog telephone interface in accordance with all relevant LSSGR, ITU, and ETSI specifications. The Si3220 includes internal ringing generation to eliminate centralized ringers and ringing relays, and the Si3225 supports centralized ringing for long loop and legacy applications. On-chip subscriber loop and audio testing allows remote diagnostics and fault detection with no external test equipment or relays. The Si3220 and Si3225 operate from a single 3.3 or 5 V supply and interface to standard PCM/SPI or GCI bus digital interfaces. The Si3200/2 linefeed ICs perform all high-voltage functions and operate from a 3.3 or 5 V supply as well as single or dual battery supplies up to 100 V (Si3200) or 125 V (Si3202). The Si3220 and Si3225 are available in a 64-pin thin quad flat package (TQFP), and the Si3200/2 is available in a thermally-enhanced 16-pin small outline (SOIC) package.

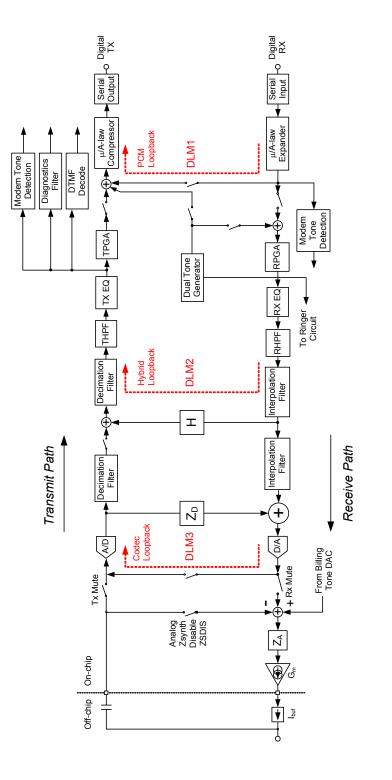

### Functional Block Diagram

**Ordering Information**

See "Dual ProSLIC Selection Guide" on page 110.

U.S. Patent #6,567,521 U.S. Patent #6,812,744 Other patents pending

- Cable telephony

- -

# TABLE OF CONTENTS

| Section                                         | <u>Page</u> |

|-------------------------------------------------|-------------|

| 1. Electrical Specifications                    | 4           |

| 2. Bill of Materials                            |             |

| 3. Functional Description                       | 30          |

| 3.1. Dual ProSLIC Architecture                  |             |

| 3.2. Power Supply Sequencing                    | 31          |

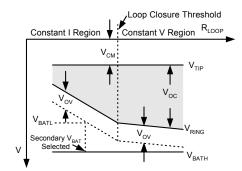

| 3.3. DC Feed Characteristics                    |             |

| 3.4. Adaptive Linefeed                          | 34          |

| 3.5. Ground Start Operation                     |             |

| 3.6. Linefeed Calibration                       |             |

| 3.7. Loop Voltage and Current Monitoring        | 37          |

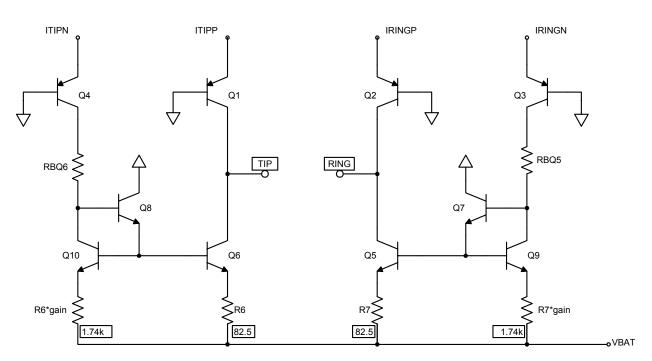

| 3.8. Power Monitoring and Power Fault Detection | 37          |

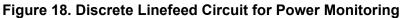

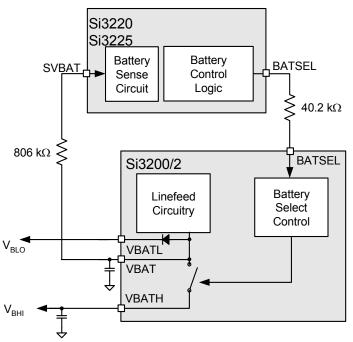

| 3.9. Automatic Dual Battery Switching           |             |

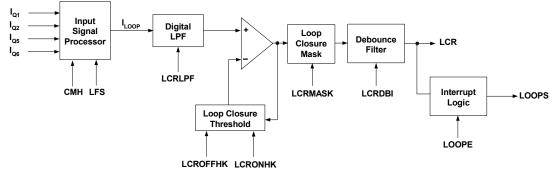

| 3.10. Loop Closure Detection                    |             |

| 3.11. Ground Key Detection                      | 46          |

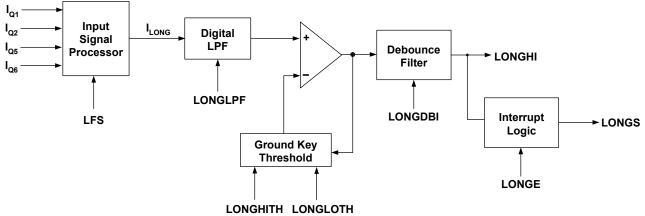

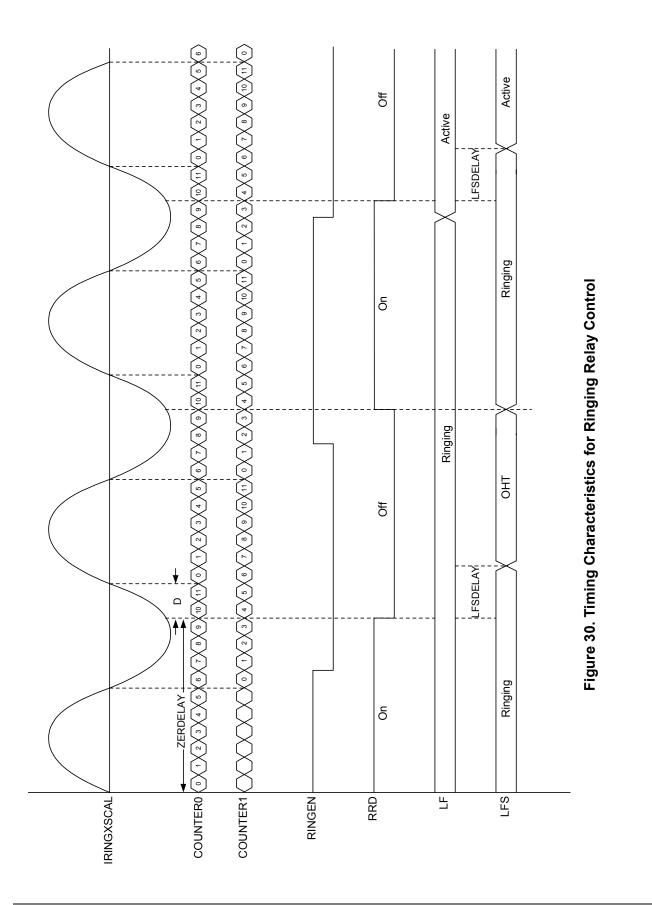

| 3.12. Ringing Generation                        |             |

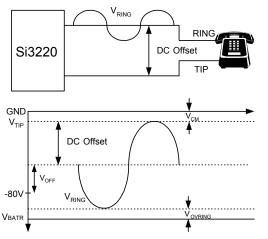

| 3.13. Internal Unbalanced Ringing               |             |

| 3.14. Ringing Coefficients                      |             |

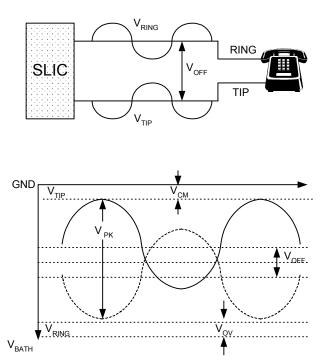

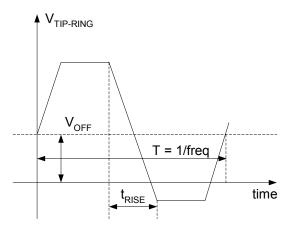

| 3.15. Ring Trip Detection                       | 54          |

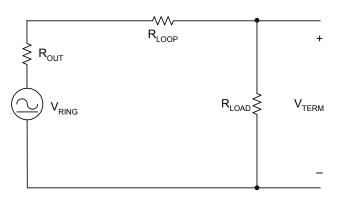

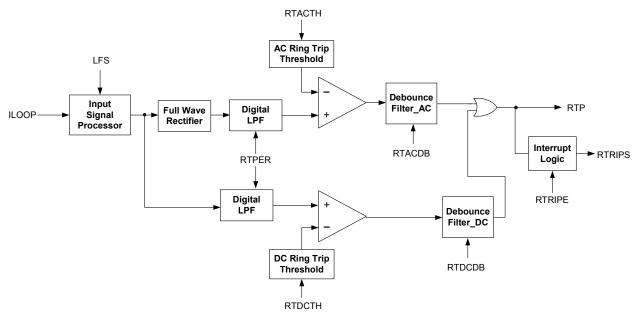

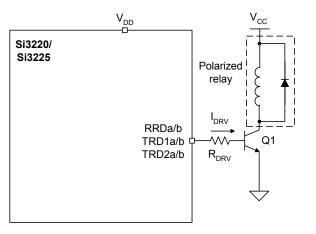

| 3.16. Relay Driver Considerations               | 57          |

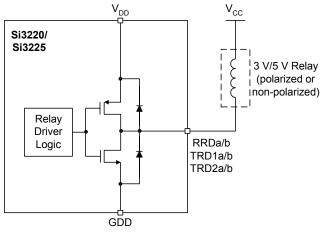

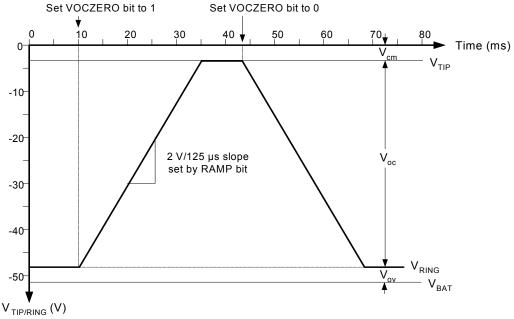

| 3.17. Polarity Reversal                         |             |

| 3.18. Two-Wire Impedance Synthesis              | 62          |

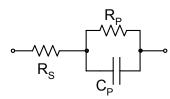

| 3.19. Transhybrid Balance Filter                |             |

| 3.20. Tone Generators                           |             |

| 3.21. Caller ID Generation                      | 67          |

| 3.22. Pulse Metering Generation                 | 68          |

| 3.23. DTMF Detection                            | 69          |

| 3.24. Modem Tone Detection                      | 70          |

| 3.25. Audio Path Processing                     | 70          |

| 3.26. System Clock Generation                   | 72          |

| 3.27. Interrupt Logic                           | 73          |

| 3.28. SPI Control Interface                     | 73          |

| 3.29. PCM Interface                             |             |

| 3.30. PCM Companding                            |             |

| 3.31. General Circuit Interface                 | 84          |

| 3.32. System Testing                            |             |

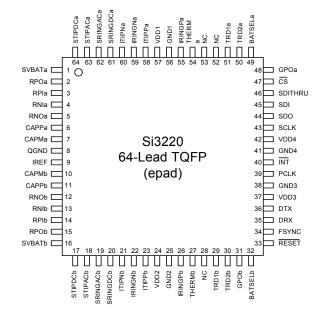

| 4. Pin Descriptions: Si3220/25                  |             |

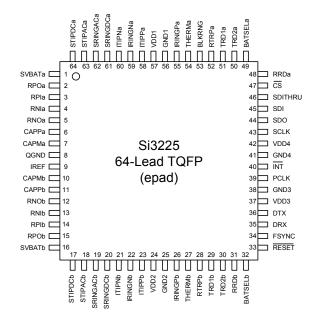

| 5. Pin Descriptions: Si3200/2                   |             |

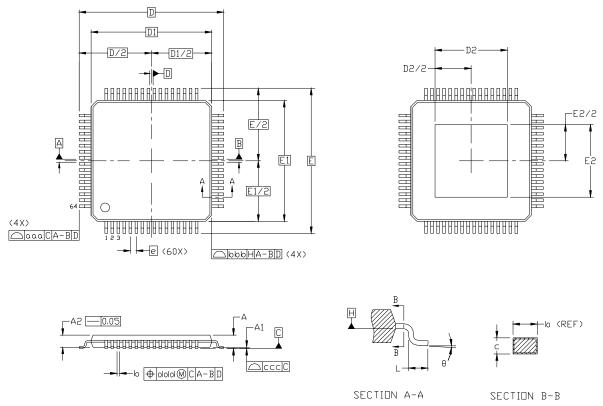

| 6. Package Outline: 64-Pin TQFP                 |             |

| 7. Package Outline: 16-Pin ESOIC                |             |

| 8. Silicon Labs Si3220/25 Support Documentation |             |

| 9. Dual ProSLIC Selection Guide                 |             |

| Document Change List                            |             |

| Contact Information                             | 112         |

# 1. Electrical Specifications

## Table 1. Absolute Maximum Ratings and Thermal Information<sup>1</sup>

| Parameter                                                                                       | Symbol                                  | <b>Test Condition</b> | Min                   | Мах                   | Unit |

|-------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------|-----------------------|-----------------------|------|

| Si3220/Si3225                                                                                   |                                         |                       | +                     | <u> </u>              |      |

| Supply Voltage                                                                                  | V <sub>DD1-</sub><br>V <sub>DD4</sub>   |                       | -0.5                  | 6.0                   | V    |

| STIPAC, STIPDC, SRINGAC, SRINGDC Current                                                        |                                         |                       | -20                   | +20                   | mA   |

| Input Current, Digital Pins                                                                     | I <sub>IN</sub>                         |                       | -10                   | +10                   | mA   |

| Input Voltage, Digital Pins                                                                     | V <sub>IND</sub>                        |                       | -0.3                  | V <sub>DDD</sub> +0.3 | V    |

| Analog Ground Differential Voltage<br>(GND1 to ePad, GND2 to ePad or GND1 to GND2) <sup>2</sup> |                                         | $\Delta V_{GNDA}$     | -50                   | +50                   | mV   |

| Digital Ground Differential Voltage<br>(GND3 to GND4) <sup>2</sup>                              |                                         | $\Delta V_{GNDD}$     | -50                   | +50                   | mV   |

| Si3200                                                                                          |                                         |                       |                       |                       |      |

| Supply Voltage                                                                                  | V <sub>DD</sub>                         |                       | -0.5                  | 6.0                   | V    |

| High Battery Supply Voltage <sup>3</sup>                                                        | V <sub>BATH</sub>                       | Continuous            | -104                  | 0.4                   | V    |

|                                                                                                 |                                         | 10 ms                 | -109                  | 0.4                   | V    |

| Low Battery Supply Voltage                                                                      | V <sub>BAT</sub> ,<br>V <sub>BATL</sub> | Continuous            | V <sub>BATH</sub>     | 0.4                   | V    |

| TIP or RING Voltage                                                                             | V <sub>TIP</sub> ,                      | Continuous            | -104                  | 0.4                   | V    |

|                                                                                                 | V <sub>RING</sub>                       | Pulse < 10 us         | V <sub>BATH</sub> –15 | 0.4                   | V    |

|                                                                                                 |                                         | Pulse < 4 us          | V <sub>BATH</sub> –35 | 0.4                   | V    |

| TIP or RING Current                                                                             | I <sub>TIP</sub> , I <sub>RING</sub>    |                       | -100                  | +100                  | mA   |

| Si3202                                                                                          | 4                                       |                       | +                     | <u> </u>              |      |

| Supply Voltage                                                                                  | V <sub>DD</sub>                         |                       | -0.5                  | 6.0                   | V    |

Notes:

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded, and exposure to absolute maximum rating conditions for extended periods may affect device reliability. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet.

- 2. The PCB pad placed under the device package must be connected with multiple vias to the PCB ground layer and to the GND1-GND4 pins via short traces. The TQFP-64 e-Pad must be properly soldered to the PCB pad during PCB assembly. This type of low-impedance grounding arrangement is necessary to ensure that maximum differentials are not exceeded under any operating condition in addition to providing thermal dissipation.

- 3. On Si3200 revision E, the dv/dt of the voltage applied to the V<sub>BAT</sub>, V<sub>BATH</sub>, and V<sub>BATL</sub> pins must be limited to 10 V/µs.

- 4. Operation of the Si3220/Si3225 above 125 °C junction temperature may degrade device reliability. The Si3200/Si3202 should be operated at a junction temperature below 140 °C for optimal reliability.

- 5. The thermal resistance of an exposed pad package is assured when the recommended printed circuit board layout guidelines are followed correctly. The specified performance requires that the exposed pad be soldered to an exposed copper surface of equal size and that multiple vias are added to enable heat transfer between the top-side copper surface and a large internal copper ground plane. Refer to "AN55: Dual ProSLIC<sup>®</sup> User Guide" or to the Si3220/3225 evaluation board data sheet for specific layout examples.

| Parameter                                        | Symbol                                  | <b>Test Condition</b> | Min                   | Max  | Unit |

|--------------------------------------------------|-----------------------------------------|-----------------------|-----------------------|------|------|

| High Battery Supply Voltage                      | V <sub>BATH</sub>                       | Continuous            | -130                  | 0.4  | V    |

|                                                  |                                         | 10 ms                 | -135                  | 0.4  | V    |

| Low Battery Supply Voltage                       | V <sub>BAT</sub> ,<br>V <sub>BATL</sub> | Continuous            | V <sub>BATH</sub>     | 0.4  | V    |

| TIP or RING Voltage                              | V <sub>TIP</sub> ,                      | Continuous            | -130                  | 0.4  | V    |

|                                                  | V <sub>RING</sub>                       | Pulse < 10 us         | V <sub>BATH</sub> –15 | 0.4  | V    |

|                                                  |                                         | Pulse < 4 us          | V <sub>BATH</sub> –35 | 0.4  | V    |

| TIP or RING Current                              | I <sub>TIP</sub> , I <sub>RING</sub>    |                       | -100                  | +100 | mA   |

| Thermal Information                              |                                         | I                     | 11                    |      |      |

| Operating temperature (All devices) <sup>4</sup> |                                         |                       | -40                   | +100 | °C   |

| Storage temperature (All devices)                |                                         |                       | -40                   | +150 | °C   |

| Thermal Resistance (Si3220/Si3225) <sup>5</sup>  | $\theta_{JA}$                           | TQFP-64 ePad          | 25 (typical)          |      | °C/W |

| Thermal Resistance (Si3200/Si3202) <sup>5</sup>  | $\theta_{JA}$                           | SOIC-16 ePad          | 55 (typical)          |      | °C/W |

### Table 1. Absolute Maximum Ratings and Thermal Information<sup>1</sup> (Continued)

Notes:

1. Permanent device damage may occur if the absolute maximum ratings are exceeded, and exposure to absolute maximum rating conditions for extended periods may affect device reliability. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet.

2. The PCB pad placed under the device package must be connected with multiple vias to the PCB ground layer and to the GND1-GND4 pins via short traces. The TQFP-64 e-Pad must be properly soldered to the PCB pad during PCB assembly. This type of low-impedance grounding arrangement is necessary to ensure that maximum differentials are not exceeded under any operating condition in addition to providing thermal dissipation.

3. On Si3200 revision E, the dv/dt of the voltage applied to the  $V_{BAT}$ ,  $V_{BATH}$ , and  $V_{BATL}$  pins must be limited to 10 V/µs.

4. Operation of the Si3220/Si3225 above 125 °C junction temperature may degrade device reliability. The Si3200/Si3202 should be operated at a junction temperature below 140 °C for optimal reliability.

5. The thermal resistance of an exposed pad package is assured when the recommended printed circuit board layout guidelines are followed correctly. The specified performance requires that the exposed pad be soldered to an exposed copper surface of equal size and that multiple vias are added to enable heat transfer between the top-side copper surface and a large internal copper ground plane. Refer to "AN55: Dual ProSLIC<sup>®</sup> User Guide" or to the Si3220/3225 evaluation board data sheet for specific layout examples.

| Table 2. Recommended | <b>Operating Conditions</b> |

|----------------------|-----------------------------|

|----------------------|-----------------------------|

| Parameter                                                                                                                                                                                                                            | Symbol                             | Test<br>Condition | Min* | Тур     | Max*              | Unit |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|------|---------|-------------------|------|--|--|

| Ambient Temperature                                                                                                                                                                                                                  | T <sub>A</sub>                     | K/F-Grade         | 0    | 25      | 70                | °C   |  |  |

| Ambient Temperature                                                                                                                                                                                                                  | T <sub>A</sub>                     | B/G-Grade         | -40  | 25      | 85                | °C   |  |  |

| Supply Voltage, Si3220/Si3225                                                                                                                                                                                                        | V <sub>DD1</sub> –V <sub>DD4</sub> |                   | 3.13 | 3.3/5.0 | 5.25              | V    |  |  |

| Supply Voltage, Si3200/Si3202                                                                                                                                                                                                        | V <sub>DD</sub>                    |                   | 3.13 | 3.3/5.0 | 5.25              | V    |  |  |

| High Battery Supply Voltage, Si3200                                                                                                                                                                                                  | V <sub>BATH</sub>                  |                   | -15  |         | -99               | V    |  |  |

| Low Battery Supply Voltage, Si3200                                                                                                                                                                                                   | V <sub>BATL</sub>                  |                   | -15  |         | V <sub>BATH</sub> | V    |  |  |

| High Battery Supply Voltage, Si3202                                                                                                                                                                                                  | V <sub>BATH</sub>                  |                   | -15  |         | -125              | V    |  |  |

| Low Battery Supply Voltage, Si3202                                                                                                                                                                                                   | V <sub>BATL</sub>                  |                   | -15  |         | V <sub>BATH</sub> | V    |  |  |

| Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.<br>Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated. |                                    |                   |      |         |                   |      |  |  |

# Table 3. 3.3 V Power Supply Characteristics<sup>1</sup>

$(V_{DD}, V_{DD1} - V_{DD4} = 3.3 \text{ V}, T_A = 0 \text{ to } 70 \text{ }^{\circ}\text{C} \text{ for K/F-Grade}, -40 \text{ to } 85 \text{ }^{\circ}\text{C} \text{ for B/G-Grade})$

| Parameter                                 | Symbol                               | Test Condition                                                                                | Min | Тур                              | Мах                    | Unit |    |   |    |

|-------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|-----|----------------------------------|------------------------|------|----|---|----|

| V <sub>DD1</sub> –V <sub>DD4</sub> Supply | I <sub>VDD1</sub> –I <sub>VDD4</sub> | Sleep mode, RESET = 0                                                                         | _   | 200                              | _                      | μA   |    |   |    |

| Current (Si3220/<br>Si3225)               |                                      | Open (high-impedance)                                                                         | _   | 17                               | _                      | mA   |    |   |    |

|                                           | ,                                    |                                                                                               |     |                                  | Active on-hook standby | _    | 16 | _ | mA |

|                                           |                                      | Forward/reverse active off-hook                                                               | _   | 45 + I <sub>LIM</sub><br>+ ABIAS | _                      | mA   |    |   |    |

|                                           |                                      | Forward/reverse active OHT<br>OBIAS = 4 mA, V <sub>BAT</sub> = –70 V                          | _   | 47                               |                        | mA   |    |   |    |

|                                           |                                      | Ringing, $V_{RING}$ = 45 $V_{rms}$ , $V_{BAT}$ = -70 V,<br>Sine Wave, 1 REN load <sup>2</sup> | _   | 26                               |                        | mA   |    |   |    |

Notes:

1. All specifications are for a single channel based on measurements with both channels in the same operating state.

2. See "3.14.4. Ringing Power Considerations" on page 54 for current and power consumption under other operating conditions.

Power consumption does not include additional power required for dc loop feed. Total system power consumption must include an additional (V<sub>DD</sub> + |V<sub>BAT</sub>|) x I<sub>LOOP</sub> term.

# Table 3. 3.3 V Power Supply Characteristics<sup>1</sup> (Continued)

$(V_{DD}, V_{DD1} - V_{DD4} = 3.3 \text{ V}, T_A = 0 \text{ to } 70 \text{ }^{\circ}\text{C} \text{ for K/F-Grade}, -40 \text{ to } 85 \text{ }^{\circ}\text{C} \text{ for B/G-Grade})$

| Parameter                                     | Symbol            | Test Condition                                                                                           | Min | Тур                       | Мах | Unit |

|-----------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------|-----|---------------------------|-----|------|

| V <sub>DD</sub> Supply Current                | I <sub>VDD</sub>  | Sleep mode, RESET = 0                                                                                    |     | 110                       | _   | μA   |

| (Si3200/2)                                    |                   | Open (high-impedance)                                                                                    | —   | 110                       | —   | μA   |

|                                               |                   | Active on-hook standby                                                                                   | _   | 110                       | _   | μA   |

|                                               |                   | Forward/reverse active off-hook,<br>ABIAS = 4 mA, V <sub>BAT</sub> = -24 V                               | _   | 110                       | _   | μA   |

|                                               |                   | Forward/reverse OHT, OBIAS = 4 mA, $V_{BAT}$ = -70 V                                                     |     | 110                       | _   | μA   |

|                                               |                   | Ringing, V <sub>RING</sub> = 45 V <sub>rms</sub> ,<br>V <sub>BAT</sub> = -70 V,<br>Sine Wave, 1 REN load | _   | 110                       | _   | μA   |

| V <sub>BAT</sub> Supply Current<br>(Si3200/2) | I <sub>VBAT</sub> | Sleep mode, RESET=0,<br>V <sub>BAT</sub> = -70 V                                                         | —   | 100                       | —   | μA   |

|                                               |                   | Open (high-impedance),<br>V <sub>BAT</sub> = -70 V                                                       | _   | 189                       | —   | μA   |

|                                               |                   | Active on-hook standby,<br>V <sub>BAT</sub> = -70 V                                                      | _   | 517                       | —   | μA   |

|                                               |                   | Forward/reverse active off-hook,<br>ABIAS = 4 mA, V <sub>BAT</sub> = -24 V                               |     | 4.5 +<br>I <sub>LIM</sub> | —   | mA   |

|                                               |                   | Forward/reverse OHT, OBIAS = 4 mA, $V_{BAT}$ = -70 V                                                     | _   | 8.6                       | _   | mA   |

|                                               |                   | Ringing, $V_{RING}$ = 45 $V_{rms}$ ,<br>$V_{BAT}$ = -70 V,<br>Sine Wave, 1 REN load <sup>2</sup>         | _   | 6.5                       | —   | mA   |

Notes:

1. All specifications are for a single channel based on measurements with both channels in the same operating state.

2. See "3.14.4. Ringing Power Considerations" on page 54 for current and power consumption under other operating conditions.

Power consumption does not include additional power required for dc loop feed. Total system power consumption must include an additional (V<sub>DD</sub> + |V<sub>BAT</sub>|) x I<sub>LOOP</sub> term.

# Table 3. 3.3 V Power Supply Characteristics<sup>1</sup> (Continued)

$(V_{DD}, V_{DD1} - V_{DD4} = 3.3 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C for K/F-Grade}, -40 \text{ to } 85 \text{ °C for B/G-Grade})$

| Parameter                    | Symbol                           | Test Condition                                                                                          | Min | Тур | Мах | Unit |

|------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Chipset Power<br>Consumption | P <sub>SLEEP</sub>               | Sleep mode, RESET = 0,<br>V <sub>BAT</sub> = -70 V                                                      |     | 8   |     | mW   |

|                              | P <sub>OPEN</sub>                | Open (high-impedance), $V_{BAT}$ = -70 V                                                                | _   | 69  |     | mW   |

|                              | P <sub>STBY</sub>                | Active on-hook standby, $V_{BAT}$ = -70 V                                                               |     | 89  |     | mW   |

|                              | P <sub>ACTIVE</sub> <sup>3</sup> | Forward/reverse active off-hook,<br>ABIAS = 4 mA, V <sub>BAT</sub> = –24 V                              | _   | 267 | _   | mW   |

|                              | P <sub>OHT</sub>                 | Forward/reverse OHT, OBIAS = 4 mA, $V_{BAT}$ = -70 V                                                    | _   | 757 | _   | mW   |

|                              | P <sub>RING</sub>                | Ringing, V <sub>RING</sub> = 45 v <sub>rms</sub> ,<br>V <sub>BAT</sub> = -70 V, 1 REN load <sup>2</sup> | _   | 541 | _   | mW   |

Notes:

1. All specifications are for a single channel based on measurements with both channels in the same operating state.

2. See "3.14.4. Ringing Power Considerations" on page 54 for current and power consumption under other operating conditions.

3. Power consumption does not include additional power required for dc loop feed. Total system power consumption must include an additional ( $V_{DD}$  +  $|V_{BAT}|$ ) x I<sub>LOOP</sub> term.

## Table 4. 5 V Power Supply Characteristics<sup>1</sup>

$(V_{DD}, V_{DD1} - V_{DD4} = 5 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C for K/F-Grade}, -40 \text{ to } 85 \text{ °C for B/G-Grade})$

| Parameter                      | Symbol                               | Test Condition                                                                                          | Min | Тур                                 | Max | Unit |

|--------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-------------------------------------|-----|------|

| $V_{DD1} - V_{DD4}$ Supply     | I <sub>VDD1</sub> –I <sub>VDD4</sub> | Sleep mode, RESET = 0                                                                                   | _   | 1                                   |     | mA   |

| Current (Si3220/Si3225)        |                                      | Open (high-impedance)                                                                                   | _   | 22                                  |     | mA   |

|                                |                                      | Active on-hook standby                                                                                  | _   | 21                                  |     | mA   |

|                                |                                      | Forward/reverse active off-hook                                                                         |     | 62 +<br>I <sub>LIM</sub> +<br>ABIAS | _   | mA   |

|                                |                                      | Forward/reverse active OHT<br>OBIAS = 4 mA                                                              | _   | 65                                  | _   | mA   |

|                                |                                      | Ringing, V <sub>RING</sub> = 45 V <sub>rms</sub> ,<br>V <sub>BAT</sub> = –70 V, 1 REN load <sup>2</sup> | _   | 31                                  | —   | mA   |

| V <sub>DD</sub> Supply Current | I <sub>VDD</sub>                     | Sleep mode, RESET = 0                                                                                   | _   | 110                                 | —   | μA   |

| (Si3200/2)                     |                                      | Open (high-impedance)                                                                                   | _   | 110                                 | —   | μA   |

|                                |                                      | Active on-hook standby                                                                                  | _   | 110                                 | _   | μA   |

|                                |                                      | Forward/reverse active off-hook,<br>ABIAS = 4 mA, V <sub>BAT</sub> = –24 V                              |     | 110                                 | _   | μA   |

|                                |                                      | Forward/reverse OHT, OBIAS = 4 mA,<br>$V_{BAT}$ = -70 V                                                 |     | 110                                 | _   | μA   |

|                                |                                      | Ringing, V <sub>RING</sub> = 45 V <sub>rms</sub> ,<br>V <sub>BAT</sub> = -70 V,<br>1 REN load           |     | 110                                 |     | μA   |

#### Notes:

1. All specifications are for a single channel based on measurements with both channels in the same operating state.

2. See "3.14.4. Ringing Power Considerations" on page 54 for current and power consumption under other operating conditions.

3. Power consumption does not include additional power required for dc loop feed. Total system power consumption must include an additional ( $V_{DD}$  +  $|V_{BAT}|$ ) x I<sub>LOOP</sub> term.

# Table 4. 5 V Power Supply Characteristics<sup>1</sup> (Continued)

$(V_{DD}, V_{DD1} - V_{DD4} = 5 \text{ V}, \text{ T}_{A} = 0 \text{ to } 70 \text{ }^{\circ}\text{C} \text{ for K/F-Grade}, -40 \text{ to } 85 \text{ }^{\circ}\text{C} \text{ for B/G-Grade})$

| Parameter                                     | Symbol                           | Test Condition                                                                                          | Min | Тур                       | Мах | Unit |

|-----------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|-----|---------------------------|-----|------|

| V <sub>BAT</sub> Supply Current<br>(Si3200/2) | I <sub>VBAT</sub>                | Sleep mode, RESET = 0,<br>V <sub>BAT</sub> = -70 V                                                      | _   | 125                       |     | μA   |

|                                               |                                  | Open (high-impedance), $V_{BAT}$ = -70 V                                                                | _   | 190                       | _   | μA   |

|                                               |                                  | Active on-hook standby, $V_{BAT} = -70 \text{ V}$                                                       | _   | 700                       |     | μA   |

|                                               |                                  | Forward/reverse active off-hook,<br>ABIAS = 4 mA, V <sub>BAT</sub> = –24 V                              | _   | 4.7 +<br>I <sub>LIM</sub> |     | mA   |

|                                               |                                  | Forward/reverse OHT, OBIAS = 4 mA, $V_{BAT}$ = -70 V                                                    | _   | 8.8                       | _   | mA   |

|                                               |                                  | Ringing, $V_{RING}$ = 45 $V_{rms}$ ,<br>$V_{BAT}$ = -70 V,<br>1 REN load <sup>2</sup>                   | —   | 6.5                       | —   | mA   |

| Chipset Power<br>Consumption                  | P <sub>SLEEP</sub>               | Sleep mode, RESET = 0,<br>V <sub>BAT</sub> = -70 V                                                      | _   | 13.8                      | _   | mW   |

|                                               | P <sub>OPEN</sub>                | Open (high-impedance), $V_{BAT}$ = -70 V                                                                | _   | 123                       | _   | mW   |

|                                               | P <sub>STBY</sub>                | Active on-hook standby, $V_{BAT} = -70 \text{ V}$                                                       |     | 154                       |     | mW   |

|                                               | P <sub>ACTIVE</sub> <sup>3</sup> | Forward/reverse active off-hook,<br>ABIAS = 4 mA, V <sub>BAT</sub> = –24 V                              |     | 436                       | _   | mW   |

|                                               | P <sub>OHT</sub>                 | Forward/reverse OHT, OBIAS = 4 mA, $V_{BAT}$ = -70 V                                                    |     | 941                       |     | mW   |

|                                               | P <sub>RING</sub>                | Ringing, V <sub>RING</sub> = 45 V <sub>rms</sub> ,<br>V <sub>BAT</sub> = –70 V, 1 REN load <sup>2</sup> |     | 610                       | _   | mW   |

Notes:

1. All specifications are for a single channel based on measurements with both channels in the same operating state.

2. See "3.14.4. Ringing Power Considerations" on page 54 for current and power consumption under other operating conditions.

3. Power consumption does not include additional power required for dc loop feed. Total system power consumption must include an additional ( $V_{DD}$  +  $|V_{BAT}|$ ) x I<sub>LOOP</sub> term.

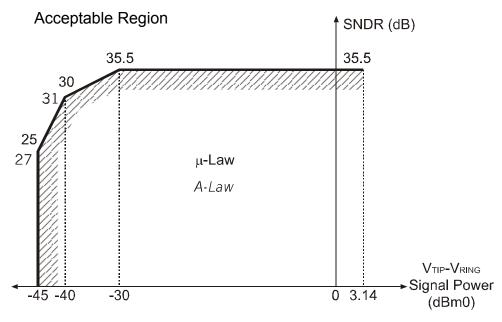

#### Table 5. AC Characteristics

(V<sub>DD</sub>, V<sub>DD1</sub> – V<sub>DD4</sub> = 3.13 to 5.25 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, -40 to 85 °C for B/G-Grade)

| Parameter                                                        | Test Condition                                                                        | Min        | Тур          | Max      | Unit            |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------|--------------|----------|-----------------|

|                                                                  | TX/RX Performance                                                                     | l          |              |          |                 |

| Overload Level                                                   |                                                                                       | 2.5        | _            | _        | V <sub>PK</sub> |

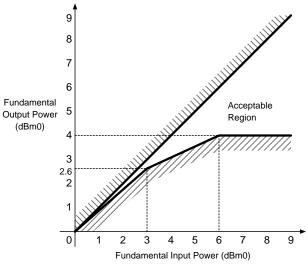

| Overload Compression                                             | 2-Wire – PCM                                                                          | Figure 6   | _            | _        |                 |

| Single Frequency Distortion <sup>1</sup>                         | 2-Wire – PCM or PCM – 2-Wire:<br>200 Hz to 3.4 kHz                                    | —          | -85          | -65      | dB              |

|                                                                  | PCM – 2-Wire – PCM:<br>200 Hz – 3.4 kHz,<br>16-bit Linear mode                        | —          | -87          | -65      | dB              |

| Signal-to-(Noise + Distortion)<br>Ratio <sup>2</sup>             | 200 Hz to 3.4 kHz<br>D/A or A/D 8-bit<br>Active off-hook, and OHT, any Z <sub>T</sub> | Figure 5   | _            |          |                 |

| Audio Tone Generator Signal-to-<br>Distortion Ratio <sup>2</sup> | 0 dBm0, Active off-hook, and<br>OHT, any Z <sub>T</sub>                               | 46         |              |          | dB              |

| Intermodulation Distortion                                       |                                                                                       | —          | _            | -41      | dB              |

| Gain Accuracy <sup>2</sup>                                       | 2-Wire to PCM or PCM to 2-Wire<br>1014 Hz, Any gain setting                           | -0.25      | _            | +0.25    | dB              |

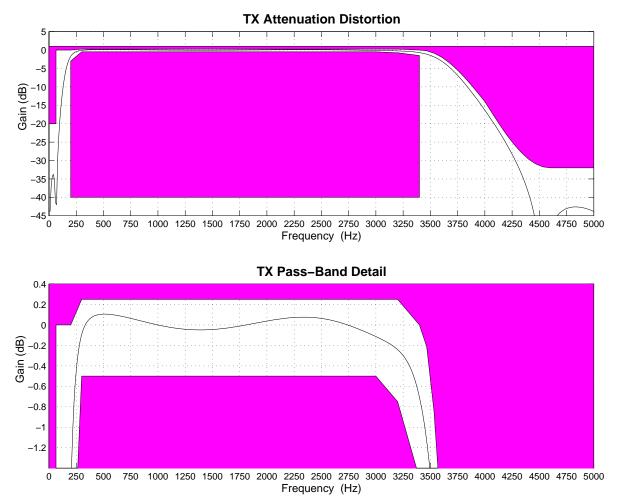

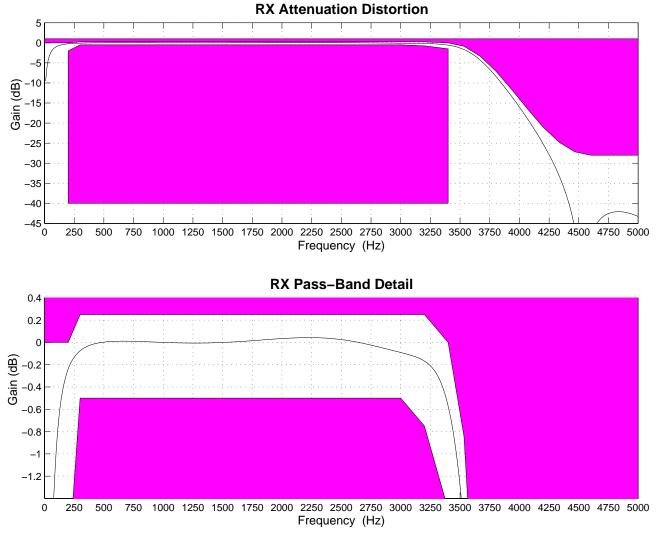

| Attenuation Distortion vs. Freq.                                 | 0 dBm 0                                                                               | Figure 7,8 | _            | _        | _               |

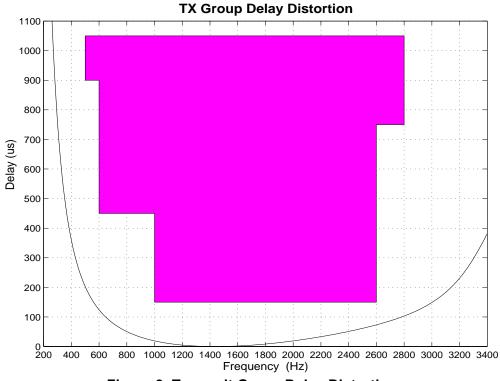

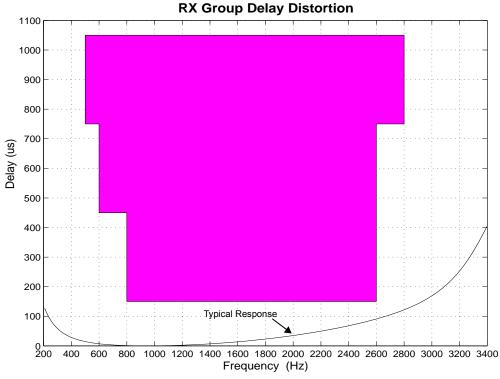

| Group Delay vs. Frequency                                        |                                                                                       | Figure 9   | —            | —        | _               |

| Gain Tracking <sup>3</sup>                                       | 1014 Hz sine wave,<br>reference level –10 dBm<br>Signal level:                        | _          | —            | —        |                 |

|                                                                  | 3 dB to –37 dB                                                                        | —          | —            | ± 0.25   | dB              |

|                                                                  | -37 dB to -50 dB                                                                      | _          | —            | ± 0.5    | dB              |

|                                                                  | –50 dB to –60 dB                                                                      | _          | —            | ± 1.0    | dB              |

| Round-Trip Group Delay                                           | 1014 Hz, Within same time-slot                                                        | —          | 600          | 700      | μs              |

| Crosstalk between Channels<br>TX or RX to TX<br>TX or RX to RX   | 0 dBm0,<br>300 Hz to 3.4 kHz<br>300 Hz to 3.4 kHz                                     |            | -108<br>-108 | 75<br>75 | dB<br>dB        |

| Gain Step Increment <sup>4</sup>                                 | Step size around 0 dB                                                                 | —          | ±0.0005      | _        | dB              |

| 2-Wire Return Loss <sup>5</sup>                                  | 200 Hz to 3.4 kHz                                                                     | 26         | 30           | _        | dB              |

| Transhybrid Balance <sup>5</sup>                                 | 300 Hz to 3.4 kHz                                                                     | 34         | 40           |          | dB              |

Notes:

The input signal level should be 0 dBm0 for frequencies greater than 100 Hz. For 100 Hz and below, the level should be –10 dBm0. The output signal magnitude at any other frequency will be smaller than the maximum value specified.

Analog signal massured as V = V = Assumes ideal line impedance matching

2. Analog signal measured as  $V_{TIP} - V_{RING}$ . Assumes ideal line impedance matching.

The quantization errors inherent in the μ/A-law companding process can generate slightly worse gain tracking performance in the signal range of 3 to –37 dB for signal frequencies that are integer divisors of the 8 kHz PCM sampling rate.

**4.** The digital gain block is a linear multiplier that is programmable from –∞ to +6 dB. The step size in dB varies over the complete range. See "3.25. Audio Path Processing" on page 70.

5.  $V_{DD1} - V_{DD4} = 3.3 \text{ V}$ ,  $V_{BAT} = -52 \text{ V}$ , no fuse resistors,  $R_L = 600 \Omega$ ,  $Z_S = 600 \Omega$  synthesized using RS register coefficients.

6. The level of any unwanted tones within the bandwidth of 0 to 4 kHz does not exceed –55 dBm.

7. The OBIAS and ABIAS registers program the dc bias current through the SLIC in the on-hook transmission and offhook active conditions, respectively. This per-pin total current setting should be selected so it can accommodate the sum of the metallic and longitudinal currents through each of the TIP and RING leads for a given application.

#### Table 5. AC Characteristics (Continued)

(V<sub>DD</sub>, V<sub>DD1</sub> – V<sub>DD4</sub> = 3.13 to 5.25 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                                 | Test Condition                                                                                                                  | Min      | Тур                  | Max  | Unit                 |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|------|----------------------|--|--|--|--|

| Noise Performance                         |                                                                                                                                 |          |                      |      |                      |  |  |  |  |

| Idle Channel Noise <sup>6</sup>           | C-Message weighted                                                                                                              |          | 12                   | 15   | dBrnC                |  |  |  |  |

|                                           | Psophometric weighted                                                                                                           | _        | -78                  | -75  | dBmP                 |  |  |  |  |

|                                           | 3 kHz flat                                                                                                                      | _        | —                    | 18   | dBrn                 |  |  |  |  |

| PSRR from $V_{DD1} - V_{DD4}$             | RX and TX, dc to 3.4 kHz                                                                                                        | 40       | _                    | —    | dB                   |  |  |  |  |

| PSRR from V <sub>BAT</sub>                | RX and TX, dc to 3.4 kHz                                                                                                        | 60       | _                    | —    | dB                   |  |  |  |  |

|                                           | Longitudinal Performance                                                                                                        |          |                      |      |                      |  |  |  |  |

| Longitudinal to Metallic/PCM              | 200 Hz to 1 kHz                                                                                                                 | 58       | 70                   | —    | dB                   |  |  |  |  |

| Balance (forward or reverse)              | 1 kHz to 3.4 kHz                                                                                                                | 53       | 58                   | —    | dB                   |  |  |  |  |

| Metallic/PCM to Longitudinal<br>Balance   | 200 Hz to 3.4 kHz                                                                                                               | 40       |                      | —    | dB                   |  |  |  |  |

| Longitudinal Impedance <sup>7</sup>       | 200 Hz to 3.4 kHz at TIP or RING<br>Register-dependent<br>OBIAS/ABIAS<br>00 = 4 mA<br>01 = 8 mA<br>10 = 12 mA<br>11 = 16 mA     | <br><br> | 50<br>25<br>25<br>20 | <br> | Ω<br>Ω<br>Ω          |  |  |  |  |

| Longitudinal Current per Pin <sup>7</sup> | Active off-hook<br>200 Hz to 3.4 kHz<br>Register-dependent<br>OBIAS/ABIAS<br>00 = 4 mA<br>01 = 8 mA<br>10 = 12 mA<br>11 = 16 mA | <br><br> | 4<br>8<br>8<br>10    |      | mA<br>mA<br>mA<br>mA |  |  |  |  |

Notes:

The input signal level should be 0 dBm0 for frequencies greater than 100 Hz. For 100 Hz and below, the level should be –10 dBm0. The output signal magnitude at any other frequency will be smaller than the maximum value specified.

2. Analog signal measured as  $V_{TIP} - V_{RING}$ . Assumes ideal line impedance matching.

The quantization errors inherent in the µ/A-law companding process can generate slightly worse gain tracking performance in the signal range of 3 to –37 dB for signal frequencies that are integer divisors of the 8 kHz PCM sampling rate.

**4.** The digital gain block is a linear multiplier that is programmable from –∞ to +6 dB. The step size in dB varies over the complete range. See "3.25. Audio Path Processing" on page 70.

- 5.  $V_{DD1} V_{DD4} = 3.3 \text{ V}$ ,  $V_{BAT} = -52 \text{ V}$ , no fuse resistors,  $R_L = 600 \Omega$ ,  $Z_S = 600 \Omega$  synthesized using RS register coefficients.

- 6. The level of any unwanted tones within the bandwidth of 0 to 4 kHz does not exceed –55 dBm.

- 7. The OBIAS and ABIAS registers program the dc bias current through the SLIC in the on-hook transmission and offhook active conditions, respectively. This per-pin total current setting should be selected so it can accommodate the sum of the metallic and longitudinal currents through each of the TIP and RING leads for a given application.

#### **Table 6. Linefeed Characteristics**

(V<sub>DD</sub>, V<sub>DD1</sub> – V<sub>DD4</sub> = 3.13 to 5.25 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                                                          | Symbol            | Test Condition                                                                                                  | Min  | Тур  | Max  | Unit            |

|--------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-----------------|

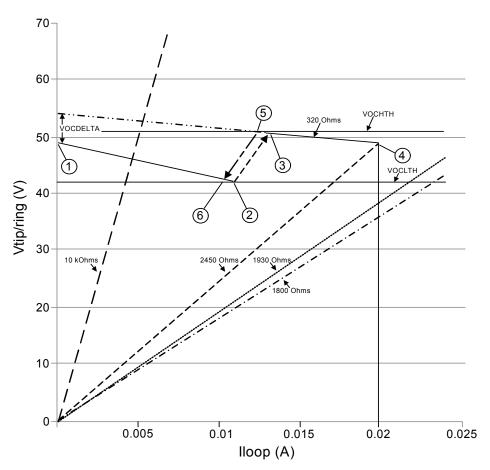

| Maximum Loop Resistance (adaptive linefeed disabled <sup>1</sup> ) | R <sub>LOOP</sub> | $R_{DC,MAX}^2$ = 430 Ω,<br>I <sub>LOOP</sub> = 18 mA, V <sub>BAT</sub> = -52 V,<br>ABIAS = 8 mA<br>VOCDELTA = 0 | 1870 |      |      | Ω               |

| Maximum Loop Resistance (adaptive linefeed enabled <sup>1</sup> )  | R <sub>LOOP</sub> | $R_{DC,MAX}^2$ = 430 Ω,<br>I <sub>LOOP</sub> = 18 mA, V <sub>BAT</sub> = -52 V,<br>ABIAS = 8 mA<br>VOCDELTA ≠ 0 | 2030 |      |      | Ω               |

| DC Loop Current Accuracy                                           |                   | I <sub>LIM</sub> = 18 mA                                                                                        |      |      | ±10  | %               |

| DC Open Circuit Voltage Accuracy                                   |                   | Active Mode; $V_{OC}$ = 48 V,<br>$V_{TIP} - V_{RING}$                                                           |      |      | ±4   | V               |

| DC Differential Output Resistance                                  | R <sub>DO</sub>   | I <sub>LOOP</sub> < I <sub>LIM</sub>                                                                            |      | 320  |      | Ω               |

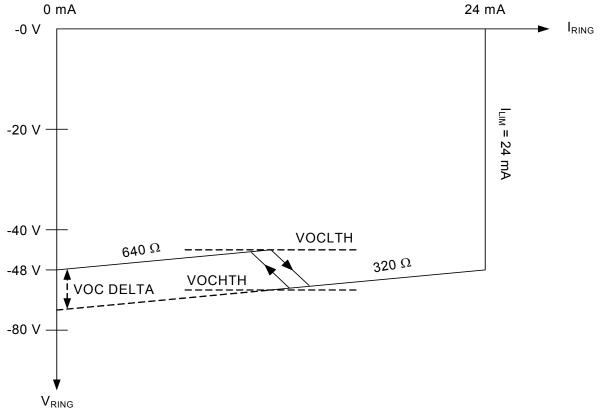

| DC On-Hook Voltage Accuracy—Ground<br>Start                        | V <sub>OHTO</sub> | $I_{RING}$ < $I_{LIM}$ ; $V_{RING}$ wrt ground,<br>$V_{RING}$ = -51 V                                           |      |      | ±4   | V               |

| DC Output Resistance—Ground Start                                  | R <sub>ROTO</sub> | I <sub>RING</sub> <i<sub>LIM; RING to ground</i<sub>                                                            |      | 320  | _    | Ω               |

| DC Output Resistance—Ground Start                                  | R <sub>TOTO</sub> | TIP to ground                                                                                                   | 300  |      |      | kΩ              |

| Loop Closure Detect Threshold Accuracy                             |                   | I <sub>THR</sub> = 13 mA                                                                                        | _    | ±10  | ±15  | %               |

| Ground Key Detect Threshold Accuracy                               |                   | I <sub>THR</sub> = 13 mA                                                                                        | _    | ±10  | ±15  | %               |

| Ring Trip Threshold Accuracy                                       |                   | Si3220, ac detection,<br>VRING = 70 Vpk, no offset,<br>I <sub>TH</sub> = 80 mA                                  |      | ±4   | ±5   | mA              |

|                                                                    |                   | Si3220, dc detection,<br>20 V dc offset, I <sub>TH</sub> = 13 mA                                                |      | ±1.5 | ±2   | mA              |

|                                                                    |                   | Si3225, dc detection,<br>48 V dc offset, $R_{loop}$ = 1500 $\Omega$                                             |      |      | ±4.5 | mA              |

| Ringing Amplitude, Si3220 <sup>3</sup>                             | V <sub>RING</sub> | Open circuit, V <sub>BATH</sub> = 100 V                                                                         | 93   | _    |      | V <sub>PK</sub> |

|                                                                    |                   | 5 REN load, R <sub>LOOP</sub> = 0 $\Omega$ ,<br>V <sub>BATH</sub> = 100 V                                       | 82   |      |      | V <sub>PK</sub> |

| Sinusoidal Ringing Total<br>Harmonic Distortion                    | R <sub>THD</sub>  |                                                                                                                 |      | 2    |      | %               |

| Ringing Frequency Accuracy                                         |                   | f = 16 Hz to 100 Hz                                                                                             |      | —    | ±1   | %               |

| Ringing Cadence Accuracy                                           |                   | Accuracy of ON/OFF times                                                                                        | —    | —    | ±50  | ms              |

| Calibration Time                                                   |                   | ↑CAL to ↓CAL bit                                                                                                |      | —    | 600  | ms              |

Notes:

1. Adaptive linefeed is enabled when the VOCDELTA RAM address is set to a non-zero value and is disabled when VOCDELTA is set to 0.

R<sub>DC,MAX</sub> is the maximum dc resistance of the CPE; hence the specified total loop resistance is R<sub>LOOP</sub> + R<sub>DC,MAX</sub>.

Ringing amplitude is set for 93 V peak using the RINGAMP RAM address and measured at TIP-RING using no series protection resistance.

#### Table 6. Linefeed Characteristics (Continued)

(V<sub>DD</sub>, V<sub>DD1</sub> – V<sub>DD4</sub> = 3.13 to 5.25 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                      | Symbol | Test Condition                                                                                 | Min | Тур | Max | Unit |

|--------------------------------|--------|------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Loop Voltage Sense Accuracy    |        | Accuracy of boundaries for<br>each output code;<br>V <sub>TIP</sub> – V <sub>RING</sub> = 48 V | _   | ±2  | ±4  | %    |

| Loop Current Sense Accuracy    |        | Accuracy of boundaries for<br>each output code;<br>I <sub>LOOP</sub> = 18 mA                   | _   | ±7  | ±10 | %    |

| Power Alarm Threshold Accuracy |        | Power Threshold = 300 mW                                                                       | —   | _   | ±25 | %    |

Notes:

1. Adaptive linefeed is enabled when the VOCDELTA RAM address is set to a non-zero value and is disabled when VOCDELTA is set to 0.

- 2.  $R_{DC,MAX}$  is the maximum dc resistance of the CPE; hence the specified total loop resistance is  $R_{LOOP}$  +  $R_{DC,MAX}$ .

- 3. Ringing amplitude is set for 93 V peak using the RINGAMP RAM address and measured at TIP-RING using no series protection resistance.

#### Table 7. Monitor ADC Characteristics

(V<sub>DD</sub>, V<sub>DD1</sub>–V<sub>DD4</sub> = 3.13 to 5.25 V,  $T_A$  = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                 | Symbol | Test Condition | Min  | Тур   | Max   | Unit       |

|---------------------------|--------|----------------|------|-------|-------|------------|

| Resolution                |        |                | —    | 8     | —     | Bits       |

| Differential Nonlinearity | DNL    |                | -1.0 | ±0.75 | +1.5  | LSB<br>LSB |

| Integral Nonlinearity     | INL    |                | —    | ±0.6  | ±1.5  | LSB        |

| Gain Error                |        |                | —    | ±0.1  | ±0.25 | LSB        |

#### Table 8. Si3200/2 Characteristics

(V<sub>DD</sub> = 3.13 to 5.25 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                                                                                                                            | Symbol           | Test Condition                                                                                  | Min | Тур | Мах | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| TIP/RING Pulldown Transistor Satura-<br>tion Voltage                                                                                 | V <sub>OV</sub>  | V <sub>RING</sub> – V <sub>BAT</sub> (Forward)<br>V <sub>TIP</sub> – V <sub>BAT</sub> (Reverse) |     |     |     |      |

|                                                                                                                                      |                  | $I_{LIM}$ = 22 mA, $I_{ABIAS}$ = 4 mA <sup>1</sup>                                              |     | 3   |     | V    |

|                                                                                                                                      |                  | I <sub>LIM</sub> = 45 mA,<br>I <sub>ABIAS</sub> = 16 mA <sup>1</sup>                            | —   | 4   | _   | V    |

| TIP/RING Pullup Transistor<br>Saturation Voltage                                                                                     | V <sub>CM</sub>  | GND – V <sub>TIP</sub> (Forward)<br>GND – V <sub>RING</sub> (Reverse)                           |     |     |     |      |

|                                                                                                                                      |                  | I <sub>LIM</sub> = 22 mA <sup>1</sup>                                                           | —   | 3   |     | V    |

|                                                                                                                                      |                  | I <sub>LIM</sub> = 45 mA <sup>1</sup>                                                           |     | 4   | —   | V    |

| Battery Switch Saturation<br>Impedance                                                                                               | R <sub>SAT</sub> | (V <sub>BAT</sub> – V <sub>BATH</sub> )/I <sub>OUT</sub> (Note 2)                               |     | 15  |     | Ω    |

| OPEN State TIP/RING Leakage Current                                                                                                  | I <sub>LKG</sub> | R <sub>L</sub> = 0 Ω                                                                            |     |     | 100 | μA   |

| Internal Blocking Diode Forward Voltage                                                                                              | V <sub>F</sub>   | V <sub>BAT</sub> – V <sub>BATL</sub> (Note 2)                                                   |     | 0.8 |     | V    |

| <b>Notes:</b><br><b>1.</b> V <sub>AC</sub> = 2.5 V <sub>PK</sub> , R <sub>LOAD</sub> = 600 Ω.<br><b>2.</b> I <sub>OUT</sub> = 60 mA. |                  |                                                                                                 |     |     |     |      |

# Table 9. DC Characteristics ( $V_{DD}$ , $V_{DD1}$ – $V_{DD4}$ = 5 V)

(V<sub>DD</sub>, V<sub>DD1</sub> – V<sub>DD4</sub> = 4.75 to 5.25 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                             | Symbol           | Test Condition                                                            | Min                   | Тур | Max                   | Unit |

|---------------------------------------|------------------|---------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| High Level Input<br>Voltage           | V <sub>IH</sub>  |                                                                           | 0.7 x V <sub>DD</sub> | —   | 5.25                  | V    |

| Low Level Input<br>Voltage            | V <sub>IL</sub>  |                                                                           | —                     | _   | 0.3 x V <sub>DD</sub> | V    |

| High Level Output<br>Voltage          | V <sub>OH</sub>  | I <sub>O</sub> = 8 mA                                                     | V <sub>DD</sub> – 0.6 | —   | _                     | V    |

| Low Level Output<br>Voltage           | V <sub>OL</sub>  | DTX, SDO, <del>INT</del> , SDITHRU:<br>I <sub>O</sub> = –8 mA             | —                     | —   | 0.4                   | V    |

|                                       |                  | BATSELa/b, RRDa/b,<br>GPOa/b, TRD1a/b,TRD2a/b:<br>I <sub>O</sub> = -40 mA | _                     | _   | 0.72                  | V    |

| SDITHRU Internal<br>Pullup Resistance |                  |                                                                           | 20                    | 30  | _                     | kΩ   |

| Relay Driver Source<br>Impedance      | R <sub>OUT</sub> | V <sub>DD1</sub> –V <sub>DD4</sub> = 4.75 V<br>I <sub>O</sub> < 28 mA     | —                     | 63  | _                     | Ω    |

| Relay Driver Sink<br>Impedance        | R <sub>IN</sub>  | V <sub>DD1</sub> –V <sub>DD4</sub> = 4.75 V<br>I <sub>O</sub> < 85 mA     | —                     | 11  | —                     | Ω    |

| Input Leakage Current                 | ١L               |                                                                           | —                     |     | ±10                   | μA   |

# Table 10. DC Characteristics ( $V_{DD}$ , $V_{DD1}$ – $V_{DD4}$ = 3.3 V)

(V<sub>DD</sub>, V<sub>DD1</sub> – V<sub>DD4</sub> = 3.13 to 3.47 V, T<sub>A</sub> = 0 to 70 °C for K/F-Grade, –40 to 85 °C for B/G-Grade)

| Parameter                          | Symbol           | Test Condition                                                             | Min                   | Тур | Max                   | Unit |

|------------------------------------|------------------|----------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| High Level Input Voltage           | V <sub>IH</sub>  |                                                                            | 0.7 x V <sub>DD</sub> | _   | 5.25                  | V    |

| Low Level Input Voltage            | V <sub>IL</sub>  |                                                                            | —                     |     | 0.3 x V <sub>DD</sub> | V    |

| High Level Output<br>Voltage       | V <sub>OH</sub>  | I <sub>O</sub> = 4 mA                                                      | V <sub>DD</sub> – 0.6 | _   | —                     | V    |

| Low Level Output<br>Voltage        | V <sub>OL</sub>  | DTX, SDO, ĪNT,<br>SDITHRU:<br>I <sub>O</sub> = –4 mA                       | _                     | _   | 0.4                   | V    |

|                                    |                  | BATSELa/b, RRDa/b,<br>GPOa/b, TRD1a/b, TRD2a/b:<br>I <sub>O</sub> = –40 mA | _                     | _   | 0.72                  |      |

| SDITHRU internal pullup resistance |                  |                                                                            | 35                    | 50  | —                     | kΩ   |

| Relay Driver Source Imped-<br>ance | R <sub>OUT</sub> | V <sub>DD1</sub> –V <sub>DD4</sub> = 3.13 V<br>IO < 28 mA                  | —                     | 63  | —                     | Ω    |

| Relay Driver Sink Impedance        | R <sub>IN</sub>  | V <sub>DD1</sub> -V <sub>DD4</sub> = 3.13 V<br>IO < 85 mA                  | —                     | 11  | —                     | Ω    |

| Input Leakage Current              | ١ <sub>L</sub>   |                                                                            | —                     | _   | ±10                   | μA   |

## Table 11. Switching Characteristics—General Inputs<sup>1</sup>

$(V_{DD}, V_{DD1} - V_{DD4} = 3.13 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C for K/F-Grade}, -40 \text{ to } 85 \text{ °C for B/G-Grade}, C_L = 20 \text{ pF})$

| Parameter                                | Symbol          | Min | Тур | Мах | Unit |

|------------------------------------------|-----------------|-----|-----|-----|------|

| Rise Time, RESET                         | t <sub>r</sub>  | —   | —   | 5   | ns   |

| RESET Pulse Width, GCI Mode <sup>2</sup> | t <sub>rl</sub> | 500 |     | —   | ns   |

| RESET Pulse Width, SPI Daisy Chain Mode  | t <sub>rl</sub> | 6   |     |     | μs   |

Notes:

All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels are V<sub>IH</sub> = V<sub>DD</sub> – 0.4 V, V<sub>II</sub> = 0.4 V. Rise and Fall times are referenced to the 20% and 80% levels of the waveform.

2. The minimum RESET pulse width assumes the SDITHRU pin is tied to ground via a pulldown resistor no greater than 10 k $\Omega$  per device.

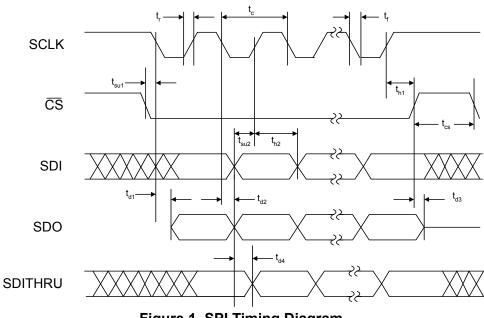

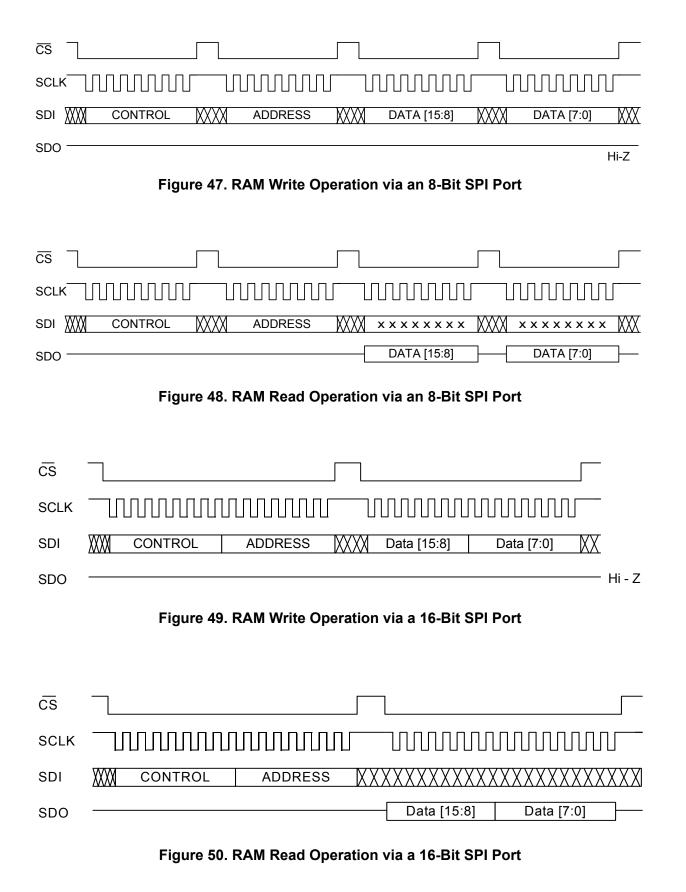

#### Table 12. Switching Characteristics—SPI

$(V_{DD}, V_{DD1} - V_{DD4} = 3.13 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C for K/F-Grade}, -40 \text{ to } 85 \text{ °C for B/G-Grade}, C_L = 20 \text{ pF})$

| Parameter <sup>1</sup>                                   | Symbol           | Test Conditions | Min | Тур | Max | Unit |

|----------------------------------------------------------|------------------|-----------------|-----|-----|-----|------|

| Cycle Time SCLK <sup>2</sup>                             | t <sub>c</sub>   |                 | 62  |     |     | ns   |

| Rise Time, SCLK                                          | t <sub>r</sub>   |                 |     |     | 25  | ns   |

| Fall Time, SCLK                                          | t <sub>f</sub>   |                 | _   | _   | 25  | ns   |

| Delay Time, SCLK Fall to SDO Active                      | t <sub>d1</sub>  |                 | _   | _   | 20  | ns   |

| Delay Time, SCLK Fall to SDO<br>Transition               | t <sub>d2</sub>  |                 | —   | —   | 20  | ns   |

| Delay Time, $\overline{\text{CS}}$ Rise to SDO Tri-state | t <sub>d3</sub>  |                 | —   | _   | 20  | ns   |

| Setup Time, CS to SCLK Fall                              | t <sub>su1</sub> |                 | 25  | _   | _   | ns   |

| Hold Time, $\overline{CS}$ to SCLK Rise                  | t <sub>h1</sub>  |                 | 20  | _   | _   | ns   |

| Setup Time, SDI to SCLK Rise                             | t <sub>su2</sub> |                 | 25  | _   | _   | ns   |

| Hold Time, SDI to SCLK Rise                              | t <sub>h2</sub>  |                 | 20  | _   | _   | ns   |

| Delay Time between Chip Selects                          | t <sub>cs</sub>  |                 | 220 | _   | _   | ns   |

| SDI to SDITHRU Propagation Delay                         | t <sub>d4</sub>  |                 | _   | 4   | 10  | ns   |

#### Notes:

1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_{DDD} - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$

2. The minimum SCLK cycle time is based on a single Si3220 connected to the SPI bus. If multiple Si3220s are connected to the same SPI bus, please contact a Silicon Laboratories representative for the recommended minimum SCLK cycle time for your application.

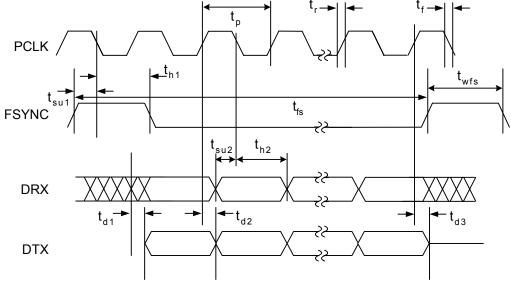

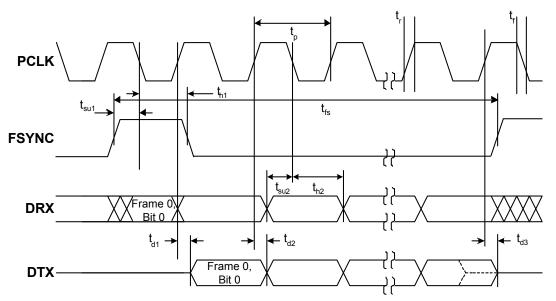

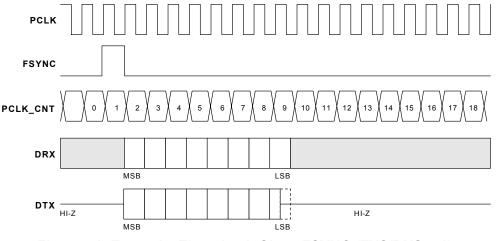

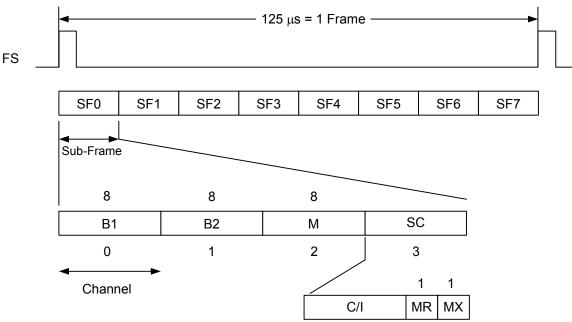

#### Table 13. Switching Characteristics—PCM Highway Interface

$(V_{DD}, V_{DD1} - V_{DD4} = 3.13 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C for K/F-Grade}, -40 \text{ to } 85 \text{ °C for B/G-Grade}, C_L = 20 \text{ pF})$

| Parameter                                             | Symbol              | Test<br>Conditions | Min <sup>1</sup>  | Typ <sup>1</sup>                                                        | Max <sup>1</sup>      | Units                                                |

|-------------------------------------------------------|---------------------|--------------------|-------------------|-------------------------------------------------------------------------|-----------------------|------------------------------------------------------|

| PCLK Period                                           | t <sub>p</sub>      |                    | 122               | —                                                                       | 3906                  | ns                                                   |

| Valid PCLK Inputs                                     |                     |                    |                   | 256<br>512<br>768<br>1.024<br>1.536<br>1.544<br>2.048<br>4.096<br>8.192 |                       | kHz<br>kHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz |

| FSYNC Period <sup>2</sup>                             | t <sub>fs</sub>     |                    | _                 | 125                                                                     |                       | μs                                                   |

| PCLK Duty Cycle Tolerance                             | t <sub>dty</sub>    |                    | 40                | 50                                                                      | 60                    | %                                                    |

| PCLK Period Jitter Tolerance                          | t <sub>jitter</sub> |                    | —                 | —                                                                       | ±120                  | ns                                                   |

| Rise Time, PCLK                                       | t <sub>r</sub>      |                    | —                 | —                                                                       | 25                    | ns                                                   |

| Fall Time, PCLK                                       | t <sub>f</sub>      |                    | —                 | —                                                                       | 25                    | ns                                                   |

| Delay Time, PCLK Rise to DTX Active                   | t <sub>d1</sub>     |                    | —                 | —                                                                       | 20                    | ns                                                   |

| Delay Time, PCLK Rise to DTX<br>Transition            | t <sub>d2</sub>     |                    | _                 | _                                                                       | 20                    | ns                                                   |

| Delay Time, PCLK Rise to DTX<br>Tristate <sup>3</sup> | t <sub>d3</sub>     |                    | _                 | _                                                                       | 20                    | ns                                                   |

| Setup Time, FSYNC to PCLK Fall                        | t <sub>su1</sub>    |                    | 25                | —                                                                       |                       | ns                                                   |

| Hold Time, FSYNC to PCLK Fall                         | t <sub>h1</sub>     |                    | 20                |                                                                         |                       | ns                                                   |

| Setup Time, DRX to PCLK Fall                          | t <sub>su2</sub>    |                    | 25                | —                                                                       | —                     | ns                                                   |

| Hold Time, DRX to PCLK Fall                           | t <sub>h2</sub>     |                    | 20                | —                                                                       | —                     | ns                                                   |

| FSYNC Pulse Width                                     | t <sub>wfs</sub>    |                    | t <sub>p</sub> /2 | —                                                                       | 125 µs–t <sub>p</sub> |                                                      |

Notes:

1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} - V_{I/O} - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ .

2. FSYNC source is assumed to be 8 kHz under all operating conditions.

3. Specification applies to PCLK fall to DTX tristate when that mode is selected.

Figure 2. PCM Highway Interface Timing Diagram

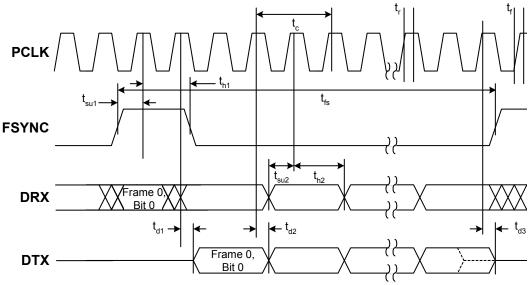

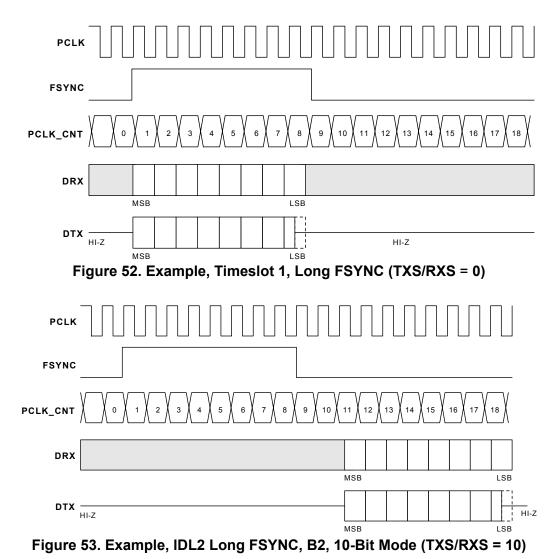

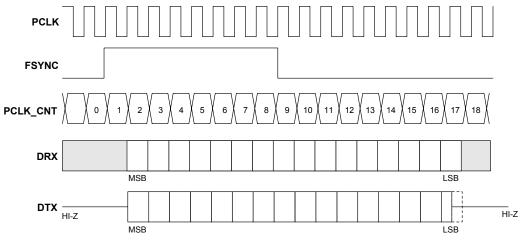

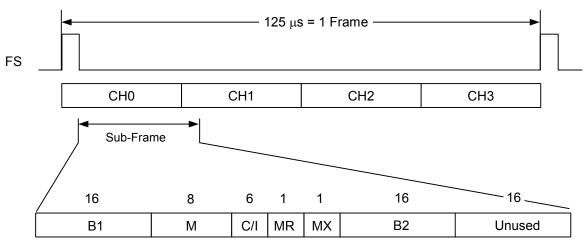

## Table 14. Switching Characteristics—GCI Highway Serial Interface

$(V_{DD}, V_{DD1} - V_{DD4} = 3.13 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70 \text{ }^{\circ}\text{C} \text{ for K/F-Grade}, -40 \text{ to } 85 \text{ }^{\circ}\text{C} \text{ for B/G-Grade})$

| Parameter <sup>1</sup>                             | Symbol              | Test<br>Conditions | Min               | Тур | Мах  | Units |

|----------------------------------------------------|---------------------|--------------------|-------------------|-----|------|-------|

| PCLK Period (2.048 MHz PCLK Mode)                  | t <sub>p</sub>      |                    | _                 | 488 | —    | ns    |

| PCLK Period (4.096 MHz PCLK Mode)                  | t <sub>p</sub>      |                    | _                 | 244 | _    | ns    |

| FSYNC Period <sup>2</sup>                          | t <sub>fs</sub>     |                    | _                 | 125 | —    | μs    |

| PCLK Duty Cycle Tolerance                          | t <sub>dty</sub>    |                    | 40                | 50  | 60   | %     |

| FSYNC Jitter Tolerance                             | t <sub>jitter</sub> |                    | _                 | —   | ±120 | ns    |

| Rise Time, PCLK                                    | t <sub>r</sub>      |                    |                   | —   | 25   | ns    |

| Fall Time, PCLK                                    | t <sub>f</sub>      |                    | _                 |     | 25   | ns    |

| Delay Time, PCLK Rise to DTX Active                | t <sub>d1</sub>     |                    | _                 | —   | 20   | ns    |

| Delay Time, PCLK Rise to DTX Transition            | t <sub>d2</sub>     |                    |                   | _   | 20   | ns    |

| Delay Time, PCLK Rise to DTX Tristate <sup>3</sup> | t <sub>d3</sub>     |                    | _                 |     | 20   | ns    |

| Setup Time, FSYNC Rise to PCLK Fall                | t <sub>su1</sub>    |                    | 25                | _   | —    | ns    |

| Hold Time, PCLK Fall to FSYNC Fall                 | t <sub>h1</sub>     |                    | 20                | _   | —    | ns    |

| Setup Time, DRX Transition to PCLK Fall            | t <sub>su2</sub>    |                    | 25                | _   | _    | ns    |

| Hold Time, PCLK Falling to DRX Transition          | t <sub>h2</sub>     |                    | 20                | —   | —    | ns    |

| FSYNC Pulse Width                                  | t <sub>wfs</sub>    |                    | t <sub>p</sub> /2 | —   | —    | ns    |

| Netee                                              |                     |                    |                   |     |      |       |

Notes:

1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_O - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ , rise and fall times are referenced to the 20% and 80% levels of the waveform.

2. FSYNC source is assumed to be 8 kHz under all operating conditions.

3. Specification applies to PCLK fall to DTX tristate when that mode is selected.

Figure 3. GCI Highway Interface Timing Diagram (2.048 MHz PCLK Mode)

Figure 4. GCI Highway Interface Timing Diagram (4.096 MHz PCLK Mode)

Figure 6. Overload Compression Performance

Figure 7. Transmit Path Frequency Response

Figure 8. Receive Path Frequency Response

### Figure 10. Receive Group Delay Distortion

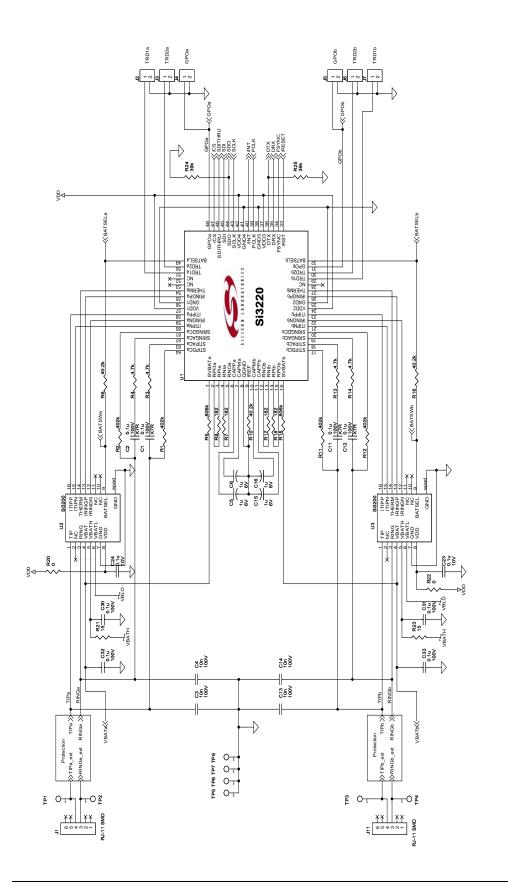

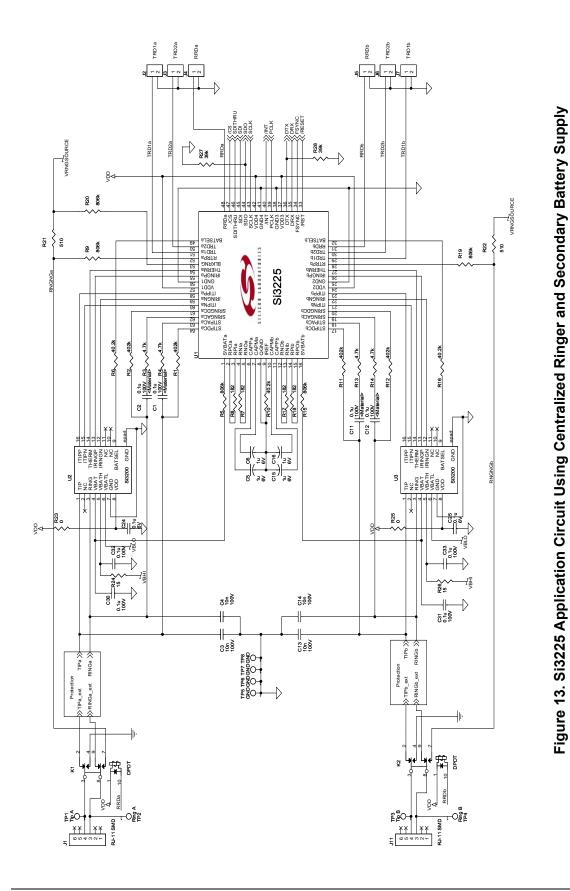

Figure 12. Si3220 Application Circuit Using Dual Battery Supply

# 2. Bill of Materials

| Component             | Value                    | Function                                                                                  |

|-----------------------|--------------------------|-------------------------------------------------------------------------------------------|

| C1, C2, C11, C12      | 100 nF, 100 V, X7R, ±20% | Filter capacitors for TIP, RING ac-sensing inputs.                                        |

| C3, C4, C13, C14      | 10 nF, 100 V, X7R, ±20%  | TIP/RING compensation capacitors.                                                         |

| C5, C6, C15, C16      | 1 μF, 6.3 V, X7R, ±20%   | Low-pass filter capacitors to stabilize differential and common-mode SLIC feedback loops. |

| C30–C33               | 0.1 µF, 100 V, Y5V       | Decoupling for battery voltage supply pins.                                               |

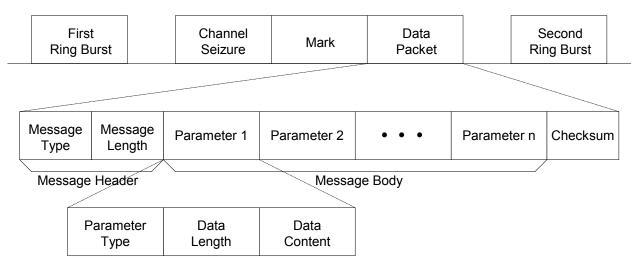

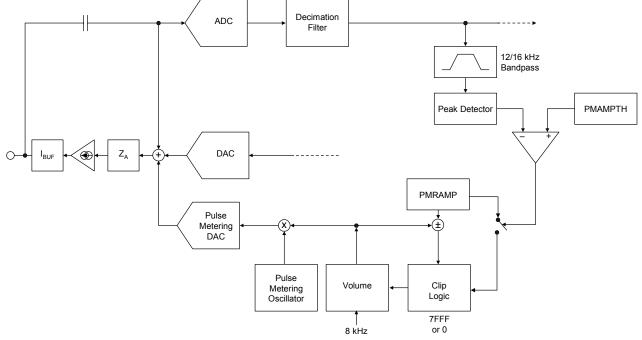

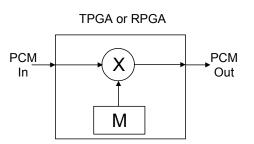

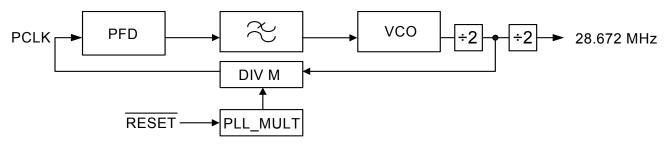

| C20–C25               | 0.1 µF, 10 V, Y5V        | Decoupling for analog and digital chip supply pins.                                       |