|                                                           |                                                                               |               |                |                |                       |                       |      | RE    | VISI         | ons        |            |                      |             |       |         |                   |    |           |       |      |

|-----------------------------------------------------------|-------------------------------------------------------------------------------|---------------|----------------|----------------|-----------------------|-----------------------|------|-------|--------------|------------|------------|----------------------|-------------|-------|---------|-------------------|----|-----------|-------|------|

| LTR                                                       |                                                                               |               |                |                | Di                    | ESCRI                 | PTIO | N     |              |            |            |                      | D           | ATE ( | YR-MO   | -DA)              |    | APPRO     | OVED  |      |

| A                                                         | to 1                                                                          | para;<br>rect | grapl<br>ed d: | n 1.2<br>imens | 2.2.,<br>sions        | to<br>1.4<br>on<br>Re | ., a | nd to | able<br>line | I.<br>X. M | lade       |                      |             | 93.   | -08-    | L9                | ĸ. | Cott      | congi | Lm   |

|                                                           |                                                                               |               |                |                |                       |                       |      |       |              |            |            |                      |             |       |         |                   |    |           |       |      |

| REV                                                       |                                                                               |               |                |                |                       |                       |      |       |              |            |            |                      |             |       |         |                   |    |           |       |      |

| SHEET                                                     |                                                                               |               |                |                |                       |                       |      |       |              |            |            |                      |             |       |         |                   |    |           |       |      |

| REV                                                       | A                                                                             | A             | A              | A              | A                     | A                     | A    | A     | A            | A          | А          |                      |             |       |         |                   |    |           |       |      |

| SHEET                                                     | 15                                                                            | 16            | 17             | 18             | 19                    | 20                    | 21   | 22    | 23           | 24         | 25         |                      |             |       |         |                   |    |           |       |      |

| REV STAT                                                  |                                                                               |               |                | RE             | v                     |                       | A    | A     | A            | A          | A          | A                    | A           | A     | A       | A                 | A  | A         | Α     | A    |

| PMIC N/A                                                  |                                                                               |               |                | PREP           | EET ARED E            |                       | 1    | 2     | 3            | 4<br>D1    | 5<br>EFENS |                      |             |       |         | 10<br>PPLY<br>454 |    | 12<br>TER | 13    | . 14 |

| STANDARDIZED  MILITARY  DRAWING  CHECKED BY Michael Jones |                                                                               |               |                |                | MT/                   | מפר                   |      | -     |              |            |            |                      | STD-        | 155   |         |                   |    |           |       |      |

| THIS DRAWII<br>FOR USE BY                                 | THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS  APPROVED BY Alan Barone |               |                |                |                       | ANI                   | D MI | L-S   | rD-1         | 760        | , во       | C, M<br>C/RT<br>C, H | U/MT        | Γ,    | * ~ ~ . |                   |    |           |       |      |

| DEPARTME                                                  | ENCIES OF THE DRAWING APPROVAL DATE 92-03-18                                  |               |                |                | SIZE CAGE CODE 5962-9 |                       |      | 917   | 34           |            |            |                      |             |       |         |                   |    |           |       |      |

| AMSC N/                                                   | A                                                                             |               |                | REVI           | ISION I               | LEVEL                 |      |       |              | SH         | EET        | 1 (                  | 67268 or 25 |       |         | ;                 |    |           |       |      |

DESC FORM 193

JUL 91

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E**3**89-93

**3** 9004708 0011436 186 **3**

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). This drawing describes device requirements for hybrid microcircuits to be processed in accordance with MIL-H-38534. Two product assurance classes, military high reliability (device class H) and space application (device class K) and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of radiation hardness assurance levels are reflected in the PIN.

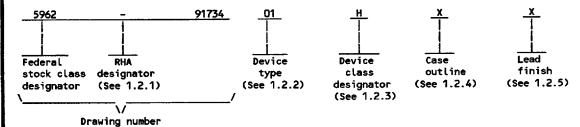

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes H and K RHA marked devices shall meet the MIL-H-38534 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>                                   |

|-------------|----------------|-----------------------------------------------------------|

| 01          | See 6.7        | MIL-STD-1553, BC/RTU/MT, transceiver multiplexed terminal |

| 02          | See 6.7        | MIL-STD-1553, BC/RTU/MT, transceiver multiplexed terminal |

| 03          | See 6.7        | MIL-STD-1553, BC/RTU/MT, transceiver multiplexed terminal |

| 04          | See 6.7        | MIL-STD-1760, BC/RTU/MT, transceiver multiplexed terminal |

1.2.3 <u>Device class designator</u>. This device class designator shall be a single letter identifying the product assurance level as follows:

### Device class

Device requirements documentation

H or K

Certification and qualification to MIL-H-38534

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style |

|----------------|------------------------|------------------|---------------|

| x              | See figure 1           | 78               | Dual-in-line  |

| Y              | See figure 1           | 82               | Flat package  |

| Z              | See figure 1           | 78               | Flat package  |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-H-38534 for classes H and K. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-91734 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>2 |

DESC FORM 193A JUL 91

**510 9004708 0011437 012**

1.3 Absolute maximum ratings. 1/ Positive supply voltage range ( $V_{CC}$ ): Devices types 01-04 - - - --0.5 V dc to +7.0 V dc Negative supply voltage range ( $V_{EE}$ ) +0.3 V dc to -18 V dc Devices types 01, 02, and 04 = --------0.5 V dc to +7.0 V dc 2.23 W Device type 02 ------2.16 W Device type 03 -----0.32 W -65°C to +150°C Lead temperature (soldering, 10 seconds)--------+300°C 6.13°C/W 112°C/W Device type 03 ------1.4 Recommended operating conditions. Positive supply voltage range ( $V_{CC}$ ): Device types 01, 02, and 04 - - - - - - - - - - - - - - -+4.5 V dc to +5.5 V dc Device type 03 ------+4.75 V dc to +5.5 V dc Logic supply voltage range ( $V_{DD}$ ): Device types 01, 02, and 04 --Device types 01, 02, and 04 - - - - - - - - - +4.5 V dc to +5.5 V dc

Device type 03 - - - - - - - - - +4.75 V dc to +5.5 V dc Negative supply voltage range ( $V_{EE}$ ): -14.25 V dc to -15.75 V dc -11.40 V dc to -12.60 V dc 2.2 V dc 0.8 V dc -55°C to +125°C Operating frequency (F<sub>OP</sub>) - - - - - - - - - - - - 16.0 MHz

$\underline{1}$ / Applies up to  $T_C = +125$ °C.

<sup>3/</sup> Assumes 100 percent transmitter duty cycle on one channel and 0 percent duty cycle on the other channel.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-91734 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>3 |

DESC FORM 193A JUL 91

■ 9004708 0011438 T59 ■

<sup>2/</sup> Hottest die.

#### 2. APPLICABLE DOCUMENTS

2.1 Government specifications, standards, and handbook. Unless otherwise specified, the following specifications, standards, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATIONS**

**MILITARY**

MIL-H-38534

- Hybrid Microcircuits, General Specification for.

**STANDARDS**

**MILITARY**

MIL-STD-883

- Test Methods and Procedures for Microelectronics.

MII -STD-973

MIL-STD-1835

Configuration ManagementMicrocircuit Case Outlines.

HANDBOOK

MILITARY

MIL-HDBK-780

- Standardized Military Drawings.

(Copies of the specifications, standards, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with MIL-H-38534 and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-H-38534 and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

- 3.2.4 Pin functions. The pin functions shall be as specified in table III.

- 3.3 Electrical performance characteristics. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full specified operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 Marking. Marking shall be in accordance with MIL-H-38534. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in QML-38534.

- 3.6 <u>Manufacturer eligibility</u>. In addition to the general requirements of MIL-H-38534, the manufacturer of the part described herein shall maintain the electrical test data (variables format) from the initial quality conformance inspection group A lot sample, produced on the certified line, for each device type listed herein. The data should also include a summary of all parameters manually tested, and for those which, if any, are guaranteed. This data shall be maintained under document revision level control by the manufacturer and be made available to the preparing activity (DESC-EC) upon request.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-91734 |

|------------------------------------------------------------------------------------|-----------|---------------------|------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>4 |

DESC FORM 193A JUL 91

**--** 9004708 0011439 995 **--**

| Test                                                              | Symbol                     | Conditions<br>  -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C                                                                                                                                   | Group A<br>  subgroups | Device<br>type | Limi          | Unit               |                   |

|-------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|---------------|--------------------|-------------------|

|                                                                   |                            | unless otherwise specified                                                                                                                                                                  | 1/                     |                | Min           | Max                | .  <br> <br> <br> |

| Logic supply current, idle <u>2</u> /                             | I <sub>DD</sub>            | V <sub>DD</sub> = 5.5 V, V <sub>CC</sub> = 5.5 V,   for all device types.   V <sub>EE</sub> = -15 V for device types 01 and 04, and -12 V   for device type 02.   f <sub>IN</sub> = 16 MHz. | 1,2,3                  | ALL            | 5.0           | 80                 | mA                |

| Positive supply current, idle <u>3</u> /                          | <br>  1 <sub>CC1</sub><br> |                                                                                                                                                                                             |                        | 01,02,04       | 5.0           | 90                 | _                 |

| _                                                                 |                            |                                                                                                                                                                                             |                        | 03             | 5.0           | 80                 | <br> <br> -       |

| Negative supply current, idle 4/                                  | I EE1                      |                                                                                                                                                                                             | .                      | 01,02,04       | -5.0          | <br>  -80<br>      | <br> <br> -       |

| Positive supply current,<br>channel A = 25 percent<br>duty cycle, | I <sub>CC2</sub>           | -<br> <br>                                                                                                                                                                                  | 100                    | 01,02,04       | <br>  5.0<br> | 90                 | <br> <br> -<br>   |

| channel B = idle 3/                                               |                            |                                                                                                                                                                                             |                        | 03             | 5.0           | 230                | _<br>_!           |

| Positive supply current,<br>channel B = 25 percent                | 1 <sub>CC3</sub>           | <br>                                                                                                                                                                                        |                        | 01,02,04       | 5.0           | 90                 | -<br>-            |

| duty cycle,<br>channel A = idle <u>3</u> /                        | <br> <br>                  |                                                                                                                                                                                             |                        | 03             | 5.0           | 230                | _                 |

| Negative supply current,<br>channel A = 25 percent                | I <sub>EE2</sub>           |                                                                                                                                                                                             |                        | 01,04          | -25           | <br> -130<br>      | _                 |

| duty cycle,<br>channel B = idle <u>4</u> /                        |                            |                                                                                                                                                                                             |                        | 02             | -25           | <br>  <b>-13</b> 5 | _                 |

| Negative supply current,<br>channel B = 25 percent                | I <sub>EE3</sub>           |                                                                                                                                                                                             |                        | 01,04          | <br>  -25<br> | -130               | -                 |

| duty cycle,<br>channel A = idle <u>4</u> /                        |                            |                                                                                                                                                                                             |                        | 02             | -25           | -135               | 1                 |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91734 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>5 |

DESC FORM 193A JUL 91

9004708 0011440 607 📟

| Test                                    | Symbol                               | Condi<br>-55°C ≤ T                                                                      | Group A                    | Device<br>type | Limits        |                            | Unit          |                   |     |  |  |

|-----------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------|----------------------------|----------------|---------------|----------------------------|---------------|-------------------|-----|--|--|

|                                         |                                      | unless otherw                                                                           | íse specified              | 1/             | 1             | <br>  Min                  | Max           |                   |     |  |  |

| High Level output voltage <u>5</u> /    | V <sub>OH1</sub>                     | V <sub>DD</sub> = 4.5 V,<br>  V <sub>CC</sub> = 4.5 V,<br>  V <sub>CC</sub> = 2.7 V,    | I <sub>OH1</sub> = -400 μA | 1,2,3          | ALL           | 2.4                        |               | V                 |     |  |  |

| High level output voltage 7/            | V <sub>ОН2</sub>                     | device types.  V <sub>EE</sub> = -15 V for device types 01 and 04, and -12 V for device | device types.              | device types.  | device types. | I <sub>OH2</sub> = -3.4 mA |               |                   | 3.7 |  |  |

| High level output<br>voltage <u>8</u> / | v <sub>OH3</sub>                     |                                                                                         | I <sub>OH3</sub> = -6.8 mA |                |               | 3.7                        |               | <br>              |     |  |  |

| Low level output voltage <u>8</u> /     | v <sub>oL1</sub>                     | type 02. <u>6</u> /                                                                     | I <sub>OL1</sub> = +6.8 mA |                |               |                            | 0.4           |                   |     |  |  |

| Low level output voltage 9/             | V <sub>OL2</sub>                     | -<br> <br> <br> <br> -                                                                  | I <sub>OL2</sub> = +2.0 mA |                |               |                            | 0.4           | <br> <br>         |     |  |  |

| Low level output<br>voltage <u>10</u> / | V <sub>OL3</sub>                     |                                                                                         | I <sub>OL3</sub> = +4.0 mA |                | <br> <br>     |                            | 0.4           | <br> <br> <br>    |     |  |  |

| Low level output voltage 7/             | V <sub>OL</sub> 4                    |                                                                                         | I <sub>OL4</sub> = +3.4 mA |                |               |                            | 0.4           |                   |     |  |  |

| High level input current 11/            | I IH1                                |                                                                                         | -15 V tor                  | 1,2,3          | ALL           | -20                        | <br> -155<br> | μ <b>Α</b>        |     |  |  |

| High level input current 12/            | I <sub>IH2</sub>                     | device types 0<br> -12 V for devi                                                       | 1 and 04, and              |                |               | -50                        | -200<br>      | <br> <br> -<br> - |     |  |  |

| High level input current 13/            | I <sub>I</sub> IH3                   |                                                                                         |                            |                |               | -10                        | +10           | <br> <br> <br>    |     |  |  |

| High level input<br>current 14/         | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | _<br> <br>                                                                              |                            |                |               | -10                        | <br> -165<br> |                   |     |  |  |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-91734 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>6 |

DESC FORM 193A JUL 91

9004708 0011441 543 🖿

| Test                                                           | Symbol                         |                                                                                                                                                           | sul           | roup A<br>bgroups | Device<br>type | Lim          | its       | Unit       |

|----------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|----------------|--------------|-----------|------------|

|                                                                |                                | unless otherwise specifi                                                                                                                                  | ed  <br> <br> | <u>1</u> /        |                | Min          | Max       |            |

| ow level input<br>current <u>11</u> /                          | I <sub>IL1</sub>               | V <sub>DD</sub> = 5.5 V, V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 0.4 V for all devi<br>types. V <sub>EE</sub> = -15 V for<br>device types 01 and 04, | ,<br>ce       | 1,2,3             | ALL            | -20          | -155      | μΑ         |

| ow level input<br>current <u>12</u> /                          | I <sub>IL2</sub>               | device types 01 and 04,<br>-12 V for device type 02                                                                                                       | and .         |                   |                | -100         | <br> -400 |            |

| Low level input<br>current <u>13</u> /                         | I <sub>IL</sub> 3              |                                                                                                                                                           |               |                   |                | -10          | +10       | _          |

| Low level input<br>current <u>14</u> /                         | I <sub>IL4</sub>               |                                                                                                                                                           |               |                   |                | -10<br>      | -165      |            |

| Transmitter/Receiver differential input                        | R <sub>IN</sub>                | <br> 75 kHz to 1.0 MHz                                                                                                                                    |               | 4,5,6             | 01,02,04       | <br>  11<br> |           | _ <br>  kΩ |

| resistance <u>15</u> / <u>16</u> / <u>17</u> /                 | <br>                           |                                                                                                                                                           |               |                   | 03             | 2            |           |            |

| Transmitter/Receiver differential input capacitance 15/16/17/  | c <sub>IN</sub>                | DC to 1.0 MHz                                                                                                                                             |               |                   | ALL            |              | 10        | pF         |

| Receiver input threshold<br>voltage                            | v <sub>TH</sub>                | <br> <br> Transformer coupled<br>                                                                                                                         |               |                   | ALL            | 650          | 860       | mVpp       |

| Receiver differential<br>input voltage <u>15</u> / <u>16</u> / | VIN                            | DC to 1.0 MHz                                                                                                                                             |               |                   | 01,02,04       |              | 40        | Vpp        |

|                                                                | !<br>!<br>!                    |                                                                                                                                                           |               | _                 | 03             |              | 11.9      | <u> </u>   |

| Transmitter differential output voltage                        | v <sub>o</sub>                 | <br> Transformer coupled, meas<br> across the stub.                                                                                                       | sured         |                   | 01,02,03       | 18           | 27        | Урр<br>—   |

|                                                                | <br> <br>                      | <br>                                                                                                                                                      |               |                   | 04 20          |              | 27        |            |

| Transmitter output rise and fall time                          | t <sub>r</sub> ,t <sub>f</sub> |                                                                                                                                                           |               |                   | ALL            | 100          | 300       | ns         |

| Output offset voltage                                          | v <sub>os</sub>                | -<br> <br> -<br>                                                                                                                                          |               |                   | ALL            | -250         | +250      | mV         |

| See footnotes at end of                                        | table.                         |                                                                                                                                                           |               |                   |                |              |           |            |

| MILIT                                                          | NDARDI                         | AWING                                                                                                                                                     | SIZE          | E                 |                |              |           | 5962-9173  |

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444        |                                |                                                                                                                                                           |               | REVISION          | LEVEI<br>A     | . !          | SHEET 7   |            |

🕶 9004708 0011442 48T 🖿

TABLE I. <u>Electrical performance characteristics</u> - Continued. Limits Unit Device Group A Conditions Symbol Test  $-55^{\circ}C \le T_C \le +125^{\circ}C$  unless otherwise specified type subgroups 1/ Min Max ALL -900 +900 Transformer coupled, measured 4,5,6 Transmitter overshoot VOVRSHT across the stub. V<sub>DD</sub> = 4.5 V, V<sub>CC</sub> = 4.5 V, V<sub>IL</sub> = 0.4 V, V<sub>IH</sub> = 2.7 V, for all device types pass/ ALL <u>6</u>/ 7,8 Functional tests fail V<sub>EE</sub> = -15 V for device types | OT and 04, and -12 V for | device type 02. See 4.3.1b.  $V_{DD} = 4.5 \text{ V}, V_{CC} = 4.5 \text{ V}, \\ V_{IH} = 2.7 \text{ V}, V_{IL} = 0.4 \text{ V}, \\ I_{OH1} = -400 \,\mu\text{A}, I_{OH2} = \\ I_{OL1} = 6.8 \,\text{mA}, I_{OL2} = 2.0 \,\text{mA}, \\ I_{OL3} = 4.0 \,\text{mA}, I_{OL4} = 3.4 \,\text{mA} \\ \text{for all device types.} \quad V_{EE} = -15 \,\text{V} \text{ for device types} \text{ O1} \\ I_{OL3} = 4.0 \,\text{mA}, I_{OL4} = 3.4 \,\text{mA} \\ \text{for all device types} = 0.0 \,\text{mA}, I_{OL4} = 3.4 \,\text{mA} \\ \text{for all device types} = 0.0 \,\text{mA}, I_{OL4} = 3.4 \,\text{mA} \\ \text{for all device types} = 0.0 \,\text{mA}, I_{OL4} = 3.4 \,\text{mA}, I_{OL5} = 3.4$ 9,10,11 | ALL 100 200 ns IOEN low pulse width t<sub>pw1</sub> (memory read) 18/ 25 75 READYD low pulse width t<sub>pw2</sub> (memory read) 18/ 100 200 and 04, and -12 V for device type 02. <u>6</u>/ <u>19</u>/ MEMOE low pulse width t<sub>pw3</sub> (memory read) 18/ 25 75 MEMWR low pulse width t<sub>pw4</sub> (memory write) 20/ 100 200 MEMENA-OUT low pulse t<sub>pw5</sub> width (memory read)18/ MEMENA-OUT low pulse 20/ tpu6 100 200 width (memory write) 3 5 Цs BSCTRCV low pulse t<sub>pw7</sub> width 21/ INT low pulse width 22/|tpw8 450 550 ns 175 75 CMD\_STR low pulse width (receive command) 23/ See footnotes at end of table.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

REVISION LEVEL

SHEET

A

8

DESC FORM 193A JUL 91

🕶 9004708 0011443 316 📟

| TABLE I. | Electrical | performance | characteristics | _ | Continued. |

|----------|------------|-------------|-----------------|---|------------|

|----------|------------|-------------|-----------------|---|------------|

| Test                                              | Symbol                     | Conditions<br>  -55°C ≤ T <sub>C</sub> ≤ +125°C                                                                                                                                                                                                                                                                                                                                | Group A | Device<br>type | Limi | ts             | Unit               |

|---------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|------|----------------|--------------------|

| į                                                 | unless otherwise specified | 1 1/                                                                                                                                                                                                                                                                                                                                                                           |         | Min            | Max  |                |                    |

| MD_STR low pulse width (transmit command) 24/     | t <sub>pw</sub> 10         | V <sub>DD</sub> = 4.5 V, V <sub>CC</sub> = 4.5 V,<br>  V <sub>IH</sub> = 2.7 V, V <sub>IL</sub> = 0.4 V,<br>  I <sub>OH</sub> = -400 \( \mu A, \) I <sub>OH2</sub> =<br>  -3.4 mA, I <sub>OH3</sub> = -6.8 mA,<br>  I <sub>OL1</sub> = 6.8 mA, I <sub>OL2</sub> = 2.0 mA,<br>  I <sub>OL3</sub> = 4.0 mA, I <sub>OL4</sub> = 3.4 mA<br>  for all device types. V <sub>EE</sub> | 9,10,11 | ALL            | 75   | 175            | ns                 |

| RX_DTA_STR low pulse width 23/                    | t <sub>pw11</sub>          |                                                                                                                                                                                                                                                                                                                                                                                | <br>    |                | 75   | 175            |                    |

| TX_DTA_STR low pulse<br>(memory read) <u>18</u> / | t <sub>pw12</sub>          | = -15 V for device types 01<br> and 04, and -12 V for device<br> type 02. <u>6</u> / <u>19</u> /                                                                                                                                                                                                                                                                               |         |                | 450  | 550            |                    |

| INCMD low pulse width (receive word) 23/          | tpw13                      | -<br> <br> <br>                                                                                                                                                                                                                                                                                                                                                                | <br>    | <br>           | 47.5 | <br>  52.5<br> | <br>  ha           |

| INCMD low pulse width (transmit word) 24/         | t <sub>pw14</sub>          | <br>                                                                                                                                                                                                                                                                                                                                                                           | <br>    | <br> <br>      | 48.7 | 53.7           | <br> -<br> -<br> - |

- 1/ All group A subgroup testing of the same temperature may be performed concurrently.

- 2/ Measured at the following pins:

Case X:

Device types 01-04: Pin 14.

Case Y:

Device types 01-04: Pin 28.

Case Z:

Device types 01-04: Pin 27.

3/ Measured at the following pins:

Case X:

Device types 01-04: Pins 58 and 77.

Case Y:

Device types 01-04: Pins 37 and 46.

Case Z:

Device types 01-04: Pins 36 and 43.

4/ Measured at the following pins:

Case X:

Device types 01, 02, and 04: Pins 18 and 39.

Case Y:

Device types 01, 02, and 04: Pins 36 and 45.

Case Z:

Device types 01-04: Pins 35 and 42.

5/ Measured at the following pins:

Case X:

Device types 01-04: Pins 12, 13, 16, 52, 53, 55, and 70.

Case Y:

Device types 01-04: Pins 24-27, 31, 32, and 60.

Case Z:

Device types 01-04: Pins 23-26, 30, 31, and 57.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-91734 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>9 |

DESC FORM 193A JUL 91

9004708 0011444 252 📟

```

TABLE I. Electrical performance characteristics - Continued.

\underline{6}/ For device type 03, V_{CC} = 4.75 V, V_{DD} = 4.75 V.

7/ Measured at the following pins:

Case X:

Device types 01-04: Pins 30, 31, 68, 72, 73, and 75.

Case Y:

Device types 01-04: Pins 50, 54, 56, 61, 63, and 64.

Case Z:

Device types 01-04: Pins 47, 51, 53, 58, 60, and 61.

8/ Measured at the following pins:

Case X:

Device types 01-04: Pins 1-8, 22-29, 41-48, and 60-67.

Case Y:

Device types 01-04: Pins 2-17 and 65-80.

Case Z:

Device types 01-04: Pins 1-16 and 62-77.

9/ Measured at the following pins:

Case X:

Device types 01-04: Pins 12, 13, 16, 55, and 70.

Case Y:

Device types 01-04: Pins 24, 26, 31, 32, and 60.

Case Z:

Device types 01-04: Pins 23, 25, 30, 31, and 57.

10/ Measured at the following pins:

Case X:

Device types 01-04: Pins 52 and 53.

Case Y:

Device types 01-04: Pins 27 and 25.

Case Z:

Device types 01-04: Pins 24 and 26.

11/ Measured at the following pins:

Case X:

Device types 01-04: Pins 1-8, 15, 22-29, 30, 33-37, 41-48, 57, 60-67, 71, 74, and 76.

Case Y:

Device types 01-04: Pins 2-17, 30, 35, 48, 49, 51-53, 55, 57, 58, 63, and 65-80.

Device types 01-04: Pins 1-16, 29, 34, 44-46, 48, 50, 52, 54, 55, 60, and 62-77.

12/ Measured at the following pins:

Case X:

Device types 01-04: Pins 9-11 and 49-51.

Case Y:

Device types 01-04: Pins 18-23.

Case Z:

Device types 01-04: Pins 17-22.

13/ Measured at the following pins:

Case X:

Device types 01-04: Pins 17, 54, and 56.

Case Y:

Device types 01-04: Pins 29, 33, and 34.

Case Z:

Device types 01-04: Pins 28, 32, and 33.

SIZE

5962-91734

STANDARDIZED

MILITARY DRAWING

A

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SHEET

REVISION LEVEL

10

A

```

**5004708 0011445 199 페**

TABLE I. <u>Electrical performance characteristics</u> - Continued. 14/ Measured at the following pins: Case X: Device types 01-04: Pins 32 and 69. Case Y: Device types 01-04: Pins 59 and 62. Case Z: Pins 56 and 59. 15/ Measured at the following pins: Case X: Device types 01-04: Pins 20, 40, 59, and 78. Case Y: Device types 01-04: Pins 39, 40, 43, and 44. Case Z: Device types 01-04: Pins 39-41. 16/ Parameter shall be tested as part of the initial characterization of this device and after design and process changes. Parameter shall be guaranteed to limits specified in table I for all lots not specifically tested. 17/ The test limits assume a 2 V rms balanced, differential, sinusoidal input. The applicable frequency range is 75 kHz to 1 MHz. The limits are applicable for both unpowered and powered conditions. 18/ Test limits based on the following test conditions: - TRANSPARENT/BUFFERED\_L input set to Logic "1". - SELECT\_L input set to logic "O". - MEM/REG\_L input set to logic "1". RD/WR\_L input set to logic "1". - 250 ns active low pulse into STRBD\_L. 19/ All timing parameters are measured at the 50 percent level of the waveform. 20/ Test limits based on the following test conditions: - TRANSPARENT/BUFFERED-L input set to logic "1". - SELECT\_L input set to logic "0". - MEM/REG L input set to logic "1". - RD/WR\_L input set to logic "O". - 250 ns active low pulse into STRBD\_L. 21/ Test limits based on the following test conditions: - DUT active in RT mode. - BRO\_ENA input set to logic "1". -1553 command 1F R O1 O1 is sent to DUT. 22/ Test limits based on the following test conditions: DUT active in RT mode. - Interrupt mask register is programmed with a hex value of 0080 (interrupt on rt address parity error). The following sequence is input on the rt address inputs: 1. rt address = 01 (rt address parity bit = 0). rt address = 00 (rt address parity bit = 0). 3. rt address = 01 (rt address parity bit = 0). Note: interrupt pulse will occur in response to step 2. 23/ Test limits based on the following test conditions: - DUT active in RT mode. - rt address = 01 (rt address parity = 0). - 1553 Command 01 R 01 01 is sent to DUT. 24/ Test limits based on the following test conditions: - DUT active in RT mode. - rt address = 01 (rt address parity = 0). -1553 Command 01 T 01 01 is sent to DUT. 5962-91734 SIZE **STANDARDIZED** MILITARY DRAWING A DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL SHEET 11

DESC FORM 193A JUL 91

9004708 0011446 025

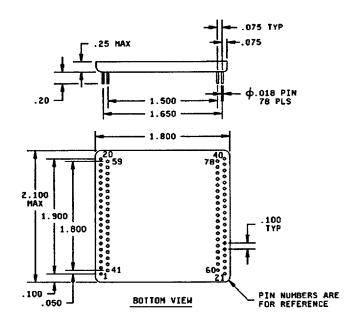

## Device types 01 through 04

#### Case X

| T 1    |       |

|--------|-------|

| Inches | mm    |

| .018   | 0.45  |

| .050   | 1.27  |

| .056   | 1.42  |

| .075   | 1.91  |

| .100   | 2.54  |

| . 25   | 6.4   |

| 1.500  | 38.10 |

| 1.650  | 41.91 |

| 1.800  | 45.72 |

| 1.900  | 48.26 |

| 2.100  | 53.34 |

|        |       |

## NOTES:

- 1. Dimensions are in inches

- 2. Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerance is  $\pm .005$  (0.13 mm) for three place decimals and  $\pm .01$  (0.3 mm) for two place decimals.

FIGURE 1. Case outlines.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91734  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>12 |

DESC FORM 193A JUL 91

9004708 0011447 T61 **=**

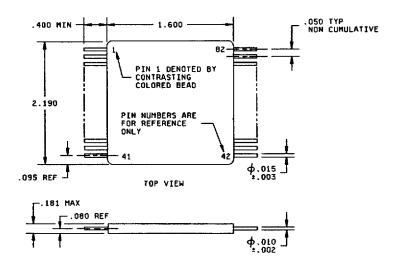

## Device types 01 through 04

Case Y

| Inches | mm    |

|--------|-------|

| .002   | 0.05  |

| .003   | 0.08  |

| .010   | 0.25  |

| .015   | 0.38  |

| .050   | 1.27  |

| .080   | 2.03  |

| .095   | 2.41  |

| .181   | 4.60  |

| . 400  | 10.16 |

| 1.600  | 40.64 |

| 2.190  | 55.63 |

## NOTES:

- Dimensions are in inches.

Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerance is  $\pm .005$  (0.13 mm) for three place decimals and  $\pm .01$  (0.3 mm) for two place decimals.

FIGURE 1. Case outlines - Continued.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-91734  |

|-----------------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL<br>A | SHEET<br>13 |

DESC FORM 193A JUL 91

■ 9004708 0011448 9T8 ■

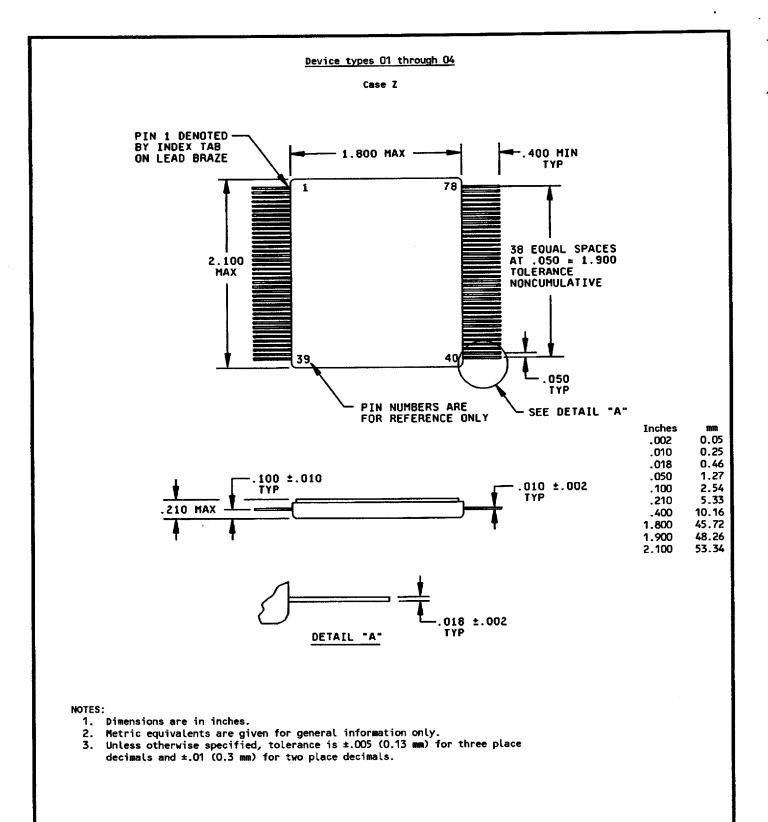

FIGURE 1. <u>Case outlines</u> - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                     | 5962-91734  |

|------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>14 |

■ 468 644709 9024006 ■

| Device types    | AL                                   | L             | Device types    | Al                                   | l L                                  |

|-----------------|--------------------------------------|---------------|-----------------|--------------------------------------|--------------------------------------|

| Case outline    | x                                    | Υ             | Case outline    | x                                    | Y                                    |

| Terminal number | Terminal                             | symbol        | Terminal number | Terminal                             | symbol                               |

| 1               | DO0                                  | No connection | 22              | A01                                  | RTAD4                                |

| 2               | p02                                  | DOO           | 23              | A03                                  | RTADP                                |

| 3               | DO4                                  | DO1           | 24              | A05                                  | MSG_ERROR                            |

| 4               | DO6                                  | p02           | 25              | A07                                  | RX_DTA_STR                           |

| 5               | D08                                  | <b>D</b> 03   | 26              | 1 A09                                | CMD_STR                              |

| 6               | D10                                  | DO4           | 27              | A11                                  | TX_DTA_STR                           |

| 7               | D12                                  | DO5           | 28              | A13                                  | v <sub>DD</sub>                      |

| 8               | D14                                  | D06           | 29              | A15                                  | BRO_ENA                              |

| 9               | RTAD1                                | DO7           | 30              | MEMOE/ADDR_LAT                       | TAG_CLK                              |

| 10              | RTADO                                | 800           | 31              | MEMENA-OUT                           | RTFAIL                               |

| 11              | RTAD4                                | DO9           | 32              | CLOCK IN                             | BCSTRCV                              |

| 12              | MSG_ERROR                            | D10           | 33              | MEM/REG                              | RTFLAG                               |

| 13              | CMD_STR                              | 11ס           | 34              | STRBD                                | ILLENA                               |

| 14              | V <sub>DD</sub>                      | D12           | 35              | TRANSP/BUFFERED                      | TX_INH_B                             |

| 15              | <br>  TAG_CLK<br>                    | D13           | 36              | RD/WR                                | V <sub>EE</sub> (CH B)<br>(see note) |

| 16              | BCSTRCV                              | D14           | 37              | SSFLAG                               | V <sub>CC</sub> (CH B)               |

| 17              | ILLENA                               | D15           | 38              | GNDA                                 | <br>  GNDB                           |

| 18              | V <sub>EE</sub> (CH B)<br>(see note) | RTAD1         | 39              | V <sub>EE</sub> (CH A)<br>(see note) | TX/RX-B                              |

| 19              | GNDB                                 | RTAD3         | 40              | TX/RX-A                              | TX/RX-B                              |

| 20              | TX/RX-B                              | RTADO         | 41              | p01                                  | No connection                        |

| 21              | LOGIC GND                            | RTAD2         | 42              | D03                                  | No connection                        |

FIGURE 2. <u>Terminal connections</u>.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-91734  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>15 |

■ 9004708 0011450 55b **■**

| Device types    | AL                     |                                   | Device types    | Al                     | .t             |

|-----------------|------------------------|-----------------------------------|-----------------|------------------------|----------------|

| Case outline    | х                      | Y                                 | Case outline    | x                      | Y              |

| Terminal number | Terminal               | symbol                            | Terminal number | Terminal symbol        |                |

| 43              | DO5                    | TX/RX-A                           | 63              | A06                    | MEMOE/ADDR_LAT |

| 44              | DO7                    | TX/RX-A                           | 64              | 808                    | MEMWR          |

| 45              | DO9                    | V <sub>EE</sub> (CH A) (see note) | 65              | A10                    | A15            |

| 46              | D11                    | V <sub>CC</sub> (CH A)            | 66              | A12                    | A14            |

| 47              | D13                    | GNDA                              | 67              | A14                    | A13            |

| 48              | D15                    | TX_INH_A                          | 68              | MEMUR                  | A12            |

| 49              | RTAD3                  | SSFLAG                            | 69              | MEMENA-IN              | A11            |

| )<br>  50       | RTAD2                  | READYD                            | 70              | INCMD                  | A10            |

| 51              | RTADP                  | RD/WR                             | 71              | MSTRCLR                | A09            |

| 52              | RX_DTA_STR             | SELECT                            | 72              | INT                    | 80A            |

| 53              | TX_DTA_STR             | TRANS/BUFFERED                    | 73              | IOEN                   | A07            |

| 54              | BRO_ENA                | IOEN                              | 74              | SELECT                 | A06            |

| 55              | RTFAIL                 | STRBD                             | 75              | READYD                 | A05            |

| 56              | RTFLAG                 | INT                               | 76              | A_HM1_XT               | A04            |

| 57              | TX_INH_B               | MEM/REG                           | 77              | V <sub>CC</sub> (CH A) | A03            |

| 58              | V <sub>CC</sub> (CH B) | MSTRCLR                           | 78              | TX/RX-A                | A02            |

| 59              | TX/RX-B                | CLOCK IN                          | 79              |                        | A01            |

| 60              | A00                    | INCMD                             | 80              |                        | A00            |

| 61              | A02                    | MEMENA-OUT                        | 81              |                        | LOGIC GND      |

| 62              | A04                    | NEMENA-IN                         | 82              |                        | No connection  |

NOTE: For device type 03, no connection.

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-91734  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>16 |

DESC FORM 193A JUL 91

9004708 0011451 492 📟

| Device type     |                 |                 | 01 through 04          |                 |                 |

|-----------------|-----------------|-----------------|------------------------|-----------------|-----------------|

| Case outline    |                 |                 | Z                      |                 |                 |

| Terminal number | Terminal symbol | Terminal number | Terminal symbol        | Terminal number | Terminal symbol |

| 1               | DOO             | 27              | V <sub>DD</sub>        | 53              | INT             |

| [<br>  2        | DO1             | 28              | SA/MC-3                | 54              | MEM/REG         |

| 3               | D02             | 29              | SA/MC-1                | 55              | MSTRCLR         |

| 4               | D03             | 30              | THIS-RT                | 56              | CLOCK-IN        |

| 5               | b04             | 31              | BCSTRCV                | 57              | INCMD           |

| 6               | DO5             | 32              | RTPARERR               | <br>  58        | MEMENA-OUT      |

| 7               | D06             | 33              | LMC                    | 59              | MEMENA-IN       |

| 8               | DO7             | 34              | T/R                    | 60              | MEMOE           |

| 9               | <br>  DO8       | 35              | VEE (CH B)             | 61              | MEMUR           |

| 10              | DO9             | 36              | V <sub>CC</sub> (CH B) | 62              | A15             |

| 11              | <br>  D10       | 37              | GNDB                   | 63              | A14             |

| 12              | <br>  D11       | )<br>38         | TX/RX-B                | 64              | A13             |

| 13              | 012             | 39              | TX/RX-B                | 65              | A12             |

| 14              | D13             | 40              | TX/RX-A                | 66              | A11             |

| 15              | D14             | 41              | TX/RX-A                | 67              | A10             |

| 16              | D15             | 42              | VEE (CH A)             | 68              | A09             |

| 17              | RTAD1           | 43              | V <sub>CC</sub> (CH A) | 69              | 80A             |

| 18              | RTAD3           | 44              | GNDA                   | 70              | A07             |

| 19              | RTADO           | 45              | TAGEN                  | 71              | A06             |

| 20              | <br>  RTAD2     | 46              | EXTLD                  | 72              | A05             |

| 21              | RTAD4           | 47              | READYD                 | 73              | A04             |

| )<br>  22       | RTADP           | 48              | RD/WR                  | 74              | A03             |

| 23              | ILLCMD          | 49              | SELECT                 | 75              | A02             |

| 24              | SA/MC-2         | 50              | EXTEN                  | 76              | A01             |

| 25              | SA/MC-O         | 51              | IOEN                   | 77              | A00             |

| 26              | SA/MC-4         | 52              | STRBD                  | 78              | GND             |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-91734  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>17 |

9004708 0011452 329

## Device types 01 through 04 ILLEGALLIZATION LOGIC ILLENA (ILLEGALIZATION -BK X 15 DUAL PORT RAM BUS-25679 CLK IN (16 MHz) ۔ ئے LOW-POWER TRANSCEIVER A DUAL ENCODER/ DECODER, BC/RT/MT PROTOCOL TX INH A DATA BUFFERS 015-00 (PROCESSOR MEMORY DATA BUS-25679 السلط A15-A0 (PROCESSOR ADDRESS) LOW-POWER ADDRESS LATCHES/ BUFFERS TRANSCEIVER B MEMORY ADDRESS ADDR LAT (ADDRESS LATCH CONTROL) ERED, MSTCLR TRANSPARENT/BUFFERED, HSTCLE STRBD, SELECT, MEM/REG, RD/HR (PROCESSOR RTAD 4-0. RTADP (RT ADDRESS) IOEN, READYD MEMORY MANAGEMENT, SHARED RAM PROCESSOR INTERFACE, INTERFACE BRO ENA (BROADCAST ENABLE) (INTERRUPT REQUEST) RTFAIL HEMEN-OUT, MEMNR, MEMOE (MEMORY CONTROL) RTFLAG MEMENA-IN BCSTRCY, CHD STR, TXDTA STR RXDTA STR, MSG ERR, INCMD (SUBSYSTEM FLAG) (TIME TAG CLOCK) SSFLAG LOGIC (BROADCAST, — MESSAGE | TIMING, DATA STROBE AND ERROR INDICATORS) TAGCLK FIGURE 3. Block diagram. STANDARDIZED SIZE 5962-91734 MILITARY DRAWING A DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL SHEET 18 A DESC FORM 193A

JUL 91

M 9004708 0011453 265 📟

- 3.7 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to supply to this drawing. The certificate of compliance submitted to DESC-ECT shall affirm that the manufacturer's product meets the requirements of MIL-H-38534 and the requirements herein.

- 3.8 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-H-38534 shall be provided with each lot of microcircuits delivered to this drawing.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-H-38534.

- 4.2 <u>Screening</u>. Screening shall be in accordance with MIL-H-38534. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DESC-EC or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A$  as specified in accordance with table I of method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with MIL-H-38534 and as specified herein.

- 4.3.1 Group A inspection. Group A inspection shall be in accordance with MIL-H-38534 and as follows:

- a. Tests shall be as specified in table II herein.

- b. Subgroups 7 and 8 shall consist of verifying the functionality of the device. It forms a part of the vendors test tape and shall be maintained and available from the approved source of supply.

- 4.3.2 Group B inspection. Group B inspection shall be in accordance with MIL-H-38534.

- 4.3.3 Group C inspection. Group C inspection shall be in accordance with MIL-H-38534 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state Life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DESC-EC or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- (2)  $T_A$  as specified in accordance with table I of method 1005 of MIL-STD-883.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- 4.3.4 Group D inspection. Group D inspection shall be in accordance with MIL-H-38534.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-91734  |

|------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>19 |

, 🎫 9004708 0011454 171 🗪

TABLE II. <u>Electrical test requirements</u>.

| MIL-H-38534 test requirements                                              | Subgroups (in accordance with MIL-H-38534, group A test table)   |

|----------------------------------------------------------------------------|------------------------------------------------------------------|

| Interim electrical parameters                                              | 1,2,3,4,5,6,<br>7,8,9,10,11                                      |

| Final electrical test parameters                                           | 1*,2,3,4,5,6,<br>7,8,9,10,11                                     |

| Group A test requirements                                                  | 1,2,3,4,5,6,<br>7,8,9,10,11                                      |

| Group C end-point electrical parameters                                    | 1,2,3,4,5,6,<br>7,8,9,10,11                                      |

| MIL-STD-883, Group E end-point<br>electrical parameters for RHA<br>devices | Subgroups** (in accordance with method 5005, group A test table) |

\*PDA applies to subgroup 1

\*\*When applicable to this standardized military drawing,

the subgroups shall be defined.

- 4.3.5 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes H and K shall be M, D, R, and H. RHA quality conformance inspection sample tests shall be performed at the RHA level specified in the acquisition document.

- a. RHA tests for device classes H and K for levels M, D, R, and H shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- b. End-point electrical parameters shall be as specified in table II herein.

- c. Prior to total dose irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table II herein.

- d. For device classes H and K, the devices shall be subjected to radiation hardness assured tests as specified in MIL-H-38534 for RHA level being tested, and meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A$  = +25°C ±5 percent, after exposure.

- e. Prior to and during total dose irradiation testing, the devices shall be biased to establish a worst case condition as specified in the radiation exposure circuit.

- f. For device classes H and K, subgroups 1 and 2 in table V, method 5005 of MIL-STD-883 shall be tested as appropriate for device construction.

- g. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-91734  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>20 |

DESC FORM 193A JUL 91

· 🗰 9004708 0011455 038 🗯

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-H-38534.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.5 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444, or telephone (513) 296-5374.

- 6.6 One part one part number system. The one part one part number system described below has been developed to allow for transitions between identical generic devices covered by the four major microcircuit requirements documents (MIL-M-38510, MIL-H-38534, MIL-I-38535, and 1.2.1 of MIL-STD-883) without the necessity for the generation of unique PIN's. The four military requirements documents represent different class levels, and previously when a device manufacturer upgraded military product from one class level to another, the benefits of the upgraded product were unavailable to the Original Equipment Manufacturer (OEM), that was contractually locked into the original unique PIN. By establishing a one part number system covering all four documents, the OEM can acquire to the highest class level available for a given generic device to meet system needs without modifying the original contract parts selection criteria.

| Military documentation format                              | Example PIN under new system | Manufacturing source listing | Document<br><u>Listing</u> |

|------------------------------------------------------------|------------------------------|------------------------------|----------------------------|

| New MIL-H-38534 Standardized Military<br>Drawings          | 5962-XXXXXZZ(H or K)YY       | QML-38534                    | MIL-BUL-103                |

| New M1L-I-38535 Standardized Military<br>Drawings          | 5962-XXXXXZZ(Q or V)YY       | QML-38535                    | MIL-BUL-103                |

| New 1.2.1 of MIL-STD-883 Standardized<br>Military Drawings | 5962-XXXXZZ(M)YY             | MIL-BUL-103                  | MIL-BUL-103                |

6.7 <u>Sources of supply for device classes H and K</u>. Sources of supply for device classes H and K are listed in QML-38534. The vendors listed in QML-38534 have submitted a certificate of compliance (see 3.7 herein) to DESC-EC and have agreed to this drawing.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-91734  |

|------------------------------------------------------------------------------------|-----------|---------------------|-------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>21 |

DESC FORM 193A JUL 91

9004708 0011456 174

TABLE III. Pin functions.

| Terminal symbol        | 1/0 | Description                                                                                                                                                                   |

|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOO                    | 1/0 | Data bus bit O (LSB).                                                                                                                                                         |

| DO2                    | 1/0 | Data bus bit 2.                                                                                                                                                               |

| DO4                    | 1/0 | Pata bus bit 4.                                                                                                                                                               |

| D06                    | 1/0 | Data bus bit 6.                                                                                                                                                               |

| DO8                    | 1/0 | Data bus bit 8.                                                                                                                                                               |

| D10                    | 1/0 | Data bus bit 10.                                                                                                                                                              |

| D12                    | 1/0 | Data bus bit 12.                                                                                                                                                              |

| D14                    | 1/0 | Data bus bit 14.                                                                                                                                                              |

| RTAD1                  | 1   | Remote terminal address bit 1.                                                                                                                                                |

| RTADO                  | I   | Remote terminal address bit 0 (LSB).                                                                                                                                          |

| RTAD4                  | I   | Remote terminal address bit 4 (MSB).                                                                                                                                          |

| MSG_ERROR              | 0   | In BC or RT modes, will be low following a word or format error and remain low until the start of the next message.                                                           |

| CMD_STR                | 0   | In RT/transparent mode, this output will pulse low for nominally 125 ns when a received Command Word is on D15-DO.                                                            |

| V <sub>DD</sub>        | 1   | +5 V supply input for digital logic section.                                                                                                                                  |

| TAG_CLK                | I   | External Time Tag Clock Input, for BC/RT modes.                                                                                                                               |

| BCSTRSV                | 0   | Broadcast received. Indicates current command is a 1553 broadcast command.                                                                                                    |

| ILLENA                 | 0   | Illegalization Enable. If logic 1, designates shared RAM   addresses 0300-03FF to be dedicated for command illegalization in RT mode. If logic 0, illegalization is disabled. |

| V <sub>EE</sub> (CH B) | I   | Input power supply connection for the B channel transceiver.<br>-15 V for device type 01, -12 V for device type 02. For device type 03 no connection (NC).                    |

| GNDB                   | -   | Ground B. Power supply return connection for the B channel transceiver.                                                                                                       |

| TX/RX-B                | I/O | Transmit/receive transceiver-B. Input/output to the coupling transformer that connects to the B channel of the 1553 bus.                                                      |

| LOGIC GND              | -   | Logic ground. Power supply return for the digital logic section.                                                                                                              |

| A01                    | 1/0 | Address bit 1.                                                                                                                                                                |

| A03                    | 1/0 | Address bit 3.                                                                                                                                                                |

| A05                    | 1/0 | Address bit 5.                                                                                                                                                                |

| STANDARDIZED  MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTED | SIZE<br>A |                     | 5962-91734  |

|-------------------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444              |           | REVISION LEVEL<br>A | SHEET<br>22 |

■ 9004708 0011457 900 **■**

TABLE III. Pin functions - Continued.

| Terminal symbol | 1/0 | Description                                                                                                                                                                    |

|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A07             | 1/0 | Address bit 7.                                                                                                                                                                 |

| A09             | 1/0 | Address bit 9.                                                                                                                                                                 |