# DiSEqC™ 2.1 Slave Microcontroller for LNBs and Switchers

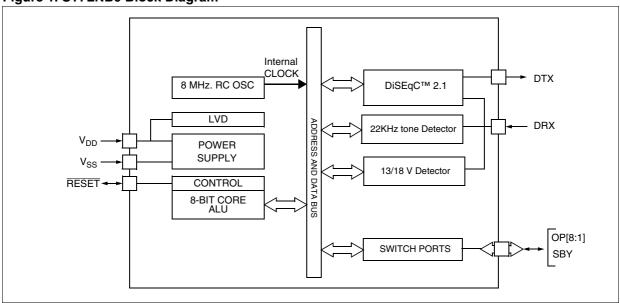

The ST7LNB0 is an 8-bit microcontroller dedicated to DiSEqC $^{\text{TM}}$  slave operation in LNBs and switchers, it is compliant with the DiSEqC $^{\text{TM}}$  2.1 level, also it supports backwards compatible (13/18 V, 22 kHz tone) and toneburst signalling.

# ■ Clock, Reset and Supply Management

- Reduced power consumption.

- Safe power on/off management by low voltage detector (LVD).

- Internal 8 MHz oscillator

### ■ Communication interface

- One DiSEqC™ 2.1 communication interface

### Analog interface

- 13/18 V voltage detector

- 22 KHz tone detector

### ■ I/O ports

- 8 output ports for control of committed and uncommitted switches

- 1 output port for standby control

**Table 1. Device Summary**

| Features          | ST7LNB0Y0M6                                                               |

|-------------------|---------------------------------------------------------------------------|

| Packages          | SO16 150"                                                                 |

| Peripherals       | DiSEqC™ 2.1 communication interface, 22KHz tone detector, 13/18V detector |

| Operating Voltage | 4.5 V t0 5.5 V                                                            |

| Temperature range | -40°C to +85°C                                                            |

Rev. 3.0

December 2004 1/22

# 1 ST7LNB0 PIN DESCRIPTION

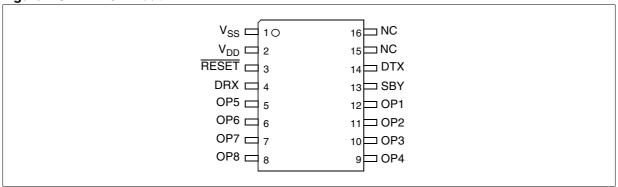

Figure 2 ST7LNB0 Pinout

The following table gives the pin functions

**Table 2. ST7LNB0 Pin Functions**

| Pin Number       | Function Name   | Function Description         |

|------------------|-----------------|------------------------------|

| 1                | Vss             | Ground                       |

| 2                | V <sub>DD</sub> | Power Supply (+5 volts)      |

| 3                | RESET           | Reset (active low) input     |

| 4                | DRX             | Receive input                |

| 5                | OP5             | output 5 (uncommitted port)  |

| 6                | OP6             | output 6 (uncommitted port)  |

| 7                | OP7             | output 7 (uncommitted port)  |

| 8                | OP8             | output 8 (uncommitted port)  |

| 9                | OP4             | output 4 (SO B/A)            |

| 10 <sup>1)</sup> | OP3             | output 3 (SB/SA)             |

| 11               | OP2             | output 2 (H/V)               |

| 12               | OP1             | output 1 (Hi/Lo)             |

| 13               | SBY             | STANDBY                      |

| 14               | DTX             | DiSEqC™ data transmit output |

| 15,16            | -               | Not used pins <sup>2)</sup>  |

- 1. During normal operation this pin must be pulled- up, internally or externally (external pull-up of 10k mandatory in noisy environment). This is to avoid entering ICC mode unexpectedly during a reset. In the application, even if the pin is configured as output, any reset will put it back in input pull-up

- 2. Unused pins 15 and 16 must be tied to ground.

# **2 ST7LNB0 IMPLEMENTATION**

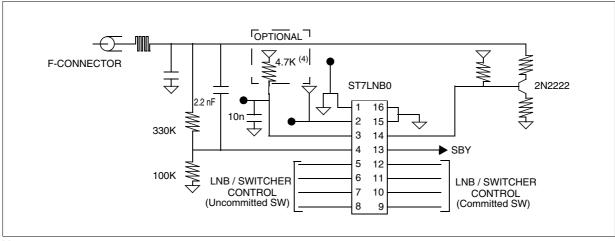

The following figure shows a typical application circuit for the ST7LNB0:

Figure 3 ST7LNB0 typical application circuit

- 1.The divider chain connected to the DRX pin must have the following resistance values: 330K $\Omega$  and 100K $\Omega$ .

- 2. The reset circuitry linked to the RESET pin is optional, in fact the ST7LNB0 has an internal voltage level detector LVD which generates a static reset when the VDD supply is below a threshold voltage of 4.1 V.

- 3. The DiSEqC signalling must have a tone frequency of 22KHz(+/- 20%) and an amplitude exceeding 150 mV peak to peak.

- 4. When the LVD is enabled (default state), it is mandatory not to connect a pull-up resistor. A 10nF pull-down capacitor is recommended to filter noise on the reset line.

# 3 ST7LNB0 FUNCTIONAL DESCRIPTION

### 3.1 ST7LNB0 Configuration

Unlike the original slave microcontroller described in the "Eutelsat DiSEqC slave microcontroller version 1.0" the ST7LNB0 does not scan the control pins in order to determine the slave configuration, instead all configuration parameters must be programmed for each specific application, an Option List (Section 8) must be filled-in in order to program the necessary options at the manufacturing stage.

The slave configuration parameters are the following:

- The DiSEqC<sup>™</sup> slave address e.g.: 11h for an LNB, 15h for a switcher.

- The Local oscillator frequency table entry numbers.

- The DiSEqC<sup>™</sup> configuration byte (refer to DiSEqC slave microcontroller document page 15)

- The output mode (see next paragraph)

- 22 kHz tone use in backwards compatible mode (SB/SA or Hi/Lo switching)

- Standby pin use.

### 3.2 ST7LNB0 Switching Output Modes

The ST7LNB0 has 8 pins (OP1 to OP 8) available to provide 'TTL' logic levels to operate switches to select various signal conditions and sources (e.g. horizontal polarization, satellite position).

As listed in Table 2 the committed output port is composed of OP1 to OP4 and the uncommitted output port is composed of OP5 to OP8.

Depending on the application hardware, the switching control pins OP1 to OP8 may be operat-

ed differently. Three possible output modes can be configured:

**Single polarity output mode.** In this mode each pin can be controlled individually as described in the following table:

Table 3. Single polarity output mode

| Pin Number | Function Name | Function<br>Description |

|------------|---------------|-------------------------|

| 9          | OP4           | SO B/A                  |

| 10         | OP3           | SB/SA                   |

| 11         | OP2           | Hor/Ver                 |

| 12         | OP1           | Hi/Lo                   |

| 5          | OP5           | SW5                     |

| 6          | OP6           | SW6                     |

| 7          | OP7           | SW7                     |

| 8          | OP8           | SW8                     |

**Decoded output mode.** This mode offers the possibility to demultiplex three adjacent committed or uncommitted control lines (e.g Hi/Lo, SB/SA and SOB/A) in order to have a 1 of 8 demux on the output port OP1 to OP8. (for more details refer to DiSEqC™ slave microcontroller specification document page 10).

It is also possible to have a 1 of 4 demux by decoding only 2 control lines e.g. SB/SA and SO B/A for controlling a 1 of 4 switcher for example.

**Complementary output mode.** In this mode the state of the uncommitted switching outport pins is the complementary of the state of the committed output ports pins (for more details refer to DiSE-qC<sup>TM</sup> slave microcontroller document page 14).

# 4 SUPPORTED DISEqC™ COMMANDS

Table 4. ST7LNB0 DiSEqC™ supported commands

| Command<br>number (Hex<br>byte) | Command name | Command Function                              |

|---------------------------------|--------------|-----------------------------------------------|

| 00h                             | RESET        | Reset DiSEqC™ microcontroller                 |

| 01h                             | clr RESET    | Clear the "RESET" flag                        |

| 02h                             | STANDBY      | Switch peripheral power off                   |

| 03h                             | Power on     | Switch peripheral power supply off            |

| 04h                             | Set Cont     | Set contention flag                           |

| 05h                             | Contend      | Return address only if contention flag is set |

| 06h                             | Clr Cont     | Clear contention flag                         |

| 07h                             | Address      | Return address unless contention flag is set  |

| 08h                             | Move C       | Change address only if contention flag is set |

| 09h                             | Move         | Change address unless contention flag is set  |

| 10h                             | STATUS       | Read STATUS register                          |

| 11h                             | Config       | Read Configuration register                   |

| 14h                             | Group 0      | Read switching state (committed port)         |

| 15h                             | Group 1      | Read switching state (uncommitted port)       |

| 20h                             | Set Lo       | Select the low Local oscillator frequency     |

| 21h                             | Set VR       | Select the vertical polarization              |

| 22h                             | Set Pos A    | Select satellite position A                   |

| 23h                             | Set SO A     | Select switch Option A                        |

| 24h                             | Set Hi       | Select the Hi local oscillator frequency      |

| 25h                             | Set HL       | Select the Horizontal polarization            |

| 26h                             | Set Pos B    | Select satellite position B                   |

| 27h                             | Set SO B     | Select the switch Option B                    |

| 28h                             | Set S1 A     | Select switch S1 input A                      |

| 29h                             | Set S2 A     | Select switch S2 input A                      |

| 2Ah                             | Set S3 A     | Select switch S3 input A                      |

| 2Bh                             | Set S4 A     | Select switch S4 input A                      |

| 2Ch                             | Set S1 B     | Select switch S1 input B                      |

| 2Dh                             | Set S2 B     | Select switch S2 input B                      |

| 2Eh                             | Set S3 B     | Select switch S3 input B                      |

| 2Fh                             | Set S4B      | Select switch S4 input B                      |

| 38h                             | Write N0     | Write to port group 0 (committed switches)    |

| 39h                             | Write N1     | Write to port group 1 (uncommitted switches)  |

| 51h                             | LO           | Read current L.O frequency table entry number |

| 52h                             | LO Lo        | Read Lo L.O frequency table entry number      |

| 53h                             | LO Hi        | Read Hi L.O frequency table entry number      |

# Note:

After a power-on, the ST7LNB0 responds to backwards compatible signalling (13/18 V, 22 kHz, tone burst) until a valid DiSEqC frame is detected.

In order to return to backwards compatible mode, a RESET command must be sent.

# 5 ST7LNB0 CONFIGURATION

To configure the ST7LNB0 to the required target application, a dedicated DiSEqC command is implemented. This configuration is stored in the ST7LNB0 embedded EEPROM location.

# 5.1 COMMAND 0Fh

ST7LNB0 devices are shipped to customers with a default parameter value. These parameters can be updated using a dedicated 0Fh DiSEqC command.

This command has the following format where "data" is the parameter value to be programmed at the "index" location as shown in Table 5.

| E0h | DiSEqC<br>Slave address | 0Fh | index | data |

|-----|-------------------------|-----|-------|------|

|-----|-------------------------|-----|-------|------|

### Note:

The special command E0 xx 0F FF FF protects the EEPROM data from any subsequent write access (where xx is the corresponding DiSEqC Slave address).

# 5.2 COMMAND 0Dh

For reading a parameter inside the EEPROM a dedicated 0Dh command has been added.

This command has the following format where" index" is the address in the EPPROM of the byte to be read (see Table 5)

| E2h DiSEqC<br>Slave address | 0Dh | index |

|-----------------------------|-----|-------|

|-----------------------------|-----|-------|

:The reply frame has the following format where "data" is the read byte from the EEPROM:

### Timings:

the time required to update a byte parameter (write and read operation) is 130 ms the time required to update all the parameters is about 3.5 s

**Table 5. ST7LNB0 EEPROM Parameters**

| index | Parameter               | Description                                  | Default Value   |

|-------|-------------------------|----------------------------------------------|-----------------|

| 00    | slave address           | DiSEqC slave address (00 to FFh), see note 1 | 14h             |

| 01    | L.O frequencies         | see note 2                                   | 00h             |

| 02    | output configuration    | see note 3                                   | 0Ah             |

| 03    | Carial / araian na      |                                              | 1Bh, see note 4 |

| 04    | Serial / version number | user can enter a value:0000h to FFFFh        | FFh             |

### Notes:

- 1.Besides the address defined in the EEPROM at index 00h, addresses 10h and 00h are recognized also as valid addresses.

- 2. L.O frequencies: Local oscillator table entry numbers.

- High nibble: High L.O frequency

- Low nibble: Low L.O frequency

- 3. Output configuration byte:

| Bit Number                   | Bit Description              | Value                             |

|------------------------------|------------------------------|-----------------------------------|

| 0                            | 22 KHz use                   | - 0: High/Low switching           |

|                              |                              | - 1: SB/SA switching              |

| [1:4]                        | Decoded Mode Selection       | - 0: mode not selected            |

| [1:4] Decoded Mode Selection |                              | - [ 1 to 8] : decoded mode number |

| 5                            | Complementary Mode Selection | - 0: mode not selected            |

| 5                            | Complementary Mode Selection | - 1: mode selected                |

|                              | 2 Lines Decoded Mode         | - 0: mode not selected            |

| 6                            | Selection                    | - 1: mode selected                |

| 7                            | Not Used                     | - 0                               |

If neither the decoded mode nor the complementary mode is set then the "Single polarity mode" is selected by default.

4. Software version

# **6 ELECTRICAL CHARACTERISTICS**

### **6.1 PARAMETER CONDITIONS**

Unless otherwise specified, all voltages are referred to  $V_{SS}$ .

# 6.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ =25°C and  $T_A$ = $T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD}=5V$  for the  $4.5V \le V_{DD} \le 5.5V$  voltage range. They are given only as design guidelines and are not tested.

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

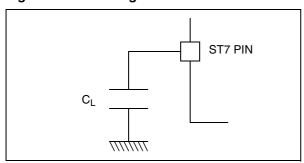

The loading conditions used for pin parameter measurement are shown in Figure 4.

Figure 4. Pin loading conditions

### 6.1.5 Pin input voltage

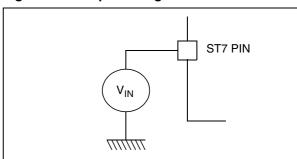

The input voltage measurement on a pin of the device is described in Figure 5.

Figure 5. Pin input voltage

### **6.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 6.2.1 Voltage Characteristics

| Symbol                            | Ratings                                            | Maximum value                  | Unit |

|-----------------------------------|----------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | Supply voltage                                     | 7.0                            | V    |

| V <sub>IN</sub>                   | Input voltage on any pin 1) & 2)                   | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | V    |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (Human Body Model) | see section 6.5.3 on page 13   |      |

| V <sub>ESD(MM)</sub>              | Electrostatic discharge voltage (Machine Model)    |                                |      |

### 6.2.2 Current Characteristics

| Symbol                                    | Ratings                                                     | Maximum value | Unit |

|-------------------------------------------|-------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                          | Total current into V <sub>DD</sub> power lines (source) 3)  | 100           |      |

| I <sub>VSS</sub>                          | Total current out of V <sub>SS</sub> ground lines (sink) 3) | 100           |      |

|                                           | Output current sunk by any standard I/O and control pin     | 25            |      |

| I <sub>IO</sub>                           | Output current sunk by any high sink I/O pin                | 50            | mA   |

|                                           | Output current source by any I/Os and control pin           | - 25          | IIIA |

| I <sub>INJ(PIN)</sub> 2) & 4)             | Injected current on RESET pin                               | ± 5           |      |

| Injected current on any other pin 5) & 6) |                                                             | ± 5           |      |

| ΣI <sub>INJ(PIN)</sub> 2)                 | Total injected current (sum of all I/O and control pins) 5) | ± 20          |      |

# 6.2.3 Thermal Characteristics

| Symbol           | Ratings                                                                | Value       | Unit |

|------------------|------------------------------------------------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range                                              | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature (see Section 7.2 THERMAL CHARACTERISTICS) |             |      |

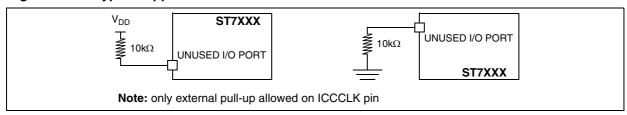

- 1. Directly connecting the I/O pins to  $V_{DD}$  or  $V_{SS}$  could damage the device if an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $10k\Omega$  for I/Os). Unused I/O pins must be tied in the same way to  $V_{DD}$  or  $V_{SS}$  according to their reset configuration.

- 2. When the current limitation is not possible, the  $V_{IN}$  absolute maximum rating must be respected, otherwise refer to  $I_{INJ(PIN)}$  specification. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .

- 3. All power  $(V_{DD})$  and ground  $(V_{SS})$  lines must always be connected to the external supply.

- 4. Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken:

- Analog input pins must have a negative injection less than 0.8 mA (assuming that the impedance of the analog voltage is lower than the specified limits)

- Pure digital pins must have a negative injection less than 1.6mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

- 5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{\text{INJ(PIN)}}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{\text{INJ(PIN)}}$  maximum current injection on four I/O port pins of the device.

- 6. True open drain I/O port pins do not accept positive injection.

# **6.3 OPERATING CONDITIONS**

# 6.3.1 General Operating Conditions:

| Symbol         | Parameter           | Conditions | Min | Max | Unit |

|----------------|---------------------|------------|-----|-----|------|

| $V_{DD}$       | Supply voltage      |            | 4.5 | 5.5 | V    |

| T <sub>A</sub> | Ambient temperature |            | -40 | +85 | °C   |

# 6.3.2 Operating Conditions with Low Voltage Detector (LVD)

| Symbol                | Parameter                                         | Conditions                  | Min  | Тур  | Max   | Unit |  |

|-----------------------|---------------------------------------------------|-----------------------------|------|------|-------|------|--|

| V <sub>IT+(LVD)</sub> | Reset release threshold (V <sub>DD</sub> rise)    |                             | 4.00 | 4.25 | 4.50  | - V  |  |

| V <sub>IT-(LVD)</sub> | Reset generation threshold (V <sub>DD</sub> fall) |                             | 3.80 | 4.10 | 4.30  |      |  |

| V <sub>hys</sub>      | LVD voltage threshold hysteresis                  | $V_{IT+(LVD)}-V_{IT-(LVD)}$ |      | 200  |       | mV   |  |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time rate <sup>1)</sup>      |                             | 20   |      | 20000 | μs/V |  |

| t <sub>g(VDD)</sub>   | Filtered glitch delay on V <sub>DD</sub>          | Not detected by the LVD     |      |      | 150   | ns   |  |

| I <sub>DD(LVD</sub> ) | LVD/AVD current consumption                       |                             |      | 200  |       | μΑ   |  |

#### Notes:

# 6.3.3 Operating Conditions with the DiSEqC™ Signalling

| Symbol                | Parameter                                                         | Conditions | Min  | Тур | Max  | Unit |

|-----------------------|-------------------------------------------------------------------|------------|------|-----|------|------|

| f <sub>DiSEqC</sub>   | DiSEqC™ tone frequency                                            |            | 17.6 | 22  | 26.4 | KHz  |

| $V_{DiSEqC}$          | DiSEqC™ tone voltage                                              |            | 150  | 650 |      | mVpp |

| V <sub>Backward</sub> | 13/18 volt backward compatibility voltage threshold <sup>1)</sup> |            |      | 15  |      | V    |

# Notes:

1. In backwards compatible mode, bus DC voltage is compared with 15 V, if it exceeds this voltage then it is considered as 13 V else it is considered as 18 V.

<sup>1.</sup> Not tested in production. The  $V_{DD}$  rise time rate condition is needed to ensure a correct device power-on and LVD reset. When the  $V_{DD}$  slope is outside these values, the LVD may not ensure a proper reset of the MCU.

# **6.4 SUPPLY CURRENT CHARACTERISTICS**

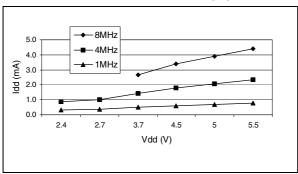

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added.

# 6.4.1 Supply Current

$T_A = -40 \text{ to } +125^{\circ}\text{C}$  unless otherwise specified

| Symbol | Parameter                                                     | Conditions                                    | Тур  | Max | Unit |

|--------|---------------------------------------------------------------|-----------------------------------------------|------|-----|------|

|        | Supply current in RUN mode 1)                                 |                                               | 4.50 | 7   |      |

|        | Supply current for LNB or switcher applications <sup>2)</sup> | V <sub>DD</sub> =5.5V, f <sub>CPU</sub> =8MHz |      | 20  | mA   |

- 1. CPU running with memory access, all I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (CLKIN) driven by external square wave, LVD disabled.

- 2. Data based on typical ST7LNB0 LNB or switcher application software running.

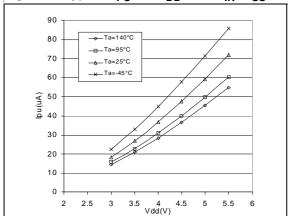

Figure 6. Typical I<sub>DD</sub> in RUN vs. f<sub>CPU</sub>

### **6.5 EMC CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

# 6.5.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 6.5.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical applica-

tion environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                     | Level/<br>Class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2 | 2B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4 | ЗВ              |

# 6.5.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbol Parameter | Parameter     | Conditions    | Monitored       | Max vs. [f | osc/f <sub>CPU</sub> ] | Unit      |

|------------------|---------------|---------------|-----------------|------------|------------------------|-----------|

|                  | i arameter    | Conditions    | Frequency Band  | 1/4MHz     | 1/8MHz                 |           |

|                  |               | SO16 package, | 0.1MHz to 30MHz | 8          | 14                     |           |

| S                | Sc Peak level |               | 30MHz to 130MHz | 27         | 32                     | $dB\mu V$ |

| SEMI             |               |               | 130MHz to 1GHz  | 26         | 28                     | İ         |

|                  |               |               | SAE EMI Level   | 3.5        | 4                      | -         |

### Notes:

1. Data based on characterization results, not tested in production.

# **EMC CHARACTERISTICS (Cont'd)**

# 6.5.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### 6.5.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard.

# **Absolute Maximum Ratings**

| Symbol                | Ratings                                             | Conditions            | Maximum value 1) | Unit |

|-----------------------|-----------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage (Human Body Model) | T <sub>A</sub> =+25°C | 4000             | V    |

#### Notes:

1. Data based on characterization results, not tested in production.

### 6.5.3.2 Static and Dynamic Latch-Up

■ LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

■ DLU: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

### **Electrical Sensitivities**

| Symbol | Parameter              | Conditions                                    | Class 1) |

|--------|------------------------|-----------------------------------------------|----------|

| LU     | Static latch-up class  | T <sub>A</sub> =+25°C                         | A        |

| DLU    | Dynamic latch-up class | $V_{DD}$ =5.5V, $f_{OSC}$ =4MHz, $T_A$ =+25°C | Α        |

### Notes:

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

**577**

# 6.6 I/O PORT PIN CHARACTERISTICS

### 6.6.1 General Characteristics

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                | Parameter                                      | Conditions                                             | Min          | Тур | Max          | Unit |

|-----------------------|------------------------------------------------|--------------------------------------------------------|--------------|-----|--------------|------|

| V <sub>IL</sub>       | Input low level voltage                        |                                                        |              |     | $0.3xV_{DD}$ | V    |

| V <sub>IH</sub>       | Input high level voltage                       |                                                        | $0.7xV_{DD}$ |     |              | V    |

| V <sub>hys</sub>      | Schmitt trigger voltage hysteresis 1)          |                                                        |              | 400 |              | mV   |

| ΙL                    | Input leakage current                          | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>      |              |     | ±1           | μА   |

| I <sub>S</sub>        | Static current consumption 2)                  | Floating input mode                                    |              |     | 200          | μА   |

| R <sub>PU</sub>       | Weak pull-up equivalent resistor <sup>3)</sup> | V <sub>IN</sub> =V <sub>SS</sub> , V <sub>DD</sub> =5V | 50           | 120 | 250          | kΩ   |

| C <sub>IO</sub>       | I/O pin capacitance                            |                                                        |              | 5   |              | pF   |

| t <sub>f(IO)out</sub> | Output high to low level fall time 1)          | C <sub>L</sub> =50pF                                   |              | 25  |              | ns   |

| t <sub>r(IO)out</sub> | Output low to high level rise time 1)          | Between 10% and 90%                                    |              | 25  |              | 115  |

### Notes:

- 1. Data based on characterization results, not tested in production.

- 2. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see Figure 7). Data based on design simulation and/or technology characteristics, not tested in production.

- 3. The  $R_{PU}$  pull-up equivalent resistor is based on a resistive transistor (corresponding  $I_{PU}$  current characteristics described in Figure 8).

Figure 7. Two typical Applications with unused I/O Pin

Figure 8. Typical I<sub>PU</sub> vs. V<sub>DD</sub> with V<sub>IN</sub>=V<sub>SS</sub>

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# **6.6.2 Output Driving Current**

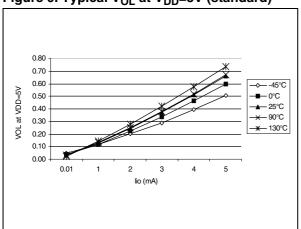

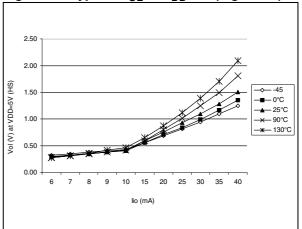

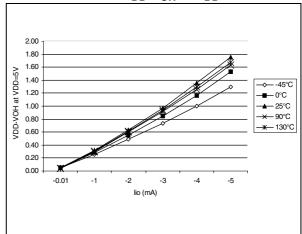

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                        | Parameter                                                                                          |                   | Conditions             | Min                  | Max  | Unit |

|-------------------------------|----------------------------------------------------------------------------------------------------|-------------------|------------------------|----------------------|------|------|

|                               | Output low level voltage for a standard I/O pin                                                    |                   | I <sub>IO</sub> =+5mA  |                      | 1.0  |      |

| V 1)                          | when 8 pins are sunk at same time (see Figure 9)                                                   |                   | I <sub>IO</sub> =+2mA  |                      | 0.4  |      |

| VOL /                         | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time (see Figure 10) | -5V               | I <sub>IO</sub> =+20mA |                      | 1.3  |      |

|                               |                                                                                                    | V <sub>DD</sub> = | I <sub>IO</sub> =+8mA  |                      | 0.75 | V    |

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin                                                           |                   | I <sub>IO</sub> =-5mA  | V <sub>DD</sub> -1.5 |      |      |

|                               | when 4 pins are sourced at same time (see Figure 11)                                               |                   | I <sub>IO</sub> =-2mA  | V <sub>DD</sub> -0.8 |      |      |

- 1. The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 6.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 2. The  $I_{IO}$  current sourced must always respect the absolute maximum rating specified in Section 6.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VDD}$ . True open drain I/O pins does not have  $V_{OH}$ .

- 3. Not tested in production, based on characterization results.

Figure 9. Typical  $V_{OL}$  at  $V_{DD}$ =5V (standard)

Figure 10. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink)

Figure 11. Typical  $V_{DD}$ - $V_{OH}$  at  $V_{DD}$ =5V

# **6.7 CONTROL PIN CHARACTERISTICS**

### 6.7.1 Asynchronous RESET Pin

| Symbol                  | Parameter                              | Conditions          |                        | Min          | Тур | Max          | Unit  |

|-------------------------|----------------------------------------|---------------------|------------------------|--------------|-----|--------------|-------|

| V <sub>IL</sub>         | Input low level voltage                |                     |                        |              |     | $0.3xV_{DD}$ | V     |

| V <sub>IH</sub>         | Input high level voltage               |                     |                        | $0.7xV_{DD}$ |     |              | ľ     |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 1)  |                     |                        |              | 1   |              | V     |

| V                       | Output low level voltage <sup>2)</sup> | V <sub>DD</sub> =5V | I <sub>IO</sub> =+5mA  |              | 0.5 | 1.0          | V     |

| $V_{OL}$                | Output low level voltage               | ADD-2A              | I <sub>IO</sub> =+2mA  |              | 0.2 | 0.4          | \ \ \ |

| R <sub>ON</sub>         | Pull-up equivalent resistor 3) 1)      | V <sub>DD</sub> =5V |                        | 20           | 40  | 80           | kΩ    |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration         | Internal r          | Internal reset sources |              | 30  |              | μS    |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)      |                     |                        | 20           |     |              | μS    |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration 5)            |                     |                        |              | 200 |              | ns    |

#### Notes:

- 1. Data based on characterization results, not tested in production.

- 2. The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 6.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 3. The  $R_{ON}$  pull-up equivalent resistor is based on a resistive transistor. Specified for voltage on  $\overline{RESET}$  pin between  $V_{ILmax}$  and  $V_{DD}$

- $\underline{4.\ To\ g}$ uarantee the reset of the device, a minimum pulse has to be applied to the  $\overline{\text{RESET}}$  pin. All short pulses applied on  $\overline{\text{RESET}}$  pin with a duration below  $t_{h(RSTL)in}$  can be ignored.

- 5. The reset network protects the device against parasitic resets.

- 6. The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- 7. Whatever the reset source is (internal or external), the user must ensure that the level on the  $\overline{\text{RESET}}$  pin can go below the  $V_{IL}$  max. level specified in section 6.7.1 on page 16. Otherwise the reset will not be taken into account internally.

- 8. Because the reset circuit is <u>designed</u> to allow the internal RESET to be output in the <u>RESET</u> pin, the user must ensure that the current sunk on the <u>RESET</u> pin (by an external pull-up for example) is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 6.2.2 on page 9.

# 7 PACKAGE CHARACTERISTICS

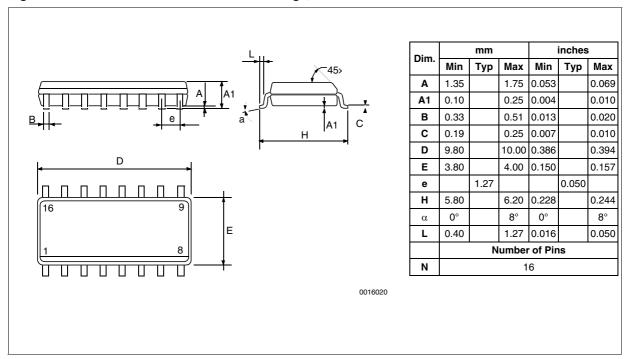

# 7.1 PACKAGE MECHANICAL DATA

Figure 12. 16-Pin Plastic Small Outline Package, 150-mil Width

### 7.2 THERMAL CHARACTERISTICS

| Symbol            | Ratings                                          | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient) | TBD   | °C/W |

| P <sub>D</sub>    | Power dissipation 1)                             | 500   | mW   |

| $T_{Jmax}$        | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

- 1. The power dissipation is obtained from the formula  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power  $(I_{DD} \times V_{DD})$  and  $P_{PORT}$  is the port power dissipation determined by the user.

- 2. The average chip-junction temperature can be obtained from the formula  $T_J = T_A + P_D x$  RthJA.

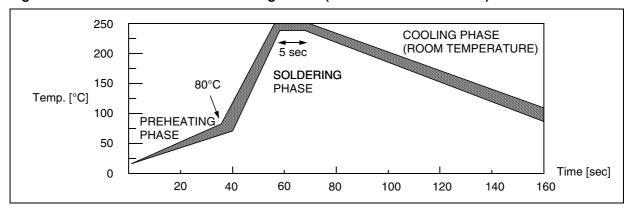

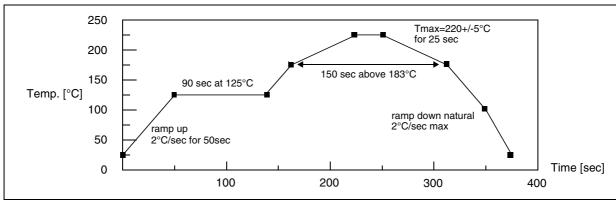

# 7.3 SOLDERING AND GLUEABILITY INFORMATION

Recommended soldering information given only as design guidelines.

Figure 13. Recommended Wave Soldering Profile (with 37% Sn and 63% Pb)

Figure 14. Recommended Reflow Soldering Oven Profile (MID JEDEC)

Recommended glue for SMD plastic packages:

■ Heraeus: PD945, PD955

Loctite: 3615, 3298

# 8 DEVICE CONFIGURATION

### **8.1 DATA EEPROM OPTION BYTES**

| Byte Name | Description                                      | Address |

|-----------|--------------------------------------------------|---------|

| FAM       | Device Family Address (11h:LNB; 15h: switcher)   | 1002h   |

| LOFREQ    | Local Oscillator Frequency Table Entry Numbers   | 1003h   |

| PARAM     | Output Mode and 22 kHz Tone Use (Hi/Lo or SB/SA) | 1004h   |

### **FAM OPTION BYTE**

Device Family Address. 11h: Normal LNB 15h: Normal Switcher

### **LOFREQ OPTION BYTE**

Local Oscillator Frequency Table Entry Number

This byte indicates the value of a LNB local oscillator:

Lowest Nibble = Lo Local Oscillator Frequency Table Entry Number

Highest Nibble = Hi Local Oscillator Frequency Table Entry Number

**Note**: see table 2 on page 8 of the "Eutelsat DisEqC slave microcontroller version 1.0".

### **PARAM OPTION BYTE**

Output Mode and 22 kHz Tone Use (Hi/Lo or SB/SA)

Bit 7:8 = Not used.

Bit 6 = Decoded Mode With Only Two Lines (the lowest line of a selection group is kept low)

0: Decoded mode with only two lines not selected

1: Decoded mode with only two lines selected

Bit 5 = Complementary Mode Selection

0: Complementary Mode not selected

1: Complementary Mode selected

### Bit 4:1 = Decoded Mode Number

0: Decoded Mode not selected

1 to 8 : Decoded Mode Number (refer to table 5a on page 11 of the "Eutelsat DisEqC slave microcontroller version 1.0").

Bit 0 = 22 kHz Tone Use

0: 22 kHz tone use for Hi/Lo switching in backwards compatible mode

1: 22 kHz tone use for SB/SA switching in backwards compatible mode

**Note:** if neither a decoded mode nor a complementary output mode is selected, the output mode is the single polarity output mode (refer to Table 3, "Single polarity output mode," on page 4).

| ST7LNB0 DiSEqC <sup>TM</sup> "slave" MICROCONTROLLER OPTION LIST (Last update: December 2004)                                          |                                                                        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| Customer<br>Address                                                                                                                    |                                                                        |  |  |  |

| Contact<br>Phone No                                                                                                                    |                                                                        |  |  |  |

| - Family addr                                                                                                                          | ess (tick one box)                                                     |  |  |  |

|                                                                                                                                        | Normal LNB (11h)                                                       |  |  |  |

|                                                                                                                                        | Normal Switcher (15h)                                                  |  |  |  |

| - Backwards (                                                                                                                          | Compatible 22 kHz tone usage (tick one box)                            |  |  |  |

|                                                                                                                                        | Hi/Lo switching                                                        |  |  |  |

|                                                                                                                                        | SB/SA switching                                                        |  |  |  |

| - Local oscilla                                                                                                                        | tor frequencies table entry number                                     |  |  |  |

|                                                                                                                                        | Hi L.O table entry number                                              |  |  |  |

|                                                                                                                                        | Lo L.O table entry number                                              |  |  |  |

| - Switching o                                                                                                                          | utput type: (tick or fill one box)                                     |  |  |  |

|                                                                                                                                        | Single polarity output  Decoded mode output (indicate the mode number) |  |  |  |

|                                                                                                                                        | Complementary output                                                   |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

| 0                                                                                                                                      |                                                                        |  |  |  |

| Comments                                                                                                                               | ·                                                                      |  |  |  |

| Nichola                                                                                                                                |                                                                        |  |  |  |

| Notes                                                                                                                                  |                                                                        |  |  |  |

| 0:                                                                                                                                     |                                                                        |  |  |  |

| Signature<br>Date                                                                                                                      |                                                                        |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

|                                                                                                                                        |                                                                        |  |  |  |

| Please download the latest version of this option list from:<br>http://www.st.com/mcu > downloads > ST7 microcontrollers > Option list |                                                                        |  |  |  |

# **9 REVISION HISTORY**

| Date         | Revision | Main changes                                                                                                                                                            |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September-04 | 2.0      | First release on st.com                                                                                                                                                 |

| December-04  | 3.0      | Changed note 4 and added "optional" in Figure 3 "ST7LNB0 typical application circuit" on page 3 Added default values in Table 5, "ST7LNB0 EEPROM Parameters," on page 7 |

| S. | Т7 | NI | D | Λ |

|----|----|----|---|---|

| J  |    | ľ  | D | v |

| Notes: |  |

|--------|--|

| notes: |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners © 2004 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia – Belgium - Brazil - Canada - China – Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com