# EUROTECHNIQUE (

# ET2147/ETL2147 Family 4096 × 1 Static Random Access Memories

## **General Description**

The ET2147 is a 4096-word by 1-bit static random access memory fabricated using N-channel silicon-gate technology X-MOS. All internal circuits are fully static and therefore require no clocks or refreshing for operation. The data is read out non-destructively and has the same polarity as the input data.

The separate ship select input automatically switches the part to its low power standby mode.

The output is held in a high impedance state during write to simplify common I/O applications

#### **Features**

- All inputs and outputs directly TTL compatible

- Static operation -no clocks or refreshing required

- Automatic power down

- High speed down to 55 ns access time

- Three-state output for bus interface

- Separate Data In and Data Out pins

- Single + 5V supply

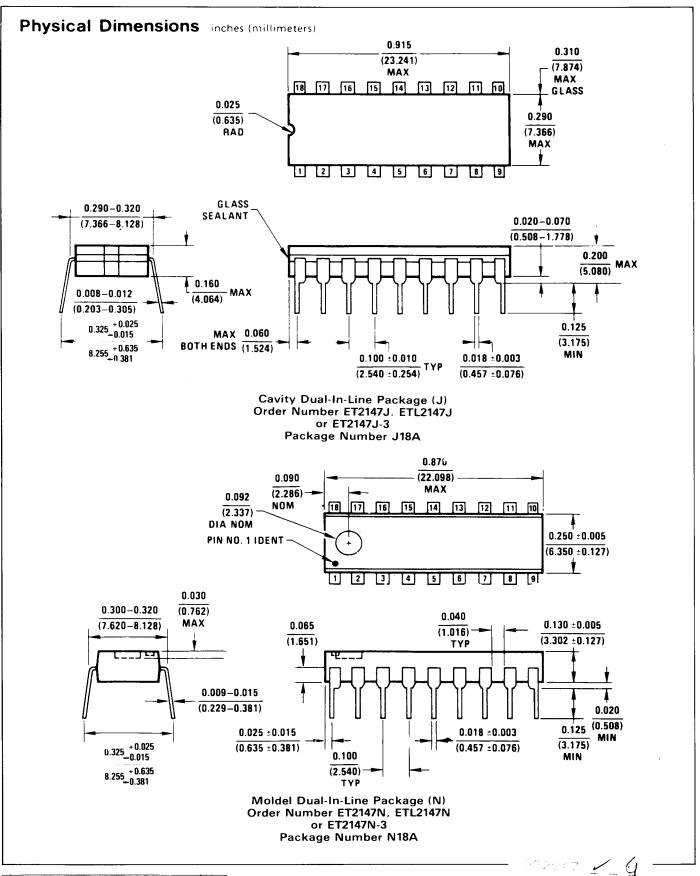

- Standard 18-pin dual-in-line package

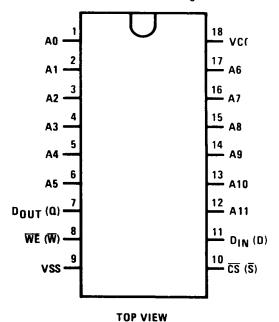

### Connection Diagram\*

#### Dual-In-Line Package

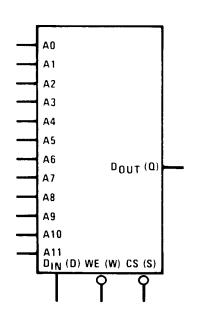

# Logic Symbol\*

#### Pin Names\*

| AU-#11   | Address Inputs |

|----------|----------------|

| WE (W)   | Write Enable   |

| CS (S)   | Chip Şelect    |

| DIN (D)  | Data In        |

| DOUT (Q) | Data Out       |

| VCC      | Power (+5V)    |

| VSS      | Ground         |

|          |                |

### Truth Table\*

| CS<br>(S) | WE<br>(W) | D <sub>IN</sub><br>(D) | Pout<br>(Q) | MODE         | POWER   |

|-----------|-----------|------------------------|-------------|--------------|---------|

| н         | X         | X                      | Hi-Z        | Not Selected | Standby |

| L         | L         | Н                      | Hi-Z        | Write 1      | Active  |

| L         | L         | L                      | Hi-Z        | Write 0      | Active  |

| L         | н         | X                      | DOUT        | Read         | Active  |

<sup>&</sup>quot;Symbols in parentheses are industry standard.

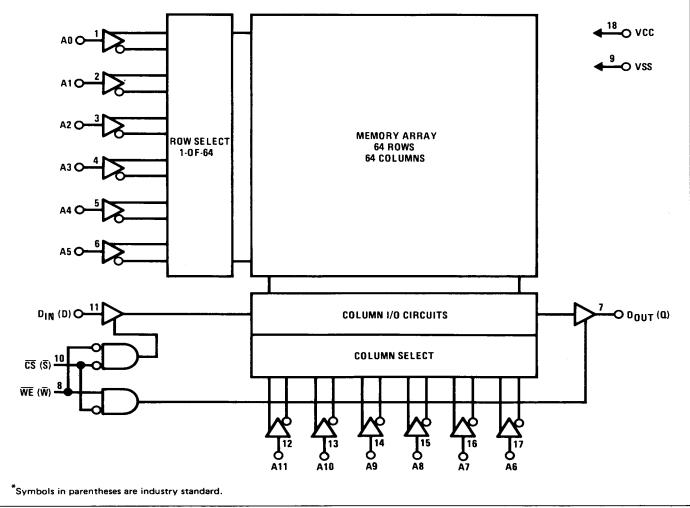

#### **Functional Description**

Two pins control the operation of the ET2147. Chip select enables write and read operations, deselects the device putting it in the low power standby mode, and controls TRI-STATING of the data-output buffer. Write enable chooses between READ and WRITE modes and also controls output TRI-STATING. The truth table details the states produced by combinations of the controls.

READ-cycle timing is shown in the section on Switching Time Waveforms. Write enable is kept high. Independent of chip select any change in address code causes new data to be fetched and brought to the output buffer. Chip select must be low, however, for the output buffer to be enabled and transfer the data to the output pin.

Address access time is the time required for an address change to produce new data at the output pin, assuming chip select has enabled the output buffer prior to data arrival. Chip select access time is the time required for chip select to enable the output buffer and transfer

previously fetched data to the output pin. Operation with chip select continuously held low is permissible.

WRITE-cycle timing is shown in the section on Switching Time Waveforms. Writing occurs only during the time both chip select and write enable are low. Minimum write pulse width refers to this simultaneous low region. Data set-up and hold times are measured with respect to whichever control first rises. Successive write operations may be performed with chip select continuously held low. Write enable then is used to terminate WRITE between address changes. Alternatively, write enable may be held low for successive WRITES and chip select used for write interruption between address change. In any event, either write enable or chip select (or both) must be high during address transitions to prevent erroneous WRITE.

Standby operation allows data to be maintained with approximately 85% less current. The device automatically switches to the low power standby mode whenever it is deselected.

### **Block Diagram\***

#### **Absolute Maximum Ratings**

#### **Operating Conditions**

Voltage on any Pin Relative to VSS Storage Temperature Range Power Dissipation

-1.5V to +7V -65°C to +150°C 1.2W

MIN MAX UNITS Supply Voltage (VCC) 5.5 Ambient Temperature (TA) +70

°C

DC Output Current Bias Temperature Range

20 mA  $-10^{\circ}$ C to  $+85^{\circ}$ C

Lead Temperature (Soldering, 10 seconds)

300° C

### DC Electrical Characteristics TA = 0°C to +70°C, VCC = 5V ±10% (Note 1)

| SYMBOL PAI |                                   | CONDITIONS                                                   | ET2147-3 |     | ET2147 |     | ETL2147 |     |       |

|------------|-----------------------------------|--------------------------------------------------------------|----------|-----|--------|-----|---------|-----|-------|

|            | PARAMETER                         |                                                              | MIN      | MAX | MIN    | MAX | MIN     | MAX | UNITS |

| VIH        | Logical "1" Input Voltage         |                                                              | 2.0      | 6.0 | 2.0    | 6.0 | 2.0     | 6.0 | V     |

| VIL        | Logical "0" Input Voltage         |                                                              | -1.0     | 0.8 | -1.0   | 0.8 | -1.0    | 0.8 | V     |

| VOH        | Logical "1" Output Voltage        | IOH = -4.0 mA                                                | 2.4      |     | 2.4    |     | 2.4     |     | V     |

| VOL        | Logical "0" Output Voltage        | IOL = 8.0 mA                                                 |          | 0.4 |        | 0.4 |         | 0.4 | V     |

| ILI        | Input Load Current                | VIN = 0 to 5.25V,<br>VCC = Max                               |          | 10  |        | 10  |         | 10  | μА    |

| IILOI      | Output Leakage Current            | VO = 4.5V to Gnd,<br>CS = VIH, VCC = Max                     |          | 50  |        | 50  |         | 50  | μΑ    |

| ICC1       | Power Supply Current              | VCC = Max, $\overline{CS}$ = VIL,<br>Outputs Open, TA = 25°C |          | 170 |        | 150 |         | 135 | mA    |

| ICC2       | Power Supply Current              | VCC = Max, $\overline{CS}$ = VIL,<br>Outputs Open, TA = 0°C  |          | 180 |        | 160 |         | 140 | mA    |

| ISB        | Standby Current                   | VCC = Min to Max,<br>CS = VIH                                |          | 30  |        | 20  |         | 10  | mA    |

| IPO        | Peak Power ON Current<br>(Note 2) | VCC = Gnd to VCC Min,  CS = Lower of VCC or  VIH (MIN)       |          | 70  |        | 50  |         | 30  | mA    |

#### Capacitance TA = 25°C, f = 1 MHz (Note 3)

| SYMBOL | PARAMETER          | CONDITIONS          | MIN | MAX | UNITS |

|--------|--------------------|---------------------|-----|-----|-------|

| CIN    | Input Capacitance  | All inputs VIN = 0V |     | 5   | pF    |

| COUT   | Output Capacitance | VO = 0V             |     | 6   | pF    |

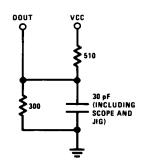

# AC Test Conditions (Note 4)

Input Pulse Levels Input Rise and Fall Times Input and Output Timing Reference Levels Output Load

Gnd to 3.5V 10 ns 1.5V See Figure 1

FIGURE 1. Output Load

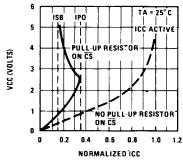

FIGURE 2. Power On Current

Note 1: Guaranteed with transverse air flow greater than 400 linear feet per minute.

Note 2: A pull-up resistor to VCC on the chip select input is required to keep the device deselected or power on current approaches ICC active (see Figure 2).

Note 3: This parameter is guaranteed by periodic testing.

Note 4: This device requires a 500 ns time delay after VCC reaches the specified minimum limit to ensure proper operation after power on. This allows the internally generated substrate bias to reach its functional level.

# Read Cycle AC Electrical Characteristics TA = 0°C to +70°C, VCC = 5V ±10%

| SYMBOL          |          |                                      | ET2 | ET2147-3 |     | ET2147, ETL2147 |       |

|-----------------|----------|--------------------------------------|-----|----------|-----|-----------------|-------|

| ALTERNATE       | STANDARD | PARAMETER                            | MIN | MAX      | MIN | MAX             | UNITS |

| †RC             | TAVAV    | Read Cycle Time                      | 55  |          | 70  |                 | ns    |

| tAA.            | TAVQV    | Address Access Time                  |     | 55       | 1   | 70              | ns    |

| tACS1           | T3LQV1   | Chip Select Access Time (Note 5)     |     | 55       | 1   | 70              | ns    |

| tACS2           | TSLQV2   | Chip Select Access Time (Nate 6)     |     | 65       | 1   | 80              | ns    |

| tOH             | XOXAT    | Output Hold from Address Change      | 5   |          | 5   |                 | ns    |

| <sup>t</sup> LZ | TSLQX    | . Chip Selection to Output Active    | 10  |          | 10  |                 | ns    |

| tHZ             | TSHQZ    | Chip Deselection to Output TRI-STATE | 0   | 40       | 0   | 40              | . ns  |

| tPU             | TSLICCH  | Chip Selection to Power Up           | 0   |          | 0   |                 | ns    |

| <sup>t</sup> PD | TSLICCL  | Chip Deselection to Power Down       |     | 30       |     | 30              | ns    |

Note 5: Chip deselected for greater than 55 ns prior to selection.

Note 6: Chip deselected for a finite time that is less than 55 ns prior to selection.

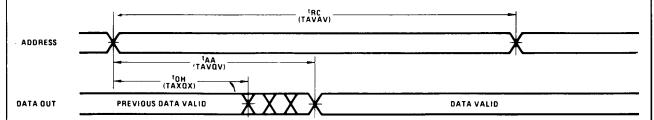

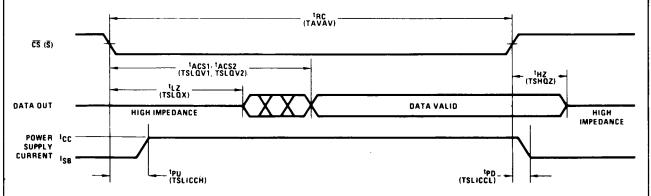

# Read Cycle Waveforms\*

#### Read Cycle No. 1 (Continuously Selected)

#### Read Cycle No. 2 (Chip Select Switched)

\*Symbols in parentheses are industry standard.

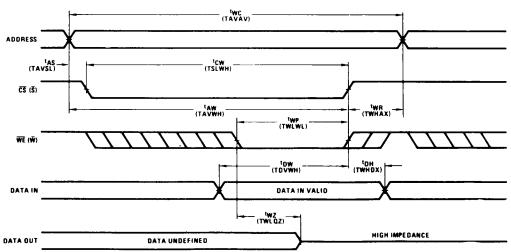

# Write Cycle AC Electrical Characteristics TA = 0°C to +70°C, VCC = 5V ±10%

| SYMBOL    |                | 242445752                       | ET2147-3 |     | ET2147, ETL2147 |     |       |

|-----------|----------------|---------------------------------|----------|-----|-----------------|-----|-------|

| ALTERNATE | STANDARD       | PARAMETER                       | MIN      | MAX | MIN             | MAX | UNITS |

| twc       | TAVAV          | Write Cycle Time                | 55       |     | 70              |     | ns    |

| †CW       | TSLWH          | Chip Selection to End of Write  | 45       |     | 55              |     | ns    |

| †AW       | TAVWH          | Address Valid to End of Write   | 45       |     | 55              |     | ns    |

| †AS       | TAVWL<br>TAVSL | Address Setup Time              | 0        |     | 0               |     | ns    |

| tWP       | TWLWL          | Write Pulse Width               | 35       |     | 40              |     | ns    |

| twr       | TWHAX          | Write Recovery Time             | 10       |     | 15              |     | ns    |

| tDW.      | TDVWH          | Data Valid to End of Write      | 25       |     | 30              |     | ns    |

| †DH       | TWHDX          | Data Hold Time                  | 10       |     | 10              |     | ns    |

| twz       | TWLQZ          | Write Enabled to Output in Hi-Z | 0        | 30  | 0               | 35  | ns    |

| vov       | TWHQX          | Output Active from End of Write | 0        | ļ   | 0               |     | ns    |

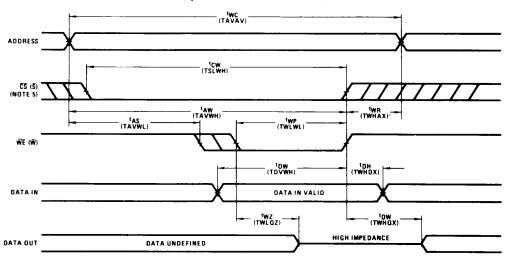

# Write Cycle Waveforms\* (Note 7)

### Write Cycle No. 1 (WE Controlled)

#### Write Cycle No. 2 (CS Controlled)

Note 7: A write occurs during the coincidental low of  $\overline{CS}$  and  $\overline{WE}$ . The output remains TRI-STATE if  $\overline{CS}$  and  $\overline{WE}$  go high simultaneously.  $\overline{WE}$  or  $\overline{CS}$  or both must be high during adress transitions.

\*Symbols in parentheses are industry standard.

Eurotechnique: 3, place Gustave Eiffel, Silic 209, 94518 Rungis Cedex, France, Tél. (1) 687.23.03, Telex: 201068

Eurotechnique Semiconductor Ltd: 4 th floor Lambourne House, 7 Western Road, Romford, Essex RM 1 3LD, UK, Tel. (708) 27.488, Telex:896683 E.T.S. Eurotechnique Semiconductor Verkaufs -GmbH, Neusser Strasse 9, D-8000 Munich 40, Germany, Tel. (89) 36.30.85/86, Telex: 528283

Headquarters, International Sales Office and Factory: Eurotechnique B.P. 2, 13790 Rousset, France, tel. (42) 23.98.01, telex: 440.306 F Eurotechnique does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and Eurotechnique reserves the right, at any time without notice, to change said circuitry