## iC-LFL1402

## 256x1 LINEAR IMAGE SENSOR

Rev A3, Page 1/8

#### **FEATURES**

- ◆ 256 active photo pixels of 56 µm at a gap and distortion free pitch of 63.5 µm (400 DPI)

- ♦ Integrating L-V conversion followed by a sample & hold circuit

- ♦ High sensitivity and uniformity over wavelength

- ♦ High clockrates of up to 5 MHz

- ♦ Only 256 clocks required for readout

- ♦ Shutter function enables flexible integration times

- ♦ Glitch-free analogue output

- ♦ Push-pull output amplifier

- ♦ 5 V single supply operation

- ♦ Can run off external bias to reduce power consumption

- ♦ Function equivalent to TSL1402 (serial mode)

### APPLICATIONS

- ♦ Optical line sensors

- **♦** CCD substitute

Copyright © 2006 iC-Haus http://www.ichaus.com

## iC-LFL1402

### 256x1 LINEAR IMAGE SENSOR

Rev A3, Page 2/8

#### **DESCRIPTION**

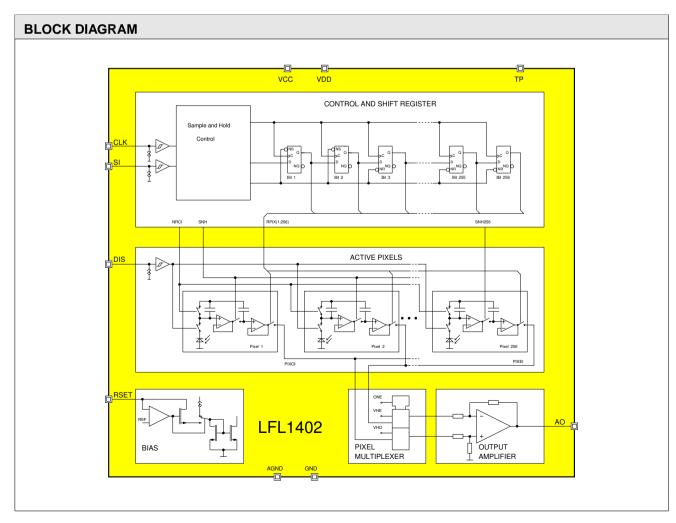

iC-LFL1402 is an integrating light-to-voltage converter with a single line of 256 pixels pitched at 63.5  $\mu$ m (center-to-center distance). Due to the monolithical integration there is no pixel-gap or pitch distortion whatsoever. Each pixel consists of a 56.4  $\mu$ m x 200  $\mu$ m photodiode, an integration capacitor and a sample and hold circuit.

The integrated control logic makes operation very simple, with only a start and clock signal necessary. A third control input enables the integration period to be prematurely terminated at any time (electronic shutter).

When the start signal is given the hold mode is activated for all pixels simultaneously with the next rising clock edge; starting with pixel 1 the hold voltages are switched in sequence to the push-pull output amplifier. The second clock pulse deletes all integration capacitors and the integration period starts again in the background during the output phase. A run is complete after 256 clock pulses.

iC-LFL1402 is suitable for high clock rates of up to 5 MHz. If this is not required the supply current can be reduced via the external bias setting.

#### PACKAGES OBGA™ LFL1C

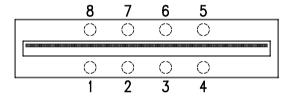

# PIN CONFIGURATION OBGA™ LFL1C (top view)

#### **PIN FUNCTIONS**

#### No. Name Function

1 SI Start Integration Input

2 CLK Clock Input

3 AO Analogue Output

4 VCC +5 V Supply Voltage

5 RSET Bias Current (resistor from VCC to

RSET; when connected to GND the in-

ternal bias setting is activated)

6 AGND Analogue Ground

7 GND Digital Ground

8 DIS Disable Integration Input

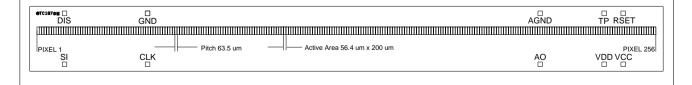

#### **CHIP-LAYOUT**

#### iC-LFL1402

Chip size: 16.6 mm x 1.7 mm

Rev A3, Page 3/8

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol | Parameter                             | Conditions                                     | Fig. |      |              | Unit |

|------|--------|---------------------------------------|------------------------------------------------|------|------|--------------|------|

| No.  | -      |                                       |                                                |      | Min. | Max.         |      |

| G001 | VDD    | Digital Supply Voltage                |                                                |      | -0.3 | 6            | V    |

| G002 | VCC    | Analogue Supply Voltage               |                                                |      | -0.3 | 6            | V    |

| G003 | V()    | Voltage at SI, CLK, DIS, RSET, TP, AO |                                                |      | -0.3 | VCC +<br>0.3 | V    |

| G004 | I()    | Current in RSET, TP, AO               |                                                |      | -10  | 10           | mA   |

| G005 | Vd()   | ESD Susceptibility at all pins        | MIL-STD-883, Method 3015,<br>HBM 100 pF/1.5 kΩ |      |      | 2            | kV   |

| G006 | Tj     | Operating Junction Temperature        |                                                |      | -40  | 125          | °C   |

| G007 | Ts     | Storage Temperature Range             | see package specification OBGA™ LFL1C          |      |      |              |      |

#### THERMAL DATA

Operating Conditions: VCC = VDD = 5 V ±10%

| Item | Symbol | Parameter                                                     | Conditions  | Fig. |      |      |      | Unit |

|------|--------|---------------------------------------------------------------|-------------|------|------|------|------|------|

| No.  |        |                                                               |             |      | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range see package specification |             |      |      |      |      |      |

|      |        |                                                               | OBGA™ LFL1C |      |      |      |      |      |

Rev A3, Page 4/8

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VCC = VDD = 5 V ±10%, RSET = GND, Tj = -25...85 °C unless otherwise noted

| Item<br>No. | Symbol           | Parameter                                        | Conditions                                                                | Tj<br>℃ | Fig. | Min. | Тур.         | Max. | Unit     |

|-------------|------------------|--------------------------------------------------|---------------------------------------------------------------------------|---------|------|------|--------------|------|----------|

| Total       | Device           |                                                  |                                                                           |         |      |      |              |      |          |

| 001         | VDD              | Digital Supply Voltage Range                     |                                                                           |         |      | 4.5  |              | 5.5  | V        |

| 002         | VCC              | Analogue Supply Voltage Range                    |                                                                           |         |      | 4.5  |              | 5.5  | V        |

| 003         | I(VDD)           | Supply Current in VDD                            | f(CLK) = 1 MHz<br>f(CLK) = 5 MHz                                          |         |      |      | 0.39<br>1.85 |      | mA<br>mA |

| 004         | I(VCC)           | Supply Current in VCC                            |                                                                           |         |      |      | 11.5         |      | mA       |

| 005         | Vc()hi           | Clamp Voltage hi at SI, CLK, DIS, TP, RSET       | Vc()hi = V() - V(VCC);<br>I() = 1 mA                                      |         |      | 0.3  |              | 1.8  | V        |

| 006         | Vc()lo           | Clamp Voltage lo at SI, CLK, DIS, TP, RSET       | Vc()hi = V() - V(AGND);<br>I() = -1 mA                                    |         |      | -1.5 |              | 0.3  | V        |

| 007         | Vc()hi           | Clamp Voltage hi at AO                           | Vc()hi = V(AO) - V(VCC);<br>I(AO) = 1 mA                                  |         |      | 0.3  |              | 1.5  | V        |

| 800         | Vc()lo           | Clamp Voltage lo at AO, VCC, VDD, GND            | Vc()lo = V() - V(AGND);<br>I() = -1 mA                                    |         |      | -1.5 |              | -0.3 | V        |

| Photo       | diode Arra       | У                                                | -                                                                         |         |      |      |              |      |          |

| 201         | A()              | Radiant Sensitive Area                           | 200 µm x 56.40 µm per Pixel                                               |         |      |      | 0.01128      |      | mm²      |

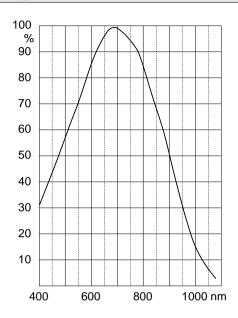

| 202         | $S(\lambda)$ max | Spectral Sensitivity                             | $\lambda = 680  \text{nm}$                                                |         | 1    |      | 0.5          |      | A/W      |

| 203         | $\lambda_{ar}$   | Spectral Application Range                       | $S(\lambda_{ar}) = 0.25 \times S(\lambda) \text{max}$                     |         | 1    | 400  |              | 980  | nm       |

| Analo       | gue Outpu        | t AO                                             |                                                                           |         |      |      |              |      |          |

| 301         | Vs()lo           | Saturation Voltage lo                            | I() = 1 mA                                                                |         |      |      |              | 0.5  | V        |

| 302         | Vs()hi           | Saturation Voltage hi                            | Vs()hi = VCC - V(), I() = -1 mA                                           |         |      |      |              | 1    | V        |

| 303         | K                | Sensitivity                                      | λ = 680 nm,<br>package OBGA™ LFL1C                                        |         |      |      | 2.88         |      | V/pWs    |

| 304         | V0()             | Offset Voltage                                   | integration time 1 ms, no illumination                                    |         |      |      | 400          | 800  | mV       |

| 305         | ΔV0()            | Offset Voltage Deviation during integration mode | $\Delta V0() = V(AO)t1 - V(AO)t2,$<br>$\Delta t = t2 - t1 = 1 \text{ ms}$ |         |      | -250 |              | 50   | mV       |

| 306         | ΔV()             | Signal Deviation during hold mode                | $\Delta V0() = V(AO)t1 - V(AO)t2,$<br>$\Delta t = t2 - t1 = 1 \text{ ms}$ |         |      | -150 |              | 150  | mV       |

| 307         | tp(CLK-<br>AO)   | Settling Time                                    | $CI(AO) = 10 pF, CLK lo \rightarrow hi until V(AO) = 0.98 x V(VCC)$       |         |      |      |              | 200  | ns       |

| Powe        | r-On-Reset       |                                                  |                                                                           |         |      |      |              |      |          |

| 801         | VCCon            | Power-On Release by VCC                          |                                                                           |         |      |      |              | 4.4  | V        |

| 802         | VCCoff           | Power-Down Reset by VCC                          |                                                                           |         |      | 1    |              |      | V        |

| 803         | VCChys           | Hysteresis                                       | VCChys = VCCon - VCCoff                                                   |         |      | 0.4  | 1            | 2    | V        |

| Bias (      | Current Adj      | ust RSET                                         |                                                                           |         | •    |      |              |      |          |

| 901         | Ibias()          | Permissible External Bias Current                |                                                                           |         |      | 20   |              | 100  | μΑ       |

| 902         | Vref             | Reference Voltage                                | I(RSET) = Ibias                                                           |         |      | 2.5  | 3            | 3.5  | V        |

| Input       | Interface S      | I, CLK, DIS                                      |                                                                           |         | •    |      |              |      |          |

| B01         | Vt()hi           | Threshold Voltage hi                             |                                                                           |         |      | 1.4  |              | 1.8  | V        |

| B02         | Vt()lo           | Threshold Voltage lo                             |                                                                           |         | İ    | 0.9  |              | 1.2  | V        |

| B03         | Vt()hys          | Hysteresis                                       | Vt()hys = $Vt()$ hi $ Vt()$ lo                                            |         |      | 300  |              | 800  | mV       |

| B04         | I()              | Pull-Down Current                                |                                                                           |         |      | 10   | 30           | 50   | μA       |

| B05         | fclk             | Permissible Clock Frequency                      |                                                                           |         |      |      |              | 5    | MHz      |

Rev A3, Page 5/8

### **OPTICAL CHARACTERISTICS: Diagrams**

Figure 1: Relative spectral sensitivity

#### **OPERATING REQUIREMENTS: Logic**

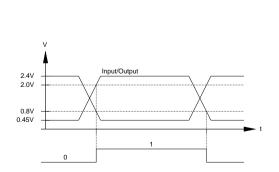

Operating Conditions: VCC = VDD = 5 V  $\pm$ 10%, Tj = -25...85 °C input levels lo = 0...0.45 V, hi = 2.4 V...VCC, see Fig. 2 for reference levels

| Item | Symbol | Parameter                                   | Conditions | Fig. |      |      | Unit |

|------|--------|---------------------------------------------|------------|------|------|------|------|

| No.  |        |                                             |            |      | Min. | Max. |      |

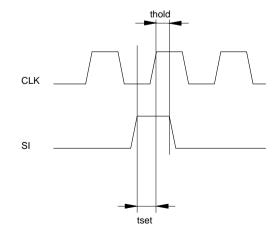

| 1001 | tset   | Setup Time:<br>SI stable before CLK lo → hi |            | 3    | 50   |      | ns   |

| 1002 | thold  | Hold Time:<br>SI stable after CLK lo → hi   |            | 3    | 50   |      | ns   |

Figure 2: Reference levels

Figure 3: Timing diagram

Rev A3, Page 6/8

#### **DESCRIPTION OF FUNCTIONS**

#### **Normal operation**

Following an internal power-on reset the integration and hold capacitors are discharged and the sample and hold circuit is set to sample mode. A high signal at SI and a rising edge at CLK triggers a readout cycle and with it a new integration cycle.

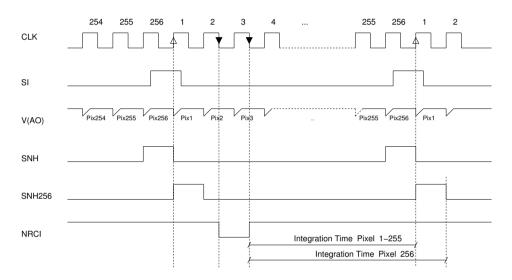

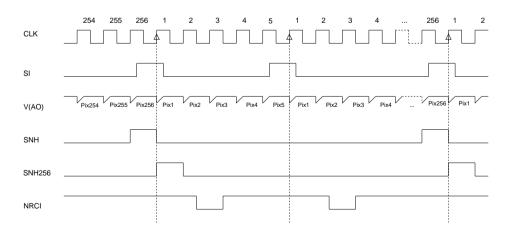

In this process the hold capacitors of pixels 1 to 255 are switched to hold mode immediately (SNH = 1),

with pixel 256 (SNH256 = 1) following suit one clock pulse later. This special procedure allows all pixels to be read out with just 256 clock pulses. The integration capacitors are discharged by a one clock long reset signal (NRCI = 0) which occurs between the  $2^{nd}$  and  $3^{rd}$  falling edge of the readout clock pulse (cf. Figure 4). After the 255 pixels have been read out these are again set to sample mode (SNH = 0), likewise for pixel 256 one clock pulse later (SNH256 = 0).

Figure 4: Readout cycle and integration sequence

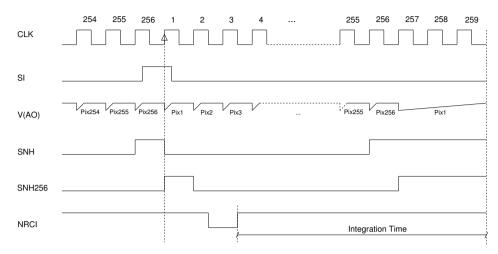

If prior to the 256<sup>th</sup> clock pulse a high signal occurs at SI the present readout is halted and immediately reinitiated with pixel 1. In this instance the hold ca-

pacitors retain their old value i.e. hold mode prevails (SNH/SNH256 = 0).

Figure 5: Restarting a readout cycle

With more than 256 clock pulses until the next SI signal, pixel 1 is output without entering hold mode; the

output voltage tracks the voltage of the pixel 1 integration capacitor.

Rev A3, Page 7/8

Figure 6: Clock pulse continued without giving a new integration start signal

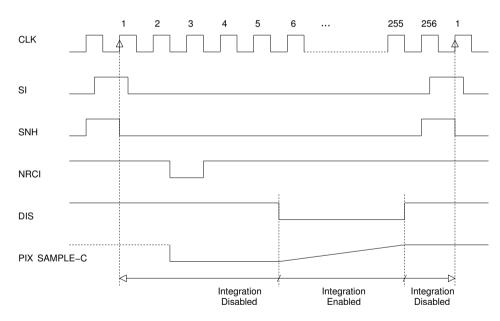

#### Operation with the shutter function

Integration can be stopped at any time via pin DIS, i.e. the photodiodes are disconnected from their corresponding integration capacitor when DIS is high and

the current integration capacitor voltages are maintained. If this pin is open or switched to GND the pixel photocurrents are summed up by the integration capacitors until the next successive SI signal follows.

Figure 7: Defining the integration time via shutter input DIS

#### **External bias current setting**

In order to reduce the power consumption of the device an external reference current can be supplied to pin RSET which reduces the maximum readout frequency, however. To this end a resistor must be connected from VCC to RSET. If this pin is not used, it should be connected to GND.

This specification is for a newly developed product. iC-Haus therefore reserves the right to change or update, without notice, any information contained herein, design and specification; and to discontinue or limit production or distribution of any product versions. Please contact iC-Haus to ascertain the current data. Copying – even as an excerpt – is only permitted with iC-Haus approval in writing and precise reference to source.

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification on this site and does not assume liability for any errors or omissions in the materials. The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

Rev A3, Page 8/8

#### ORDERING INFORMATION

| Туре       | Package          | Order Designation                |

|------------|------------------|----------------------------------|

| iC-LFL1402 | OBGA™ LFL1C<br>- | iC-LFL OBGA LFL1C<br>iC-LFL Chip |

For information about prices, terms of delivery, other packaging options etc. please contact:

iC-Haus GmbH Tel.: +49 (61 35) 92 92-0

Am Kuemmerling 18 Fax: +49 (61 35) 92 92-192

D-55294 Bodenheim Web: http://www.ichaus.com

GERMANY E-Mail: sales@ichaus.com