Document Number: MC33790 Rev 11.0. 3/2008

# Two-Channel Distributed System Interface (DSI) Physical Interface Device

The 33790 is a dual channel physical layer interface IC for the Distributed System Interface (DSI) bus. It is designed to meet automotive requirements. It can also be used in non automotive applications. It supports bidirectional communication between slave and master ICs. Some slave devices derive a regulated 5.0 V from the bus, which can be used to power sensors, thereby eliminating the need for additional circuitry and wiring.

#### **Features**

- · Two Independent DSI Compatible Buses

- · Pinout Matched to MC68HC55 (SPI to DSI Logic)

- · Wave-Shaped Bus Output Voltage

- · Independent Thermal Shutdown and Current Limit

- · Return Signalling Current Detection

- · Internal Logic Input Pull ups and Pull downs

- On-Board Charge Pump

- · 2.0 kV ESD Capability

- · Communications Rate Up to 150 kbps

- · Pb-Free Packaging Designated by Suffix Code EG

# 33790

## **DISTRIBUTED SYSTEM INTERFACE (DSI)**

DW SUFFIX EG SUFFIX (PB-FREE) 98ASB42567B 16-PIN SOICW

| ORDERING INFORMATION |                                        |           |  |  |

|----------------------|----------------------------------------|-----------|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package   |  |  |

| MC33790DW/R2         | -40°C to 85°C                          | 16 SOICW  |  |  |

| MCZ33790EG/R2        | -40 C 10 65 C                          | 10 301000 |  |  |

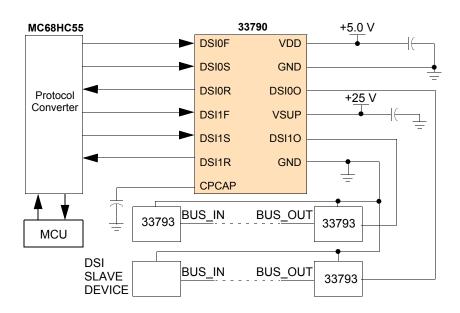

Figure 1. 33790 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

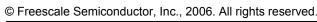

## INTERNAL BLOCK DIAGRAM

Figure 2. 33790 Simplified Internal Block Diagram

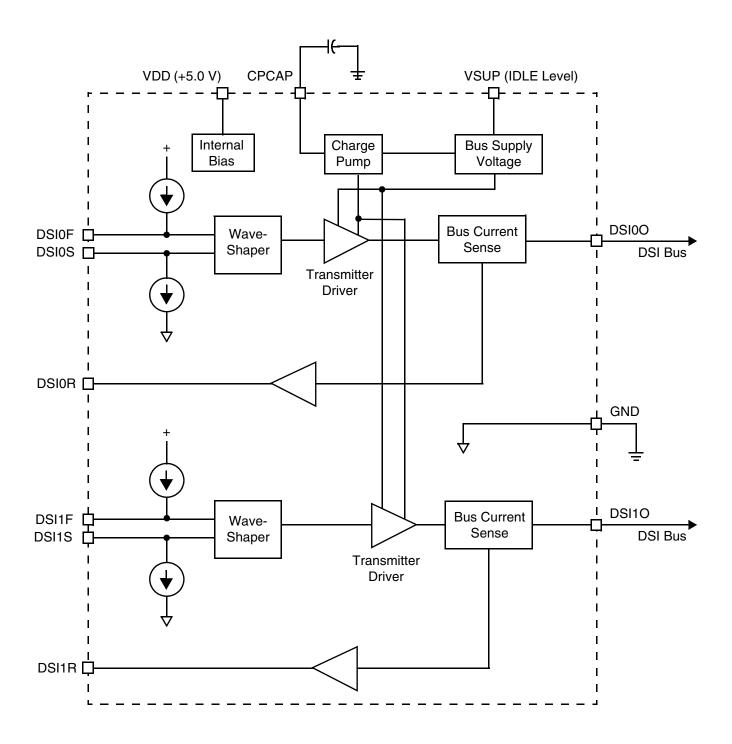

## **PIN CONNECTIONS**

Figure 3. 33790 Pin Connections

Table 1. 33790 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 8.

| Pin Number | Pin Name | Definition                                                                                                            |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 1          | DSI0F    | This logic input controls the frame output for DSI channel 0 in accordance with <u>Table 5</u> , page <u>8</u> .      |

| 2          | DSI0S    | This logic input controls the signalling output for DSI channel 0 in accordance with <u>Table 5</u> , page <u>8</u> . |

| 3          | DSI0R    | This logic output provides the return data for DSI channel 0 in accordance with <u>Table 5</u> , page <u>8</u> .      |

| 4          | DSI1F    | This logic input controls the frame output for DSI channel 1 in accordance with <u>Table 5</u> , page <u>8</u> .      |

| 5          | DSI1S    | This logic input controls the signalling output for DSI channel 1 in accordance with <u>Table 5</u> , page <u>8</u> . |

| 6          | DSI1R    | This logic output provides the return data for DSI channel 1 in accordance with <u>Table 5</u> , page <u>8</u> .      |

| 7          | NC       | Unused.                                                                                                               |

| 8          | CPCAP    | Used to store and filter charge pump output.                                                                          |

| 9          | NC       | Unused.                                                                                                               |

| 10         | NC       | Unused.                                                                                                               |

| 11         | GND      | Circuit and bus ground return.                                                                                        |

| 12         | DSI10    | DSI bus 1 input/output.                                                                                               |

| 13         | VSUP     | Idle level supply input. The voltage supplied to this pin sets the idle level on the DSI bus.                         |

| 14         | DSI0O    | DSI bus 0 input/output.                                                                                               |

| 15         | GND      | Circuit and bus ground return.                                                                                        |

| 16         | VDD      | 5.0 V logic supply input.                                                                                             |

## **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

## **Table 2. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                | Symbol              | Value                         | Unit |

|--------------------------------------------------------|---------------------|-------------------------------|------|

| ELECTRICAL RATINGS                                     |                     |                               | •    |

| Supply Voltage                                         |                     |                               | V    |

| Continuous                                             | $V_{SUP}$           | -0.5 to 25                    |      |

| Load Dump - t < 300 ms                                 | V <sub>SUP(t)</sub> | 40                            |      |

| Maximum Voltage on Input/Output Pins                   | V <sub>DD</sub>     | -0.3 to 5.5                   | V    |

|                                                        | DSIxS, DSIxF (1)    | $-0.3$ to $V_{DD} + 0.3$      |      |

|                                                        | DSIxO (1)           | -0.3 to $V_{\mbox{SUP}}$ +0.3 |      |

| Storage Temperature                                    | T <sub>STG</sub>    | -55 to 150                    | °C   |

| Operating Ambient Temperature                          | T <sub>A</sub>      | -40 to 85                     | °C   |

| Operating Junction Temperature                         | T <sub>J</sub>      | -40 to 150                    | °C   |

| Peak Package Reflow Temperature During Reflow (2), (3) | T <sub>PPRT</sub>   | Note 3                        | °C   |

| Continuous Current per Pin                             | $V_{DD}$            | 0 to 10                       | mA   |

|                                                        | DSIxR               | -2.5 to 5.0                   |      |

|                                                        | $V_{SUP}$           | 500                           |      |

| Thermal Resistance Junction to Ambient                 | $R_{	hetaJA}$       | 45                            | °C/W |

| Thermal Shutdown                                       | T <sub>SD</sub>     | 155 to 190                    | °C   |

| ESD Voltage (All Pins) (4)                             |                     |                               | V    |

| Human Body Model                                       | V <sub>ESD1</sub>   | $\pm 2000$                    |      |

| Machine Model                                          | V <sub>ESD2</sub>   | ±200                          |      |

#### Notes

- 1.  $R = 0 \Omega$ .

- 2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 3. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

- Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 4. ESD1 performed in accordance with the Human Body Model ( $C_{ZAP}$ =100pF,  $R_{ZAP}$ =1500  $\Omega$ ), ESD2 performed in accordance with the Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ ).

## STATIC ELECTRICAL CHARACTERISTICS

**Table 3. Static Electrical Characteristics**

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 8.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  25.0 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted.

| Characteristic                                                                                | Symbol              | Min                 | Тур  | Max                 | Unit |

|-----------------------------------------------------------------------------------------------|---------------------|---------------------|------|---------------------|------|

| SUPPLY                                                                                        |                     |                     |      |                     |      |

| I <sub>SUP</sub> Supply Current/Channel (Not Including I <sub>OUT</sub> )                     |                     |                     |      |                     | mA   |

| DSIx0 = Idle Voltage, -100 mA ≤ I <sub>OUT</sub> ≤ 0 mA                                       | $I_{SUPI}$          | _                   | 1.35 | 3.25                |      |

| DSIx0 = Output High Voltage, I <sub>OUT</sub> = 12 mA                                         | I <sub>SUPH</sub>   | _                   | 5.0  | 9.00                |      |

| I <sub>DD</sub> Supply Current/Channel                                                        | I <sub>DD</sub>     | _                   | 0.5  | 1.0                 | mA   |

| BUS TRANSMITTER                                                                               |                     | '                   |      |                     |      |

| V <sub>SUP</sub> to DSIxO ON Resistance (During Idle)                                         | R <sub>DS(ON)</sub> |                     |      |                     | Ω    |

| I <sub>OUT</sub> = -100 mA                                                                    |                     | _                   | -    | 10                  |      |

| Output High Voltage                                                                           | DSIV <sub>OH</sub>  |                     |      |                     | V    |

| DSIx0 (-15 mA $\leq$ I <sub>OUT</sub> $\leq$ 1.0 mA)                                          |                     | 4.175               | 4.5  | 4.825               |      |

| Output Low Voltage                                                                            | DSIV <sub>OL</sub>  |                     |      |                     | V    |

| DSIx0 (-15 mA $\leq$ I <sub>OUT</sub> $\leq$ 1.0 mA)                                          |                     | 1.325               | 1.5  | 1.675               |      |

| Output High-Side Current Limit (5)                                                            | I <sub>CLH</sub>    | -100                | -    | -200                | mA   |

| Output Low-Side Current Limit (5)                                                             | I <sub>CLL</sub>    | 110                 | _    | 220                 | mA   |

| Input Leakage                                                                                 | DSI <sub>IB</sub>   |                     |      |                     | μА   |

| DSIxO When DSIxF Is High and DSIxS Is Low (0 V $\leq$ DSIxO $\leq$ Min (V $_{SUP}$ = 16.5 V)) |                     | -200                | -    | 50                  |      |

| BUS RECEIVER                                                                                  |                     |                     |      |                     |      |

| Return Current Threshold                                                                      | I <sub>RH</sub>     | -5.0                | -6.0 | -7.0                | mA   |

| MICROCONTROLLER INTERFACE                                                                     |                     |                     |      |                     |      |

| Logic Input Thresholds DSIxS, DSIxF                                                           | V <sub>IN(TH)</sub> | 1.10                | -    | 2.20                | V    |

| Output High Voltage                                                                           | V <sub>OH</sub>     |                     |      |                     | V    |

| DSIxR Pin = -0.5 mA                                                                           |                     | 0.8 V <sub>DD</sub> | _    | $V_{DD}$            |      |

| Output Low Voltage                                                                            | V <sub>OL</sub>     |                     |      |                     | V    |

| DSIxR Pin = 1.0 mA                                                                            |                     | 0.0                 | -    | 0.2 V <sub>DD</sub> |      |

| Internal Pullup for DSIxF                                                                     | I <sub>IL</sub>     | -100                | _    | -10                 | μΑ   |

| Internal Pulldown for DSIxS                                                                   | lн                  | 10                  | -    | 100                 | μА   |

#### Notes

5. After 10  $\mu s$  settling time (assured by design).

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

**Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 8.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  25.0 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted.

| Characteristic                                             | Symbol                    | Min                   | Тур              | Max                   | Unit |

|------------------------------------------------------------|---------------------------|-----------------------|------------------|-----------------------|------|

| MICROCONTROLLER INTERFACE                                  |                           |                       |                  |                       |      |

| Microcontroller Signal Cycle Time                          | tcyc                      | 6.6                   | _                | 1000                  | μS   |

| Microcontroller Signal Low Time                            | tcycL                     | 2.0                   | _                | 667                   | μS   |

| Microcontroller Signal High Time                           | t <sub>CYCH</sub>         | 2.0                   | _                | 667                   | μS   |

| Microcontroller Signal Duty Cycle for Logic Zero           | DC <sub>LO</sub>          | 30                    | 33               | 36                    | %    |

| Microcontroller Signal Duty Cycle for Logic One            | DC <sub>HI</sub>          | 60.0                  | 66.7             | 72.0                  | %    |

| Microcontroller Signal Slew Time (6)                       | tslew                     | -                     | _                | 500                   | ns   |

| Frame Start to Signal Delay Time                           | t <sub>DLY1</sub>         | t <sub>cyc</sub> -0.1 | t <sub>cyc</sub> | t <sub>cyc</sub> +0.1 | μS   |

| Signal End to Frame End Delay Time                         | t <sub>DLY2</sub>         | 1.0                   | _                | -                     | μS   |

| Rise Time <sup>(6)</sup>                                   | t <sub>RISE</sub>         | 0                     | -                | 100                   | ns   |

| Fall Time <sup>(6)</sup>                                   | t <sub>FALL</sub>         | 0                     | _                | 100                   | ns   |

| BUS TRANSMITTER                                            |                           |                       | L                |                       |      |

| Idle to Frame and Frame to Idle Slew Rate                  | t <sub>SLEW(FRAME)</sub>  |                       |                  |                       | V/μs |

| $C \le 5.0 \text{ nF}$                                     |                           | 3.0                   | 6.0              | 10.0                  |      |

| Signal High to Low and Signal Low to High Slew Rate        | t <sub>SLEW(SIGNAL)</sub> |                       |                  |                       | V/μs |

| C ≤ 5.0 nF                                                 |                           | 3.0                   | 4.5              | 8.0                   |      |

| Data Valid ( $V_{SUPx}$ = 25 V, $C_L \le 5.0 \text{ nF}$ ) |                           |                       |                  |                       | μS   |

| DSIxF, V <sub>IN(TH)</sub> to DSIxO = 5.3 V                | t <sub>DVLD1</sub>        | 2.44                  | _                | 6.56                  |      |

| DSIxS, V <sub>IN(TH)</sub> to DSIxO = 2.6 V                | t <sub>DVLD2</sub>        | 0.25                  | _                | 1.3                   |      |

| DSIxS, V <sub>IN(TH)</sub> to DSIxO = 3.4 V                | t <sub>DVLD3</sub>        | 0.25                  | _                | 1.3                   |      |

| DSIxF, V <sub>IN(TH)</sub> to DSIxO = 7.0 V                | t <sub>DVLD4</sub>        | 0.25                  | _                | 1.3                   |      |

| BUS RECEIVER                                               | 1                         |                       | ı                | ı                     |      |

| Receiver Delay Time                                        |                           |                       |                  |                       | ns   |

| $t_{DRH}$ : I = $I_{RH}$ to DSIxR = 2.5 V                  | t <sub>DRH</sub>          | -                     | 400              | 750                   |      |

| $t_{DRL}$ : I = $I_{RH}$ to DSIxR = 2.5 V                  | t <sub>DRL</sub>          | -                     | 400              | 750                   |      |

#### Notes

6. Slew times and rise and fall times between 10% and 90% of output high and low levels.

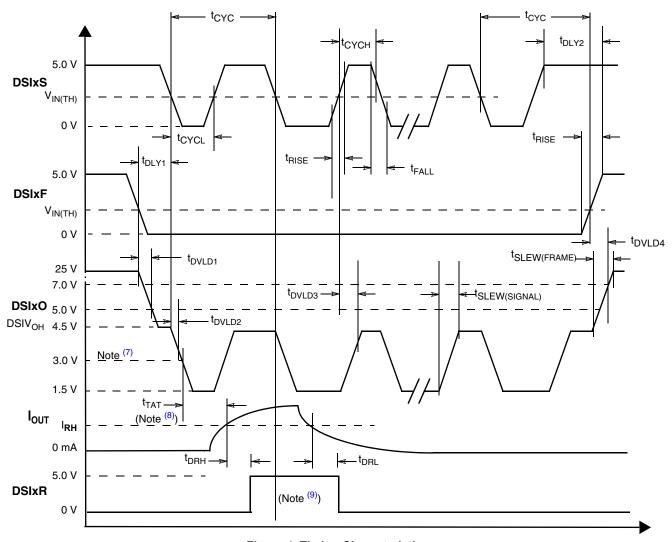

## **TIMING CHARACTERISTICS**

Figure 4. Timing Characteristics

### Notes

- 7. Typical BUSIN/BUSOUT logic thresholds (V  $_{\rm THL}$  ) from MC33793 datasheet.

- 8. t<sub>TAT</sub> (Turnaround Time) is dependent upon wire length, bus loads, and slave response characteristics.

- 9. DSIxR stable on falling edge of DSIxS or rising edge of DSIxF.

## **FUNCTIONAL DESCRIPTION**

#### **INTRODUCTION**

The 33790 is designed to provide the interface between logic and the DSI bus. It accepts signals with a typical 0 V to 5.0 V logic level to control the state of the bus output (Idle Level, Logic High Level, Logic Low Level, and High Impedance). It detects the current drawn from the bus output during signaling and outputs a 0 V to 5.0 V logic level

corresponding to the bus current being above (Logic [1] out) the bus return logic [1] current or below (Logic [0] out). The 33790 contains current limiting of the bus outputs as required by the DSI Bus specification and thermal shutdown to protect itself from damage. Two independent DSI bus outputs are provided by the IC.

#### **FUNCTIONAL TERMINAL DESCRIPTION**

#### **Bus Driver and Receiver**

The Wave-Shaper converts the 0 V to 5.0 V logic inputs from DSIxF (frame) and DSIxS (signal) to a wave-shaped signal on the DSIxO output, as shown in the timing diagrams in Figure 2, page 2, and the truth table in Table 5. The Bus Current Sense detects the current being drawn by the device(s) on the bus during signalling (DSIxF=0). If the current is above a set level, DSIxR will be high; otherwise, it is low. Due to the variations in the turnaround time ( $t_{TAT}$ ) from slave devices and bus delays, DSIxR should be sampled on the falling edge of DSIxS and on the rising edge of DSIxF (for the last return bit).

Table 5. DSI Bus Truth Table

| DSIxF | DSIxS    | Tx <sub>LIM</sub> | DSIxR       | DSIxO                        |

|-------|----------|-------------------|-------------|------------------------------|

| 0     | 0        | 0                 | Not Defined | Low (1.5 V)                  |

| 0     | 1        | 0                 | Not Defined | High (4.5 V)                 |

| 0     | <b>\</b> | 0                 | Return Data | Unchanged                    |

| 1     | Х        | 0                 | Return Data | Unchanged                    |

| 1     | 0        | 0                 | 0           | High Impedance               |

| 1     | 1        | 0                 | 0           | Idle≥V <sub>SUP</sub> -0.5 V |

| Х     | Х        | 1                 | 1           | High Impedance               |

The current for the idle state is from the supply connected to  $V_{\text{SUP}}$  and this supply should not be current limited below

250 mA per channel. During idle state, the voltage on the DSI bus will be very close to the  $V_{\rm SUP}$  voltage.

Internal thermal shutdown circuitry and current limit individually protect the DSIxO outputs from shorts to battery and ground.

Typically, the thermal shutdown occurs between  $160^{\circ}C$  and  $170^{\circ}C$ . If the junction temperature rises above this temperature, the internal  $Tx_{LIM}$  bit is asserted, and the output drivers for DSIxO are disabled by the thermal shutdown circuitry. The output drivers remain off until the junction temperature decreases below approximately  $155^{\circ}C$ , at which time the thermal shutdown circuitry turns off and the outputs are re-enabled. Each DSIxO output has a unique thermal sense and shutdown circuit, so a short on one channel does not affect the other channel.

## **Charge Pump**

The charge pump uses on-board capacitors to step the input voltage up to the voltage needed to drive the on-board transmitter FETs. A filter/storage capacitor is connected to CPCAP to hold the stepped-up voltage.

#### **Input Pullups and Pulldowns**

Internal current pullups are used on the DSIxF pins and pulldowns on the DSIxS pins. If these pins are left unconnected, their associated DSI bus will go to the unused (high impedance) state.

## **TYPICAL APPLICATIONS**

The 33790 is intended for use in a DSI system. This device supplies the interface between standard logic levels and the voltage and current required for the DSI bus. Two independent DSI busses are supported by this part. The 33790 does not form the timing for the DSI bus. This is done by logic either embedded in a microcontroller or by the MC68HC55, which uses SPI commands and forms DSI protocol for communications over the DSI bus.

The pins from the MC68HC55 are made to line up with the pins connecting to the 33790. This includes all the DSIxF, DSIxS, and DSIxR pins.

A capacitor attached to CPCAP serves as a charge reservoir for the gate drive charge pump. This circuit creates a voltage that is higher than the source of the N-channel output transistor. This allows turning on of the transistor enough to prevent any significant voltage drop across it. The rest of charge pump electronics are completely self-contained on the IC.

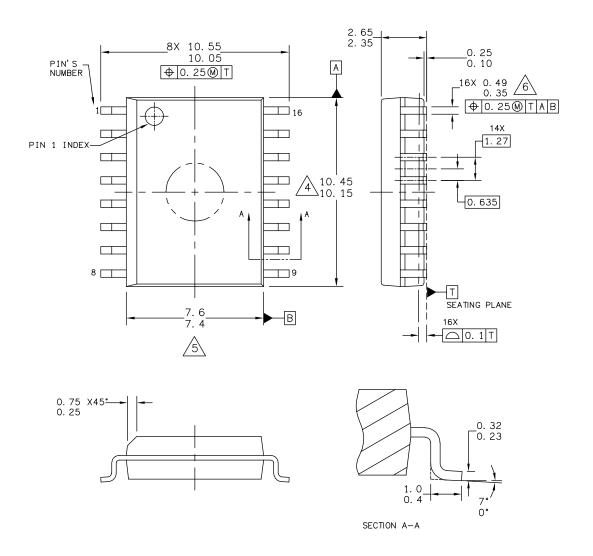

## **PACKAGING**

## **PACKAGE DIMENSIONS**

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the "98A" listed below.

#### DW SUFFIX EG SUFFIX (PB-FREE) 98ASB42567B 16-PIN SOICW

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO: 98ASB42567B |                  | REV: F      |

| 16LD SOIC W/B, 1.27 PITO<br>CASE-OUTLINE             |           | CASE NUMBER              | R: 751G-04       | 02 JUN 2005 |

|                                                      |           | STANDARD: JE             | IDEC MS-013AA    |             |

# **REVISION HISTORY**

| REVISION | DATE    | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.0      | 5/2006  | <ul><li>Implemented Revision History page</li><li>Converted to Freescale format</li></ul>                                                                                                                                                                                                                                                                                                |

| 8.0      | 11/2006 | <ul> <li>Updated data sheet format</li> <li>Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from Maximum Ratings on page 4. Added note with instructions to obtain this information from www.freescale.com.</li> </ul>                                                                                                                                   |

| 9.0      | 11/2006 | Minor correction changes to Figure 1 and ordering information                                                                                                                                                                                                                                                                                                                            |

| 10.0     | 12/2006 | Restated note Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics. on page 4 |

| 11.0     | 3/2008  | Removed watermark from page 1.                                                                                                                                                                                                                                                                                                                                                           |

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2006. All rights reserved.