# Pl2121 Cool-ORing<sup>™</sup> Series

## 8 Volt, 24 Amp Full-Function Active ORing Solution

### **Description**

The Cool-ORing<sup>TM</sup> PI2121 is a complete full-function Active ORing solution with a high-speed ORing MOSFET controller and a very low on-state resistance MOSFET designed for use in redundant power system architectures. The PI2121 Cool-ORing solution is offered in an extremely small, thermally enhanced 5mm x 7mm LGA package and can be used in low voltage (≤5Vbus) high side Active ORing applications. The PI2121 enables extremely low power loss with fast dynamic response to fault conditions, critical for high availability systems. A master/slave feature allows the paralleling of PI2121 for high current solutions Active requirements.

The PI2121, with its  $1.5 m\Omega$  internal MOSFET provides very high efficiency and low power loss during steady state operation, while achieving high-speed turn-off of the internal MOSFET during input power source fault conditions that cause reverse current flow. The PI2121 provides an active low fault flag output to the system during excessive forward current, light load, reverse current, overvoltage, under-voltage and over-temperature fault conditions. A temperature sensing function indicates a fault if the maximum junction temperature exceeds  $160^{\circ}$ C. The under-voltage and over-voltage thresholds are programmable via an external resistor divider.

### **Features**

- Integrated High Performance 24A, 1.5mΩ MOSFET

- Very-small, high density fully-optimized solution providing simple PCB layout.

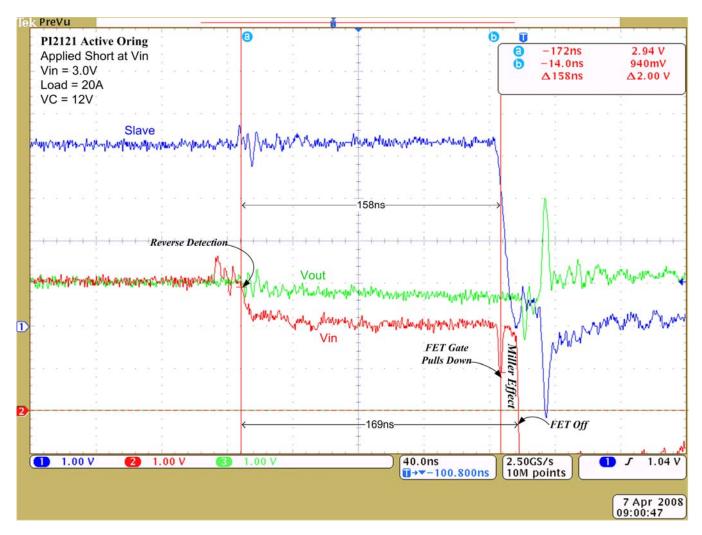

- Fast Dynamic Response to Power Source failures, with 160ns reverse current turn-off delay time

- Accurate sensing capability to indicate system fault conditions

- Programmable under & over-voltage functions

- Over temperature fault detection

- Adjustable reverse current blanking timer

- Master/Slave I/O for paralleling

- Active low fault flag output

### **Applications**

- N+1 Redundant Power Systems

- Servers & High End Computing

- Telecom Systems

- High-side Active ORing

- High current Active ORing (≤5Vbus)

### **Package Information**

17-pin 5mm x 7mm Thermally Enhanced LGA Package

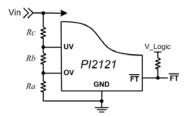

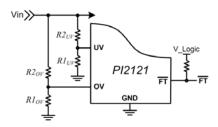

### **Typical Application:**

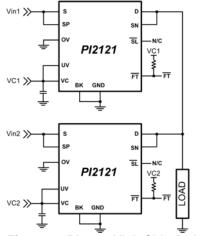

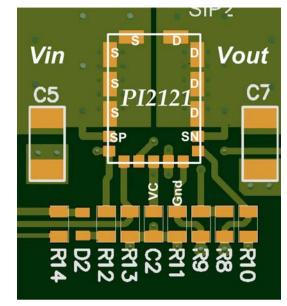

Figure 1: Pl2121 High Side Active ORing

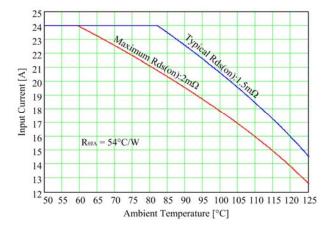

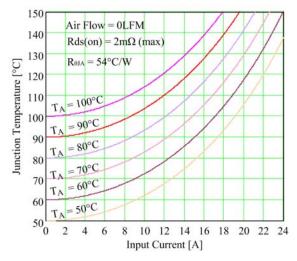

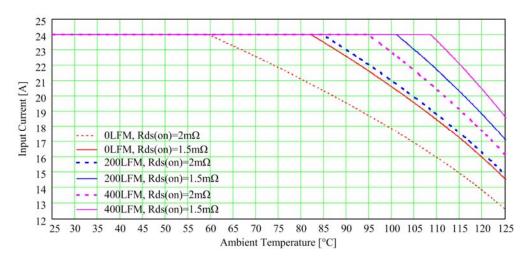

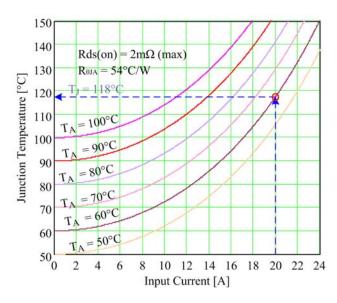

**Figure 2:** PI2121 input current de-rating based on maximum T<sub>,I</sub>=150°C vs. ambient temperature

### **Pin Description**

| Pin<br>Name     | Pin<br>Number    | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D               | 1, 15,<br>16, 17 | Drain- The Drain of the internal N-channel MOSFET, connect to the output load.                                                                                                                                                                                                                                                                                                                  |

| S               | 2, 3, 4, 5       | <b>Source-</b> The source of the internal N-channel MOSFET, connect to the input power source bus voltage.                                                                                                                                                                                                                                                                                      |

| SP              | 6                | <b>Positive Sense Input &amp; Clamp:</b> Connect SP pin to the S pin. The polarity of the voltage difference between SP and SN provides an indication of current flow direction through the MOSFET.                                                                                                                                                                                             |

| $\overline{FT}$ | 7                | <b>Fault State Output:</b> This open collector pin pulls low when a fault occurs. Fault logic inputs are VC Under-Voltage, Input Under-Voltage, Input Over-Voltage, Forward Over-Current, light load, reverse current, and Over-Temperature. Leave this pin open if unused.                                                                                                                     |

| ВК              | 8                | <b>Blanking timer Input-Output:</b> Connect a resistor from BK to GND to set the blanking time for the Reverse Comparator function. To configure in slave mode, connect BK to VC. To configure in master mode with the fastest turn-off response connect BK directly to GND.                                                                                                                    |

| SL              | 9                | <b>Slave Input-Output:</b> This pin is used for paralleling multiple PI2121 solutions in high power applications. When the PI2121 is configured as the Master, this pin functions as an output capable of driving up to $10 \ \overline{SL}$ pins of slaved PI2121 devices. It serves as an input when the PI2121 is configured in slave mode.                                                  |

| vc              | 10               | Input Supply Pin: This pin is the supply pin for the control circuitry and gate driver. Connect a 1μF capacitor between VC pin and the GND pin. Voltage on this pin is limited to 15.5V by an internal shunt regulator in high auxiliary voltage applications. For high voltage auxiliary supply applications connect a shunt resistor between VC and the auxiliary supply.                     |

| GND             | 11               | Ground: This pin is ground for the gate driver and control circuitry.                                                                                                                                                                                                                                                                                                                           |

| ov              | 12               | Input Over Voltage Input: The OV pin is used to detect an input source over-voltage condition in ground referenced applications. When the OV pin voltage crosses the OV threshold, the $\overline{FT}$ pin pulls low indicating a fault condition. The input voltage OV threshold is programmable through an external resistor divider. Connect OV to GND to disable this function.             |

| UV              | 13               | <b>Input Under-Voltage Input:</b> The UV pin is used to detect an input source under-voltage condition in ground referenced applications. When the UV pin voltage drops below the UV threshold, the $\overline{FT}$ pin pulls low indicating a fault condition. The input voltage UV threshold is programmable through an external resistor divider. Connect UV to VC to disable this function. |

| SN              | 14               | <b>Negative Sense Input &amp; Clamp-</b> Connect SN to D pin. The polarity of the voltage difference between SP and SN provides an indication of current flow direction through the MOSFET.                                                                                                                                                                                                     |

### **Package Pin-out**

17 Pin LGA (5mm x 7mm)

Top view

### **Absolute Maximum Ratings**

| Drain-to-Source Voltage (VDS)                      | 8V @ 25°C                                          |

|----------------------------------------------------|----------------------------------------------------|

| Source Current (Is ) Continuous                    | 24A                                                |

| Source Current (Is ) Pulsed (10µs)                 | 100A                                               |

| Thermal Resistance R <sub>0JA</sub> <sup>(3)</sup> | 54°C/W                                             |

| VC                                                 | -0.3V to 17.3V / 40mA                              |

| SP, SN, OV, $\overline{SL}$                        | -0.3V to 8.0V / 10mA                               |

| UV,BK, $\overline{FT}$                             | -0.3V to 17.3V / 10mA                              |

| GND                                                | -0.3V / 5A peak                                    |

| Storage Temperature                                | -65°C to 150°C                                     |

| Operating Junction Temperature                     | -40°C to Over Temperature Fault (T <sub>FT</sub> ) |

| Lead Temperature (Soldering, 20 sec)               | 250°C                                              |

| ESD Rating                                         | 2kV HBM                                            |

### **Electrical Specifications**

Unless otherwise specified:  $-40^{\circ}$ C < T<sub>J</sub> < 125°C, VC =12V, C<sub>Vc</sub> = 1uF, C<sub>SL</sub> = 10pF

| Parameter                          | Symbol               | Min | Тур  | Max  | Units | Conditions                                                           |  |  |

|------------------------------------|----------------------|-----|------|------|-------|----------------------------------------------------------------------|--|--|

| VC Supply                          |                      |     |      |      |       |                                                                      |  |  |

| Operating Supply Range (4)         | $V_{VC\text{-GND}}$  | 4.5 |      | 13.2 | V     | No VC limiting resistors                                             |  |  |

| Quiescent Current                  | I <sub>VC</sub>      |     | 3.7  | 4.2  | mA    | Normal Operating Condition, No Faults                                |  |  |

| VC Clamp Voltage                   | $V_{VC\text{-}CLM}$  | 15  | 15.5 | 16   | V     | I <sub>VC</sub> =10mA                                                |  |  |

| VC Clamp Shunt Resistance          | R <sub>VC</sub>      |     |      | 7.5  | Ω     | Delta I <sub>VC</sub> =10mA                                          |  |  |

| VC Under-voltage Rising Threshold  | $V_{VCUVR}$          |     | 4.3  | 4.5  | V     |                                                                      |  |  |

| VC Under-voltage Falling Threshold | V <sub>VCUVF</sub>   | 4.0 | 4.15 |      | V     |                                                                      |  |  |

| VC Under-voltage Hysteresis        | V <sub>VCUV-HS</sub> |     | 150  |      | mV    |                                                                      |  |  |

| Internal N-Channel MOSFET          |                      |     |      |      |       |                                                                      |  |  |

| Drain-to-Source Breakdown Voltage  | BV <sub>DSS</sub>    | 8   |      |      | V     | In OFF state, I <sub>D</sub> =250µA ,<br>Tj=25°C; Figure 10, page 11 |  |  |

| Source Current Continuous          | I <sub>S</sub>       |     |      | 24   | Α     | In ON state, Tj=25°C                                                 |  |  |

| Drain Leakage Current              | I <sub>DLK</sub>     |     |      | 10   | μA    | In OFF state, VDS=8V, Tj=25°C                                        |  |  |

| Drain-to-Source On Resistance      | R <sub>DSon</sub>    |     | 1.5  | 2.0  | mΩ    | In ON state, Is=20A, Tj=25°C<br>VC-V(S) ≥ 5V                         |  |  |

| Body Diode Forward Voltage         | $V_{\text{f-BD}}$    |     | 0.7  | 1.0  | V     | In ON state, Is=4A, Tj=25°C                                          |  |  |

| FAULT                              | FAULT                |     |      |      |       |                                                                      |  |  |

| Under-Voltage Rising Threshold     | $V_{UVR}$            |     | 500  | 540  | mV    |                                                                      |  |  |

| Under-Voltage Falling Threshold    | $V_{UVF}$            | 440 | 475  |      | mV    |                                                                      |  |  |

| Under-Voltage Threshold Hysteresis | V <sub>UV-HS</sub>   |     | 25   |      | mV    |                                                                      |  |  |

| Under-Voltage Bias Current         | I <sub>UV</sub>      | -1  |      | 1    | μA    |                                                                      |  |  |

| Over-Voltage Rising Threshold      | V <sub>OVR</sub>     |     | 500  | 540  | mV    |                                                                      |  |  |

| Over-Voltage Falling Threshold     | V <sub>OVF</sub>     | 440 | 475  |      | mV    |                                                                      |  |  |

### **Electrical Specifications**

Unless otherwise specified:  $-40^{\circ}$ C < T<sub>J</sub> < 125°C, VC =12V,  $C_{Vc}$  = 1uF,  $C_{SL}$  = 10pF

| Parameter                                                   | Symbol              | Min  | Тур  | Max | Units | Conditions                                                       |

|-------------------------------------------------------------|---------------------|------|------|-----|-------|------------------------------------------------------------------|

| FAULT (Continued)                                           |                     |      |      |     |       |                                                                  |

| Over-Voltage Threshold Hysteresis                           | $V_{\text{OV-HS}}$  |      | 25   |     | mV    |                                                                  |

| Over-Voltage Bias Current                                   | I <sub>OV</sub>     | -1   |      | 1   | μA    |                                                                  |

| Fault Output Low Voltage                                    | $V_{FTL}$           |      | 0.2  | 0.5 | V     | I <sub>FT</sub> =2mA, VC>3.5V                                    |

| Fault Output High Leakage Current                           | I <sub>FT-LC</sub>  |      |      | 10  | μA    | V <sub>FT</sub> =14V                                             |

| Fault Delay Time                                            | t <sub>FT-DEL</sub> | 20   | 40   | 60  | μs    | Includes output glitch filter                                    |

| Over Temperature Fault (1)                                  | $T_{FT}$            |      | 160  |     | °C    |                                                                  |

| Over Temperature Fault Hysteresis <sup>(1)</sup>            | T <sub>FT-HS</sub>  |      | -10  |     | °C    |                                                                  |

| DIFFERENTIAL AMPLIFIER AND CO                               | MPARAT              | ORS  |      |     |       |                                                                  |

| Common Mode Input Voltage                                   | $V_{CM}$            | -0.1 |      | 5.5 | V     | SP to GND & SN to GND                                            |

| Differential Operating Input Voltage                        | $V_{SP-SN}$         | -50  |      | 125 | mV    | SP-SN                                                            |

| SP Input Bias Current                                       | $I_{SP}$            | -50  | -37  |     | μA    | SP=SN=1.25V                                                      |

| SN Input Bias Current                                       | I <sub>SN</sub>     |      | 3.5  | 8   | μA    | SP=SN=1.25V                                                      |

| SN Voltage                                                  | $V_{SN}$            |      |      | 5.5 | V     | SP=0V                                                            |

| Reverse Comparator Threshold                                | $V_{RVS-TH}$        | -10  | -6   | -2  | mV    | V <sub>CM</sub> = 3.3V                                           |

| Reverse Comparator Hysteresis                               | $V_{RVS-HS}$        | 2    |      | 5   | mV    | V <sub>CM</sub> = 3.3V                                           |

| Reverse to Slave Low Delay Time                             | t <sub>RVS-MS</sub> |      | 160  | 200 | ns    | $V_{SP-SN}$ = -50mV step, $V_{BK}$ =0 (minimum blanking)         |

| Reverse to Slave Low Delay Time                             | t <sub>RVS-SL</sub> |      | 430  | 600 | ns    | $V_{SP-SN}$ = -50mV step, $V_{BK}$ = $V_{VC}$ (maximum blanking) |

| Forward Comparator Threshold                                | $V_{\text{FWD-TH}}$ | 2    | 6    | 9   | mV    | V <sub>CM</sub> = 3.3V                                           |

| Forward Comparator Hysteresis                               | $V_{\text{FWD-HS}}$ | -5   |      | -2  | mV    | $V_{CM} = 3.3V$                                                  |

| Forward Over Current Comparator<br>Threshold                | V <sub>OC-TH</sub>  | 60   | 66   | 70  | mV    | V <sub>CM</sub> = 3.3V                                           |

| Forward Over Current Comparator<br>Hysteresis               | V <sub>OC-HS</sub>  | -8   |      | -4  | mV    | V <sub>CM</sub> = 3.3V                                           |

| SLAVE                                                       |                     |      |      |     |       |                                                                  |

| Slave Source Current                                        | I <sub>SL</sub>     |      | -60  | -25 | μA    | V <sub>SL</sub> = 1V, Normal Operating Conditions, No Faults     |

| Slave Output Voltage High                                   | $V_{\text{SL-Hi}}$  |      | 4.3  | 5.5 | V     | Normal Operating Conditions,<br>No Faults                        |

| Slave Output Voltage Low                                    | $V_{\text{SL-Lo}}$  |      | 0.2  | 0.5 | V     | I <sub>SL</sub> =4mA                                             |

| Slave Hold-off Voltage at VC UVLO                           | V <sub>SL-UV</sub>  |      | 0.7  | 1   | V     | I <sub>SL</sub> =5µA,1.5V <vc<3.5v< td=""></vc<3.5v<>            |

| Slave Threshold                                             | V <sub>SL-TH</sub>  |      | 1.75 | 2   | V     |                                                                  |

| Slave Fall Time                                             | t <sub>SL-FL</sub>  |      | 15   | 25  | ns    | VBK=0                                                            |

| Slave Low to FET Turn Off Delay (1) Time <i>Master Mode</i> | t <sub>G-SL</sub>   |      | 20   | 30  | ns    | VBK=0                                                            |

| Slave Low to FET Turn Off Delay (1) Time <b>Slave Mode</b>  | t <sub>G-SL</sub>   |      | 100  | 130 | ns    | VBK=VC                                                           |

### **Electrical Specifications**

Unless otherwise specified:  $-40^{\circ}$ C < T<sub>J</sub> < 125°C, VC =12V, C<sub>Vc</sub> = 1uF, C<sub>SL</sub> = 10pF

|                            | , :== =; := := :, = <u>:</u> : |     |      |     |       |                                       |

|----------------------------|--------------------------------|-----|------|-----|-------|---------------------------------------|

| Parameter                  | Symbol                         | Min | Тур  | Max | Units | Conditions                            |

| BLANK                      |                                |     |      |     |       |                                       |

| Blank Source Current       | I <sub>BK</sub>                | -60 | -45  | -30 | μA    | V <sub>BK</sub> =0V                   |

| Blank Output Voltage       | $V_{BK}$                       |     | 0.77 | 0.9 | V     | I <sub>BK</sub> =5μA Connected to GND |

| Blank Slave Mode Threshold | V <sub>BK-TH</sub>             | 1.2 | 1.45 | 1.7 | V     |                                       |

- **Note 1:** These parameters are not production tested but are guaranteed by design, characterization and correlation with statistical process control.

- Note 2: Current sourced by a pin is reported with a negative sign.

- Note 3: Thermal resistance characterized on PI2121-EVAL1 evaluation board with 0 LFM airflow.

- **Note 4:** Refer to the *Auxiliary Power Supply* section in the *Application Information* for details on the VC requirement to fully enhance the internal MOSFET.

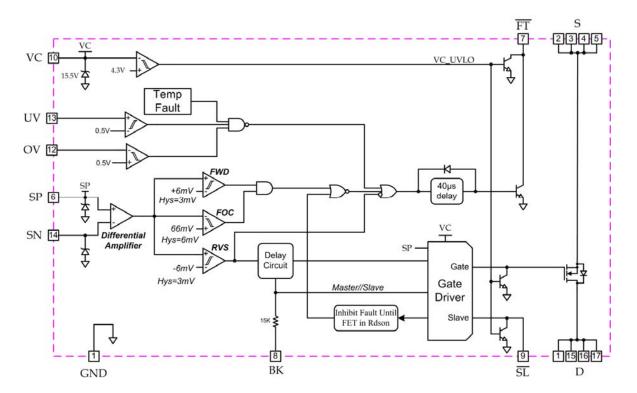

#### **Functional Description:**

The PI2121 integrated *Cool-ORing* product takes advantage of two different technologies combining a  $1.5m\Omega$  on-state resistance (Rds(on)) single N-channel MOSFET with high density control circuitry. This combination provides superior density, minimizing PCB space to achieve an ideal ORing diode function, significantly reducing power dissipation and eliminating the need for heat sinking, while minimizing design complexity.

The PI2121's 1.5m $\Omega$  on-state resistance MOSFET used in the conduction path enables a dramatic reduction in power dissipation versus performance of a diode used in conventional ORing applications due to its high forward voltage drop. This can allow for the elimination of complex heat sinking and other thermal management requirements. Due to the inherent characteristics of the integrated MOSFET, while the gate remains enhanced above the gate threshold voltage it will allow current to flow in the forward and reverse direction. Ideal ORing applications do not allow for reverse current flow, so the integrated controller has to be capable of very fast and accurate detection of reverse current caused by input power source failures, and turn off the gate of the MOSFET as quickly as possible. Once the gate voltage falls below the gate threshold, the MOSFET is off and the body diode will be reverse biased preventing reverse current flow and subsequent excessive voltage droop on the redundant bus. During forward overcurrent conditions caused by load faults, the controller maintains gate drive to the MOSFET to keep power dissipation as low as possible, otherwise the inherent body diode of the MOSFET would conduct, which has higher effective forward drop. Conventional ORing solutions using diodes offer no protection against forward over-current conditions. the forward During over-current condition, the PI2121 will provide an active-low fault flag to the system via the fault pin. The fault flag is also issued during the reverse current condition, light load conditions, VC under-voltage, Input Under-Voltage and Over-Voltage and Over-Temperature conditions.

#### **Differential Amplifier:**

The PI2121 integrates a high-speed, low offset voltage differential amplifier to sense the difference between the Sense Positive (SP) pin voltage and Sense Negative (SN) pin voltage with high accuracy. The amplifier output is connected to three comparators: Reverse comparator, Forward comparator, and Forward over-current comparator.

#### **Reverse Comparator: RVS**

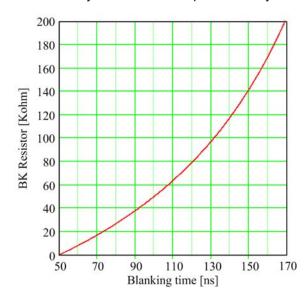

The reverse comparator is the most critical comparator. It looks for negative voltage caused by reverse current. When the SN pin is 6mV higher than the SP pin, the reverse comparator will enable the BK current source to charge an internal 2pF capacitor. The blanking timer provides noise filtering for typical switching power conversion that might cause premature reverse current detection. Once the voltage across the capacitor reaches the timer threshold voltage (1.25V) the MOSFET will be turned off. The shortest blanking time is 50ns when BK is connected to ground. The Blanking time will be added to the controller delay time. The Electrical Specifications in the DIFFERENTIAL AMPLIFIER AND COMPARATOR section for Reverse Fault to Slave Low Delay Time " $t_{RVS-MS}$  or  $t_{RVS-SL}$ " is the controller delay time plus the blanking time.

#### Reverse Blanking Timer: BK

Connecting an external resistor ( $R_{\rm BK}$ ) between the BK pin and ground will increase the blanking time as shown in the following chart.

Where:

$$R_{BK} \leq 200 K\Omega$$

If BK is connected to VC for slave mode operation, then the blanking time will be about 320ns typically, and total delay time will be 430ns.

The reverse comparator has 3mV of hysteresis referenced to SP-SN.

If the conditions are met for a reverse current fault, then the active-low fault flag output will also indicate a fault to the system after the 40µs fault delay time.

#### Forward Voltage Comparator: FWD

The FWD comparator detects when a forward current condition exists and SP is 6mV positive with respect to SN. When SP-SN is less than 6mV, the FWD comparator will assert the Fault flag to report a fault condition indicative of a light load "load not present" condition or possible shorted MOSFET.

#### **Forward Over Current Comparator: FOC**

The FOC comparator indicates an excessive forward current condition when SP is 66mV (typical) higher than SN. When the FET is in the on-state and SP-SN is higher than 66mV (typical) the PI2121 will initiate a fault condition via the  $\overline{FT}$  pin.

#### Slave:

In high current applications that exceed the single PI2121 current handling capability, multiple PI2121's can be paralleled and synchronized by using the slave function.

The Slave function synchronizes multiple PI2121's together and allows for localized control of each paralleled MOSFET. One PI2121 will be designated as the master and it will control the response of the slaved PI2121's.

When the PI2121 is configured in the "Master Mode" by connecting the BK to ground, the  $\overline{SL}$  will be an output having the same signal characteristics as the internal Gate Driver. In this configuration, the  $\overline{SL}$  output is capable of driving up to ten PI2121's, configured in "Slave Mode", through their corresponding  $\overline{SL}$  pins. Logic high for the  $\overline{SL}$  pin is limited to 5.5V (max).

When the BK pin is tied to VC, the PI2121 becomes a slave and the  $\overline{SL}$  pin will be an input. The internal Gate driver section and reverse current section are the only active circuits in the slaved PI2121 while the master performs the diagnostics and gate drive control.

#### VC and Internal Voltage Regulator:

The PI2121 has a separate input (VC) that provides power to the control circuitry and the internal gate driver. An internal regulator clamps the VC voltage to 15.5V.

For high side applications, the VC input should be 5V above the bus voltage to properly enhance the internal N-channel MOSFET.

The internal regulator circuit has a comparator to monitor the VC voltage and initiates a FAULT

condition when VC is lower than the VC Under-Voltage Threshold

#### UV:

The Under-Voltage (UV) input trip point can be programmed through an external resistor divider to monitor the input voltage. The UV comparator initiates a fault condition and pulls the  $\overline{FT}$  pin low, when UV falls below the Under-Voltage Falling Threshold. If the PI2121 is configured in a floating application, where the GND pin is connected to the input voltage, the UV pin cannot detect the input voltage. In this case, the UV pin should be disabled by connecting it to the VC pin.

#### OV:

The Over-Voltage (OV) input trip point can be programmed through an external resistor divider to monitor the input voltage. The OV comparator initiates a fault condition and pulls the  $\overline{FT}$  pin low when OV rises above the Over-Voltage Rising Threshold. If the PI2121 is configured in a floating application, where the GND pin is connected to the input voltage, the OV pin cannot detect the input voltage. In this case, the OV pin should be disabled by connecting it to the controller GND pin.

#### **Over-Temperature Detection:**

The internal Over-Temperature block monitors the junction temperature of the controller. The over-temperature threshold is set to  $160^{\circ}\text{C}$  with  $-10^{\circ}\text{C}$  of hysteresis. When the controller temperature exceeds this threshold, the over-temperature circuit initiates a fault condition and pulls the  $\overline{FT}$  pin low.

#### Fault:

The fault circuit output is an open collector with  $40\mu s$  delay to prevent any false triggering. The  $\overline{FT}$  pin will be pulled low when any of the following faults occur:

- Reverse Current

- Forward Over-Current

- Forward Low Current

- Over-Temperature

- Input Under-Voltage

- Input Over-Voltage

- VC pin Under-Voltage

A gate voltage detector prevents FOC or FWD from initiating a fault when the MOSFET is in an OFF condition.

The only fault condition that initiates gate turn-off of the MOSFET (as well as a fault flag signal) is when the reverse current fault conditions are met. All other fault conditions issue only a fault flag signal via the

$\overline{FT}$  pin, but do not affect the gate of the MOSFET. The  $\overline{FT}$  pin serves as an indicator that a fault condition may be present. This information can be

reported to a Host to signal that some system level maintenance may be required.

Figure 3: Pl2121 Internal Block Diagram

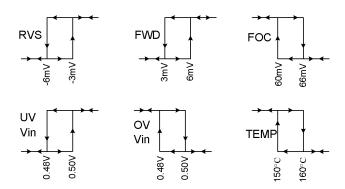

Figure 4: Comparator hysteresis, values are for reference only, please refer to the electrical specifications.

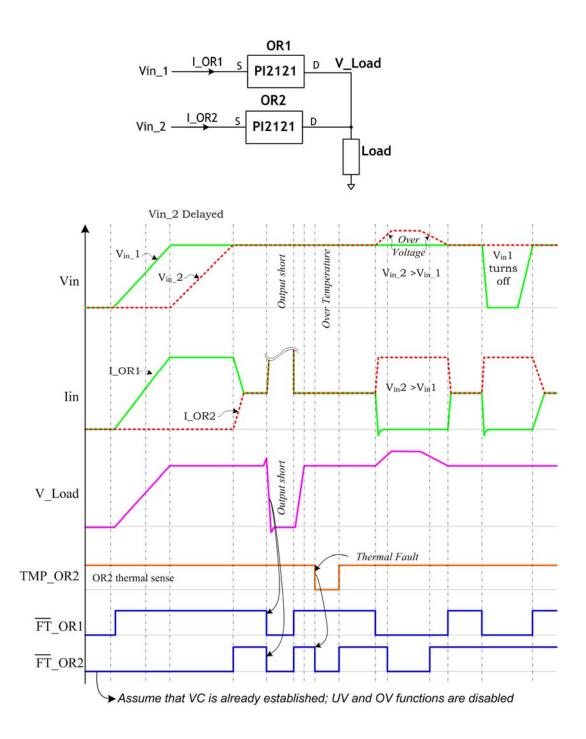

Figure 5: Timing diagram for two PI2121 solutions in an Active ORing application

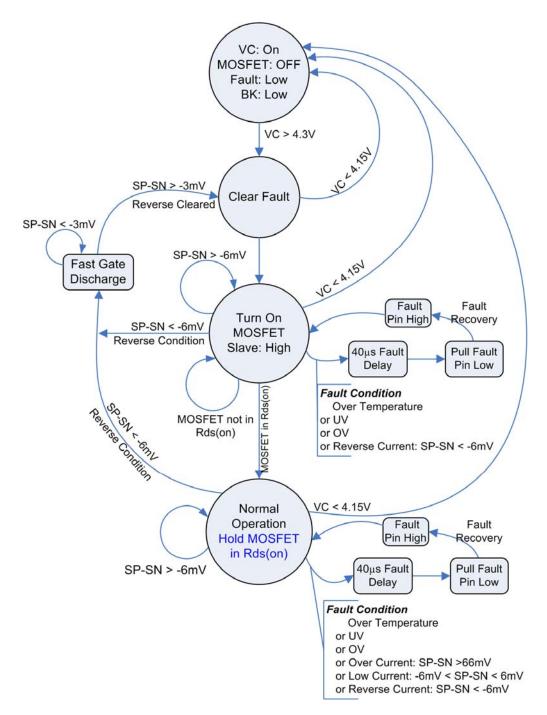

Figure 6: Pl2121 State diagram, master mode.

### **Typical Characteristics:**

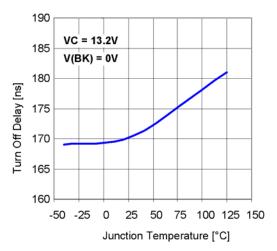

**Figure 7:** Reverse Condition internal MOSFET Turn off delay time vs. temperature.

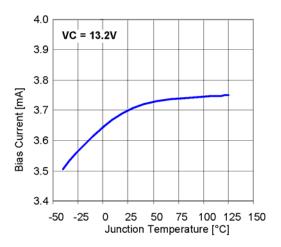

Figure 9: Controller bias current vs. temperature.

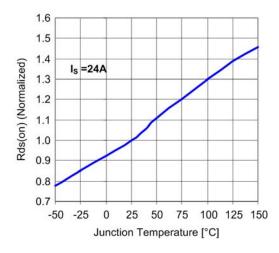

**Figure 11:** Internal MOSFET on-state resistance vs. temperature.

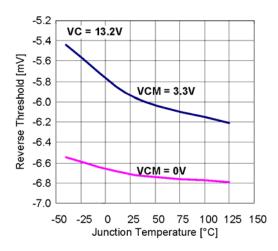

**Figure 8:** Reverse comparator threshold vs. temperature. **VCM:** Common Mode Voltage.

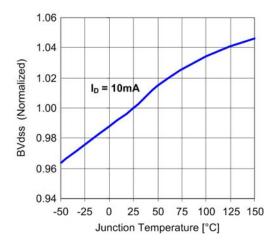

**Figure 10:** Internal MOSFET drain to source breakdown voltage vs. temperature.

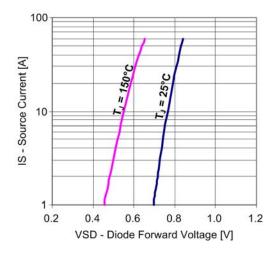

Figure 12: Internal MOSFET source to drain diode forward voltage (pulsed ≤300µs).

#### **Thermal Characteristics:**

**Figure 13:** Junction Temperature vs. Input Current (0LFM)

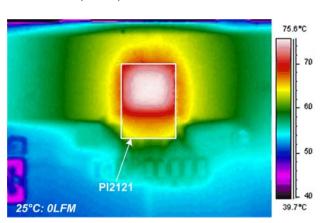

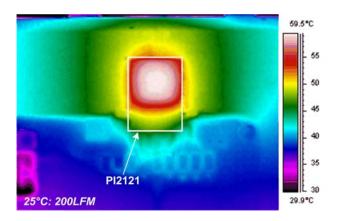

**Figure 15:** PI2121 mounted on PI2121-EVAL1 Thermal Image picture, lout=24A, T<sub>A</sub>=25°C, Air Flow=0LFM

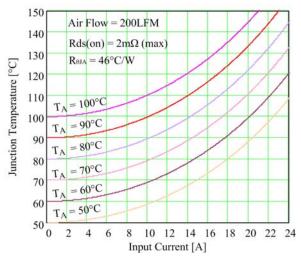

**Figure 14:** Junction Temperature vs. Input Current (200LFM)

**Figure 16:** Pl2121 mounted on Pl2121-EVAL1 Thermal Image picture, lout=24A, T<sub>A</sub>=25°C, Air Flow=200LFM

Figure 17: PI2121 input current de-rating based on maximum T<sub>J</sub>=150°C vs. ambient temperature

Figure 18: Plot of Pl2121 response time to reverse current detection (Example 1, Figure 22)

#### **Application Information**

The Pl2121 is designed to replace ORing diodes in high current, low voltage redundant power architectures. Replacing a traditional diode with a Pl2121 will result in significant power dissipation reduction as well as board space reduction, efficiency improvement and additional protection features. This section describes in detail the procedure to follow when designing with the Pl2121 Active ORing solution. Two Active ORing design examples are presented.

#### **Fault Indication:**

The FT output pin is an open collector and should be pulled up to the logic voltage or to the controller VC via a resistor (10K $\Omega$ ).

#### **Blanking Timer:**

Connect the blanking timer pin (BK) to GND to program the device for the fastest reverse comparator response time of 160ns typical. To increase the blanking time, connect the BK pin to GND via a resistor to avoid the fault response to short reverse current pulses. Refer to the plot in the reverse comparator functional description for resistor values versus the reverse blanking time.

#### **Auxiliary Power Supply (Vaux):**

Vaux is an independent power source required to supply power to the VC input. The Vaux voltage should be 5V higher than Vin (redundant power source output voltage) to fully enhance the internal MOSFET.

A bias resistor (Rbias) is required if Vaux is higher than 15V. Rbias should be connected between the VC pin and Vaux.

Minimize the resistor value for low Vaux voltage levels to avoid a voltage drop that may reduce the VC voltage lower than required to drive the gate of the internal MOSFET.

Select the value of Rbias using the following equations:

$$Rbias = \frac{Vaux_{\min} - VC_{clamp}}{IC_{\max}}$$

Rbias maximum power dissipation:

$$Pd_{Rbias} = \frac{(Vaux_{max} - VC_{clamp})^2}{Rbias}$$

Where:

$\mathit{Vaux}_{\min}$  : Vaux minimum voltage

$Vaux_{\max}$ : Vaux maximum voltage

$VC_{Clamp}$ : Controller clamp voltage, 15.5V

$IC_{

m max}$  : Controller maximum bias current, use

4.2mA

Example: Vaux 20V to 30V

$$Rbias = \frac{Vaux_{min} - VC_{clamp}}{IC_{max}} = \frac{20V - 15.5V}{4.2mA} = 1.07K\Omega$$

$$Pd_{Rbias} = \frac{(Vaux_{max} - VC_{clamp})^2}{Rbias} = \frac{(30V - 15.5V)^2}{1.07K\Omega} = 196mW$$

#### Internal N-Channel MOSFET BVdss:

The PI2121's internal N-Channel MOSFET breakdown voltage (BVdss) is rated for 8V at 25°C and will degrade at -40°C to 7.75V, refer to Figure 10. In an application when the MOSFET is turned off due to a reverse fault, the series parasitic elements in the circuit may contribute to the MOSFET being exposed to a voltage higher than its voltage rating.

In Active ORing applications when one of the input power sources is shorted, a large reverse current is sourced from the circuit output through the MOSFET. Depending on the output impedance of the system, the reverse current may reach over 60A in some conditions before the MOSFET is turned off. Such high current conditions will store energy even in a small parasitic element. For example: a 1nH parasitic inductance with 60A reverse current will generate 1.8 $\mu$ J (½Li²). When the MOSFET is turned off, the stored energy will be released and produce a high negative voltage ringing at the MOSFET

source. At the same time the energy stored at the drain side of the internal MOSFET will be released and produce a voltage higher than the load voltage. This event will create a high voltage difference between the drain and source of the MOSFET. To reduce the magnitude of the ringing voltage, add a ceramic capacitor very close to the source that can react to the voltage ringing frequency and another capacitor close to the drain. Recommended values for the ceramic capacitors are  $1\mu F$ , refer to C5 and C7 in Figure 24.

#### Slave:

For a high current application where one Pl2121 can not handle the total load current, multiple Pl2121's can be paralleled in a master / slave configuration to support the total current per input. In the Master / Slave mode, one Pl2121 is configured as the master and the rest are configured as slaves. The slave  $(\overline{SL})$  pin of the master unit will act as an output driving the units configured in slave mode. The  $\overline{SL}$  pins of the slave units will act as inputs under the control of the master.

Tie the BK pin to VC to configure the unit in slave mode.

#### Power dissipation:

In Active ORing circuits the MOSFET is always on in steady state operation and the power dissipation is derived from the total source current and the on-state resistance of the internal MOSFET.

The PI2121 internal MOSFET power dissipation can be calculated with the following equation:

$$Pd_{MOSFET} = Is^2 * Rds(on)$$

Where:

Is : Source Current

Rds(on) : MOSFET on-state resistance

Note:

Calculate with Rds(on) at maximum MOSFET temperature because Rds(on) is temperature dependent. Refer to figure 11 for normalized Rds(on) values over temperature. Pl2121 nominal Rds(on) at 25°C is  $1.5 m\Omega$  and will increase by 40% at 125°C junction temperature.

The Junction Temperature rise is a function of power dissipation and thermal resistance.

$$Trise = Rth_{JA} * Pd_{MOSFET} = Rth_{JA} * Is^2 * Rds(on),$$

Where:

$Rth_{JA}$ : Junction-to-Ambient thermal resistance (54°C/Watt)<sup>(3)</sup>

This may require iteration to get to the final junction temperature. Figures 13, 14, and 17 show the PI2121 internal MOSFET final junction temperature curves versus conducted current at given ambient temperatures and air flow.

#### **OV/UV** resistor selection:

The UV and OV comparator inputs are used to monitor the input voltage and will indicate a fault condition when this voltage is out of range. The UV & OV pins can be configured in two different ways, either with a divider on each pin, or with a three-resistor divider to the same node, enabling the elimination of one resistor. Under-voltage is monitored by the UV pin input and over-voltage is monitored with the OV pin input.

The Fault pin  $(\overline{FT})$  will indicate a fault (active low) when the UV pin is below the threshold or when the OV pin is above the threshold. The threshold is 0.50V typical with 25mV hysteresis and the input current is less than  $\pm 1\mu A$ . It is important to consider the maximum current that will flow in the resistor divider and maximum error due to UV and OV input current. Set the resistor current to  $100\mu A$  or higher to maintain better than 1% accuracy for UV and OV due to the bias current.

The three-resistor voltage divider configuration for both UV and OV to monitor the same voltage node is shown in Figure 19:

Figure 19: UV & OV three-resistor divider configuration

$$Ra = \frac{V(OV_{TH})}{I_{Ra}}$$

Set  ${\it Ra}\,{\it value}\,$  based on system allowable current  $I_{\it Ra}\,$

$$Rb = Ra\left(\frac{V(OV)}{V(UV)} - 1\right)$$

$$Rc = \left(Ra + Rb\right)\left(\frac{V(UV)}{V(UV_{TH})} - 1\right)$$

Where:

$V(UV_{TH})$  : UV threshold voltage at Vin.  $V(OV_{TH})$  : OV threshold voltage at Vin.

V(UV) : UV voltage set  $I_{Ra}$  : Ra current.

Alternatively, a two-resistor voltage divider configuration can be used and is shown in (Figure 20).

The UV resistor voltage divider can be obtained from the following equations:

$$R1_{UV} = \frac{V(UV_{TH})}{I_{RUV}}$$

Set  $R1_{\mathit{UV}}$  value based on system allowable current

$$I_{\scriptscriptstyle RUV} \geq 100 \mu A$$

$$R2_{UV} = R1_{UV} \left( \frac{V(UV)}{V(UV_{TH})} - 1 \right)$$

Where:

$V(UV_{\mathit{TH}})$ : UV threshold voltage

$I_{RUV}$ :  $R1_{UV}$  current

$$R1_{UV} = \frac{V(UV_{TH})}{I_{RUV}}$$

Set  $R1_{\mathit{OV}}$  value based on system allowable current

$$I_{RUV} \geq 100 \mu A$$

$$R2_{OV} = R1_{OV} \left( \frac{V(OV)}{V(OV_{TH})} - 1 \right)$$

Where:

$V(OV_{TH})$ : OV threshold voltage

$I_{ROV}$  :  $R1_{OV}$  current

Figure 20: UV & OV two-resistor divider configuration

#### **Typical Application Example 1:**

#### Requirement:

Redundant Bus Voltage = 3.3V Load Current = 20A (assume through each redundant path)

Maximum Ambient Temperature = 60°C, no air flow Auxiliary Voltage = 12V (10V to 14V)

#### Solution:

A single PI2121 for each redundant 3.3V power source should be used, configured as shown in the circuit schematic in Figure 22.

#### Vaux:

Since the Vaux voltage does not exceed the VC pin clamp voltage, connect the Vaux directly to the VC pin

#### SP and SN pins:

Connect each SP pin to the S pins and each SN pin to the D pins

#### BK pin:

Connect the BK pin to ground to achieve the minimum reverse current response time.

$\overline{SL}$  pin: Not required, so leave floating

#### FT pin:

Connect to the logic input and to the logic power supply via a  $10K\Omega$  resistor.

#### Program UV and OV to monitor input voltage:

Program UV at 3.0V and OV at 3.6V

Use the three-resistor divider configuration:

$$I_{Ra} = 200 \mu A$$

$$Ra = \frac{500mV}{200\mu A} = 2.5k\Omega$$

or 2.49k $\Omega$  1%

$$Rb = 2.49k\Omega \left(\frac{3.6V}{3.0V} - 1\right) = 498\Omega$$

or 499 $\Omega$  1%

$$Rc = (2.49k\Omega + 499\Omega)\left(\frac{3.0V}{500mV} - 1\right) = 14.95k\Omega$$

or 15kΩ 1%

#### **Power Dissipation and Junction Temperature:**

First use Figure 13 (Junction Temperature vs. Input Current) to find the final junction temperature for 20A load current at 60°C ambient temperature. In Figure 13 (illustrated in Figure 21) draw a vertical line from 20A to intersect the 60°C ambient temperature line. At the intersection draw a horizontal line towards the Y-axis (Junction Temperature). The Junction Temperature at full load current (20A) and 60°C ambient is 118°C.

Rds(on) is 2.0m $\Omega$  maximum at 25°C and will increase as the Junction temperature increases. From Figure 11, at 118°C Rds(on) will increase by ~35%, then

$Rds(on) = 2.0m\Omega*1.35 = 2.7m\Omega$  maximum at 118°C Maximum power dissipation is:

$$Pd_{max} = Iin^2 * Rds(on) = (20A)^2 * 2.7m\Omega = 1.08W$$

Recalculate T<sub>.1</sub>:

$$T_{J \text{ max}} = 60^{\circ}C + \left(\frac{54^{\circ}C}{W} * (20A)^2 * 2.7m\Omega\right) = 118.3^{\circ}C$$

Figure 21: Example 1 final junction temperature at  $20A/60^{\circ}C$  T<sub>A</sub>

#### **Reverse Current Threshold:**

The following procedure demonstrates how to calculate the minimum required reverse current in the internal MOSFET to generate a reverse fault condition and turn off the internal MOSFET.

At room temperature (25°C) typical Rds(on):

$$Is.reverse = \frac{Vth.reverse}{Rds(on)} = \frac{-6mV}{1.5m\Omega} = -4A$$

At maximum junction temperature (118°C) and maximum Rds(on):

$$Is.reverse = \frac{Vth.reverse}{Rds(on)} = \frac{-6mV}{2.7m\Omega} = -2.2A$$

Figure 22: Two PI2121 in High Side ORing configuration

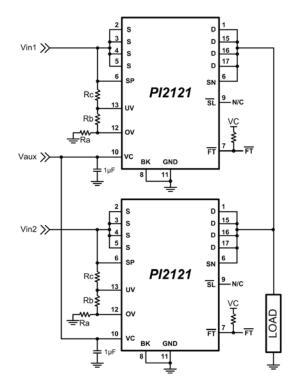

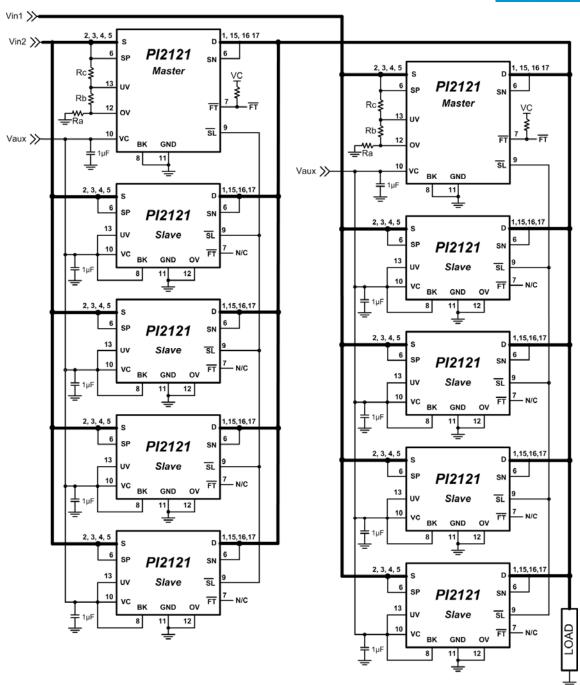

#### **Typical Application Example 2:**

#### Requirement:

Redundant Bus Voltage = 1.2V Load Current = 100A (assume through each redundant path) Auxiliary Voltage = 12V

#### Solution:

Five PI2121's for each redundant 1.2V power source should be used, configured in a master / slave configuration as shown in the circuit schematic in Figure 23.

**Vaux:** Since the Vaux voltage does not exceed the VC pin clamp voltage, connect the Vaux directly to each PI2121 VC pin.

**SP** and **SN** pins: For each specific Pl2121, connect each SP pin to the respective S pins and each SN pin to the respective D pins. The master unit will perform the sensing function.

**BK pin:** Connect the Master PI2121 BK pin directly to ground to achieve the minimum reverse current response time, and connect the BK pin of the slaved PI2121's to the respective local VC pin.

$\overline{SL}$  **pin:** For each set of parallel PI2121's connect the  $\overline{SL}$  pins together.

$\overline{FT}$  pin: Connect the  $\overline{FT}$  pin of the Master PI2121 to a logic input and to the logic power supply via a 10K $\Omega$  resistor.

# Program UV and OV of the Master PI2121 to monitor Input Voltage:

Program UV at 1.1V and OV at 1.3V Use the three-resistor divider configuration:

$$I_{Ra} = 200 \,\mu\text{A}$$

$$Ra = \frac{500 mV}{200 \,\mu\text{A}} = 2.5 k\Omega \text{ or } 2.49 k\Omega \, 1\%$$

$$Rb = 2.49 k\Omega \left(\frac{1.3V}{1.1V} - 1\right) = 452 \Omega \text{ or } 453 \Omega \, 1\%$$

$$Rc = \left(2.49 k\Omega + 453 \Omega\right) \left(\frac{1.1V}{500 mV} - 1\right) = 3.53 k\Omega$$

or  $3.57 k\Omega \, 1\%$

Figure 23: PI2121 used in a 100A Active ORing application (master/slave configuration)

#### **Layout Recommendation:**

Use the following general guidelines when designing printed circuit boards. An example of the typical land pattern for the PI2121 is shown in Figure 24:

- Make sure to have a solid ground (return) plane to reduce circuit parasitic.

- Connect all S pads together with a wide trace to reduce trace parasitics to accommodate the high current input, and also connect all D pads together with a wide trace to accommodate the high current output.

- Connect the SP pin to the S pins and connect the SN pin to D pins as shown in Figure 24.

- Use 1oz of copper or thicker if possible to reduce trace resistance and reduce power dissipation.

- The VC bypass capacitor should be located as close as possible to the VC and GND pins. Place the Pl2121 and bypass capacitor on the same layer of the board. The VC pin and C<sub>VC</sub> (shown as C2 in Figure 24) PCB trace should not contain any vias or connect to the ground plane close to the GND pin.

- Keep the power source very close to the S input pins, any parasitic in the trace connecting the power source and S pins will have inductive kick back when there is high current flow in the trace and the MOSFET turns off due to reverse current fault conditions. The inductive kick back

will produce a high voltage across the MOSFET. If it is not possible to connect the power source and S pins with a very short trace or common point, connect a capacitor (shown as C5 in figure 24), recommended value  $1\mu F$ , close to the S pins and return (ground). Also for the same reason use C7 in figure 24 at the output.

Figure 24: PI2121 layout recommendation

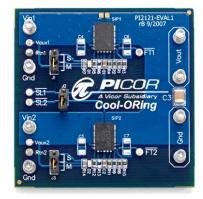

Figure 25: PI2121 Mounted on PI2121-EVAL1

Please visit www.picorpower.com for information on PI2121-EVAL1

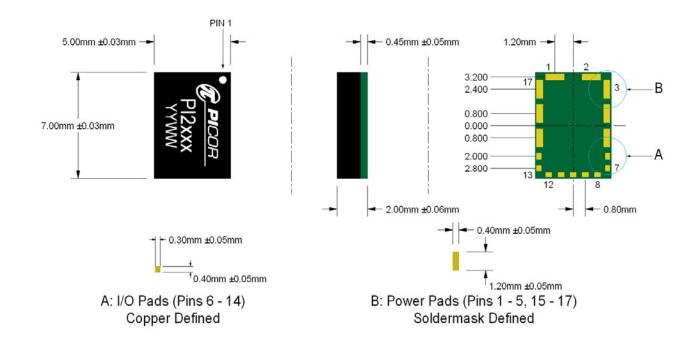

### **Package Drawing**

#### **Thermal Resistance Ratings**

| Parameter               | Symbol            | Typical | Max | Unit |

|-------------------------|-------------------|---------|-----|------|

| Junction-to-Ambient (3) | $\theta_{\sf JA}$ | 54      | -   | °C/W |

| Junction-to-PCB         | $\theta_{\sf JC}$ | 14      | -   | °C/W |

Note 3: Thermal resistance characterized on PI2121-EVAL1 evaluation board with 0 LFM airflow.

#### **Ordering Information**

| Part Number    | Package          | Transport Media |

|----------------|------------------|-----------------|

| PI2121-00-LGIZ | 5x7mm 17-pin LGA | Tape & Reel     |

### Warranty

Vicor products are guaranteed for two years from date of shipment against defects in material or workmanship when in normal use and service. This warranty does not extend to products subjected to misuse, accident, or improper application or maintenance. Vicor shall not be liable for collateral or consequential damage. This warranty is extended to the original purchaser only.

EXCEPT FOR THE FOREGOING EXPRESS WARRANTY, VICOR MAKES NO WARRANTY, EXPRESS OR LIMITED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Vicor will repair or replace defective products in accordance with its own best judgment. For service under this warranty, the buyer must contact Vicor to obtain a Return Material Authorization (RMA) number and shipping instructions. Products returned without prior authorization will be returned to the buyer. The buyer will pay all charges incurred in returning the product to the factory. Vicor will pay all reshipment charges if the product was defective within the terms of this warranty.

Information published by Vicor has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Vicor reserves the right to make changes to any products without further notice to improve reliability, function, or design. Vicor does not assume any liability arising out of the application or use of any product or circuit; neither does it convey any license under its patent rights nor the rights of others. Vicor general policy does not recommend the use of its components in life support applications wherein a failure or malfunction may directly threaten life or injury. Per Vicor Terms and Conditions of Sale, the user of Vicor components in life support applications assumes all risks of such use and indemnifies Vicor against all damages.

Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor components are not designed to be used in applications, such as life support systems, wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor's Terms and Conditions of Sale, which are available upon request.

Specifications are subject to change without notice.

Vicor Corporation 25 Frontage Road Andover, MA 01810 USA Picor Corporation 51 Industrial Drive North Smithfield, RI 02896 USA

Customer Service: custserv@vicorpower.com Technical Support: apps@vicorpower.com Tel: 800-735-6200 Fax: 978-475-6715